Professional Documents

Culture Documents

FSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant Operation

Uploaded by

sontuyet82Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant Operation

Uploaded by

sontuyet82Copyright:

Available Formats

2007 Fairchild Semiconductor Corporation www.fairchildsemi.

com

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

FSQ0565R, FSQ0765R Rev. 1.0.0

October 2007

FSQ0565R, FSQ0765R

Green-Mode Fairchild Power Switch (FPS) for

Quasi-Resonant Operation - Low EMI and High Efficiency

Features

Optimized for Quasi-Resonant Converter (QRC)

Low EMI through Variable Frequency Control and AVS

(Alternating Valley Switching)

High-Efficiency through Minimum Voltage Switching

Narrow Frequency Variation Range over Wide Load

and Input Voltage Variation

Advanced Burst-Mode Operation for Low Standby

Power Consumption

Simple Scheme for Sync Voltage Detection

Pulse-by-Pulse Current Limit

Various Protection functions: Overload Protection

(OLP), Over-Voltage Protection (OVP), Abnormal

Over-Current Protection (AOCP), Internal Thermal

Shutdown (TSD) with Hysteresis, Output Short

Protection (OSP)

Under-Voltage Lockout (UVLO) with Hysteresis

Internal Start-up Circuit

Internal High-Voltage Sense FET (650V)

Built-in Soft-Start (15ms)

Applications

Power Supply for LCD TV and Monitor, VCR, SVR,

STB, and DVD & DVD Recorder

Adapter

Related Resourses

Visit: http://www.fairchildsemi.com/apnotes/ for:

AN-4134: Design Guidelines for Offline Forward

Converters Using Fairchild Power Switch (FPS

)

AN-4137: Design Guidelines for Offline Flyback

Converters Using Fairchild Power Switch (FPS

)

AN-4140: Transformer Design Consideration for

Offline Flyback Converters Using Fairchild Power

Switch (FPS

)

AN-4141: Troubleshooting and Design Tips for

Fairchild Power Switch (FPS

) Flyback Applications

AN-4145: Electromagnetic Compatibility for Power

Converters

AN-4147: Design Guidelines for RCD Snubber of

Flyback

AN-4148: Audible Noise Reduction Techniques for

Fairchild Power Switch Fairchild Power Switch(FPS

)

Applications

AN-4150: Design Guidelines for Flyback Converters

Using FSQ-Series Fairchild Power Switch (FPS

)

Description

A Quasi-Resonant Converter (QRC) generally shows

lower EMI and higher power conversion efficiency than a

conventional hard-switched converter with a fixed

switching frequency. The FSQ-series is an integrated

Pulse-Width Modulation (PWM) controller and

SenseFET specifically designed for quasi-resonant

operation and Alternating Valley Switching (AVS). The

PWM controller includes an integrated fixed-frequency

oscillator, Under-Voltage Lockout (UVLO), Leading-

Edge Blanking (LEB), optimized gate driver, internal soft-

start, temperature-compensated precise current sources

for a loop compensation, and self-protection circuitry.

Compared with a discrete MOSFET and PWM controller

solution, the FSQ-series can reduce total cost,

component count, size, and weight; while simultaneously

increasing efficiency, productivity, and system reliability.

This device provides a basic platform that is well suited

for cost-effective designs of quasi-resonant switching

flyback converters.

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 2

Ordering Information

Notes:

1. The junction temperature can limit the maximum output power.

2. 230V

AC

or 100/115V

AC

with doubler.

3. Typical continuous power in a non-ventilated enclosed adapter measured at 50C ambient temperature.

4. Maximum practical continuous power in an open-frame design at 50C ambient.

5. Pb-free package per JEDEC J-STD-020B.

Product

Number

PKG.

(5)

Operating

Temp.

Current

Limit

R

DS(ON)

Max.

Maximum Output Power

(1)

Replaces

Devices

230V

AC

15%

(2)

85-265V

AC

Adapter

(3)

Open

Frame

(4)

Adapter

(3)

Open

Frame

(4)

FSQ0565R TO-220F-6L -25 to +85C 3.0A 2.2 70W 80W 41W 60W

FSCM0565R

FSDM0565RB

FSQ0765R TO-220F-6L -25 to +85C 3.5A 1.6 80W 90W 48W 70W

FSCM0765R

FSDM0765RB

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 3

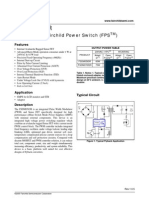

Application Diagram

Figure 1. Typical Flyback Application

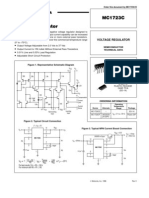

Internal Block Diagram

Figure 2. Internal Block Diagram

V

CC

GND

Drain

Sync

V

O

PWM

FB

AC

IN

V

str

FSQ0765R Rev.00

8V/12V

V

ref

S

Q R

V

CC

V

ref

I

delay

I

FB

V

SD

V

OVP

V

OCP

S

Q

Q

R

R

3R

V

CC

good

V

CC

Drain

FB

GND

AOCP

Gate

driver

V

CC

good

LEB

250ns

PWM

V

Burst

5

Sync

(1.1V)

Soft-

Start

0.35/0.55

OSC

V

str

TSD

4

3 1 6

FSQ0765R Rev.00

2

AVS

Q

V

OSP

LPF

LPF

t

ON

< t

OSP

after SS

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 4

Pin Configuration

Figure 3. Pin Configuration (Top View)

Pin Definitions

Pin # Name Description

1 Drain SenseFET drain. High-voltage power SenseFET drain connection.

2 GND Ground. This pin is the control ground and the SenseFET source.

3 V

CC

Power Supply. This pin is the positive supply input. This pin provides internal operating cur-

rent for both start-up and steady-state operation.

4 FB

Feedback. This pin is internally connected to the inverting input of the PWM comparator. The

collector of an opto-coupler is typically tied to this pin. For stable operation, a capacitor should

be placed between this pin and GND. If the voltage of this pin reaches 6V, the overload pro-

tection triggers, which shuts down the FPS.

5 Sync

Sync. This pin is internally connected to the sync-detect comparator for quasi-resonant switch-

ing. In normal quasi-resonant operation, the threshold of the sync comparator is 1.2V/1.0V.

6 V

str

Start-up. This pin is connected directly, or through a resistor, to the high-voltage DC link. At

start-up, the internal high-voltage current source supplies internal bias and charges the exter-

nal capacitor connected to the V

CC

pin. Once V

CC

reaches 12V, the internal current source is

disabled. It is not recommended to connect V

str

and Drain together.

6. V

str

5. Sync

4. FB

3. V

CC

2. GND

1. Drain

FSQ0765R Rev.00

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 5

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be opera-

ble above the recommended operating conditions and stressing the parts to these levels is not recommended. In addi-

tion, extended exposure to stresses above the recommended operating conditions may affect device reliability. The

absolute maximum ratings are stress ratings only. T

A

= 25C, unless otherwise specified.

Notes:

6. Repetitive rating: Pulse width limited by maximum junction temperature.

7. L=14mH, starting T

J

=25C.

Thermal Impedance

T

A

= 25C unless otherwise specified.

Notes:

8. Free standing with no heat-sink under natural convection.

9. Infinite cooling condition - refer to the SEMI G30-88.

Symbol Parameter Min. Max. Unit

V

str

V

str

Pin Voltage 500 V

V

DS

Drain Pin Voltage 650 V

V

CC

Supply Voltage 20 V

V

FB

Feedback Voltage Range -0.3 13 V

V

Sync

Sync Pin Voltage -0.3 11 V

I

DM

Drain Current Pulsed

FSQ0565R 11 A

FSQ0765R 15 A

I

D

Continuous Drain Current

(6)

FSQ0565R

T

C

= 25C 2.8

A

T

C

= 100C 1.7

FSQ0765R

T

C

= 25C 3.8

A

T

C

= 100C 2.4

E

AS

Single Pulsed Avalanche

Energy

(7)

FSQ0565R 190 mJ

FSQ0765R 370 mJ

P

D

Total Power Dissipation(Tc=25

o

C) 45 W

T

J

Operating Junction Temperature Internally limited C

T

A

Operating Ambient Temperature -25 +85 C

T

STG

Storage Temperature -55 +150 C

ESD

Electrostatic Discharge Capability, Human Body Model 2.0 kV

Electrostatic Discharge Capability, Charged Device Model 2.0 kV

Symbol Parameter Package Value Unit

JA

Junction-to-Ambient Thermal Resistance

(8)

TO-220F-6L

50

C/W

JC

Junction-to-Case Thermal Resistance

(9)

2.8

C/W

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 6

Electrical Characteristics

T

A

= 25C unless otherwise specified.

Continued on the following page...

Symbol Parameter Condition Min. Typ. Max. Unit

SENSEFET SECTION

BV

DSS

Drain Source Breakdown Voltage V

CC

= 0V, I

D

= 100A 650 V

I

DSS

Zero-Gate-Voltage Drain Current V

DS

= 560V 250 A

R

DS(ON)

Drain-Source On-State

Resistance

FSQ0565R T

J

= 25C, I

D

= 0.5A 1.76 2.20

FSQ0765R T

J

= 25C, I

D

= 0.5A 1.4 1.6

C

OSS

Output Capacitance

FSQ0565R

V

GS

= 0V, V

DS

= 25V, f = 1MHz

78

pF

FSQ0765R 100

t

d(on)

Turn-On Delay Time

FSQ0565R

V

DD

= 350V, I

D

= 25mA

22

ns

FSQ0765R 25

t

r

Rise Time

FSQ0565R

V

DD

= 350V, I

D

= 25mA

52

ns

FSQ0765R 60

t

d(off)

Turn-Off Delay Time

FSQ0565R

V

DD

= 350V, I

D

= 25mA

95

ns

FSQ0765R 115

t

f

Fall Time

FSQ0565R

V

DD

= 350V, I

D

= 25mA

50

ns

FSQ0765R 65

CONTROL SECTION

t

ON.MAX

Maximum On Time T

J

= 25C 8.8 10.0 11.2 s

t

B

Blanking Time T

J

= 25C, V

sync

= 5V 13.2 15.0 16.8 s

t

W

Detection Time Window T

J

= 25C, V

sync

= 0V 6.0 s

f

S

Initial Switching Frequency 59.6 66.7 75.8 kHz

f

S

Switching Frequency Variation

(9)

-25C < T

J

< 85C 5 10 %

t

AVS

AVS Triggering

Threshold

(9)

On Time

at V

IN

= 240V

DC

, Lm = 360H

(AVS triggered when V

AVS

>spec

& t

AVS

<spec.)

4.0 s

V

AVS

Feedback

Voltage

1.2 V

t

SW

Switching Time Variance by AVS

(9)

Sync = 500kHz sine input

V

FB

= 1.2V, t

ON

= 4.0s

13.5 20.5 s

I

FB

Feedback Source Current V

FB

= 0V 700 900 1100 A

D

MIN

Minimum Duty Cycle V

FB

= 0V 0 %

V

START

UVLO Threshold Voltage

11 12 13 V

V

STOP

After turn-on 7 8 9 V

t

S/S

Internal Soft-Start Time With free-running frequency 17.5 ms

BURST-MODE SECTION

V

BURH

Burst-Mode Voltages

T

J

= 25C, t

PD

= 200ns

(8)

0.45 0.55 0.65 V

V

BURL

0.25 0.35 0.45 V

Hysteresis 200 mV

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 7

Electrical Characteristics (Continued)

T

A

= 25C unless otherwise specified.

Notes:

8. Propagation delay in the control IC.

9. Guaranteed by design; not tested in production.

10. Includes gate turn-on time.

Symbol Parameter Condition Min. Typ. Max. Unit

PROTECTION SECTION

I

LIMIT

Peak Current

Limit

FSQ0565R T

J

= 25C, di/dt = 370mA/s 2.64 3.00 3.36

A

FSQ0765R T

J

= 25C, di/dt = 460mA/s 3.08 3.50 3.92

V

SD

Shutdown Feedback Voltage V

CC

= 15V 5.5 6.0 6.5 V

I

DELAY

Shutdown Delay Current V

FB

= 5V 4 5 6 A

t

LEB

Leading-Edge Blanking Time

(9)

250 ns

t

OSP

Output Short

Protection

(9)

Threshold Time

T

J

= 25C

OSP triggered when t

ON

<t

OSP

,

V

FB

>V

OSP

& lasts longer than

t

OSP_FB

1.2 1.4 s

V

OSP

Threshold Feedback

Voltage

1.8 2.0 V

t

OSP_FB

Feedback Blanking Time 2 2.5 3.0 s

T

SD Thermal

Shutdown

(9)

Shutdown Temperature 125 140 155

C

Hys Hysteresis 60

SYNC SECTION

V

SH1

Sync Threshold Voltage 1 V

CC

= 15V, V

FB

= 2V

1.0 1.2 1.4

V

V

SL1

0.8 1.0 1.2

t

sync

Sync Delay Time

(9)(10)

230 ns

V

SH2

Sync Threshold Voltage 2 V

CC

= 15V, V

FB

= 2V

4.3 4.7 5.1

V

V

SL2

4.0 4.4 4.8

V

CLAMP

Low Clamp Voltage

I

SYNC_MAX

= 800A

I

SYNC_MIN

= 50A

0.0 0.4 0.8 V

V

OVP Over-Voltage

Protection

Threshold Voltage V

CC

= 15V, V

FB

= 2V 7 8 9 V

t

OVP

Blanking Time

(9)

1.0 1.7 2.4 s

TOTAL DEVICE SECTION

I

OP

Operating Supply Current

(Control Part Only)

V

CC

= 13V 1 3 5 mA

I

START

Start Current

V

CC

= 10V

(before V

CC

reaches V

START

)

350 450 550 A

I

CH

Start-up Charging Current

V

CC

= 0V, V

STR

= mininmum

50V

0.65 0.85 1.00 mA

V

STR

Minimum V

STR

Supply Voltage 26 V

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 8

Comparison Between FSDM0x65RNB and FSQ-Series

Function FSDM0x65RE FSQ-Series FSQ-Series Advantages

Operation Method

Constant

Frequency PWM

Quasi-Resonant

Operation

Improved efficiency by valley switching

Reduced EMI noise

Reduced components to detect valley point

EMI Reduction

Frequency

Modulation

Reduce EMI Noise

Valley Switching

Inherent Frequency Modulation

Alternate Valley Switching

Hybrid Control

CCM or AVS

Based on Load

and Input Condition

Improves efficiency by introducing hybrid control

Burst-Mode

Operation

Burst-Mode

Operation

Advanced

Burst-Mode

Operation

Improved standby power by AVS in burst-mode

Strong Protections OLP, OVP

OLP, OVP,

AOCP, OSP

Improved reliability through precise AOCP

Improved reliability through precise OSP

TSD

145

C without

Hysteresis

140C with 60C

Hysteresis

Stable and reliable TSD operation

Converter temperature range

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 9

Typical Performance Characteristics

These characteristic graphs are normalized at T

A

= 25C.

Figure 4. Operating Supply Current (I

OP

) vs. T

A

Figure 5. UVLO Start Threshold Voltage

(V

START

) vs. T

A

Figure 6. UVLO Stop Threshold Voltage

(V

STOP

) vs. T

A

Figure 7. Start-up Charging Current (I

CH

) vs. T

A

Figure 8. Initial Switching Frequency (f

S

) vs. T

A

Figure 9. Maximum On Time (t

ON.MAX

) vs. T

A

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 10

Typical Performance Characteristics (Continued)

These characteristic graphs are normalized at T

A

= 25C.

Figure 10. Blanking Time (t

B

) vs. T

A

Figure 11. Feedback Source Current (I

FB

) vs. T

A

Figure 12. Shutdown Delay Current (I

DELAY

) vs. T

A

Figure 13. Burst-Mode High Threshold Voltage

(V

burh

) vs. T

A

Figure 14. Burst-Mode Low Threshold Voltage

(V

burl

) vs. T

A

Figure 15. Peak Current Limit (I

LIM

) vs. T

A

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 11

Typical Performance Characteristics (Continued)

These characteristic graphs are normalized at T

A

= 25C.

Figure 16. Sync High Threshold Voltage 1

(V

SH1

) vs. T

A

Figure 17. Sync Low Threshold Voltage 1

(V

SL1

) vs. T

A

Figure 18. Shutdown Feedback Voltage (V

SD

) vs. T

A

Figure 19. Over-Voltage Protection (V

OV

) vs. T

A

Figure 20. Sync High Threshold Voltage 2

(V

SH2

) vs. T

A

Figure 21. Sync Low Threshold Voltage 2

(V

SL2

) vs. T

A

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

-25 0 25 50 75 100 125

0.0

0.2

0.4

0.6

0.8

1.0

1.2

N

o

r

m

a

l

i

z

e

d

Temperature [C]

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 12

Functional Description

1. Start-up: At start-up, an internal high-voltage current

source supplies the internal bias and charges the

external capacitor (C

a

) connected to the V

CC

pin, as

illustrated in Figure 22. When V

CC

reaches 12V, the

FPS begins switching and the internal high-voltage

current source is disabled. The FPS continues its normal

switching operation and the power is supplied from the

auxiliary transformer winding unless V

CC

goes below the

stop voltage of 8V.

Figure 22. Start-up Circuit

2. Feedback Control: FPS employs current-mode

control, as shown in Figure 23. An opto-coupler (such as

the FOD817A) and shunt regulator (such as the KA431)

are typically used to implement the feedback network.

Comparing the feedback voltage with the voltage across

the R

sense

resistor makes it possible to control the

switching duty cycle. When the reference pin voltage of

the shunt regulator exceeds the internal reference

voltage of 2.5V, the opto-coupler LED current increases,

pulling down the feedback voltage and reducing the duty

cycle. This typically happens when the input voltage is

increased or the output load is decreased.

2.1 Pulse-by-Pulse Current Limit: Because current-

mode control is employed, the peak current through the

SenseFET is limited by the inverting input of PWM

comparator (V

FB

*), as shown in Figure 23. Assuming

that the 0.9mA current source flows only through the

internal resistor (3R + R = 2.8k), the cathode voltage of

diode D2 is about 2.5V. Since D1 is blocked when the

feedback voltage (V

FB

) exceeds 2.5V, the maximum

voltage of the cathode of D2 is clamped at this voltage,

clamping V

FB

*. Therefore, the peak value of the current

through the SenseFET is limited.

2.2 Leading-Edge Blanking (LEB): At the instant the

internal SenseFET is turned on, a high-current spike

usually occurs through the SenseFET, caused by

primary-side capacitance and secondary-side rectifier

reverse recovery. Excessive voltage across the R

sense

resistor would lead to incorrect feedback operation in the

current-mode PWM control. To counter this effect, the

FPS employs a leading-edge blanking (LEB) circuit. This

circuit inhibits the PWM comparator for a short time

(t

LEB

) after the SenseFET is turned on.

Figure 23. Pulse-Width-Modulation (PWM) Circuit

3. Synchronization: The FSQ-series employs a quasi-

resonant switching technique to minimize the switching

noise and loss. The basic waveforms of the quasi-

resonant converter are shown in Figure 24. To minimize

the MOSFET's switching loss, the MOSFET should be

turned on when the drain voltage reaches its minimum

value, which is indirectly detected by monitoring the V

CC

winding voltage, as shown in Figure 24.

Figure 24. Quasi-Resonant Switching Waveforms

8V/12V

V

ref

Internal

Bias

V

CC V

str

I

CH

V

CC

good

V

DC

C

a

FSQ0765R Rev.00

3 6

4 OSC

V

CC

V

ref

I

delay I

FB

V

SD

R

3R

Gate

driver

OLP

D1 D2

+

V

FB

*

-

V

FB

KA431

C

B

V

O

FOD817A

R

sense

SenseFET

FSQ0765R Rev. 00

V

DC

V

RO

V

RO

V

ds

t

F

1.2V

V

sync

230ns Delay

1.0V

ON ON

V

ovp

(8V)

FSQ0765R Rev.00

MOSFET Gate

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 13

The switching frequency is the combination of blank time

(t

B

) and detection time window (t

W

). In case of a heavy

load, the sync voltage remains flat after t

B

and waits for

valley detection during t

W

. This leads to a low switching

frequency not suitable for heavy loads. To correct this

drawback, additional timing is used. The timing

conditions are described in Figures 25, 26, and 27. When

the V

sync

remains flat higher than 4.4V at the end of t

B

that is t

X

, the next switching cycle starts after internal

delay time from t

X

. In the second case, the next switching

occurs on the valley when the V

sync

goes below 4.4V

within t

B

. Once V

sync

detects the first valley within t

B

, the

other switching cycle follows classical QRC operation.

Figure 25. V

sync

> 4.4V at t

X

Figure 26. V

sync

< 4.4V at t

X

Figure 27. After V

sync

Finds First Valley

4. Protection Circuits: The FSQ-series has several

self-protective functions, such as Overload Protection

(OLP), Abnormal Over-Current Protection (AOCP),

Over-Voltage Protection (OVP), and Thermal Shutdown

(TSD). All the protections are implemented as auto-

restart mode. Once the fault condition is detected,

switching is terminated and the SenseFET remains off.

This causes V

CC

to fall. When V

CC

falls down to the

Under-Voltage Lockout (UVLO) stop voltage of 8V, the

protection is reset and the start-up circuit charges the

V

CC

capacitor. When the V

CC

reaches the start voltage

of 12V, normal operation resumes. If the fault condition is

not removed, the SenseFET remains off and V

CC

drops

to stop voltage again. In this manner, the auto-restart can

alternately enable and disable the switching of the power

SenseFET until the fault condition is eliminated.

Because these protection circuits are fully integrated into

the IC without external components, the reliability is

improved without increasing cost.

Figure 28. Auto Restart Protection Waveforms

t

B

=15s

I

DS

V

DS

V

sync

internal delay

I

DS

4.4V

1.2V

1.0V

t

X

FSQ0765R Rev. 00

t

B

=15s

I

DS

V

DS

V

sync

internal delay

I

DS

4.4V

1.2V

1.0V

t

X

FSQ0765R Rev. 00

t

B

=15s

I

DS

I

DS

V

DS

V

sync

internal delay

4.4V

1.2V

1.0V

ingnore

t

X

FSQ0765R Rev. 00

Fault

situation

8V

12V

V

CC

V

DS

t

Fault

occurs

Fault

removed

Normal

operation

Normal

operation

Power

on

FSQ0765R Rev. 00

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 14

4.1 Overload Protection (OLP): Overload is defined as

the load current exceeding its normal level due to an

unexpected abnormal event. In this situation, the

protection circuit should trigger to protect the SMPS.

However, even when the SMPS is in the normal

operation, the overload protection circuit can be

triggered during the load transition. To avoid this

undesired operation, the overload protection circuit is

designed to trigger only after a specified time to

determine whether it is a transient situation or a true

overload situation. Because of the pulse-by-pulse

current limit capability, the maximum peak current

through the SenseFET is limited, and therefore the

maximum input power is restricted with a given input

voltage. If the output consumes more than this maximum

power, the output voltage (V

O

) decreases below the set

voltage. This reduces the current through the opto-

coupler LED, which also reduces the opto-coupler

transistor current, thus increasing the feedback voltage

(V

FB

). If V

FB

exceeds 2.5V, D1 is blocked and the 5A

current source starts to charge CB slowly up to V

CC

. In

this condition, V

FB

continues increasing until it reaches

6V, when the switching operation is terminated, as

shown in Figure 29. The delay time for shutdown is the

time required to charge C

FB

from 2.5V to 6V with 5A. A

20 ~ 50ms delay time is typical for most applications.

Figure 29. Overload Protection

4.2 Abnormal Over-Current Protection (AOCP): When

the secondary rectifier diodes or the transformer pins are

shorted, a steep current with extremely high di/dt can

flow through the SenseFET during the LEB time. Even

though the FSQ-series has overload protection, it is not

enough to protect the FSQ-series in that abnormal case,

since severe current stress is imposed on the SenseFET

until OLP triggers. The FSQ-series has an internal

AOCP circuit shown in Figure 30. When the gate turn-on

signal is applied to the power SenseFET, the AOCP

block is enabled and monitors the current through the

sensing resistor. The voltage across the resistor is

compared with a preset AOCP level. If the sensing

resistor voltage is greater than the AOCP level, the set

signal is applied to the latch, resulting in the shutdown of

the SMPS.

Figure 30. Abnormal Over-Current Protection

4.3 Output-Short Protection (OSP): If the output is

shorted, steep current with extremely high di/dt can flow

through the SenseFET during the LEB time. Such a

steep current brings high voltage stress on drain of

SenseFET when turned off. To protect the device from

such an abnormal condition, OSP is included in the FSQ-

series. It is comprised of detecting V

FB

and SenseFET

turn-on time. When the V

FB

is higher than 2V and the

SenseFET turn-on time is lower than 1.2s, the FPS

recognizes this condition as an abnormal error and shuts

down PWM switching until V

CC

reaches V

start

again. An

abnormal condition output short is shown in Figure 31.

Figure 31. Output Short Waveforms

4.4 Over-Voltage Protection (OVP): If the secondary-

side feedback circuit malfunctions or a solder defect

causes an opening in the feedback path, the current

through the opto-coupler transistor becomes almost

zero. V

FB

climbs up in a similar manner to the overload

situation, forcing the preset maximum current to be

supplied to the SMPS until the overload protection

triggers. Because more energy than required is provided

to the output, the output voltage may exceed the rated

voltage before the overload protection triggers, resulting

in the breakdown of the devices in the secondary side.

To prevent this situation, an OVP circuit is employed. In

general, the peak voltage of the sync signal is

proportional to the output voltage and the FSQ-series

V

FB

t

2.5V

6.0V

Overload protection

t

12

= C

FB

*(6.0-2.5)/I

delay

t

1

t

2

FSQ0765R Rev.00

2

S

Q

Q

R

OSC

R

3R

GND

Gate

driver

LEB

250ns

PWM

+

-

V

OCP

AOCP

R

sense

FSQ0765R Rev.00

D

MOSFET

Drain

Current

Rectifier

Diode Current

V

FB

V

o

0

0

output short occurs

1.2us

I

o

0

I

LIM

Turn-off delay

Minimum turn-on time

FSQ0765R Rev. 00

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 15

uses a sync signal instead of directly monitoring the

output voltage. If the sync signal exceeds 8V, an OVP is

triggered, shutting down the SMPS. To avoid undesired

triggering of OVP during normal operation, there are two

points considered, as depicted in Figure 32. The peak

voltage of the sync signal should be designed below 6V

and the spike of the SYNC pin must be as low as

possible to avoid getting longer than t

OVP

by decreasing

the leakage inductance shown at V

CC

winding coil.

Figure 32. OVP Triggering

4.5 Thermal Shutdown with Hysteresis (TSD): The

SenseFET and the control IC are built in one package.

This makes it easy for the control IC to detect the

abnormally high temperature of the SenseFET. If the

temperature exceeds approximately 140C, the thermal

shutdown triggers IC shutdown. The IC recovers its

operation when the junction temperature decreases

60C from TSD temperature and V

CC

reaches start-up

voltage (V

start

).

5. Soft-Start: The FPS has an internal soft-start circuit

that increases PWM comparator inverting input voltage

with the SenseFET current slowly after it starts up. The

typical soft-start time is 15ms. The pulse width to the

power switching device is progressively increased to

establish the correct working conditions for transformers,

inductors, and capacitors. The voltage on the output

capacitors is progressively increased with the intention of

smoothly establishing the required output voltage. This

mode helps prevent transformer saturation and reduces

stress on the secondary diode during start-up.

6. Burst Operation: To minimize power dissipation in

standby mode, the FPS enters burst-mode operation. As

the load decreases, the feedback voltage decreases. As

shown in Figure 33, the device automatically enters

burst-mode when the feedback voltage drops below

V

BURL

(350mV). At this point, switching stops and the

output voltages start to drop at a rate dependent on

standby current load. This causes the feedback voltage

to rise. Once it passes V

BURH

(550mV), switching

resumes. The feedback voltage then falls and the

process repeats. Burst-mode operation alternately

enables and disables switching of the power SenseFET,

thereby reducing switching loss in standby mode.

Figure 33. Waveforms of Burst Operation

7. Switching Frequency Limit: To minimize switching

loss and Electromagnetic Interference (EMI), the

MOSFET turns on when the drain voltage reaches its

minimum value in quasi-resonant operation. However,

this causes switching frequency to increases at light load

conditions. As the load decreases or input voltage

increases, the peak drain current diminishes and the

switching frequency increases. This results in severe

switching losses at light-load condition, as well as

intermittent switching and audible noise. These problems

create limitations for the quasi-resonant converter

topology in a wide range of applications.

To overcome these problems, FSQ-series employs a

frequency-limit function, as shown in Figures 34 and 35.

Once the SenseFET is turned on, the next turn-on is

prohibited during the blanking time (t

B

). After the

blanking time, the controller finds the valley within the

detection time window (t

W

) and turns on the MOSFET, as

shown in Figures 34 and Figure 35 (Cases A, B, and C).

V

Vcc_coil

&V

CC

V

sync

V

OVP

(8V)

V

CC

V

Vcc_coil

V

CLAMP

V

SH2

(4.8V)

V

DC

N

pri

N

Vcc

Absolue max V

CC

(20V)

t

OVP

t

OVP

Improper OVP triggering

FSQ0765RRev.00

V

FB

V

DS

0.35V

0.55V

I

DS

V

O

V

O

set

time

Switching

disabled

t1 t2 t3

Switching

disabled

t4

FSQ0765R Rev.00

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 16

If no valley is found during t

W

, the internal SenseFET is

forced to turn on at the end of t

W

(Case D). Therefore,

the devices have a minimum switching frequency of

48kHz and a maximum switching frequency of 67kHz.

Figure 34. QRC Operation with Limited Frequency

8. AVS (Alternating Valley Switching): Due to the

quasi-resonant operation with limited frequency, the

switching frequency varies depending on input voltage,

load transition, and so on. At high input voltage, the

switching on time is relatively small compared to low

input voltage. The input voltage variance is small and the

switching frequency modulation width becomes small. To

improve the EMI performance, AVS is enabled when

input voltage is high and the switching on time is small.

Internally, quasi-resonant operation is divided into two

categories; one is first valley switching and the other is

second-valley switching after blanking time. In AVS, two

successive occurrences of first-valley switching and the

other two successive occurrences of second-valley

switching is alternatively selected to maximize frequency

modulation. As depicted in Figure 35, the switching

frequency hops when the input voltage is high. The

internal timing diagram of AVS is described in Figure 36.

Figure 35. Switching Frequency Range

Figure 36. Alternating Valley Switching (AVS)

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 17

PCB Layout Guide

Due to the combined scheme, FPS shows better noise

immunity than conventional PWM controller and

MOSFET discrete solution. Further more, internal drain

current sense eliminates the possibility of noise

generation caused by a sensing resistor. There are some

recommendations for PCB layout to enhance noise

immunity and suppress natural noise inevitable in power-

handling components.

There are typically two grounds in the conventional

SMPS: power ground and signal ground. The power

ground is the ground for primary input voltage and

power, while the signal ground is ground for PWM

controller. In FPS, those two grounds share the same

pin, GND. Normally the separate grounds do not share

the same trace and meet only at one point, the GND pin.

More, wider patterns for both grounds are good for large

currents by decreasing resistance.

Capacitors at the VCC and FB pins should be as close

as possible to the corresponding pins to avoid noise from

the switching device. Sometimes Mylar or ceramic

capacitors with electrolytic for V

CC

is better for smooth

operation. The ground of these capacitors needs to

connect to the signal ground (not power ground).

The cathode of the snubber diode should be close to the

drain pin to minimize stray inductance. The Y-capacitor

between primary and secondary should be directly

connected to the power ground of DC link to maximize

surge immunity.

Because the voltage range of feedback and sync line is

small, it is affected by the noise of the drain pin. Those

traces should not draw across or close to the drain line.

When the heat sink is connected to the ground, it should

be connected to the power ground. If possible, avoid

using jumper wires for power ground and drain.

Mylar is a registered trademark of DuPont Teijin Films.

Figure 37. Recommended PCB Layout

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 18

Typical Application Circuit

Features

Average efficiency of 25%, 50%, 75%, and 100% load conditions is higher than 80% at universal input

Low standby mode power consumption (<1W at 230V

AC

input and 0.5W load)

Reduce EMI noise through valley switching operation

Enhanced system reliability through various protection functions

Internal soft-start (15ms)

Key Design Notes

The delay time for overload protection is designed to be about 23ms with C105 of 33nF. If faster/slower triggering of

OLP is required, C105 can be changed to a smaller/larger value (e.g. 100nF for 70ms).

The input voltage of V

Sync

must be between 4.7V and 8V just after MOSFET turn-off to guarantee hybrid control and

to avoid OVP triggering during normal operation.

The SMD-type 100nF capacitor must be placed as close as possible to V

CC

pin to avoid malfunction by abrupt pul-

sating noises and to improve surge immunity.

1. Schematic

Figure 38. Demo Circuit of FSQ0565R

Application FPS Device

Input Voltage

Range

Rated Output Power

Output Voltage

(Maximum Current)

LCD Monitor

Power Supply

FSQ0565R 85-265V

AC

46W

5.1V (2.0A)

12V (3.0A)

3

4

C102

150nF

275VAC

LF101

34mH

C101

150nF

275VAC

RT1

5D-9

F1

FUSE

250V

2A

C103

100F

400V

R103

33k

1W

C104

4.7nF

630V

D101

1N 4007

C105

33nF

100V

1

2

3

4

5

T1

EER3016

BD101

2KBP06M3N257

1

2

R101

2M

1W

FSQ0565R

V

str

Vfb

Vcc

Drain

GND

1

2

3

4

6

8

10

D201

MBRF10H100

C201

1000F

25V

C202

1000F

25V

L201

5H

12V, 3A

6

7

D202

MBRF1060

C203

1000F

10V

C204

1000F

10V

L202

5H

5V, 2A

R201

1k

R202

1.2k

R204

4k

R203

1.2k

C205

47nF

R205

4k

C301

4.7nF

1kV

IC301

FOD817A

IC201

KA431

R102

68k

C107

47F

50V

D102

UF 4004 R107

18k

C106

100nF

SMD

R108

12k

Sync

5

R104

20

0.5W

R105

100

0.5W

ZD101

1N4745A

Optional components

FSQ0765R Rev.00

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 19

2. Transformer

Figure 39. Transformer Schematic Diagram of FSQ0565R

3. Winding Specification

4. Electrical Characteristics

5. Core & Bobbin

Core: EER3016 (Ae=109.7mm

2

)

Bobbin: EER3016

Position No Pin (sf) Wire Turns Winding Method

Top Insulation: Polyester Tape t = 0.025mm, 4 Layers

N

p

/2 2 1 0.4 1 20 2-Layer Solenoid Winding

Insulation: Polyester Tape t = 0.025mm, 2 Layers

N

12V

/2 9 8 0.5 2(TIW) 4 Center Solenoid Winding

Insulation: Polyester Tape t = 0.025mm, 2 Layers

N

a

4 5 0.15 1 10 Center Solenoid Winding

Insulation: Polyester Tape t = 0.025mm, 2 Layers

N

5V

7 6 0.5 2(TIW) 4 Center Solenoid Winding

Insulation: Polyester Tape t = 0.025mm, 2 Layers

N

12V

/2 10 9 0.5 2(TIW) 5 Center Solenoid Winding

Insulation: Polyester Tape t = 0.025mm, 2 Layers

Bottom N

p

/2 3 2 0.4 1 32 2-Layer Solenoid Winding

Pin Specification Remarks

Inductance 1 - 3 360H 10% 100kHz, 1V

Leakage 1 - 3 15H Maximum Short all other pins

EER3016

N

p

/2

N

12V

/2

N

a

1

2

3

4

5 6

7

8

9

10

N

p

/2

N

5V

N

12V

/2

FSQ0765R Rev.00

10

Lp/2

(0.4)

TAPE 1T

3

2

2

Bottom of bobbin

10 9 9

TAPE 2T

TAPE 2T

L12V/2

(TIW 0.5,

2parallel)

7 7 6 6

L5V

(TIW 0.5,

2parallel)

TAPE 2T

4 5

TAPE 2T

9 9 8 8

L12V/2

(TIW 0.5,

2parallel)

TAPE 2T

TAPE 1T

1

Lp/2

(0.4)

LVcc(0.2)

TAPE 4T

FSQ0765R Rev.00

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 20

6. Demo Board Part List

Part Value Note Part Value Note

Resistor C205 47nF/50V Ceramic Capacitor

R101 2M 1W C301 4.7nF/1kV Ceramic Capacitor

R102 68k 1/2W Inductor

R103 33k 1W L201 5H 5A Rating

R104 20 1W L202 5H 5A Rating

R105 100 optional, 1/4W Diode

R107 18k 1/4W D101 IN4007

1A, 1000V General-Purpose

Rectifier

R108 12k 1/4W D102 UF4004 1A, 400V Ultrafast Rectifier

R201 1k 1/4W ZD101 1N4745A

1W 16V Zener Diode

(optional)

R202 1.2k 1/4W D201 MBRF10H100 10A,100V Schottky Rectifier

R203 1.2k 1/4W D202 MBRF1060 10A,60V Schottky Rectifier

R204 5.2k 1/4W IC

R205 4.7k 1/4W IC101 FSQ0565R FPS

Capacitor IC201 KA431 (TL431) Voltage Reference

C101 150nF/275V

AC

Box Capacitor IC202 FOD817A Opto-Coupler

C102 150nF/275V

AC

Box Capacitor Fuse

C103 100F/400V Electrolytic Capacitor Fuse 2A/250V

C104 4.7nF/630V Film Capacitor NTC

C105 33nF/50V Ceramic Capacitor RT101 5D-9

C106 100nF/50V SMD (1206) Bridge Diode

C107 47F/50V Electrolytic Capacitor BD101 2KBP06M2N257 Bridge Diode

C201 1000F/25V

Low ESR Electrolytic

Capacitor

Line Filter

C202 1000F/25V

Low ESR Electrolytic

Capacitor

LF101 34mH

C203 1000F/10V

Low ESR Electrolytic

Capacitor

Transformer

C204 1000F/10V

Low ESR Electrolytic

Capacitor

T1 EER3016 Ae=109.7mm

2

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 21

Package Dimensions

TO-220F-6L (Forming)

Figure 40. 6-Lead, TO-220 Package

MKT-TO220A06revB

TRADEMARKS

The following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use and is not

intended to be an exhaustive list of all such trademarks.

ACEx

Build it Now

CorePLUS

CROSSVOLT

CTL

Current Transfer Logic

EcoSPARK

Fairchild

Fairchild Semiconductor

FACT Quiet Series

FACT

FAST

FastvCore

FPS

FRFET

Global Power Resource

SM

Green FPS

Green FPS e-Series

GTO

i-Lo

IntelliMAX

ISOPLANAR

MegaBuck

MICROCOUPLER

MicroFET

MicroPak

MillerDrive

Motion-SPM

OPTOLOGIC

OPTOPLANAR

PDP-SPM

Power220

Power247

POWEREDGE

Power-SPM

PowerTrench

Programmable Active Droop

QFET

QS

QT Optoelectronics

Quiet Series

RapidConfigure

SMART START

SPM

STEALTH

SuperFET

SuperSOT-3

SuperSOT-6

SuperSOT-8

SyncFET

The Power Franchise

TinyBoost

TinyBuck

TinyLogic

TINYOPTO

TinyPower

TinyPWM

TinyWire

SerDes

UHC

UniFET

VCX

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS

HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE

APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS

PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILDS

WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body or

(b) support or sustain life, and (c) whose failure to perform

when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to

result in a significant injury of the user.

2. A critical component in any component of a life support,

device, or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In Design This datasheet contains the design specifications for product

development. Specifications may change in any manner without notice.

Preliminary First Production This datasheet contains preliminary data; supplementary data will be

published at a later date. Fairchild Semiconductor reserves the right to

make changes at any time without notice to improve design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild Semiconductor

reserves the right to make changes at any time without notice to improve

design.

Obsolete Not In Production This datasheet contains specifications on a product that has been

discontinued by Fairchild Semiconductor. The datasheet is printed for

reference information only.

Rev. I31

F

S

Q

0

5

6

5

R

,

F

S

Q

0

7

6

5

R

G

r

e

e

n

-

M

o

d

e

F

a

r

i

c

h

i

l

d

P

o

w

e

r

S

w

i

t

c

h

(

F

P

S

)

f

o

r

Q

u

a

s

i

-

R

e

s

o

n

a

n

t

O

p

e

r

a

t

i

o

n

2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0565R, FSQ0765R Rev. 1.0.0 22

All Datasheets Cannot Be Modified Without Permission

Copyright Each Manufacturing Company

This datasheet has been downloaded from:

www.EEworld.com.cn

Free Download

Daily Updated Database

100% Free Datasheet Search Site

100% Free IC Replacement Search Site

Convenient Electronic Dictionary

Fast Search System

www.EEworld.com.cn

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- FSQ311Document24 pagesFSQ311zektorNo ratings yet

- 8 Pin Ic - FSQ510Document15 pages8 Pin Ic - FSQ510Raja Pathamuthu.GNo ratings yet

- FSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument12 pagesFSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionJohan BeckersNo ratings yet

- Data SheetDocument44 pagesData SheetKendje MatsumotoNo ratings yet

- DM0565Document21 pagesDM0565Tammy WashingtonNo ratings yet

- Datasheet PDFDocument45 pagesDatasheet PDFSonidos SotoNo ratings yet

- FAN6755WDocument17 pagesFAN6755WAndres AlegriaNo ratings yet

- 2N5951 N-Channel RF Amplifier: Absolute Maximum RatingsDocument3 pages2N5951 N-Channel RF Amplifier: Absolute Maximum RatingsMarving Velásquez RivasNo ratings yet

- FSFR1800Document17 pagesFSFR1800sontuyet82No ratings yet

- IC-ON-LINE - CN dm0465r 44841Document20 pagesIC-ON-LINE - CN dm0465r 44841ubhagavanNo ratings yet

- CQ0765RT DatasheetDocument24 pagesCQ0765RT DatasheetSergio Daniel BarretoNo ratings yet

- DNP015 Fairchild SemiconductorDocument13 pagesDNP015 Fairchild SemiconductorIvan InqognitoNo ratings yet

- 1565 RTDocument24 pages1565 RTJose Samuel Robelto RNo ratings yet

- Data SheetDocument7 pagesData SheetOvi PanteaNo ratings yet

- CQ 0765RTDocument24 pagesCQ 0765RTsonivitel100% (2)

- ACPI Regulator/Controller For Dual Channel DDR Memory Systems FeaturesDocument15 pagesACPI Regulator/Controller For Dual Channel DDR Memory Systems FeaturesnakameiyoNo ratings yet

- A6251m PDFDocument7 pagesA6251m PDFYudi ElektroNo ratings yet

- FSDH0265RN, FSDM0265RN: Green Mode Fairchild Power Switch (FPS)Document20 pagesFSDH0265RN, FSDM0265RN: Green Mode Fairchild Power Switch (FPS)Wsad WsadNo ratings yet

- FSFR1700XSLDocument14 pagesFSFR1700XSLАлександр АндриановNo ratings yet

- ssc9503 10 12Document2 pagesssc9503 10 12tecnologo456No ratings yet

- ELECTRONICDocument13 pagesELECTRONICMahmoued YasinNo ratings yet

- STR S5707Document8 pagesSTR S5707lllllll7No ratings yet

- 12 Volt Smps Circuit DiagramDocument7 pages12 Volt Smps Circuit DiagramAnura MaddumageNo ratings yet

- Viper 100Document8 pagesViper 100SeanNo ratings yet

- Fan 7316Document21 pagesFan 7316sontuyet82No ratings yet

- FSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationDocument22 pagesFSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationSilvio SchwanckNo ratings yet

- IC-ON-LINE - CN dm0365r 44840Document20 pagesIC-ON-LINE - CN dm0365r 44840MoscandoNo ratings yet

- NCP 43080Document36 pagesNCP 43080TestronicpartsNo ratings yet

- DM 0565 RDocument20 pagesDM 0565 R81968No ratings yet

- Fsdm0465re Fsdm0565re Fsdm07652reDocument20 pagesFsdm0465re Fsdm0565re Fsdm07652rejesus cautivoNo ratings yet

- STRG6653Document8 pagesSTRG6653perro sNo ratings yet

- STR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsDocument7 pagesSTR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsVidal VelasquezNo ratings yet

- Fan 7530Document20 pagesFan 7530aldo_suviNo ratings yet

- CQ1565Document24 pagesCQ1565liberthNo ratings yet

- NCP1337 D PDFDocument15 pagesNCP1337 D PDFBoKi PoKiNo ratings yet

- J13009Document6 pagesJ13009gayamartNo ratings yet

- STR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsDocument7 pagesSTR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsmilebaleNo ratings yet

- STRW6754Document9 pagesSTRW6754electronicaliderNo ratings yet

- FSCQ-Series FSCQ0565RT/FSCQ0765RT/FSCQ0965RT/FSCQ1265RT/ FSCQ1465RT/FSCQ1565RT/FSCQ1565RP Green Mode Fairchild Power Switch (FPS™)Document45 pagesFSCQ-Series FSCQ0565RT/FSCQ0765RT/FSCQ0965RT/FSCQ1265RT/ FSCQ1465RT/FSCQ1565RT/FSCQ1565RP Green Mode Fairchild Power Switch (FPS™)alamgir80100% (2)

- DatasheetDocument13 pagesDatasheetebertecnicoNo ratings yet

- Fan 7711Document21 pagesFan 7711uumpNo ratings yet

- FAN7535 PFC & Ballast Control IC: Features DescriptionDocument12 pagesFAN7535 PFC & Ballast Control IC: Features Descriptionashish_rewaNo ratings yet

- STR W6735 DatasheetDocument13 pagesSTR W6735 DatasheetloagerNo ratings yet

- Data Sheet: Greenchip Smps Control IcDocument20 pagesData Sheet: Greenchip Smps Control IcMiloud ChouguiNo ratings yet

- Bias Power Supply For TV and Monitor TFT LCD Panels: FeaturesDocument30 pagesBias Power Supply For TV and Monitor TFT LCD Panels: Featureseduinggv1829No ratings yet

- FSQ321 D 1810228Document23 pagesFSQ321 D 1810228Donchon chungNo ratings yet

- STR W6000S Series Application NoteDocument20 pagesSTR W6000S Series Application NoteSutrisno OkNo ratings yet

- UCI224F - Technical Data SheetDocument8 pagesUCI224F - Technical Data Sheet3efooNo ratings yet

- Ap5002 - PWM Control 2a Step-Down ConverterDocument10 pagesAp5002 - PWM Control 2a Step-Down ConverterAmador Garcia IIINo ratings yet

- Fan 7361Document9 pagesFan 7361Odalis CabaNo ratings yet

- FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationDocument19 pagesFSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationPaulo Roberto s freireNo ratings yet

- HP 450 OptocouplerDocument16 pagesHP 450 Optocoupler1cvbnmNo ratings yet

- HV9910BDB7 HV9910B PFC 40W LED Driver Demoboard: Specifications General DescriptionDocument5 pagesHV9910BDB7 HV9910B PFC 40W LED Driver Demoboard: Specifications General DescriptionNT372No ratings yet

- FAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorDocument17 pagesFAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorVijay MistryNo ratings yet

- Feature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerDocument11 pagesFeature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerEnéas BaroneNo ratings yet

- LD7750 High-Voltage PWM ControllerDocument20 pagesLD7750 High-Voltage PWM ControllerAndres Alegria100% (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- V260B3 P01 ChimeiDocument26 pagesV260B3 P01 Chimeisontuyet82No ratings yet

- Karaoke Circuit Building InstructionsDocument10 pagesKaraoke Circuit Building Instructionssontuyet82No ratings yet

- 239716035Document25 pages239716035sontuyet82No ratings yet

- Cobra PWR Mic HG m75 FixDocument7 pagesCobra PWR Mic HG m75 FixJonathan_McNee_6601No ratings yet

- DV29 Service Manual Issue 1 PDFDocument48 pagesDV29 Service Manual Issue 1 PDFZbigniew SzaryczNo ratings yet

- Prology HDTV 707sDocument1 pagePrology HDTV 707ssontuyet82No ratings yet

- T.VST29.03 4Document13 pagesT.VST29.03 4Sutrisno Ok100% (1)

- Nd-La MV9 P-2 PDFDocument10 pagesNd-La MV9 P-2 PDFMakhtar SeyeNo ratings yet

- Technical Data & Service Manual: Indoor Unit: As52AlDocument31 pagesTechnical Data & Service Manual: Indoor Unit: As52Alsontuyet82No ratings yet

- 1bb5a8ec83aa3bae772867cdfc2752fdDocument8 pages1bb5a8ec83aa3bae772867cdfc2752fdsontuyet82No ratings yet

- PD70201EVB25Fx UG Rev 2.0Document34 pagesPD70201EVB25Fx UG Rev 2.0sontuyet82No ratings yet

- Deflection YokeDocument2 pagesDeflection Yokesontuyet82No ratings yet

- 10 Auxiliary Power Supply Minglik PL21Document29 pages10 Auxiliary Power Supply Minglik PL21sontuyet82No ratings yet

- NN Se992s NN Sd982s NN St962s Panasonic 1680Document38 pagesNN Se992s NN Sd982s NN St962s Panasonic 1680sontuyet82No ratings yet

- Mitsubishi Special Price Spares List 161111Document8 pagesMitsubishi Special Price Spares List 161111sontuyet82No ratings yet

- IC-ON-LINE - CN Upd789188 493111Document9 pagesIC-ON-LINE - CN Upd789188 493111sontuyet82No ratings yet

- E-07-09-12-15 Hkew-3Document95 pagesE-07-09-12-15 Hkew-3sontuyet82No ratings yet

- PROIND Brand SchematicsDocument56 pagesPROIND Brand Schematicssontuyet82No ratings yet