Professional Documents

Culture Documents

Characterization of RF Power BJT and Improvement of Thermal Stability With Nonlinear Base Ballasting

Uploaded by

sushil4056Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Characterization of RF Power BJT and Improvement of Thermal Stability With Nonlinear Base Ballasting

Uploaded by

sushil4056Copyright:

Available Formats

1428

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 33, NO. 9, SEPTEMBER 1998

Characterization of RF Power BJT and Improvement of Thermal Stability with Nonlinear Base Ballasting

Jaejune Jang, Student Member, IEEE, Edwin C. Kan, Member, IEEE, Torkel Arnborg, Senior Member, IEEE, Ted Johansson, Senior Member, IEEE, and Robert W. Dutton, Fellow, IEEE

Abstract A novel base ballasting scheme for interdigitated power RF bipolar transistors has demonstrated improved performance and thermal stability. The nonlinear ballast resistor in series with each base nger is implemented using a depletion-mode FET, which requires only minor modication in the fabrication process. Mixed-mode simulation, instead of analytical equations, is used for more accurate device characterization. Index Terms Ballasting, parasitic characterization, power BJT.

I. INTRODUCTION HE positive feedback from inhomogeneous temperature distributions in interdigitated power bipolar transistors can cause thermal instability or gain collapse [1], [2]. Usually emitter ballast resistor is used for prevention, and its optimal value needs to be carefully chosen to ensure good instability protection without severe performance degradation [3]. The design of nger spacing is also a tradeoff in view of thermal management, since its reduction can increase thermal coupling between ngers and hence decrease the current hogging effect [4], [5], but this reduction will lead to inefcient head dissipation for the entire cell [5]. We propose to use a new nonlinear base ballasting scheme that is very effective in thermal instability protection with little performance penalty at normal operating conditions. Since the positive feedback from Joule heating can be nearly eliminated, the layout design can also be more aggressive toward handling total heat dissipation. II. POWER RF DEVICE MODELING Power RF devices pose signicant challenges to modeling strategies, since both thermal and parasitic effects need to be accurately accounted for. For the power bipolar junction transistor (BJT) in this study (Fig. 1), mixed-mode device/circuit simulation which interfaces Stanfords device simulator PISCES and University of California at Berkeleys circuit simulator SPICE-3f2 has been demonstrated as an effective method to model the parasitic elements and to link the detailed doping proles directly with circuit performance [6]. For devices which are fabricated on a monolithic substrate, the circuit often exhibits parasitic behavior due to elements that can be represented by a two-port network conguration as shown in Fig. 2. This T-like topology has been used

Manuscript received January 2, 1998; revised May 21, 1998. J. Jang and R. W. Dutton are with Stanford University, Stanford, CA 943054075 USA. E. C. Kan is with Cornell University, Ithaca, NY 14850 USA. T. Arnborg and T. Johansson are with Ericsson Components AB, Kista S164 81 Sweden. Publisher Item Identier S 0018-9200(98)05874-0.

Fig. 1. Modeled RF BJT layout and T-network for parasitic characterization.

Fig. 2. Modeled T-network for RF BJT.

successfully by many authors [8], [9]. For this network it is assumed that over the frequency range of concern (from 300 MHz to 3 GHz) the equivalent circuit composed of lumped RLC elements, can be described using general interconnect parasitics. In reality, at high frequencies the interconnect circuit parameters such as resistance may vary with frequency, due to skin and other distributive effects. For the frequency range considered here, however, frequency-independent modeling parameters are usually sufcient. As shown in Fig. 3, construction of the two-port matrices from the inner shell to the outer one or vice versa is straight, , , and are forward. The extracted parasitics of as below [6].

00189200/98$10.00 1998 IEEE

JANG et al.: IMPROVED THERMAL STABILITY WITH NONLINEAR BASE BALLASTING

1429

TABLE I EXTRACTED PARASITIC VALUES FOR T-NETWORK USING MIXED-MODE SIMULATION

Fig. 3. Inclusion of extrinsic parasitics. The center box represents a intrinsic RF BJT which is modeled with device simulator. Fig. 5. Comparison between measurement and simulation for IC versus fT and S -parameters.

Fig. 4. Fitted Gummel plots using mixed-mode device simulation. Mobility and lifetime are calibrated.

Where parameters

, and

are measured

Fig. 6. Gummel plots of a unit cell (a base nger and a emitter nger) with various temperature. IB and IC increase as TL increases.

det

and det

Thus by comparing measured parameters and the simulated , , , and ), extrinsic parintrinsic parameters ( , , and ) can be obtained. Unlike asitics values ( , analytical approaches [3][5], the numerical method can capture detailed transistor behaviors and electrical couplings with no operation-mode assumption, and hence has a broader range of applicability. Calibrated Gummel plots to measurements at room temperature are shown in Fig. 4. The measured SRP doping prole is also used for calibration. Extracted values of the parasitic elements are listed in Table I [6]. The emitter per nger implemented ballast resistance is about 110 as a function of using a p-type diffusion resistor. The and the -parameters are shown in the collector current Fig. 5. There is quite good agreement between measurements and simulation.

1430

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 33, NO. 9, SEPTEMBER 1998

Fig. 10. Percentage difference in IC (hot nger) compared with IC (cold nger @ T = 300 K). Fig. 7. Circuit diagram for depletion-mode FET. Each base nger is connected to an FET.

Fig. 8. ID and VDS characteristics at various temperatures. The operating point should be chosen close to (maximum protection) or below (maximum linearity) the onset of saturating region.

Fig. 11. Transition frequency (fT ) versus total IC . BJT with depletion-mode MOSFET has higher fT (@ VCE = 5 V, and T = 307 K).

Fig. 9. Gummel plot for BJT with depletion mode MOSFET. IB and IC are effectively limited by MOSFET at high current level.

Fig. 12. S -parameter comparison between BJT with depletion-mode ballasting and BJT with emitter ballasting.

JANG et al.: IMPROVED THERMAL STABILITY WITH NONLINEAR BASE BALLASTING

1431

(a) Fig. 13.

(b)

Gummel plot for (a) HBT with emitter resistor and (b) HBT with depletion-mode base ballasting at various temperatures.

III. NONLINEAR BASE BALLASTING It is apparent that a nonlinear ballast resistor will be superior to a linear one, since optimal effective resistance values can be separately designed for operating conditions and instability protection. If the ballast resistor is applied to the base end [5], [7], the equivalent resistance can be obtained by multiplying the emitter resistance with the dc current gain. Although it was argued in [7] that base ballasting can only work for heterojunction bipolar transistor (HBT), not BJT, since current for BJT, a more careful gain increases with temperature analysis in Fig. 6 reveals that the base current still increases , though not as fast as . Therefore, base ballasting with can still prevent thermal instability in the BJT, just not as effective as emitter ballasting if the equivalent value is used. A nonlinear emitter ballasting is difcult to implement owing value and limited area. With a nonlinear to its small base resistor implemented by a depletion-mode MOSFET as shown in Figs. 7 and 8, the saturation region of MOSFET will effectively limit the current through hot ngers, while the linear region will hardly affect the normal operating point of cold ngers. The MOSFET has a channel length and width

of 3 and 15 m, and a threshold voltage of 0.45 V. The dimensions of the depletion-mode FET is determined level for optimal circuit performance by setting proper and instability protection. Other layouts or devices are also applicable as long as the nonlinear resistance values are chosen appropriately (i.e., an enhancement-mode MOSFET with gate ). Fig. 9 shows improved temperature depenconnected to dence of the Gummel plot by using the nonlinear ballasting scheme. Different ballasting schemes are compared in Fig. 10 in view of instability protection. Due to increased effective of nonlinear ballasting scheme, higher is resulted as shown in Fig. 11. All coupling capacitances have been taken into account. -parameters with different ballasting scheme is also compared for high frequency characteristics as shown in Fig. 12. It can be seen that the new ballast scheme is strongly favorable to the conventional emitter ballasting. IV. HBT APPLICATIONS The proposed ballast scheme can possibly be applied to power HBT applications, too. The nonlinear resistor can be obtained by MESFET, although more difcult modication

1432

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 33, NO. 9, SEPTEMBER 1998

on fabrication is likely. A computational prototype through mixed-mode simulation is built for illustration. The HBT device follows the specication in [7] and the MESFET has a gate length and width of 2 and 5 m and a threshold voltage of 0.3 V. As shown in Fig. 13, base ballasting using depletionmode FET is more efcient in HBT due to decreasing current . With proper operating condition, the gain with increasing of HBT does not experience current gain collapse since as the hot nger increases, collector current decreases due to base does not current is effectively limited by MESFET so that increase anymore as illustrated in Fig. 10. V. CONCLUSION A new methodology of parasitic extraction and a novel base ballasting scheme for RF power bipolar transistors have been described in this paper. The nonlinear ballast resistor in series with each base nger is implemented using a depletionmode FET, which prevents from inhomogeneous temperature distribution without sacricing performance of the power device. REFERENCES

[1] R. H. Winkler, Thermal properties of high-power transistors, IEEE Trans. Electron Devices, vol. 14, pp. 260264, 1967. [2] W. Liu, S. Nelson, D. Hill, and A. Khatibzadeh, Current gain collapse in microwave multi-nger heterojunction transistors operated at very high power density, IEEE Trans. Electron Devices, vol. 40, pp. 19171927, 1993. [3] G. Gao, M. S. Unlu, H. Morkoc, and D. L. Blackburn, Emitter ballasting resistor design for, and current handling capability of AlGaAs/GaAs power heterojunction bipolar transistors, IEEE Trans. Electron Devices, vol. 38, pp. 185196, 1991. [4] W. Liu, Thermal management to avoid the collapse of current gain in power heterojunction bipolar transistors, in GaAs IC Symp. Tech. Dig., 1995, pp. 147150. [5] L. L. Liou and B. Bayraktaroglu, Thermal stability analysis of AlGaAs/GaAs heterojunction bipolar transistors with multiple emitter ngers, IEEE Trans. Electron Devices, vol. 41, pp. 629636, 1994. [6] J. Jang, E. C. Kan, L. So, R. W. Dutton, T. Johansson, and T. Arnborg, Parasitic characterization of radio-frequency (RF) circuit using mixedmode simulation, in Proc. CICC, 1996, pp. 445448. [7] W. Liu, A. Khatibzadeh, J. Sweder, and H. Chau, The use of base ballasting to prevent the collapse of current gain in AlGaAs/GaAs heterojunction bipolar transistors, IEEE Trans. Electron Devices, vol. 43, pp. 245251, 1996. [8] R. Ramachandran et al., A high efciency HBT MMIC power amplier, in Proc. GaAs IC Symp., 1990, vol. 22, pp. 357360. [9] U. Schaper and B. Holzap, Analytical parameter extraction of the HBT equivalent circuit with T-like topology from measured S parameters, IEEE Trans. Microwave Theory Tech., vol. 43, pp. 493498, 1995.

Edwin C. Kan (S86M90) received the B.S. degree from National Taiwan University in 1984 and the M.S. and Ph.D. degrees from University of Illinois at Urbana-Champaign in 1988 and 1992, respectively, all in electrical engineering. From 1984 to 1986, he served as a Second Lieutenant in the Air Force, Taiwan, ROC. In January 1992, he joined Dawn Technologies as the principal developer of advanced electronic and optical device simulators and technology CAD framework. He has been with Stanford University, Stanford, CA, as a Research Associate since October 1993. He joined Cornell University, Ithaca, NY, in July 1997 as an Assistant Professor of School of Electrical Engineering. His main research areas include VLSI technology, semiconductor device physics, composite CAD development, and numerical methods of PDE and ODE.

Torkel Arnborg (S78M79SM94) was born on January 9, 1947. He received the M.Sc. degree in 1970 and the Ph.D. degree in 1982 from the Royal Institute of Technology, Stockholm, Sweden. From 1970 to 1975, he taught analog and digital circuits. His thesis work was on MOS modeling and two-dimensional analysis of semiconductor devices using nite element methods. He joined the process development laboratory at Ericsson Components, Kista, Sweden, in 1983 and worked with applications in smart power, HVIC, VLSI, and optoelectronics for silicon and IIIV materials. During 19901991, he was a Visiting Researcher at Texas Instruments Incorporated, Dallas, working with models and scaling methods for future BiCMOS technologies. In 1993, he joined the Ericsson Microelectronics Research Center. From 19961997, he was a Visiting Scientist at the Center for Integrated Systems, Stanford University, as a Wallenberg stipend receiver. His present interests include RF modeling and new technology simulation techniques useful for telecommunication applications.

Ted Johansson (M90SM96) was born on September 20, 1959. He received the M.Sc. degree in applied physics and electrical engineering in 1985 and the Dr.Tech. and Ph.D. degrees in electronic devices from Link oping Institute of Technology, Sweden, in 1993 and 1998, respectively. From 1985 to 1989, he worked at Swedish Institute of Microwave Technology/Microelectronics in Stockholm and Kista, doing research in the area of MOS process technology. He joined Ericsson Component AB in 1989 when the development of RF power transistors for cellular base stations started and is presently Project Manager for the next bipolar RF power process generation at Ericssons semiconductor fab in Kista, Sweden. He has published more than 25 journal and conference papers, holds four patents and has another seven patent applications pending. His research interests include RF related areas on device level, including fabrication and simulations of new device structures.

Jaejune Jang (S93) received the B.S. and M.S. degrees in electrical engineering from the Michigan State University and Stanford University, in 1993 and 1995, respectively. He is currently a graduate student in the Electrical Engineering Department of Stanford University, Stanford, CA. His interests are in RF power device design.

Robert W. Dutton (S67M70SM80F84) received the B.S., M.S., and Ph.D. degrees from the University of California, Berkeley, in 1966, 1967, and 1970, respectively. He is Professor of Electrical Engineering at Stanford University, Stanford, CA, and Director of Research in the Center for Integrated Systems. He has held summer staff positions at Fairchild, Bell Telephone Laboratories, Hewlett-Packard, IBM Research, and Matsushita during 1967, 1973, 1975, 1977, and 1988, respectively. His research interests focus on integrated circuit process, device, and circuit technologiesespecially the use of computer-aided design (CAD) and parallel computational methods. He has published more than 200 journal articles and graduated more than four dozen doctorate students. Dr. Dutton was Editor of the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS (19841986), winner of the 1987 IEEE J. J. Ebers Award, the 1988 Guggenheim Fellowship to study in Japan, and was elected to the National Academy of Engineering in 1991. In December 1996, he received the Jack A. Morton Award for his seminal contributions to semiconductor process and device modeling.

You might also like

- Koneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringDocument15 pagesKoneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringLakshmi JagupillaNo ratings yet

- Apec 2012 LakshmiDocument6 pagesApec 2012 Lakshminourtal2013No ratings yet

- Latest Technology PT Igbts vs. Power Mosfets: Application Note Apt0302 Rev. A April 4, 2003Document6 pagesLatest Technology PT Igbts vs. Power Mosfets: Application Note Apt0302 Rev. A April 4, 2003Jyothsna VayyalaNo ratings yet

- Bahl 2015Document7 pagesBahl 2015Vĩnh Khoa NgôNo ratings yet

- MOSFET in SMPS High Frequency Application: A New SMPS Non Punch Thru IGBT ReplacesDocument5 pagesMOSFET in SMPS High Frequency Application: A New SMPS Non Punch Thru IGBT ReplacesAdil ButtNo ratings yet

- Hyper FETDocument7 pagesHyper FETScurdNo ratings yet

- Application Note AN-983: IGBT CharacteristicsDocument16 pagesApplication Note AN-983: IGBT Characteristicswizardgrt1No ratings yet

- Baliga Figure of MeritDocument3 pagesBaliga Figure of MeritKyle BotheNo ratings yet

- Recent Trends in IGBT TechnologyDocument3 pagesRecent Trends in IGBT TechnologyRichard TsengNo ratings yet

- Low Voltage Smart Temperature Sensor Front End: Abstract-In This Brief, A Low Voltage Low Power CMOSDocument5 pagesLow Voltage Smart Temperature Sensor Front End: Abstract-In This Brief, A Low Voltage Low Power CMOSBruno SilvaNo ratings yet

- PDFDocument4 pagesPDFDivanshu ChaturvediNo ratings yet

- 158 - MWWTL - July2002 AcikelDocument3 pages158 - MWWTL - July2002 Acikel23010301042No ratings yet

- A Practical SPICE Model SET PDFDocument7 pagesA Practical SPICE Model SET PDFBeatriz PêsNo ratings yet

- Active voltage sharing controls IGBTs in seriesDocument8 pagesActive voltage sharing controls IGBTs in seriesOsman T.No ratings yet

- Circuit Design Techniques for Linear Integrated CircuitsDocument5 pagesCircuit Design Techniques for Linear Integrated CircuitsNoita EnolaNo ratings yet

- 2007 IEEE International Symposium on Integrated Circuits Low Voltage Sub-1V CMOS BandgapDocument3 pages2007 IEEE International Symposium on Integrated Circuits Low Voltage Sub-1V CMOS Bandgapanugrajiv5898No ratings yet

- 325 Lab 8 ReportDocument10 pages325 Lab 8 Reportapi-241454978No ratings yet

- Estimation and Measurement of Junction Temperatures in A Three-Level Voltage Source ConverterDocument10 pagesEstimation and Measurement of Junction Temperatures in A Three-Level Voltage Source ConverterCharles KellyNo ratings yet

- Infineon - AN2008-03 - Thermal Equivalent Circuit ModelsDocument0 pagesInfineon - AN2008-03 - Thermal Equivalent Circuit ModelsSofiaArmenterosNo ratings yet

- Igbt Spice ModelingDocument43 pagesIgbt Spice ModelingBrian WillardNo ratings yet

- Study of Impulse Voltage Distribution in Transformer WindingsDocument5 pagesStudy of Impulse Voltage Distribution in Transformer WindingsBhuvanes Waran100% (1)

- RF Linear Power Amplifier Gain Stabilization Over Ambient TemperatureDocument7 pagesRF Linear Power Amplifier Gain Stabilization Over Ambient Temperaturejagarov4954No ratings yet

- A Resistorless CMOS Voltage Reference Based On Mutual Compensation of andDocument5 pagesA Resistorless CMOS Voltage Reference Based On Mutual Compensation of andSteven Curly ComalingNo ratings yet

- EncoderDocument8 pagesEncodersamactrangNo ratings yet

- Calculation and Analysis of IGBT Power Loss in Drive System For EVDocument2 pagesCalculation and Analysis of IGBT Power Loss in Drive System For EVDaniel Labiano AnduezaNo ratings yet

- A Curvature Compensated CMOS Bandgap Voltage ReferenceDocument4 pagesA Curvature Compensated CMOS Bandgap Voltage ReferenceMuhammad_Swilam_2010No ratings yet

- Ieee Bakker 1996Document5 pagesIeee Bakker 1996kurabyqldNo ratings yet

- Multidisciplinary Research: EPRA International Journal ofDocument7 pagesMultidisciplinary Research: EPRA International Journal ofAnand Parakkat ParambilNo ratings yet

- Static Synchronous Series Compensator Using ADocument4 pagesStatic Synchronous Series Compensator Using ASai Bhargav VeerabathiniNo ratings yet

- Flyback ConverterDocument9 pagesFlyback ConverterRaul Rosa100% (1)

- Supplementary Info: A Brief Overview of TransistorsDocument6 pagesSupplementary Info: A Brief Overview of TransistorsJoey Joe Joe Junior ShabadooNo ratings yet

- Bandgap ReferenceDocument9 pagesBandgap Referencerammanu0289No ratings yet

- Chandra KasanDocument9 pagesChandra KasanKumudu GamageNo ratings yet

- Monolithic Bidirectional Switch Based On GaN Gate Injection TransistorsDocument6 pagesMonolithic Bidirectional Switch Based On GaN Gate Injection TransistorsVenkatesan SwamyNo ratings yet

- High Voltage Pulser With A Fast Fall-Time For Plasma Immersion Ion ImplantationDocument4 pagesHigh Voltage Pulser With A Fast Fall-Time For Plasma Immersion Ion ImplantationAnonymous u5128WZ1KNo ratings yet

- A Low-Cost Solar Micro-Inverter With Soft-SwitchingDocument6 pagesA Low-Cost Solar Micro-Inverter With Soft-Switchingmohamed parvezNo ratings yet

- Electronics 11 03441 v2Document13 pagesElectronics 11 03441 v2Abdul Rehman AnsariNo ratings yet

- Thermal Wattmeter With Direct Power Conversion: Abstract-ADocument2 pagesThermal Wattmeter With Direct Power Conversion: Abstract-AMuhammad DhiyauddinNo ratings yet

- 18 A - Novel - 0.8-V - 79-nW - CMOS-Only - Voltage - Reference - With - 55-dB - PSRR - 100 - HZDocument5 pages18 A - Novel - 0.8-V - 79-nW - CMOS-Only - Voltage - Reference - With - 55-dB - PSRR - 100 - HZBalaramamurty SannidhiNo ratings yet

- Approximate Loss Formulae For Estimation of IGBT SDocument7 pagesApproximate Loss Formulae For Estimation of IGBT Sjeos20132013No ratings yet

- Iet-Est 2020 0013Document9 pagesIet-Est 2020 0013dinhquangcdtbkNo ratings yet

- IGBT/MOSFET Gate Drive Optocoupler: Optocouplers and Solid-State RelaysDocument9 pagesIGBT/MOSFET Gate Drive Optocoupler: Optocouplers and Solid-State Relaysme1816No ratings yet

- 4.) - General - Using - of - IGBT - Modules GOOD PDFDocument26 pages4.) - General - Using - of - IGBT - Modules GOOD PDFDoDuyBacNo ratings yet

- EE236 Lab7 Shobhit MaheshwariDocument7 pagesEE236 Lab7 Shobhit Maheshwarishobhitm.iitbNo ratings yet

- IGBT - Basic - 1 EE TimeDocument11 pagesIGBT - Basic - 1 EE TimeRichard TsengNo ratings yet

- I - G B T: Nsulated ATE Ipolar RansistorDocument59 pagesI - G B T: Nsulated ATE Ipolar RansistorsushilsemwalNo ratings yet

- 17 A - Nano-Watt - MOS-Only - Voltage - Reference - With - High-Slope - PTAT - Voltage - GeneratorsDocument5 pages17 A - Nano-Watt - MOS-Only - Voltage - Reference - With - High-Slope - PTAT - Voltage - GeneratorsBalaramamurty SannidhiNo ratings yet

- Factordepotencia - Reporte de RolandoDocument18 pagesFactordepotencia - Reporte de RolandoCésar Bolaños QuirósNo ratings yet

- RF Switches Using Phase Change Materials: Yonghyun Shim, Gwendolyn Hummel, and Mina Rais-ZadehDocument4 pagesRF Switches Using Phase Change Materials: Yonghyun Shim, Gwendolyn Hummel, and Mina Rais-ZadehkaurVRNo ratings yet

- Understanding IGBT heating in an AC drive system with regenerationDocument47 pagesUnderstanding IGBT heating in an AC drive system with regenerationSASNITHA A/P SELBONG STUDENTNo ratings yet

- Choosing Power Switching Devices For SMPS Designs: Mosfets or Igbts?Document6 pagesChoosing Power Switching Devices For SMPS Designs: Mosfets or Igbts?RubenG200No ratings yet

- X - Circuit Analysis of Active Mode Parasitic Oscillations in IGBT ModulesDocument7 pagesX - Circuit Analysis of Active Mode Parasitic Oscillations in IGBT ModulesOsman T.No ratings yet

- Instituto Tecnológico de La Costa GrandeDocument10 pagesInstituto Tecnológico de La Costa GrandeEver ContrerasNo ratings yet

- IEEE Transactions on Power Electronics Model Analyzes Static Induction Thyristor PerformanceDocument11 pagesIEEE Transactions on Power Electronics Model Analyzes Static Induction Thyristor PerformanceAbdulAzizNo ratings yet

- BGR OtasDocument6 pagesBGR Otaslravikumar.19.eeeNo ratings yet

- 456 UyhDocument13 pages456 Uyhkrishnan_744654120No ratings yet

- Lab1 Lab1Document17 pagesLab1 Lab1Noor AfiqNo ratings yet

- AN521 Intoduction To IGBTDocument10 pagesAN521 Intoduction To IGBTBuelnitaNo ratings yet

- IGBTs BasicsDocument10 pagesIGBTs BasicsTomas HuerdoNo ratings yet

- Heterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionFrom EverandHeterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionNo ratings yet

- Important Days of Year PDF For Competitive ExamsDocument8 pagesImportant Days of Year PDF For Competitive Examssushil4056No ratings yet

- CURRENT AFFAIRS COMPENDIUMDocument20 pagesCURRENT AFFAIRS COMPENDIUMVivek JadhavNo ratings yet

- GK Power Capsule - March 2014 PDFDocument9 pagesGK Power Capsule - March 2014 PDFKetan PatelNo ratings yet

- Zenta DentaDocument2 pagesZenta Dentasushil4056No ratings yet

- Best 40-character title for abbreviations and their full termsDocument19 pagesBest 40-character title for abbreviations and their full termsarunsanskritiNo ratings yet

- General Knowledge TodayDocument4 pagesGeneral Knowledge Todaysushil4056No ratings yet

- ArtistsDocument12 pagesArtistssushil4056No ratings yet

- QuestionsDocument3 pagesQuestionssushil4056No ratings yet

- Synergy Summit-Poster FinalDocument1 pageSynergy Summit-Poster Finalsushil4056No ratings yet

- Webdesign TrainingDocument6 pagesWebdesign Trainingsushil4056No ratings yet

- Assingment Task On LR - Q. 22 - 2Document25 pagesAssingment Task On LR - Q. 22 - 2sushil4056No ratings yet

- Gloabal Energy Summit-PosterDocument1 pageGloabal Energy Summit-PosterGlobal Energy Summit100% (1)

- Four Probe MethodDocument1 pageFour Probe MethodVita Efellina100% (3)

- Advaned Excel SylabusDocument3 pagesAdvaned Excel Sylabussushil4056No ratings yet

- Lecture Notes For Digital ElectronicsDocument43 pagesLecture Notes For Digital ElectronicsShruti GuptaNo ratings yet

- General Knowledge Today 2 3Document3 pagesGeneral Knowledge Today 2 3sushil4056No ratings yet

- Sushil Kundu CVDocument1 pageSushil Kundu CVsushil4056No ratings yet

- Wordpress Meet Responsive Design - Chris Coyier, Ian StewartDocument38 pagesWordpress Meet Responsive Design - Chris Coyier, Ian StewartAbdelaziz Zuñiga LopezNo ratings yet

- Lecture Notes For Digital ElectronicsDocument43 pagesLecture Notes For Digital ElectronicsShruti GuptaNo ratings yet

- Association of Management of MBA - MMS Institutes.1Document75 pagesAssociation of Management of MBA - MMS Institutes.1sushil4056No ratings yet

- General Knowledge Today - 3Document3 pagesGeneral Knowledge Today - 3sushil4056No ratings yet

- ES101 - Baisc Electrical & Electronics EngineeringDocument2 pagesES101 - Baisc Electrical & Electronics EngineeringMyWBUT - Home for EngineersNo ratings yet

- General Knowledge Today - 2Document3 pagesGeneral Knowledge Today - 2sushil4056No ratings yet

- General Knowledge Today-2Document3 pagesGeneral Knowledge Today-2Naman GargNo ratings yet

- General Knowledge Today 2 3Document3 pagesGeneral Knowledge Today 2 3sushil4056No ratings yet

- General Knowledge Today 2 2Document3 pagesGeneral Knowledge Today 2 2sushil4056No ratings yet

- General Knowledge TodayDocument4 pagesGeneral Knowledge Todaysushil4056No ratings yet

- Input - OutputDocument15 pagesInput - Outputsushil4056No ratings yet

- Logic GatesDocument4 pagesLogic Gatessushil4056No ratings yet

- QuanttipseditedDocument24 pagesQuanttipseditedsushil4056No ratings yet

- FTM-3100R/E: Advance ManualDocument33 pagesFTM-3100R/E: Advance ManualShedaPazNo ratings yet

- Measuring Dielectric Constants Using Microstrip LinesDocument7 pagesMeasuring Dielectric Constants Using Microstrip LinesKunal NateNo ratings yet

- PSU Tier ListDocument11 pagesPSU Tier ListEdwin Garcia HNo ratings yet

- Hadware NetwrokingDocument7 pagesHadware NetwrokingbalujalabsNo ratings yet

- Vlsi Unit-IDocument45 pagesVlsi Unit-Isuneelanubolu7No ratings yet

- Operational AmplifierDocument44 pagesOperational AmplifierPoornima GnNo ratings yet

- Led TV: Service ManualDocument50 pagesLed TV: Service ManualSertan YasanNo ratings yet

- II PU Physics Passing Package 21-22Document19 pagesII PU Physics Passing Package 21-22Kalyan ReddyNo ratings yet

- Chapter 6 QuizDocument15 pagesChapter 6 QuizEi Cho ZinNo ratings yet

- FTA-250L: Operating ManualDocument36 pagesFTA-250L: Operating Manualtom190465No ratings yet

- 26pfl4507 Chassis Pl12.1 Service ManualDocument78 pages26pfl4507 Chassis Pl12.1 Service ManualAlejandro AlcubierreNo ratings yet

- Per Unit CalculationsDocument3 pagesPer Unit CalculationssupernaenergyNo ratings yet

- PT650f e 2002Document67 pagesPT650f e 2002lehahai100% (4)

- Tutorial Sheet 1 (DC Networks & Transients)Document2 pagesTutorial Sheet 1 (DC Networks & Transients)Mr NobodyNo ratings yet

- EE221 Course Project - ReportDocument3 pagesEE221 Course Project - ReportRohit EnglaNo ratings yet

- 74LS541Document15 pages74LS541baterod3No ratings yet

- Au Optronics Corporation: Product SpecificationDocument37 pagesAu Optronics Corporation: Product Specificationсергей гомзяковNo ratings yet

- CC442 Chapter 8 Asynchronous CounterDocument19 pagesCC442 Chapter 8 Asynchronous CounterMuhamdA.BadawyNo ratings yet

- Eng Us Km2atscn-2.0.0Document171 pagesEng Us Km2atscn-2.0.0pqcrackerNo ratings yet

- PTV-Service TipsDocument101 pagesPTV-Service TipsHarold PolkaNo ratings yet

- Naida CI Q70 Product GuideDocument12 pagesNaida CI Q70 Product GuideAmirul AsyrafNo ratings yet

- Solatron FlowComputer - Man7951gasDocument334 pagesSolatron FlowComputer - Man7951gasHashemAliHashem100% (1)

- PR860 Detailed Service Manual 6881098C43-PDocument197 pagesPR860 Detailed Service Manual 6881098C43-PNermin NadžakovićNo ratings yet

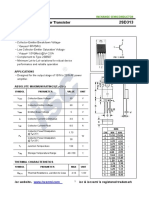

- 2SD313 60V NPN Power TransistorDocument2 pages2SD313 60V NPN Power TransistorSunu HerryNo ratings yet

- 070xna1 Panasonic IcDocument5 pages070xna1 Panasonic IcGeovanny SanJuanNo ratings yet

- Mbakfiranet PCDocument41 pagesMbakfiranet PCZhafirah Mahadewi SumantriNo ratings yet

- Connecting A Yamaha Engine To The NMEA 2000 NetworkDocument10 pagesConnecting A Yamaha Engine To The NMEA 2000 Networkpetercharland100% (2)

- Logic Design Lab Manual 10ESL38 3rd Sem 2011 PDFDocument61 pagesLogic Design Lab Manual 10ESL38 3rd Sem 2011 PDFvka_prince100% (1)

- EEC 446 B.Tech. Degree Examination Digital System DesignDocument2 pagesEEC 446 B.Tech. Degree Examination Digital System Designnaveen dandemNo ratings yet

- Eurotech U Boot PDFDocument38 pagesEurotech U Boot PDFBritoJuniorNo ratings yet