Professional Documents

Culture Documents

REALIMENTAÇÃO

Uploaded by

Weslei Ramos OvidioCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

REALIMENTAÇÃO

Uploaded by

Weslei Ramos OvidioCopyright:

Available Formats

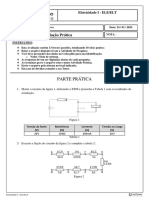

UNIVERSIDADE FEDERAL DO PAR

CAMPUS UNIVERSITRIO DE TUCURU

FACULDADE DE ENGENHARIA ELTRICA

DISCIPLINA: LABORATRIO DE ELETRNICA ANALGICA II

PROFESSOR: GUILHERME

EXPERIMENTO: REALIMENTAO

ALUNOS:

IVANIL LIMA 09134001018

LIEL NEVES 10134001518

WESLEI RAMOS 10134004418

TUCURU-PA,

2013

1 Resumo

Observar o efeito da realimentao em circuitos amplificadores.

2 Objetivos

A realimentao a ser vista aqui a negativa. Ela usada para se conseguir maior

estabilidade para o circuito. Quando realimentado degenerativamente ocorre uma reduo do

ganho de malha, no entanto, na mesma proporo que isso ocorre h uma dessenbilidade no

ganho, a reduo na distoro no-linear, a reduo do efeito do rudo, o controle das

impedncias de entrada e sada (aumento ou reduo, dependendo da topologia) e a extenso

da faixa de passagem do amplificador. Todas essas so caractersticas muito desejadas para

amplificadores, o que acaba compensando a queda do ganho.

Fazendo as combinaes possveis entre entrada/sada e srie/paralelo, tem-se as

quatro configuraes:

Amplificadores de Tenso: configurao srie- paralelo, apresenta alta resistncia de

entrada e baixa resistncia de sada.

Amplificadores de Corrente: configurao paralelo-srie, apresenta baixa resistncia

de entrada e alta resistncia de sada.

Amplificadores de Transresistncia: paralelo-paralelo, apresenta baixa resistncia de

entrada e baixa resistncia de sada.

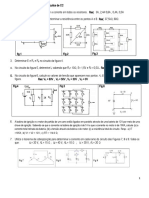

TOPOLOGIA SRIE PARALELO:

3 - Abordagem terica

Tambm conhecido como amplificador de tenso, apresenta alta resistncia de entrada

e baixa resistncia de sada (R

if

e R

of

, respectivamente). Como a entrada e a sada so tenses,

o ganho em malha direta A adimensional (V/V). Como o produto A x deve ser

adimensional, temos o ganho de realimentao tambm adimensional, e a amostra para a

realimentao dada por uma tenso V

f

, isto , = V

f

/Vo. O ganho em malha fechada A

f

dado por V

o

/V

f

.

Figura 1: topologia srie paralelo.

4 Materiais

Componentes: Resistores: R

1

= R

S

= R

L

= 1k, R

2

= 27k, amp op 741.

Equipamentos: 2 fontes de tenso DC, 1 multiteste, protoboard, 1 osciloscpio, 1 gerador de

sinais.

5- Resultado e Discusses

Com o auxlio de um multiteste ajustou-se as fontes de tenso para V

1

=+15V e

V

2

=-15V, em seguida montou-se o circuito como mostra a figura 1.

Usando os osciloscpio mediu-se V

0

=0,95V

rms

, V

S

=47,1mV

rms

e V

f

=34,3mV

rms

.

Calculou-se A

f

, beta () e A, como mostrado abaixo:

f

f

V

V

A

0

= Equao 1

3

10 3 , 34

93 , 0

=

x

A

f

11 , 27 =

f

A

0

V

V

f

= | Equao 2

93 , 0

10 3 , 34

3

=

x

|

036 , 0 = |

|

f

f

A

A

A

=

1

Equao 3

V kV A / 13 , 1 =

CIRCUITO AMPLIFICADOR DE TENSO

Mediu-se a corrente de entrada I

S

=0,07A, em seguida calculou-se a resistncia R

f

utilizando a equao 4.

S

S

if

I

V

R = Equao 4

6

3

10 07 , 0

10 1 , 47

=

x

x

R

if

O = k R

if

86 , 672

Com um potencimetro ligado na sada do circuito, diminuiu-se o sinal de entrada at

que este fosse reduzido pela metade, isso foi feito para se determinar a resistncia R

of

que foi

de 89,8.

Com os valores em mos montou-se a tabela 1:

Tabela 1: valores calculados

Config.

Srie-

paralelo

Valores prticos

R

if

(k)

R

of

() A (kV/V) A

f

672,86 89,9 1,13 0,036 27,11

TOPOLOGIA PARALELO - PARALELO:

6 - Abordagem Terica

Chamados amplificadores de transresistncias, apresentam baixa resistncia de entrada

e baixa resistncia de sada. A entrada uma corrente (I

S

) e a sada uma tenso (V

0

), logo o

ganho em malha direta A dado em (V/A) e a amostra para a realimentao dada por ama

corrente I

f

.

Figura 2: topologia paralelo paralelo.

7 Materiais

Componentes: Resistores: R

1

=4,7k, R

S

=10k, R

2

=47k, transistor: BC546BP;

Capacito=10F; potencimetro de 1K.

Equipamentos: 1 fonte de tenso DC, 1 multiteste, protoboard, 1 osciloscpio, 1 gerador de

sinais.

8- Resultado e Discusses

Ajustou-se a fonte de tenso DC para 12V, e com o circuito montado mediu-se V

B

e

V

S

e V

0

, listado na tabela 2, em seguida calculou-se A

f

utilizando as equaes 5 e 6.

Tabela 2: valores medidos de tenso.

V

0

V

B

V

S

4,01V 651mV 109mV

| A

A

A

f

+

=

1

Equao 5

) // // )( // ( /

t

r R R R R g I V A

f S C f m i o

= = Equao 6

A kV A / 7 , 358 =

Substituindo o valor de A na equao 5, tm-se:

) 10 7 , 358 (

10 47

1

1

10 7 , 358

3

3

3

x

x

x

A

f

|

.

|

\

|

+

=

O = k A

f

6 , 41

De posse desses valores, calculou-se I

S

, utilizando a equao 7.

( )

S

B S

S

R

V V

I

= Equao 7

( )

3

3 3

10 10

10 651 10 109

x

x x

I

S

=

A I

S

2 , 54 =

Com o valor de I

S

foi possvel calcular R

if

, utilizando a equao 8.

S

B

if

I

V

R = Equao 8

6

3

10 2 , 54

10 651

=

x

x

R

if

O = k R

if

01 , 12

Para obter a resistncia de sada (R

of

), conectou-se um capacitor em srie com o

potencimetro tambm ligado srie com a sada do circuito. Ajustou-se o potencimetro de

modo a se obter V

0

/2, em seguida mediu-se a resistncia no potencimetro, esta foi de

R

0f

=267.

Tabela 3: valores medidos.

Config.

Paralelo-

paralelo

Valores prticos

R

if

(k)

R

of

() A A

f

12,01 267 -358,7k -1/47k -41,6k

TOPOLOGIA PARALELO - SRIE

9- Abordagem Terica

Chamados amplificadores de corrente apresentam baixa resistncia de entrada e alta

resistncia de sada. Como a entrada e a sada so correntes, o ganho em malha direta A

adimensional (A/A). O produto A x deve tambm ser adimensional, assim como o ganho de

realimentao e a amostra para a realimentao dada por uma corrente I

f

.

Figura 3: topologia paralelo - srie.

10- Materiais

Componentes: Resistores: R

C1

=10k, R

C2

=10k, R

B1

=100k, R

B2

=15k, R

S

=100k,

R

E1

=820, R

E2

=3,3k e R= 10k, 2 transistores: BC238BP; 3 capacitores de 10F e 1 de

100F e 1 potencimetro de 1K.

Equipamentos: 1 fonte de tenso DC, 1 multiteste, protoboard, 1 osciloscpio, 1 gerador de

sinais.

11- Resultado e Discusses

Ajustou-se a fonte de tenso DC para 12V, e com o circuito montado mediu-se V

B1

,

V

S

, V

0

e V

E1

, sabendo-se que R

f

=10k calculou-se A, A

f

e . Os valores medidos esto

mostrados na tabela 4.

Tabela 4: valores simulados de tenso e corrente.

V

0

V

B1

V

S

V

E1

V

E2

I

0

0,38mV 12V 11,9V 11,9 11,9 0,38A

b

I

I

A

0

= Equao 9

f S b

I I I = Equao 10

f

E B

f

R

V V

I

2 1

= Equao 11

A I

f

10 =

S

B S

S

R

V V

I

1

= Equao 12

A I

S

10 =

Substituindo I

S

e I

f

na equao 10, tm-se:

A I

b

20 =

Substituindo I

b

na equao 9, tm-se:

A mA A / 19 =

Calculou-se o beta utilizando a equao 13:

o f

I I / = | Equao 13

31 , 26 = |

Substituindo o valor de e de A na equao 4, tm-se:

| A

A

A

f

+

=

1

Equao 4

m A

f

66 , 12 =

A partir dos valores obtidos acima, calculou-se a resistncia R

if

como mostrado

abaixo:

S

B

if

I

V

R

1

=

Equao 15

O = M R

if

2 , 1

Tabela 5: valores simulados.

Config.

Paralelo-

Srie

Valores Simulados

R

if

(M)

A A

f

1,2 -19m 26,31 -12,66m

De posse dos valores obtidos nos circuitos de realimentao, montou-se a tabela 6,

onde podemos observar uma comparao dos parmetros calculados em cada circuito.

Tabela 6: comparao entre simulao e prtica.

Configurao

Valores Simulados

R

if

()

R

of

( ) A (V/V) A

f

Paralelo-Srie 1,2M ___ -19m -1/47k -12,66m

Configurao

Valores Prticos

R

if

(k) R

of

( ) A (kV/V) A

f

Srie-paralelo 672,86 89,9 1,13 0,036 27,11

Paralelo-Paralelo 12,01 267 -358,7 -1/47k -41,6k

12 Concluso

Analisando os resultados obtidos, podemos observar que os resustados obtidos em

laboratrio esto coerentes com a teoria. Porm com algumas discrepncias nos valores de

resistncia, capacitncia e nos valores dos betas dos transistores.

13- Referncias Bibliogrficas

Livro

1- Sedra Smitch, Microeletrnica, 5 Edio.

Software:

Proteus ISIS PROFESSIONAL.

You might also like

- Matemática - Circuitos Elétricos Métodos de Resolução de Malhas MúltiplasDocument20 pagesMatemática - Circuitos Elétricos Métodos de Resolução de Malhas MúltiplasCaderno_Vestibular100% (7)

- Relatorio 4 Potencias em Regime Permanente SenoidalDocument15 pagesRelatorio 4 Potencias em Regime Permanente SenoidalLetyflixNo ratings yet

- Relatório 3 - Amp Op Malha Aberta X Realimentação Negativa PDFDocument7 pagesRelatório 3 - Amp Op Malha Aberta X Realimentação Negativa PDFWanderson GomesNo ratings yet

- Amp Op Malha Aberta X Realimentação NegativaDocument7 pagesAmp Op Malha Aberta X Realimentação NegativaWanderson GomesNo ratings yet

- Circuitos de CCDocument5 pagesCircuitos de CCAndreEmersonKey-SonAchopaNo ratings yet

- Prova 1Document5 pagesProva 1Juliana KmiecikNo ratings yet

- Projetos Em Clp Ladder Baseado Na Placa Arduino Uno Parte XiiiFrom EverandProjetos Em Clp Ladder Baseado Na Placa Arduino Uno Parte XiiiNo ratings yet

- Prova Rafael FuhrmannDocument40 pagesProva Rafael FuhrmannRafael FuhrmannNo ratings yet

- Primeira Lista de Execicios - Cicuitos Eletricos I - 2013-01Document8 pagesPrimeira Lista de Execicios - Cicuitos Eletricos I - 2013-01Lari RibeiroNo ratings yet

- Gerador de Forma de Onda SenoidalDocument15 pagesGerador de Forma de Onda SenoidalLucas MouraNo ratings yet

- Modelo Relatorio CorretoDocument13 pagesModelo Relatorio CorretoHyngrid SouzaNo ratings yet

- Amplificadores Operacionais Fundamentos e Aplicacoes Gruiter Parte 1Document8 pagesAmplificadores Operacionais Fundamentos e Aplicacoes Gruiter Parte 1Márcio De Freitas CarneiroNo ratings yet

- 1.lista Exercícios de TransistoresDocument5 pages1.lista Exercícios de TransistoresRomeu Corradi JúniorNo ratings yet

- 8-Modelo Relatorio Correto Meio CompletoDocument8 pages8-Modelo Relatorio Correto Meio CompletoHyngrid SouzaNo ratings yet

- Lista 2 Circuitos1 2018Document3 pagesLista 2 Circuitos1 2018Murilo SantosNo ratings yet

- Prova III de Instrumentos de Medida 3BELT INT 202201218-2Document4 pagesProva III de Instrumentos de Medida 3BELT INT 202201218-2Kaio MagalhaesNo ratings yet

- Questões Geradores Elétricos (ETE) - Beatriz, Enzo, Giorgia e Maria JúliaDocument7 pagesQuestões Geradores Elétricos (ETE) - Beatriz, Enzo, Giorgia e Maria JúliaRaphael VieiraNo ratings yet

- MEDIDAS - Exercícios Resolvidos PDFDocument19 pagesMEDIDAS - Exercícios Resolvidos PDFCarlos Andrade Neto100% (2)

- 10º Ano-A-física-proposta de Resolução Dos Exercícios de Preparação para o Teste-Maio 2-5-2023-Versão IDocument12 pages10º Ano-A-física-proposta de Resolução Dos Exercícios de Preparação para o Teste-Maio 2-5-2023-Versão IMarta SilvaNo ratings yet

- Exercicios de BJTDocument9 pagesExercicios de BJTVasco Joaquim MhulaNo ratings yet

- Geradores e Leis de KirchhoffDocument13 pagesGeradores e Leis de KirchhoffRomerio Ribeiro da SilvaNo ratings yet

- Eletrodinamica Só QuestoesDocument33 pagesEletrodinamica Só QuestoesAnanda FreitasNo ratings yet

- EL 009 KirchhoffDocument2 pagesEL 009 KirchhoffJoão CarlosNo ratings yet

- Relatorio 1Document6 pagesRelatorio 1Matheus AmbrósioNo ratings yet

- Circuitos - Geradores e ReceptoresDocument9 pagesCircuitos - Geradores e ReceptoresgsimurraNo ratings yet

- EXP 10 Divisor de TensãoDocument6 pagesEXP 10 Divisor de TensãoItalo JasterNo ratings yet

- Relatorio Inversor Nao - Inversor SomadorDocument9 pagesRelatorio Inversor Nao - Inversor SomadorIGOR ROMANONo ratings yet

- Exercicios 5Document15 pagesExercicios 5morcego151061No ratings yet

- Relatório de Circuitos Elétricos 2 - Circuito RC ParaleloDocument15 pagesRelatório de Circuitos Elétricos 2 - Circuito RC ParaleloWeslei Ramos OvidioNo ratings yet

- Lista Exerc 1Document6 pagesLista Exerc 1Júlio César SoaresNo ratings yet

- Exercícios ResolvidosDocument19 pagesExercícios ResolvidosDintreinamentos Qualificação Industrial75% (4)

- Exercicios Resolvidos ElétricaDocument23 pagesExercicios Resolvidos Elétricacidorai94% (31)

- Lista Exerc 1 PDFDocument6 pagesLista Exerc 1 PDFPauloDyerNo ratings yet

- Circuito RLC-sérieDocument8 pagesCircuito RLC-sérieJanderPeixotoNo ratings yet

- Sistemas TrifasicosDocument11 pagesSistemas TrifasicosCarlos MateusNo ratings yet

- EXP 13 Leis de KirchhoffDocument6 pagesEXP 13 Leis de KirchhoffItalo JasterNo ratings yet

- Planejamento Experimento IIDocument6 pagesPlanejamento Experimento IIKevin MajarowskyNo ratings yet

- ELETRICIDADE BASICO DP UnipDocument9 pagesELETRICIDADE BASICO DP UnipVictor FerreiraNo ratings yet

- Atividade Prática Final Eletricidade1-1Document4 pagesAtividade Prática Final Eletricidade1-1proeduque.cursos.profissoesNo ratings yet

- Relatório Associação em ParaleloDocument8 pagesRelatório Associação em ParaleloAline AndressaNo ratings yet

- AVI - Ernane - CircuitosDocument11 pagesAVI - Ernane - CircuitosGabriel NatividadeNo ratings yet

- Relatório Elementos ResistivosDocument10 pagesRelatório Elementos ResistivosJulia BzrrNo ratings yet

- CCAexer Resolvidos IVDocument6 pagesCCAexer Resolvidos IVtumirada bolerosNo ratings yet

- Lista de Exercícios GTDDocument6 pagesLista de Exercícios GTDjanluccasNo ratings yet

- Relatorio 2 - Circuitos Elétricos FotonicaDocument7 pagesRelatorio 2 - Circuitos Elétricos FotonicaMatheus AmbrósioNo ratings yet

- Experimento 1 Circuitos Elétrico e FotônicaDocument10 pagesExperimento 1 Circuitos Elétrico e FotônicaGuilherme Pedroso RegisNo ratings yet

- Resultados e Discussão - Circuito RLDocument4 pagesResultados e Discussão - Circuito RLRodrigo RodriguesNo ratings yet

- Avaliação Prática - Eletricidade IDocument5 pagesAvaliação Prática - Eletricidade IAnderson SilvérioNo ratings yet

- Relatório 3Document10 pagesRelatório 3vanderson rosaNo ratings yet

- Atividade de Pesquisa - Eletricidade IDocument9 pagesAtividade de Pesquisa - Eletricidade IThamara BellaNo ratings yet

- Relatório 3Document3 pagesRelatório 3alexsandrodidiNo ratings yet

- Relatorio Pratica 4Document8 pagesRelatorio Pratica 4Matheus RodriguesNo ratings yet

- Resposta em Frequência Com TBJDocument13 pagesResposta em Frequência Com TBJWeslei Ramos OvidioNo ratings yet

- 2º Relatório de Eletrônica Digital CI COM PORTAS AND, NAND, OR E NORDocument14 pages2º Relatório de Eletrônica Digital CI COM PORTAS AND, NAND, OR E NORWeslei Ramos OvidioNo ratings yet

- Resposta em Frequência Com TBJDocument13 pagesResposta em Frequência Com TBJWeslei Ramos OvidioNo ratings yet

- Relatório-Amp Op de Potência Classe ADocument10 pagesRelatório-Amp Op de Potência Classe AWeslei Ramos OvidioNo ratings yet

- Amplificador Diferencial Com TBJDocument7 pagesAmplificador Diferencial Com TBJWeslei Ramos OvidioNo ratings yet

- Resposta em Frequência Com TBJDocument13 pagesResposta em Frequência Com TBJWeslei Ramos OvidioNo ratings yet

- Relatório de Circuitos Elétricos 2 - Filtros Passa-Baixa e Passa-AltaDocument31 pagesRelatório de Circuitos Elétricos 2 - Filtros Passa-Baixa e Passa-AltaWeslei Ramos OvidioNo ratings yet

- Relatório de Circuitos Elétricos 2 - Circuito RC SérieDocument21 pagesRelatório de Circuitos Elétricos 2 - Circuito RC SérieWeslei Ramos OvidioNo ratings yet

- Relatório de Circuitos Elétricos 2 - Circuito RC ParaleloDocument15 pagesRelatório de Circuitos Elétricos 2 - Circuito RC ParaleloWeslei Ramos OvidioNo ratings yet

- Campo ANGLO SPDocument22 pagesCampo ANGLO SPJ_BellineNo ratings yet

- Fasciculo Da 10 Classe Tema C e D Nova Versao 084846 PDFDocument35 pagesFasciculo Da 10 Classe Tema C e D Nova Versao 084846 PDFClaudete Silveira0% (1)

- Ficha de Trabalho Nº 1Document5 pagesFicha de Trabalho Nº 1luciamiguelotefqNo ratings yet

- Xer HidrostaticaDocument11 pagesXer Hidrostaticadouglas_2069No ratings yet

- Atividade Avaliativa 1Document3 pagesAtividade Avaliativa 1Divanil MacedoNo ratings yet

- Evaporador Tunel 3 MP - 040414Document8 pagesEvaporador Tunel 3 MP - 040414carlosNo ratings yet

- 2.deslocamento, Velocidade Média, Velocidade e AceleraçãoDocument13 pages2.deslocamento, Velocidade Média, Velocidade e AceleraçãoCristina Casquilho M. CastroNo ratings yet

- Rev. H 07 / 2021: ProcedimentoDocument13 pagesRev. H 07 / 2021: ProcedimentoCarlos RodriguesNo ratings yet

- Simulacao de Cargas MecânicasDocument69 pagesSimulacao de Cargas MecânicasEduardo TanakaNo ratings yet

- Pressão Máxima de VaporDocument4 pagesPressão Máxima de VaporGabriel SchultzNo ratings yet

- Projecto BelarminoDocument62 pagesProjecto BelarminoDemítrio G. Pio100% (1)

- Ef12 Questao Aula Fisica Moderna ResolucaoDocument5 pagesEf12 Questao Aula Fisica Moderna ResolucaoEvaristo José Das Mangas100% (1)

- Refrigerador RS21-PortuguesDocument97 pagesRefrigerador RS21-PortuguesMaiara Balsanelli86% (7)

- Exercício em SalaDocument5 pagesExercício em SalaAna Carolina BarrosoNo ratings yet

- Aulas UPE - Módulo 3 - Parte 1 - ResistênciaDocument66 pagesAulas UPE - Módulo 3 - Parte 1 - ResistênciaToninho PorpinoNo ratings yet

- CelescDocument20 pagesCelescVanessa ZimmermannNo ratings yet

- Avaliação de CiênciasDocument6 pagesAvaliação de Ciênciaseduardo valeNo ratings yet

- Mecânica Geral - Unidade II - Sistema de Forças IDocument32 pagesMecânica Geral - Unidade II - Sistema de Forças IRayaneNo ratings yet

- Aula Eletricidade Básica 1Document11 pagesAula Eletricidade Básica 1Silas SantosNo ratings yet

- Aula Prática Transformadores - 2013Document4 pagesAula Prática Transformadores - 2013Matheus DutraNo ratings yet

- 284-Texto Do Artigo-690-1-10-20190408Document20 pages284-Texto Do Artigo-690-1-10-20190408Raul FerreiraNo ratings yet

- Apostila de Prevenção HidranteDocument32 pagesApostila de Prevenção HidrantePRESTADORA DE SERVIÇO KRGNo ratings yet

- LISTA 39 Cap 11 Momento AngularDocument2 pagesLISTA 39 Cap 11 Momento AngularMaria Eduarda EnriconiNo ratings yet

- Folheto de Curvas Características: Megacpk, HPK-L Magnochem, Magnochem-Bloc, Meganorm, MegablocDocument168 pagesFolheto de Curvas Características: Megacpk, HPK-L Magnochem, Magnochem-Bloc, Meganorm, MegablocAlexandre GelsiNo ratings yet

- Material para Trabalho EmmersonDocument35 pagesMaterial para Trabalho EmmersonEmerson SilvaNo ratings yet

- Cap 3 - Instrumentação - Sensores de Deslocamento e PosiçãoDocument18 pagesCap 3 - Instrumentação - Sensores de Deslocamento e PosiçãoWASHINGTONNo ratings yet

- Teoria Cinética MolecularDocument12 pagesTeoria Cinética MolecularJoaquim Cumbane100% (2)

- Ficha de Trabalho Nº4 PDFDocument3 pagesFicha de Trabalho Nº4 PDFanitadiogo100% (1)

- Fisica Termodinamica Gases ExerciciosDocument10 pagesFisica Termodinamica Gases ExerciciosjeversonprofNo ratings yet

- Filtros Ativos2Document24 pagesFiltros Ativos2'Yuri CardosoNo ratings yet