Professional Documents

Culture Documents

Informe

Uploaded by

Wilmer ObispoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Informe

Uploaded by

Wilmer ObispoCopyright:

Available Formats

Quartus II es una herramienta de software producida por Altera para el anlisis y la sntesis de diseos realizados en HDL.

Quartus II permite al desarrollador o desarrolladora compilar sus diseos, realizar anlisis temporales, examinar diagramas RTL y configurar el dispositivo de destino con el programador.

Con el programa de diseo Quartus II los diseadores pueden usar los dispositivos HardCopy Stratix de manera que puede prever y verificar su rendimiento, el cual resulta en promedio un 50 por ciento ms rpido que su FPGA equivalente. Adems, en el flujo de diseo del HardCopy Stratix, Quartus II incluye una serie de utilidades que reducen el tiempo de diseo. Como contraste adicional el bajo precio del Quartus II en comparacin con otras herramientas de diseo de ASIC. VHDL es el acrnimo que representa la combinacin de VHSIC y HDL, donde VHSIC es el acrnimo de Very High Speed Integrated Circuit y HDL es a su vez el acrnimo de Hardware Description Language. Es un lenguaje definido por el IEEE (Institute of Electrical and Electronics Engineers) (ANSI/IEEE 1076-1993) usado por ingenieros para describir circuitos digitales. Otros mtodos para disear circuitos son la captura de esquemas (con herramientas CAD) y los diagramas de bloques, pero stos no son prcticos en diseos complejos. Otros lenguajes para el mismo propsito son Verilog y ABEL. Aunque puede ser usado de forma general para describir cualquier circuito se usa principalmente para programar PLD (Programable Logic Device - Dispositivo Lgico Programable), FPGA (Field Programmable Gate Array), ASIC y similares. Dentro del VHDL hay varias formas con las que podemos disear el mismo circuito y es tarea del diseador elegir la ms apropiada. Funcional: Describimos la forma en que se comporta el circuito. Esta es la forma que ms se parece a los lenguajes de software ya que la descripcin es secuencial. Estas sentencias secuenciales se encuentran dentro de los llamados procesos en VHDL. Los procesos son ejecutados en paralelo entre s, y en paralelo con asignaciones concurrentes de seales y con las instancias a otros componentes. Flujo de datos: describe asignaciones concurrentes (en paralelo) de seales. Estructural: se describe el circuito con instancias de componentes. Estas instancias forman un diseo de jerarqua superior, al conectar los puertos de estas instancias con las seales internas del circuito, o con puertos del circuito de jerarqua superior. Mixta: combinacin de todas o algunas de las anteriores.

En VHDL tambin existen formas metdicas para el diseo de mquinas de estados, filtros digitales, bancos de pruebas etc. Secuencia de diseo[editar editar fuente]

El flujo de diseo de un sistema podra ser: Divisin del diseo principal en mdulos separados. La modularidad es uno de los conceptos principales de todo diseo. Normalmente se diferencia entre dos metodologas de diseo: topdown y botton-up. La metodologa top-down consiste en que un diseo complejo se divide en diseos ms sencillos que se puedan disear (o describir) ms fcilmente. La metodologa bottonup consiste en construir un diseo complejo a partir de mdulos, ya diseados, ms simples. En la prctica, un diseo usa generalmente ambas metodologas. Entrada de diseos, pueden usarse diversos mtodos tal como se vio anteriormente. Simulacin funcional, es decir, comprobaremos que lo escrito en el punto anterior realmente funciona como queremos, si no lo hace tendremos que modificarlo. En este tipo de simulacin se comprueba que el cdigo VHDL o Verilog (u otro tipo de lenguaje HDL) ejecuta correctamente lo que se pretende. Sntesis. En este paso se adapta el diseo anterior (que sabemos que funciona) a un hardware en concreto, ya sea una FPGA o un ASIC. Hay sentencias del lenguaje que no son sintetizables, como por ejemplo divisiones o exponenciaciones con nmeros no constantes. El hecho de que no todas las expresiones en VHDL sean sintetizables es que el VHDL es un lenguaje genrico para modelado de sistemas (no slo para diseo de circuitos digitales), por lo que hay expresiones que no pueden ser transformadas a circuitos digitales. Durante la sntesis se tiene en cuenta la estructura interna del dispositivo, y se definen restricciones, como la asignacin de pines. El sintetizador optimiza las expresiones lgicas con objeto de que ocupen menor rea, o bien son eliminadas las expresiones lgicas que no son usadas por el circuito. Simulacin post-sntesis. En este tipo de simulacin se comprueba que el sintetizador ha realizado correctamente la sntesis del circuito, al transformar el cdigo HDL en bloques lgicos conectados entre s. Este paso es necesario ya que, a veces, los sintetizadores producen resultados de sntesis incorrectos, o bien realiza simplificaciones del circuito al optimizarlo. Ubicacin y enrutamiento. El proceso de ubicacin consiste en situar los bloques digitales obtenidos en la sntesis de forma ptima, de forma que aquellos bloques que se encuentran muy interconectados entre s se siten prximamente. El proceso de enrutamiento consiste en interconectar adecuadamente los bloques entre s, intentando minimizar retardos de propagacin para maximizar la frecuencia mxima de funcionamiento del dispositivo.

Anotacin final. Una vez ha sido completado el proceso de ubicacin y enrutamiento, se extraen los retardos de los bloques y sus interconexiones, con objeto de poder realizar una simulacin temporal (tambin llamada simulacin post-layout). Estos retardos son anotados en un fichero SDF (Standard Delay Format) que asocia a cada bloque o interconexin un retardo mnimo/tpico/mximo. Simulacin temporal. A pesar de la simulacin anterior puede que el diseo no funcione cuando se programa, una de las causas puede ser por los retardos internos del chip. Con esta simulacin se puede comprobar, y si hay errores se tiene que volver a uno de los anteriores pasos. Programacin en el dispositivo. Se implementa el diseo en el dispositivo final y se comprueba el resultado.

You might also like

- Total Play - Estado de Cuenta PDFDocument2 pagesTotal Play - Estado de Cuenta PDFMa Asuncion Cardenas Coronel67% (3)

- Ejercicios Resueltos de Volumetria PDFDocument431 pagesEjercicios Resueltos de Volumetria PDFLaura Guarguati100% (5)

- Ejercicios Resueltos de Volumetria PDFDocument431 pagesEjercicios Resueltos de Volumetria PDFLaura Guarguati100% (5)

- Banco de Preguntas para El Examen Complexivo - Metodologia - Desarrollo de SoftwareDocument12 pagesBanco de Preguntas para El Examen Complexivo - Metodologia - Desarrollo de SoftwareJinna Salazar Vasquez100% (1)

- Medidor de Consumo Electrico DigitalDocument206 pagesMedidor de Consumo Electrico DigitalJuan LitardoNo ratings yet

- Pampa de PongoDocument146 pagesPampa de PongoRocío GuerreroNo ratings yet

- PDFDocument202 pagesPDFcarlos miño100% (2)

- Propiedades Hidráulicas ElementalesDocument19 pagesPropiedades Hidráulicas Elementalesborrita0No ratings yet

- Grupo 4 DeltasDocument46 pagesGrupo 4 DeltasWilmer ObispoNo ratings yet

- GFalcevhDocument104 pagesGFalcevhWilmer ObispoNo ratings yet

- Tratamiento EstadísticoDocument13 pagesTratamiento EstadísticoWilmer ObispoNo ratings yet

- Region de IcaDocument37 pagesRegion de IcaWilmer Obispo100% (1)

- ChronostratChart2015 01spanishDocument1 pageChronostratChart2015 01spanishPatriciaVillaHerreraNo ratings yet

- Yacimientos Relacionados en Procesos de SubducciónDocument3 pagesYacimientos Relacionados en Procesos de SubducciónWilmer ObispoNo ratings yet

- Continuidad DiscontinuidadDocument88 pagesContinuidad DiscontinuidadAbraham Alejandro Arana VilcaNo ratings yet

- Curso CuaternarioDocument89 pagesCurso CuaternarioWilmer ObispoNo ratings yet

- El Peru en El Contexto de America Del Sru - Geologia Del Peru - ListoDocument60 pagesEl Peru en El Contexto de America Del Sru - Geologia Del Peru - ListoWilmer ObispoNo ratings yet

- El FutbolDocument2 pagesEl FutbolWilmer ObispoNo ratings yet

- GEOFISICADocument9 pagesGEOFISICAWilmer ObispoNo ratings yet

- Rocas Metamorficas BDocument12 pagesRocas Metamorficas BYony Zuasnabar PaucarNo ratings yet

- Cap 8 RocasmetamorficasDocument13 pagesCap 8 RocasmetamorficasWilmer ObispoNo ratings yet

- Vista Satelital Del Cerro San Cristobal Desde Google HeartDocument18 pagesVista Satelital Del Cerro San Cristobal Desde Google HeartWilmer ObispoNo ratings yet

- Articulo Masa-ResorteDocument6 pagesArticulo Masa-ResorteSergio Aguilar GómezNo ratings yet

- METAMORFISMODocument15 pagesMETAMORFISMOWilmer ObispoNo ratings yet

- Practico 4 GranulometriaDocument15 pagesPractico 4 GranulometriaWilmer ObispoNo ratings yet

- GeolimDocument10 pagesGeolimirex11No ratings yet

- Ejercicios Resueltos (F.Vectoriales)Document21 pagesEjercicios Resueltos (F.Vectoriales)eudiswister100% (1)

- 1ra Clase de Análisis QuímicoDocument30 pages1ra Clase de Análisis QuímicoWilmer ObispoNo ratings yet

- Java - FLUJOS DE ENTRADA Y SALIDA PDFDocument15 pagesJava - FLUJOS DE ENTRADA Y SALIDA PDFGerardoHernandezCatemaxca100% (1)

- Guía Completa - Aprende Cómo Construir Un CelularDocument6 pagesGuía Completa - Aprende Cómo Construir Un CelularelianachicadeaguasNo ratings yet

- Diagrama de V de GowinDocument2 pagesDiagrama de V de GowinDIANA OLIVARESNo ratings yet

- Cubos OLAP de Información para La Toma de DecisionesDocument5 pagesCubos OLAP de Información para La Toma de DecisionesJosue Andres Aizprua MeraNo ratings yet

- Informe 2Document5 pagesInforme 2Diseños Con feNo ratings yet

- Investigación de Mercados y Sistemas de Información - PPT (Recuperado)Document8 pagesInvestigación de Mercados y Sistemas de Información - PPT (Recuperado)Manuel Alberto ManzanilloNo ratings yet

- Streaming AsirDocument60 pagesStreaming AsirJose Alberto Flores FernandezNo ratings yet

- HP Pro SFF 400 G9 6J396LT#ABM-DMDocument1 pageHP Pro SFF 400 G9 6J396LT#ABM-DMMilthon Loza ChambillaNo ratings yet

- Transmisiones MecanicasDocument29 pagesTransmisiones MecanicasANDREA CAROLINA CARBALLO AGUIRRENo ratings yet

- Manual de UsuarioDocument12 pagesManual de UsuarioNeryNo ratings yet

- Mip15b31 C2 3310 55 PR 205Document20 pagesMip15b31 C2 3310 55 PR 205victor ccansaya linaresNo ratings yet

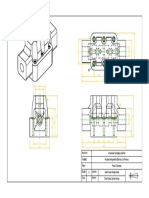

- Proyecto Final UTP-PIEZA 3 OMAR GOMEZ ARANGODocument1 pageProyecto Final UTP-PIEZA 3 OMAR GOMEZ ARANGOJahir emerson tantalean quiñonesNo ratings yet

- Mantenimiento t4Document4 pagesMantenimiento t4Carlos Cruz ElizondoNo ratings yet

- Ejercicio de Busca El Intruso. 1Document3 pagesEjercicio de Busca El Intruso. 1VERONICA PATRICIA CISNEROS QUIROLANo ratings yet

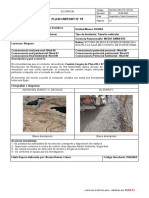

- Flash Report N 75Document1 pageFlash Report N 75Angie MendozaNo ratings yet

- Guzman Et Al - 1996 - Metodologias Participativas de Investigacion-Un Aporte Al Desarrollo Local Endogeno1Document16 pagesGuzman Et Al - 1996 - Metodologias Participativas de Investigacion-Un Aporte Al Desarrollo Local Endogeno1Oscar DelgadilloNo ratings yet

- Ejemplo de Desarrollo Del ProblemaDocument2 pagesEjemplo de Desarrollo Del ProblemaDanielNo ratings yet

- Optiplex Aio 7410 Owners Manual Es XLDocument175 pagesOptiplex Aio 7410 Owners Manual Es XLRaúl Del PezoNo ratings yet

- Actividad 3 Palancas de ReactivacionDocument6 pagesActividad 3 Palancas de ReactivacionSandra Gomez.No ratings yet

- Guía de Precios Rittal 2023 (v1)Document54 pagesGuía de Precios Rittal 2023 (v1)Jorge Rodriguez AlvaradoNo ratings yet

- Caso de Aplicacion Seis SigmaDocument7 pagesCaso de Aplicacion Seis SigmajogaviarNo ratings yet

- Publicaciones Digitales y FísicasDocument3 pagesPublicaciones Digitales y FísicasAndrea GutierrezNo ratings yet

- Bento4 Users GuideDocument168 pagesBento4 Users GuidejosejoluluNo ratings yet

- Curriculum Vitae - Marco Lo TortoDocument4 pagesCurriculum Vitae - Marco Lo TortoMarco Lo TortoNo ratings yet

- Derecho CivilDocument19 pagesDerecho CivilPedroNo ratings yet

- Informe FinalDocument6 pagesInforme Finaljuan qazNo ratings yet