Professional Documents

Culture Documents

Lab 5 DSP and FPGA Embedded Resources Signal Filtering and Display

Uploaded by

Zisa KrageOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab 5 DSP and FPGA Embedded Resources Signal Filtering and Display

Uploaded by

Zisa KrageCopyright:

Available Formats

Lab 5 DSP and FPGA Embedded Resources Signal Filtering and Display

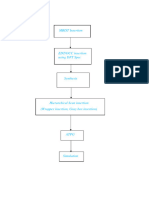

Design and implement a digital circuit that calculates and shows the magnitude of a filtered signal. Your circuit must generate all control and data signals for producing the signal, filtering it, and displaying the magnitude on both the seven segment display and a display via the VGA output of the BASYS2 board. Please refer to the introductory lab slides for information about the signal and filtering. Use the clock frequency of 25 MHz generated by a DCM, and the resolution as close as possible to 640x480 pixels. This Lab can be done in teams or individually, but teams are required to finish more tasks. Task 1 (for individuals: required, 1 point; for teams: required, 0.75 points) Design a circuit that generates a sine wave (often called a Numerically Controlled Oscillator, or NCO.) The NCO output frequency is determined by six switches [5:0]. The NCO outputs the amplitude of a sine wave every 195 clocks. The sine wave frequency ranges from 0 to 63.1 kHz in ~1 kHz increments. When the switches are all in the 0 position, the frequency is 0 Hz. When the switches are all in the 1 position, the frequency is 63.1 kHz. Task 2 (for individuals: required, 2 points; for teams: required, 1.5 points) Design a circuit that performs a Finite Impulse Response (FIR) filter. The filter has 256 taps (supplied in a coefficient file.) Use the Coregen application to generate a 1024x18 dual port read-only-memory (ROM) that contains the coefficients using a Block RAM. This is called the Tap Buffer. The dual-output of the Tap Buffer is called the Taps. Implement a circular buffer by inferring a 256x18 dual-port distributed RAM to store the most recent 256 NCO outputs. This is called the Sample Buffer. The dual-output of the Sample Buffer is called the Samples. Using two multipliers (performed by instantiating the multiplier primitive), iterate through 128 pairs of products (where one product is[ Sample(i) * Tap(i)]) while storing the accumulated sum of the products. At the end of the 128 cycles, the final sum is output and the accumulator resets for the next iteration. When a new Sample is input to the Sample Buffer, the iterative process starts again.

Task 3 (for individuals: required, 1 point; for teams: required, 0.75 points) Design a circuit that calculates the magnitude of a signed input and scales it (using a generic). Use the Coregen application to generate a 1024x18 Block RAM. Implement a circular buffer with the core. The circular buffer is uses as a shift register to calculate the moving average of the most recent 1024 values. Task 4 (for individuals: required, 1 point; for teams: required, 0.75 points) Combine Task 1-3 into a top-level FPGA file. Display the moving-average result on the seven-segment display. Task 5 (for individuals: required, 1 point; for teams: required, 0.75 points) In Task 2, the supplied coefficient file and Coregen-erated Block RAM contains 4 distinct sets of filters, each 256 taps long, and each with a different frequency response. Expand Task 4 so that switches [7:6] selects one of the four sets of taps. When the switches are 00, the first 256 taps are used. When the switches are 01, the next 256 taps are used, etc. The first set of taps has a low-pass frequency response. Select several frequencies to verify the frequency response. Approximate the frequency response of the other three filter sets. For each of the four sets, sketch the frequency response (magnitude vs frequency.) Include the sketches in your report. Task 6 (for individuals: bonus, 1 point; for teams: required, 0.75 points) Expand Task 5 to display a bar on the screen that has a height proportional to the moving-average result. The magnitude needs to be scaled differently than Task 3. When the scaled-magnitude of the filter output is at the maximum theoretical value, the height of the bar is just below 480 pixels. When the scaled magnitude of the filter output is 0, the height is 0 pixels. The bar width is 10 pixels wide. The horizontal position of the bar is determined by switches [5:0]. When the switches are all 0, the bar spans from 0 to 9 pixels in the horizontal axis. When the switches are all 1, the bar spans from 630 to 639 pixels in the horizontal axis. Thus the bars horizontal position indicates the frequency of the NCO.

Task 7 (for individuals: bonus, 1 point; for teams: required, 0.75 points) Expand Task 6 to show one of three internal values on an oscilloscope using an 8-bit parallel digital-to-analog converter (DAC): NCO output, Filter output, or the magnitude output. Signed inputs must be converted to biased unsigned representation. Then they need to be scaled so that the full-scale range is within the 8-bit DAC range. Button[0] cycles through the three choices. When the NCO is selected, also turn on LED[0]. When the filter output is selected, also turn on LED[1]. When the magnitude output is selected, also turn on LED[2]. The DAC isnt supplied in the ECE448 kit; you must purchase it separately. To properly analyze the timing, all the used FPGA inputs must be registered before they are used by logic, and all outputs must be registered before leaving the FPGA.

For the all tasks, determine the following properties: 1. Number of CLB slices 2. Minimum clock period after synthesis [ns] 3. Maximum clock frequency after synthesis [MHz] 4. Minimum clock period after implementation [ns] 5. Maximum clock frequency after implementation [MHz] 6. Minimum latency after implementation [ns] As a part of the design process: 1. Draw an optimized block diagram of your NCO, filter, magnitude and scaling, bar fill, and DAC driver circuits. 2. Translate your block diagram (and the rest of the circuits) into RTL VHDL. 3. Write a separate testbench capable of verifying the functionality of the circuits. 4. Synthesize, implement, and load your design on the Basys board to verify functionality. In the lab report include: 1. Optimized block diagrams (hand-drawn hardcopy submitted in class and used during an exit quiz, and an electronic copy submitted using Blackboard in the pdf or MS Word format (preferably, the scanned version of the hand-drawn hardcopy.) 2. Electronic copy of the frequency response of each of the four filter sets. 3. VHDL source codes for: a. Sine wave generator (NCO) b. Filter c. Magnitude, scaling, and averaging d. Bar Fill e. DAC Driver f. VGA Sync generator g. Clock management unit h. Top Level Unit 4. User Constraint File (UCF) 5. Testbench and waveforms from the functional simulation (electronic versions submitted using Blackboard) for the last Task that you implement. The testbench should exercise most of the functionality of the design.

Monday Section Introduction to the Experiment Demonstration and Deliverables Due (Schedule A) Demonstration and Deliverables Due (Schedule B)** 04/04/2011 04/18/2011 05/02/2011

Tuesday Section 04/05/2011 04/19/2011 05/03/2011

Wednesday Section 04/06/2011 04/20/2011 05/04/2011

Thursday Section 04/07/2011 04/21/2011 05/05/2011

You might also like

- EECT6306 Miidterm Project Harshit VamshiDocument13 pagesEECT6306 Miidterm Project Harshit Vamshiafrica threeNo ratings yet

- DSPACE Procedure With MPPT ExampleDocument21 pagesDSPACE Procedure With MPPT ExampleSri SriNo ratings yet

- Tutorial: Introduction To DSP Using Sysgen and Introductory AssignmentDocument11 pagesTutorial: Introduction To DSP Using Sysgen and Introductory AssignmentshivaspyNo ratings yet

- Vlsi Lab Manual 2013Document64 pagesVlsi Lab Manual 2013harish33330% (1)

- Experiment 08 Interfacing Codec TLV320AIC23, and Use of DAC and ADCDocument6 pagesExperiment 08 Interfacing Codec TLV320AIC23, and Use of DAC and ADCOmar JanjuaNo ratings yet

- Hardware-Software Codesign Lab ReportDocument15 pagesHardware-Software Codesign Lab ReportvaljokNo ratings yet

- Lab # 06 - 07Document6 pagesLab # 06 - 07Hamza AliNo ratings yet

- Matlab 6713Document15 pagesMatlab 6713ameiyappan5697No ratings yet

- 2010 CASPER Workshop: Tutorial 4: Wideband PocoDocument16 pages2010 CASPER Workshop: Tutorial 4: Wideband PocotrabajadosNo ratings yet

- Ece574 2015 Light Sensor VGA ProjectDocument4 pagesEce574 2015 Light Sensor VGA Projectmanik9000No ratings yet

- VLSI Design For Test/Power Spring 2017 Project 4: Chip Testing Lab Final Reports Due On 11:59pm, 4/30/2017Document5 pagesVLSI Design For Test/Power Spring 2017 Project 4: Chip Testing Lab Final Reports Due On 11:59pm, 4/30/2017srikar_dattaNo ratings yet

- Interrupts/Polling and Input/Output With The DSK Codec: Pre-LabDocument4 pagesInterrupts/Polling and Input/Output With The DSK Codec: Pre-LabrkNo ratings yet

- LGLite ATE 93C46Document10 pagesLGLite ATE 93C46Vijayakumar SNo ratings yet

- Cdma Reverselink Waveform Generator Fpga For Production Transmit Path TestsDocument9 pagesCdma Reverselink Waveform Generator Fpga For Production Transmit Path Testsxiao zhanNo ratings yet

- Analog - Sine Wave Generation With Psoc 1 (Demonstration With CTCSS)Document11 pagesAnalog - Sine Wave Generation With Psoc 1 (Demonstration With CTCSS)Adonis LealNo ratings yet

- DSP Lab ManualDocument84 pagesDSP Lab ManualGowtham Raj100% (2)

- 56F80x Resolver Driver and Hardware Interface: Application NoteDocument28 pages56F80x Resolver Driver and Hardware Interface: Application NoteMarco Trujillo ÜNo ratings yet

- Tutorial ProjectDocument16 pagesTutorial ProjectMuhammadNizarArifansyahNo ratings yet

- DSP Lab 2Document5 pagesDSP Lab 2Sourabh SuriNo ratings yet

- IMA ADPCM EncDec Core SpecificationsDocument11 pagesIMA ADPCM EncDec Core SpecificationsMaria MafteiNo ratings yet

- Question Bank DSD III SemDocument4 pagesQuestion Bank DSD III Semasymtodegaming0501No ratings yet

- System Generator TutorialDocument33 pagesSystem Generator TutorialAthul KsNo ratings yet

- Infineon-Component - Segment - LCD - (SegLCD) - V3.20-Software Module Datasheets-V03 - 04-ENDocument35 pagesInfineon-Component - Segment - LCD - (SegLCD) - V3.20-Software Module Datasheets-V03 - 04-ENAlhassan Ahmed OmranNo ratings yet

- Crestron Intermediate TrainingDocument28 pagesCrestron Intermediate TrainingRiten JaiswalNo ratings yet

- PROJECT #1: SRAM Design and Layout: EE 7325 Advanced VLSI DesignDocument1 pagePROJECT #1: SRAM Design and Layout: EE 7325 Advanced VLSI DesignNandeesh GowdaNo ratings yet

- StopwatchDocument40 pagesStopwatchMani SinghNo ratings yet

- Lab Sheet 4Document3 pagesLab Sheet 498140207No ratings yet

- Avr CoreDocument145 pagesAvr CoreStephanie FloresNo ratings yet

- Lab 1 - OLED, GPIO, InterruptDocument6 pagesLab 1 - OLED, GPIO, Interruptprakash_shrNo ratings yet

- Lab 7 UART DesignDocument6 pagesLab 7 UART Designaditya220No ratings yet

- Interviews Question For Physical Design: Digital Design Interview QuestionsDocument44 pagesInterviews Question For Physical Design: Digital Design Interview QuestionsPavan Raj100% (1)

- ECE3073 2014 Lab 3Document5 pagesECE3073 2014 Lab 3Andrew WalleyNo ratings yet

- DFT VisionDocument18 pagesDFT VisionNaganithesh Ghattamaneni0% (1)

- Experiment 9: Frame - Based ProcessingDocument7 pagesExperiment 9: Frame - Based ProcessingTsega TeklewoldNo ratings yet

- DSP Lab 21-09-2021Document78 pagesDSP Lab 21-09-2021POORNIMA PNo ratings yet

- ATMEGA8 Expt 1Document2 pagesATMEGA8 Expt 1कुलदीप पुरोहितNo ratings yet

- Fidel Certuche Lab 5 Report ISCD (Extra Image)Document15 pagesFidel Certuche Lab 5 Report ISCD (Extra Image)fidel.certucheNo ratings yet

- DSP Lab With Ti c6x DSP and c6713 DSK 6.3Document116 pagesDSP Lab With Ti c6x DSP and c6713 DSK 6.3Twinkle RatnaNo ratings yet

- PSoC Lab1Document10 pagesPSoC Lab1rednejetNo ratings yet

- PG HelpDocument121 pagesPG HelpraghavendraNo ratings yet

- CSE20221 Keyboard Interface ProjectDocument2 pagesCSE20221 Keyboard Interface ProjectpranjalNo ratings yet

- Vlsi Manual 2013-2014Document36 pagesVlsi Manual 2013-2014hr_suresh_kNo ratings yet

- SVA Excercise 1Document9 pagesSVA Excercise 1sujaataNo ratings yet

- EC8711 Embedded Lab Manual FinalDocument258 pagesEC8711 Embedded Lab Manual FinalbloomeceNo ratings yet

- Verilog AMS TutorialDocument29 pagesVerilog AMS TutorialSiva KrishnaNo ratings yet

- Lab 3 - Signal RoutingDocument5 pagesLab 3 - Signal RoutingkyfeeeNo ratings yet

- FPGA Lab 07Document14 pagesFPGA Lab 07Zain AlamgirNo ratings yet

- LNA Simulation Using Cadence Specter RFDocument26 pagesLNA Simulation Using Cadence Specter RFMukesh KumarNo ratings yet

- Using NI System Identification, Control Design, and Simulation Products For Design - National InstrumentsDocument12 pagesUsing NI System Identification, Control Design, and Simulation Products For Design - National InstrumentsEdwin AguilarNo ratings yet

- 3-Phase Switched Reluctance Motor Control With Encoder Using DSP56F80xDocument56 pages3-Phase Switched Reluctance Motor Control With Encoder Using DSP56F80xYusuf Ilker öztürkNo ratings yet

- H.265 High Efficiency Video Coding (HEVC) : Presented byDocument29 pagesH.265 High Efficiency Video Coding (HEVC) : Presented bybleach786_fan100% (1)

- 32-Channel Waveform Generator Implemented Using Actel's Axcelerator FPGADocument13 pages32-Channel Waveform Generator Implemented Using Actel's Axcelerator FPGASrinivas CherukuNo ratings yet

- DFT DocumentationDocument20 pagesDFT Documentationyamini100% (1)

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- 25 SohJDocument1 page25 SohJZisa KrageNo ratings yet

- 25 SohJDocument1 page25 SohJZisa KrageNo ratings yet

- Lecture 12Document10 pagesLecture 12Zisa KrageNo ratings yet

- B 0119011213Document3 pagesB 0119011213Zisa KrageNo ratings yet

- A 256 Channel Control System Using Fpgas and A PLD: Dave Delauter, Consultant DeltatDocument4 pagesA 256 Channel Control System Using Fpgas and A PLD: Dave Delauter, Consultant DeltatZisa KrageNo ratings yet

- MC 145436 APDocument8 pagesMC 145436 APRobert SepulvedaNo ratings yet

- Serial + Crack READ MEDocument2 pagesSerial + Crack READ MEtoza74100% (1)

- Harris Falcon III RF 7800v HH Handheld VHF Tactical Radio BrochureDocument6 pagesHarris Falcon III RF 7800v HH Handheld VHF Tactical Radio BrochureDamian Marley0% (1)

- Cellular Neural Networks: Theory: Stability AnalysisDocument16 pagesCellular Neural Networks: Theory: Stability AnalysisMauricio RamosNo ratings yet

- Syllabus EC5001 Embedded SystemsDocument3 pagesSyllabus EC5001 Embedded Systemskavish malakaNo ratings yet

- Kertas PeneranganDocument37 pagesKertas PeneranganPaul KennyNo ratings yet

- Investigation - of - 3G IRAT CS Handover Degradation Due To Iphone 5Document9 pagesInvestigation - of - 3G IRAT CS Handover Degradation Due To Iphone 5Akhtar KhanNo ratings yet

- Operator E-Jets News Rel 20Document11 pagesOperator E-Jets News Rel 20PDDELUCANo ratings yet

- df-550 O2 AnalyzerDocument4 pagesdf-550 O2 AnalyzerCaleb SpiderNo ratings yet

- SLC Wiring Manual-51253Document80 pagesSLC Wiring Manual-51253teum3250% (8)

- CDX C7850R PDFDocument70 pagesCDX C7850R PDFBila Nicola Florin SorinNo ratings yet

- Cblephsu 03Document6 pagesCblephsu 03Saheb PriyadarshiNo ratings yet

- ESD StandardsDocument2 pagesESD StandardsAtif JaveadNo ratings yet

- Wide Swing Cascode Current MirrorDocument4 pagesWide Swing Cascode Current MirrorSunil M. PaiNo ratings yet

- Dynamini Series Adhesive Supply UnitDocument2 pagesDynamini Series Adhesive Supply UnitITWDynatecNo ratings yet

- Intel LGA 2011 - Square ILM LGA 2066Document2 pagesIntel LGA 2011 - Square ILM LGA 2066Dejan NNo ratings yet

- JVC Dr-m1 Service ManualDocument116 pagesJVC Dr-m1 Service ManualvideosonNo ratings yet

- Eee DSP 2 MarksDocument24 pagesEee DSP 2 Marksselvakumargeorg1722No ratings yet

- Unit-3 Wiring SystemDocument97 pagesUnit-3 Wiring SystemAayushi Goyal100% (1)

- Aucr 2013Document81 pagesAucr 2013Anonymous D5OSzzfNo ratings yet

- Instrumentation EarthingDocument13 pagesInstrumentation EarthingTrung TrầnNo ratings yet

- Chapter 10Document60 pagesChapter 10jhade_cabato100% (1)

- Balanza Analitica Ohaus EP214CDocument44 pagesBalanza Analitica Ohaus EP214CJulio Cesar Avila Garcia50% (2)

- Drain Induced Barrier Lowering - Wikipedia, The Free EncyclopediaDocument2 pagesDrain Induced Barrier Lowering - Wikipedia, The Free EncyclopediatheodorechandraNo ratings yet

- 10 Atomic StructureDocument9 pages10 Atomic StructurearcNo ratings yet

- Festo Motion FHPP Step7 V5 5 enDocument48 pagesFesto Motion FHPP Step7 V5 5 enAlejandroLeumanNo ratings yet

- Ee101 Basics of Electrical Engineering (End - SP19)Document2 pagesEe101 Basics of Electrical Engineering (End - SP19)soronaj532No ratings yet

- Bioactive Glass Cosmetics UsesDocument2 pagesBioactive Glass Cosmetics UsesagdalineroNo ratings yet

- Napolcom Exam ReviewerDocument15 pagesNapolcom Exam ReviewerIrene FriasNo ratings yet

- HW 316953Document3 pagesHW 316953carlosconstructor1No ratings yet