Professional Documents

Culture Documents

Logic Design July 2013

Uploaded by

Prasad C MCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Logic Design July 2013

Uploaded by

Prasad C MCopyright:

Available Formats

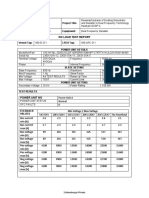

USN

06cs33

(08 Marks)

(08 Marks)

(04 Marks)

(05 Marks)

(05 Marks)

Third Semester B.E. Degree Examination, June/July 2013

Logic Design

a

I

E9

gor

"5

-bi

5r

o.a

d;

d .9.

a!

a,i

:s

-;o

o

z

6

ts

q

E

Time: 3 hrs.

.':..

Max. Marks:1O0

Notez Answer FIYE

full

questions, selecting

atleast TWO questions

lfrom

each part.

PART_A

I a. Why NAND and NOR gates are universal gates? Simptifo the following Boolean

expression using k

-

map and implement the same using

i) NAND gates only (SOP form)

ii) NOR gates only

IPOS

form

)

.

F(A, B C,D)

-

>* (0;1, 2,4, s,12,14)

+

dc(8, 10). (r0 Marks)

b.

Find the prime implicants and essential prime implicants for the following Boolean

expression using

Quine

McClusky's method.

F(A,B,C,D):r',,(1,3,6,7,9,10,

12, 13, 14, 15). (l0Marks)

a. Realize the Boolean expression

l.

F(A, B, C, D): t'. = (2.3.4,5, 13. 15)

+

dc(8, 9, 10, 11) using 8 : I multiplexers and

external gates.

b.

Generate the Boolean expression for

...

a. Design a 2

-bit

carry look ahead adder and explain, with an eprnple. (10 Marks)

b. Draw the block diagram of4

-

bit adder/ subtractor circuit using full adder and explain the

Yo

:

A' B', yr

:

ABC, yz = dg, y:

:49'

C using PROM.

c. Write the HDL code for full adder.

same.

c. Compute the sum in each of the following :

i) 7s+38

ii) 8r6

+

Fr6.

a. What is a fliplfop? Explain the different types of flipflops

diagram, and excitation table.

b. Convert the SR flipflop into JK and D flipflops.

c. Write a note on edge trigged flipflps.

along with truth table, circuit

(10 Marks)

(06 Marks)

(04 Mrrks)

PART

_

B

5 a. What is a register? Explain the tlpes of register along with their applications.

b. Design a synckonous mod- 5 counter using JK flipflop.

c. What are presettable counters? Explain with an example.

(10 Marks)

(05 Marks)

(05 Marks)

1of 2

For More Question Papers Visit - www.pediawikiblog.com

For More Question Papers Visit - www.pediawikiblog.com

www.pediawikiblog.com

r1

I

06cs33

6 a. Differentiate Mealy and Moore models. (05 Marks)

b. Design an aslmchronous sequential logic circuit for the following state transition diagram.

I _

(05 Mar(5)

-X:d,!--

..'r,\ I

^

i-".+"

$f-_

ff{'

=$do1ta,tt

-..*}

'4^-

r1g.

Qo(b)

-&"

\*r

c. Draw the'sffi,trarsition diagram by row elimination method foy!*toilowinS :

dr:1

-

r' ,,i

'd

.t.

,lr

/o

dS

Fig'

Q6&[

-=." (roMarks)

a. Draw and exptqirFtd4-Uit binary ladder D/A converter. C.,:

(t0 Marks)

b. Discuss any twQ)Gthods of A,/D conversim.

'q{"

(r0 Marks)

*se

*'i;-.

a. Defure(lflTl parameters ii) Open

-

collector gate.

-, t

(05 Marks)

b. WhA{W CMOS characteristics? Explain.

l,

}

(05 Marks)

".

ffih"

aid of a circuit diagram, explain the operation of a 2

-

input Ttl,

$.gND

gate with

_*.p*op"n

-.ollector

method.

'

"5,f0

urarr<g

r{*

""f

I

***rr*

-t'lt.

'.''a&*

2 of2

Fie.

Q6(b)

For More Question Papers Visit - www.pediawikiblog.com

For More Question Papers Visit - www.pediawikiblog.com

www.pediawikiblog.com

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Powerflex 525 Adjustable Frequency Ac DriveDocument5 pagesPowerflex 525 Adjustable Frequency Ac DriveJaime RamosNo ratings yet

- 2nd PUC Physics Mid Term Nov 2015 PDFDocument1 page2nd PUC Physics Mid Term Nov 2015 PDFPrasad C M82% (11)

- 2nd PUC Mathematics Mid Term Nov 2015 PDFDocument3 pages2nd PUC Mathematics Mid Term Nov 2015 PDFPrasad C M60% (10)

- 2nd PUC Kannada Jan 2016 PDFDocument2 pages2nd PUC Kannada Jan 2016 PDFPrasad C M81% (16)

- 2nd PUC Mathematics Jan 2016 PDFDocument2 pages2nd PUC Mathematics Jan 2016 PDFPrasad C M100% (3)

- 2nd PUC Kannada Mide Term Nov 2015 PDFDocument2 pages2nd PUC Kannada Mide Term Nov 2015 PDFPrasad C M100% (5)

- 2nd PUC PhysicsJan 2016 PDFDocument2 pages2nd PUC PhysicsJan 2016 PDFPrasad C M90% (10)

- 2nd PUC English Mid Term Nov 2015 PDFDocument4 pages2nd PUC English Mid Term Nov 2015 PDFPrasad C M78% (9)

- 2nd PUC Chemistry Jan 2016 PDFDocument2 pages2nd PUC Chemistry Jan 2016 PDFPrasad C M83% (6)

- 2nd PUC Biology Jan 2016 PDFDocument2 pages2nd PUC Biology Jan 2016 PDFPrasad C M89% (9)

- 2nd PUC English Jan 2016 PDFDocument4 pages2nd PUC English Jan 2016 PDFPrasad C M86% (14)

- 2nd PUC Biology Mid Term Nov 2015 PDFDocument1 page2nd PUC Biology Mid Term Nov 2015 PDFPrasad C M78% (9)

- 2nd PUC Chemistry Mid Term Nov 2015 PDFDocument2 pages2nd PUC Chemistry Mid Term Nov 2015 PDFPrasad C M100% (8)

- 2nd Sem DIP Appied Mathematics 2 - May 2015 PDFDocument4 pages2nd Sem DIP Appied Mathematics 2 - May 2015 PDFPrasad C M100% (8)

- 2nd Sem DIP Electrical Circuits - Dec 2015 PDFDocument3 pages2nd Sem DIP Electrical Circuits - Dec 2015 PDFPrasad C M100% (1)

- 2nd Sem DIP Applied Maths 2 - Dec 2015 PDFDocument4 pages2nd Sem DIP Applied Maths 2 - Dec 2015 PDFPrasad C M89% (9)

- 2nd Sem DIP Electrical Circuits - May 2015 PDFDocument4 pages2nd Sem DIP Electrical Circuits - May 2015 PDFPrasad C M100% (1)

- 2nd Sem DIP Electrical Circuits - May 2013 PDFDocument3 pages2nd Sem DIP Electrical Circuits - May 2013 PDFPrasad C M100% (2)

- 2nd Sem DIP Electrical Circuits - Dec 2012 PDFDocument4 pages2nd Sem DIP Electrical Circuits - Dec 2012 PDFPrasad C MNo ratings yet

- 1st Year DIP Communication Skills in English - Dec 2015 PDFDocument4 pages1st Year DIP Communication Skills in English - Dec 2015 PDFPrasad C M100% (7)

- 2nd Sem DIP Electrical Circuits - May 2011 PDFDocument3 pages2nd Sem DIP Electrical Circuits - May 2011 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electrical Circuits - Dec 2014 PDFDocument3 pages2nd Sem DIP Electrical Circuits - Dec 2014 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electrical Circuits - May 2010 PDFDocument3 pages2nd Sem DIP Electrical Circuits - May 2010 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electrical Circuits - Dec 2013 PDFDocument3 pages2nd Sem DIP Electrical Circuits - Dec 2013 PDFPrasad C M100% (1)

- 2nd SEM Electronics 1 - May 2012 PDFDocument2 pages2nd SEM Electronics 1 - May 2012 PDFPrasad C MNo ratings yet

- 2nd SEM Electronics 1 - Dec 2014 PDFDocument3 pages2nd SEM Electronics 1 - Dec 2014 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electronics 1 - Dec 2015 PDFDocument3 pages2nd Sem DIP Electronics 1 - Dec 2015 PDFPrasad C MNo ratings yet

- 2nd SEM Electronics 1 - Nov 2011 PDFDocument3 pages2nd SEM Electronics 1 - Nov 2011 PDFPrasad C MNo ratings yet

- 2nd SEM Electronics 1 - May 2011 PDFDocument2 pages2nd SEM Electronics 1 - May 2011 PDFPrasad C MNo ratings yet

- ManualDocument69 pagesManualfrankfrank0% (1)

- Sensor de CorrenteDocument3 pagesSensor de Correntejcarlos710No ratings yet

- Finite Word Length Effect in IIR FiltersDocument13 pagesFinite Word Length Effect in IIR Filterstipo_de_incognitoNo ratings yet

- Hybrid Power Boost (HPB) and Narrow VDC (NVDC) Combo Battery Charger With Smbus InterfaceDocument2 pagesHybrid Power Boost (HPB) and Narrow VDC (NVDC) Combo Battery Charger With Smbus InterfaceSelmar Cavalcanti0% (1)

- Am Loop Antennas 2004Document355 pagesAm Loop Antennas 2004Mario OlivieriNo ratings yet

- Microprocessors and MicrocontrollersDocument22 pagesMicroprocessors and Microcontrollers6012 ANILNo ratings yet

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument32 pages24AA02/24LC02B: 2KI C Serial EEPROMhanifNo ratings yet

- Sharp 27N - S100 Chasis SN - 91Document44 pagesSharp 27N - S100 Chasis SN - 91Pablo Acapulco GuerreroNo ratings yet

- Ict Chapter 2Document9 pagesIct Chapter 2Izwan Jamaluddin33% (3)

- CounterpoiseDocument12 pagesCounterpoiseAlok BhaskarNo ratings yet

- PV TutorialDocument4 pagesPV TutorialKVVNo ratings yet

- Nov P/N Yaskawa P/N Description Inter-Co Cost 60RJDocument4 pagesNov P/N Yaskawa P/N Description Inter-Co Cost 60RJRicardo VillarNo ratings yet

- ActantfetDocument7 pagesActantfetlu1agpNo ratings yet

- CS 152 Laboratory Exercise 1 (Directed Portion Only) : 1 Introduction and GoalsDocument15 pagesCS 152 Laboratory Exercise 1 (Directed Portion Only) : 1 Introduction and GoalsVinay PrasanthNo ratings yet

- Practical 2.1 & 2.2 - Transistor Suis & AmplifierDocument13 pagesPractical 2.1 & 2.2 - Transistor Suis & AmplifierJamuna RaniNo ratings yet

- The Valve Wizard: How To Design Valve Guitar Amplifiers!Document3 pagesThe Valve Wizard: How To Design Valve Guitar Amplifiers!Diego García MedinaNo ratings yet

- The DIY Pic ProgrammerDocument6 pagesThe DIY Pic Programmerdiego100% (1)

- Experiment 6 Southern Luzon State UDocument5 pagesExperiment 6 Southern Luzon State UIanElieserCometaNo ratings yet

- Lecture 2Document39 pagesLecture 2benazir masukatNo ratings yet

- Lecture NotesDocument1 pageLecture Notessatishbojjawar14840% (1)

- Modeling and Simulation of SSPC Based On Dymola Software and Modelica LanguageDocument5 pagesModeling and Simulation of SSPC Based On Dymola Software and Modelica LanguageWilliam Jaldin CorralesNo ratings yet

- Esab LAR 500-630 Magma ServicemanualDocument64 pagesEsab LAR 500-630 Magma ServicemanualTommy MellemstrandNo ratings yet

- Jurnal Mikrokontroller 12e45Document6 pagesJurnal Mikrokontroller 12e45aviliana bintariNo ratings yet

- 26 Jun 2019 18 - BERC Loading DetailsDocument31 pages26 Jun 2019 18 - BERC Loading DetailsChief Engineer TransOMNo ratings yet

- No Load Test Report PDFDocument3 pagesNo Load Test Report PDFYusmin JusohNo ratings yet

- Unit - Ii Modeling of Various Components / Accessories ObjectivesDocument43 pagesUnit - Ii Modeling of Various Components / Accessories ObjectivessarathikklNo ratings yet

- Schema IBM R60Document92 pagesSchema IBM R60Eva Beti PetreNo ratings yet

- Electrical and Electronics Engineer Job DescriptionDocument3 pagesElectrical and Electronics Engineer Job DescriptionsathyavlrNo ratings yet

- 38C44YMDocument11 pages38C44YMbehzadNo ratings yet