Professional Documents

Culture Documents

Computer Memory: How RAM Works Random Access Memory (RAM) Is The Best Known Form of

Uploaded by

vikasrampal99Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Computer Memory: How RAM Works Random Access Memory (RAM) Is The Best Known Form of

Uploaded by

vikasrampal99Copyright:

Available Formats

How RAM Works Random access memory (RAM) is the best known form of computer memory.

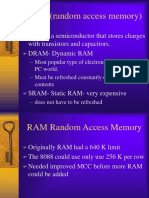

RAM is considered "random access" because you can access any memory cell directly if you know the row and column that intersect at that cell. The opposite of RAM is serial access memory (SAM). SAM stores data as a series of memory cells that can only be accessed sequentially (like a cassette tape). f the data is not in the current location! each memory cell is checked until the needed data is found. SAM works "ery well for memory buffers! where the data is normally stored in the order in which it will be used (a #ood e$ample is the te$ture buffer memory on a "ideo card). RAM data! on the other hand! can be accessed in any order. n this article! you%ll learn all about what RAM is! what kind you should buy and how to install it. Dynamic RAM Similar to a microprocessor! a memory chip is an integrated circuit ( &) made of millions of transistors and capacitors. n the most common form of computer memory! dynamic random access memory ('RAM)! a transistor and a capacitor are paired to create a memory cell! which represents a sin#le bit of data. The capacitor holds the bit of information (( a ) or a * (see +ow ,its and ,ytes -ork for information on bits). The transistor acts as a switch that lets the control circuitry on the memory chip read the capacitor or chan#e its state. A capacitor is like a small bucket that is able to store electrons. To store a * in the memory cell! the bucket is filled with electrons. To store a )! it is emptied. The problem with the capacitor%s bucket is that it has a leak. n a matter of a few milliseconds a full bucket becomes empty. Therefore! for dynamic memory to work! either the &./ or the memory controller has to come alon# and rechar#e all of the capacitors holdin# a * before they dischar#e. To do this! the memory controller reads the memory and then writes it ri#ht back. This refresh operation happens automatically thousands of times per second. This refresh operation is where dynamic RAM #ets its name. 'ynamic RAM has to be dynamically refreshed all of the time or it for#ets what it is holdin#. The downside of all of this refreshin# is that it takes time and slows down the memory. Memory cells are etched onto a silicon wafer in an array of columns ( bitlines) and rows (wordlines). The intersection of a bitline and wordline constitutes the address of the memory cell. 'RAM works by sendin# a char#e throu#h the appropriate column (&AS) to acti"ate the transistor at each bit in the column. -hen writin#! the row lines contain the state the capacitor should take on. -hen readin#! the sense(amplifier determines the le"el of char#e in the capacitor. f it is more than 0) percent! it reads it as a *1 otherwise it reads it as a ). The counter tracks the refresh sequence based on which rows ha"e been accessed in what order. The len#th of time necessary to do all this is so short that it is e$pressed in nanoseconds (billionths of a second). A memory chip ratin# of 2)ns means that it takes 2) nanoseconds to completely read and rechar#e each cell. Memory cells alone would be worthless without some way to #et information in and out of them. So the memory cells ha"e a whole support infrastructure of other speciali3ed circuits. These circuits perform functions such as4 dentifyin# each row and column (row address select and column address select) 5eepin# track of the refresh sequence (counter) Readin# and restorin# the si#nal from a cell (sense amplifier) Tellin# a cell whether it should take a char#e or not ( write enable) 6ther functions of the memory controller include a series of tasks that include identifyin# the type! speed and amount of memory and checkin# for errors. Static RAM works differently from 'RAM.

Types of RAM

The type of board and connector used for RAM in desktop computers has e"ol"ed o"er the past few years. The first types were proprietary! meanin# that different computer manufacturers de"eloped memory boards that would only work with their specific systems. Then came SIMM! which stands for single in line memory module. This memory board used a 7)(pin connector and was about 7.0 $ .20 inches in si3e (about 8 $ 9 cm). n most computers! you had to install S MMs in pairs of equal capacity and speed. This is because the width of the bus is more than a sin#le S MM. :or e$ample! you would install two ;(me#abyte (M,) S MMs to #et *< me#abytes total RAM. =ach S MM could send ; bits of data at one time! while the system bus could handle *< bits at a time. >ater S MM boards! sli#htly lar#er at ?.90 $ * inch (about ** $ 9.0 cm)! used a 29(pin connector for increased bandwidth and allowed for up to 90< M, of RAM.

!rom the top" SIMM# DIMM and S$DIMM memory modules As processors #rew in speed and bandwidth capability! the industry adopted a new standard in dual in line memory module (' MM). -ith a whoppin# *<;(pin or *;?(pin connector and a si3e of 0.? $ * inch (about *? $ 9.0 cm)! ' MMs ran#e in capacity from ; M, to * @, per module and can be installed sin#ly instead of in pairs. Most .& memory modules and the modules for the Mac @0 systems operate at 9.0 "olts! while older Mac @? systems typically use 7.7 "olts. Another standard! Rambus in line memory module (R MM)! is comparable in si3e and pin confi#uration to ' MM but uses a special memory bus to #reatly increase speed. Many brands of notebook computers use proprietary memory modules! but se"eral manufacturers use RAM based on the small outline dual in line memory module (S6' MM) confi#uration. S6' MM cards are small! about 9 $ * inch (0 $ 9.0 cm)! and ha"e *?? or 9)) pins. &apacity ran#es from *< M, to * @, per module. To conser"e space! the Apple iMac desktop computer uses S6' MMs instead of the traditional ' MMs. Sub(notebook computers use e"en smaller ' MMs! known as Micro' MMs! which ha"e either *?? pins or *29 pins. Most memory a"ailable today is hi#hly reliable. Most systems simply ha"e the memory controller check for errors at start(up and rely on that. Memory chips with built(in error(checkin# typically use a method known as parity to check for errors. .arity chips ha"e an e$tra bit for e"ery ; bits of data. The way parity works is simple. >et%s look at e%en parity first. -hen the ; bits in a byte recei"e data! the chip adds up the total number of *s. f the total number of *s is odd! the parity bit is set to *. f the total is e"en! the parity bit is set to ). -hen the data is read back out of the bits! the total is added up a#ain and compared to the parity bit. f the total is odd and the parity bit is *! then the data is assumed to be "alid and is sent to the &./. ,ut if the total is odd and the parity bit is )! the chip knows that there is an error somewhere in the ; bits and dumps the data. $dd parity works the same way! but the parity bit is set to * when the total number of *s in the byte are e"en. The problem with parity is that it disco"ers errors but does nothin# to correct them. f a byte of data does not match its parity bit! then the data are discarded and the system tries a#ain. &omputers in critical positions need a hi#her le"el of fault tolerance. +i#h(end ser"ers often ha"e a form of error(checkin# known as error correction code (=&&). >ike parity! =&& uses additional bits to monitor the data in each byte. The difference is that =&& uses se"eral bits for error checkin# (( how many depends on the width of the bus (( instead of one. =&& memory uses a special al#orithm not only to detect sin#le bit errors! but actually correct them as well. =&& memory will also detect instances when more than one bit of data in a byte fails. Such failures are "ery rare! and they are not correctable! e"en with =&&. The maAority of computers sold today use nonparity memory chips. These chips do not pro"ide any type of built(in error checkin#! but instead rely on the memory controller for error detection. The followin# are some common types of RAM4

SRAM4 Static random access memory uses multiple transistors! typically four to si$! for each memory cell but doesn%t ha"e a capacitor in each cell. t is used primarily for cache. DRAM4 Dynamic random access memory has memory cells with a paired transistor and capacitor requirin# constant refreshin#.

!&M DRAM4 !ast page mode dynamic random access memory was the ori#inal form of 'RAM. t waits throu#h the entire process of locatin# a bit of data by column and row and then readin# the bit before it starts on the ne$t bit. Ma$imum transfer rate to >9 cache is appro$imately *2< M,ps. 'D$ DRAM4 '(tended data out dynamic random access memory does not wait for all of the processin# of the first bit before continuin# to the ne$t one. As soon as the address of the first bit is located! ='6 'RAM be#ins lookin# for the ne$t bit. t is about fi"e percent faster than :.M. Ma$imum transfer rate to >9 cache is appro$imately 9<? M,ps. SDRAM4 Synchronous dynamic random access memory takes ad"anta#e of the burst mode concept to #reatly impro"e performance. t does this by stayin# on the row containin# the requested bit and mo"in# rapidly throu#h the columns! readin# each bit as it #oes. The idea is that most of the time the data needed by the &./ will be in sequence. S'RAM is about fi"e percent faster than ='6 RAM and is the most common form in desktops today. Ma$imum transfer rate to >9 cache is appro$imately 09; M,ps. DDR SDRAM4 Double data rate synchronous dynamic RAM is Aust like S'RAM e$cept that is has hi#her bandwidth! meanin# #reater speed. Ma$imum transfer rate to >9 cache is appro$imately *!)<? M,ps (for ''R S'RAM *77 M+B). RDRAM4 Rambus dynamic random access memory is a radical departure from the pre"ious 'RAM architecture. 'esi#ned by Rambus! R'RAM uses a Rambus in line memory module )RIMM*! which is similar in si3e and pin confi#uration to a standard ' MM. -hat makes R'RAM so different is its use of a special hi#h(speed data bus called the Rambus channel. R'RAM memory chips work in parallel to achie"e a data rate of ;)) M+3! or *!<)) M,ps. Since they operate at such hi#h speeds! they #enerate much more heat than other types of chips. To help dissipate the e$cess heat Rambus chips are fitted with a heat spreader! which looks like a lon# thin wafer. Cust like there are smaller "ersions of ' MMs! there are also S6(R MMs! desi#ned for notebook computers. +redit +ard Memory4 &redit card memory is a proprietary self(contained 'RAM memory module that plu#s into a special slot for use in notebook computers. &+M+IA Memory +ard4 Another self(contained 'RAM module for notebooks! cards of this type are not proprietary and should work with any notebook computer whose system bus matches the memory card%s confi#uration. +M$S RAM4 &M6S RAM is a term for the small amount of memory used by your computer and some other de"ices to remember thin#s like hard disk settin#s (( see -hy does my computer need a batteryD :or details. This memory uses a small battery to pro"ide it with the power it needs to maintain the memory contents. ,RAM4 ,ideoRAM! also known as multiport dynamic random access memory (M.'RAM)! is a type of RAM used specifically for "ideo adapters or 7(' accelerators. The "multiport" part comes from the fact that ERAM normally has two independent access ports instead of one! allowin# the &./ and #raphics processor to access the RAM simultaneously. ERAM is located on the #raphics card and comes in a "ariety of formats! many of which are proprietary. The amount of ERAM is a determinin# factor in the resolution and color depth of the display. ERAM is also used to hold #raphics(specific information such as 7(' #eometry data and te$ture maps. True multiport ERAM tends to be e$pensi"e! so today1 many #raphics cards use S-RAM (synchronous #raphics RAM) instead. .erformance is nearly the same! but S@RAM is cheaper.

You might also like

- How RAM Works: Random Access Memory (RAM) Is The Best Known Form ofDocument9 pagesHow RAM Works: Random Access Memory (RAM) Is The Best Known Form ofamirvillasNo ratings yet

- How RAM WorksDocument8 pagesHow RAM Worksapi-19737301No ratings yet

- How RAM WorksDocument3 pagesHow RAM WorksMohamed Hussain100% (2)

- How RAM Works 28 by NafeesDocument10 pagesHow RAM Works 28 by NafeesnafeesNo ratings yet

- E2805 B 43Document4 pagesE2805 B 43Verma JagdeepNo ratings yet

- RAM BasicsDocument8 pagesRAM BasicsFriend FrdsNo ratings yet

- Computer Hardware Image GalleryDocument7 pagesComputer Hardware Image Gallerymathur1995No ratings yet

- How RAM WorksDocument9 pagesHow RAM WorksPablo Miguel FelsteadNo ratings yet

- Refreshing capacitors in DRAM memory cellsDocument8 pagesRefreshing capacitors in DRAM memory cellsTuan Anh NguyenNo ratings yet

- 6 - MemoryDocument7 pages6 - MemoryamirvillasNo ratings yet

- Virtual Memory: How Computers Use RAM and Hard Disk SpaceDocument1 pageVirtual Memory: How Computers Use RAM and Hard Disk Spacevikasrampal99No ratings yet

- BY: For:: Ahmad Khairi HalisDocument19 pagesBY: For:: Ahmad Khairi HalisKhairi B HalisNo ratings yet

- Ram TutorialDocument26 pagesRam TutorialGiannis PapanikolopoulosNo ratings yet

- Types of RAM: Cache CapacitorDocument7 pagesTypes of RAM: Cache CapacitorelgherianyNo ratings yet

- Different Types of ROMDocument5 pagesDifferent Types of ROMMaria Victoria FarrugiaNo ratings yet

- Understanding RAM Types and OperationsDocument23 pagesUnderstanding RAM Types and OperationsCharlie SamonteNo ratings yet

- Computer Assignment 1Document6 pagesComputer Assignment 1Muhammad Hassnain AhmadNo ratings yet

- RAM and RomDocument4 pagesRAM and Rommanoj22490No ratings yet

- Computer Memory Basics: RAM ROM CacheDocument6 pagesComputer Memory Basics: RAM ROM CacheAbubakker SiddiqNo ratings yet

- Unit - 5 Increasing The Memory SizeDocument14 pagesUnit - 5 Increasing The Memory SizeKuldeep SainiNo ratings yet

- How Computer Memory WorksDocument6 pagesHow Computer Memory WorksToon ManNo ratings yet

- Ca Unit 5 PrabuDocument37 pagesCa Unit 5 Prabu6109 Sathish Kumar JNo ratings yet

- Computer OrganizationDocument32 pagesComputer Organizationy22cd125No ratings yet

- About RAMDocument2 pagesAbout RAMcamjassNo ratings yet

- Memory Hierarchy and RAID StorageDocument16 pagesMemory Hierarchy and RAID StorageschawingaNo ratings yet

- RAM (Random Access Memory) : RAM Is A Semiconductor That Stores Charges With Transistors and Capacitors. DRAM-Dynamic RAMDocument13 pagesRAM (Random Access Memory) : RAM Is A Semiconductor That Stores Charges With Transistors and Capacitors. DRAM-Dynamic RAMminjraNo ratings yet

- Difference Between Static RAM and Dynamic RAMDocument8 pagesDifference Between Static RAM and Dynamic RAMfahimafridiNo ratings yet

- Unit 4 and Unit-5 - MemoryDocument104 pagesUnit 4 and Unit-5 - MemorybobbykNo ratings yet

- Computer MemoryDocument6 pagesComputer MemoryShyamol BoseNo ratings yet

- Design of Sram in VerilogDocument124 pagesDesign of Sram in VerilogAbhi Mohan Reddy100% (3)

- Co PDFDocument123 pagesCo PDFSitaNo ratings yet

- Memory Types and ClassificationsDocument39 pagesMemory Types and ClassificationsJason MampohNo ratings yet

- Adding Memory: Contents at A GlanceDocument11 pagesAdding Memory: Contents at A GlanceDrift GeeNo ratings yet

- Random Access Memory ProjectDocument13 pagesRandom Access Memory Projectmuneebjaurah100% (9)

- Assignment: Embedded SystemsDocument6 pagesAssignment: Embedded SystemsSudarshanNo ratings yet

- Edo RamDocument14 pagesEdo RamMoses ImmanNo ratings yet

- T.Y. E.I. /2 / 1 Memories N.KapoorDocument5 pagesT.Y. E.I. /2 / 1 Memories N.KapoorNeelam KapoorNo ratings yet

- Memory: Computer OrganizationDocument28 pagesMemory: Computer OrganizationAteeqAftabNo ratings yet

- Semiconductor MemoryDocument17 pagesSemiconductor MemoryAnkit SaxenaNo ratings yet

- Computer MemoryDocument34 pagesComputer MemoryAlice GuarinNo ratings yet

- Group Members: Karnail Katoch Vishal Mahant Archana Kahrinar Mohammad Pisavadi Kashyap BaradDocument55 pagesGroup Members: Karnail Katoch Vishal Mahant Archana Kahrinar Mohammad Pisavadi Kashyap BaradpRiNcE DuDhAtRaNo ratings yet

- RAM TechnologiesDocument25 pagesRAM TechnologiesAmarnath M DamodaranNo ratings yet

- Unit 3 OF ESDDocument22 pagesUnit 3 OF ESDTanveer ShariffNo ratings yet

- Design For PerformanceDocument34 pagesDesign For Performancec0de517e.blogspot.com100% (1)

- Logic Assignment 2-1Document16 pagesLogic Assignment 2-1Benita AgbagwaraNo ratings yet

- Chapter 4 Memory ElementDocument87 pagesChapter 4 Memory ElementWann FarieraNo ratings yet

- Random Access MemoryDocument19 pagesRandom Access MemoryOrlando FelixNo ratings yet

- Dynamic Random-Access Memory PDFDocument17 pagesDynamic Random-Access Memory PDFBintang Kejora100% (1)

- Memory and I/O Interfacing Memory: AccessibilityDocument52 pagesMemory and I/O Interfacing Memory: Accessibilitykarthick77No ratings yet

- Chapter 5 Memory OrganizationDocument75 pagesChapter 5 Memory Organizationendris yimerNo ratings yet

- Types of MemoryDocument14 pagesTypes of MemorySriram RamakrishnanNo ratings yet

- Types of ComputersDocument48 pagesTypes of Computersnaveed321100% (5)

- Unit-4 Memory NotesDocument25 pagesUnit-4 Memory NotestarunprovidesNo ratings yet

- CAODocument65 pagesCAOPriya SinghNo ratings yet

- Memory Chapter3Document3 pagesMemory Chapter3zhuoyan xuNo ratings yet

- Computer Basics Study GuideDocument11 pagesComputer Basics Study GuidePrerak DedhiaNo ratings yet

- Different RAM Types and Its UsesDocument8 pagesDifferent RAM Types and Its Usesdanielle leigh100% (6)

- TCP/IP HTTP ReferenceDocument4 pagesTCP/IP HTTP Referencevikasrampal99No ratings yet

- ClusterDocument1 pageClustervikasrampal99No ratings yet

- EncryptionDocument1 pageEncryptionvikasrampal99No ratings yet

- Power SuppliesDocument3 pagesPower Suppliesvikasrampal99No ratings yet

- BootingDocument1 pageBootingvikasrampal99No ratings yet

- EncryptionDocument1 pageEncryptionvikasrampal99No ratings yet

- Virtual Memory: How Computers Use RAM and Hard Disk SpaceDocument1 pageVirtual Memory: How Computers Use RAM and Hard Disk Spacevikasrampal99No ratings yet

- Run 16-bit and 3.1 apps in Windows NT with NTVDMDocument4 pagesRun 16-bit and 3.1 apps in Windows NT with NTVDMvikasrampal99No ratings yet

- KernelDocument9 pagesKernelvikasrampal99No ratings yet

- Understand Your Computer's POST Diagnostic CheckDocument1 pageUnderstand Your Computer's POST Diagnostic Checkvikasrampal99No ratings yet

- Static CMOS Inverter: How Complementary MOS Circuits WorkDocument5 pagesStatic CMOS Inverter: How Complementary MOS Circuits Workvikasrampal99No ratings yet

- Virtual Memory: How Computers Use RAM and Hard Disk SpaceDocument1 pageVirtual Memory: How Computers Use RAM and Hard Disk Spacevikasrampal99No ratings yet

- NTFSDocument7 pagesNTFSvikasrampal99No ratings yet

- NetworkingDocument6 pagesNetworkingvikasrampal99No ratings yet

- MultitaskingDocument1 pageMultitaskingvikasrampal99No ratings yet

- NTFSDocument7 pagesNTFSvikasrampal99No ratings yet

- NTFSDocument7 pagesNTFSvikasrampal99No ratings yet

- Lecture Notes Week 1 Introduction To MicroprocessorDocument51 pagesLecture Notes Week 1 Introduction To Microprocessormargetrie100% (1)

- FS100 ControllerDocument2 pagesFS100 ControllermartinimartiiniNo ratings yet

- Economic Dispatch - OPFDocument1 pageEconomic Dispatch - OPFAlok AgrawalNo ratings yet

- TB6600 DatasheetDocument33 pagesTB6600 DatasheetDragan ŠašićNo ratings yet

- Microprocessor Lab ManualDocument34 pagesMicroprocessor Lab ManualTeo JavaNo ratings yet

- Pir-Am612 Teoria PDFDocument5 pagesPir-Am612 Teoria PDFEloy TorresNo ratings yet

- AJB-D DatasheetDocument2 pagesAJB-D DatasheetYash PalNo ratings yet

- Datasheet LA76812Document3 pagesDatasheet LA76812Kevin Villacis AvelinoNo ratings yet

- Geetanjali Institute of Technical Studies: A Seminar Presentation ON Night Vision TechnologyDocument19 pagesGeetanjali Institute of Technical Studies: A Seminar Presentation ON Night Vision TechnologyRajpal Singh ChauhanNo ratings yet

- Yonah CPU Schematic Block DiagramDocument45 pagesYonah CPU Schematic Block DiagramWilgen GarciaNo ratings yet

- How To Build Your Own Stun Gun From Schematic DiagramsDocument8 pagesHow To Build Your Own Stun Gun From Schematic Diagramsja632271No ratings yet

- JNTUA - B Tech - 2018 - 3 2 - Dec - R15 - EEE - 15A02603 POWER SYSTEM ANALYSISDocument2 pagesJNTUA - B Tech - 2018 - 3 2 - Dec - R15 - EEE - 15A02603 POWER SYSTEM ANALYSISVinay ChinthaNo ratings yet

- Havells Modular 2017 PDFDocument16 pagesHavells Modular 2017 PDFvikash kumarNo ratings yet

- Mn00224e v11 IDU ALP2 ALCP2 ALCP2e PDFDocument394 pagesMn00224e v11 IDU ALP2 ALCP2 ALCP2e PDFBuzduga IonutNo ratings yet

- Ebs-6200 User's ManualDocument124 pagesEbs-6200 User's ManualDavid MiguelNo ratings yet

- Installation Guide: 2.4 Inch TFT Terminal Time Attendance & Access ControlDocument13 pagesInstallation Guide: 2.4 Inch TFT Terminal Time Attendance & Access ControlDatashield InfoNo ratings yet

- Partial Discharge AnalysisDocument28 pagesPartial Discharge AnalysisRemya Manuel100% (3)

- Comparator-Based Analog-to-Digital ConvertersDocument80 pagesComparator-Based Analog-to-Digital ConvertersjoshNo ratings yet

- Fire Extinguishing RobotDocument4 pagesFire Extinguishing RobotPrajwal shettyNo ratings yet

- Mentor PADSVX ODA Starter Library Guidelines Rev1a-558Document48 pagesMentor PADSVX ODA Starter Library Guidelines Rev1a-558Zeynep Emirhan ŞenyüzNo ratings yet

- 7SR242 Duobias Complete Technical Manual PDFDocument359 pages7SR242 Duobias Complete Technical Manual PDFashutosh2009100% (1)

- Manual For 7750Document232 pagesManual For 7750cooldude_82No ratings yet

- Logic Gates QuestionsDocument14 pagesLogic Gates QuestionsDinMat0% (2)

- Regenerate Digital Signals with Schmitt TriggersDocument75 pagesRegenerate Digital Signals with Schmitt TriggersEd JudgeNo ratings yet

- Safety SwitchesDocument56 pagesSafety SwitchesaglegarteNo ratings yet

- Shindengen F072-1847335Document46 pagesShindengen F072-1847335Jm TechNo ratings yet

- Csd88584Q5Dc 40-V Half-Bridge Nexfet Power Block: 1 Features 3 DescriptionDocument26 pagesCsd88584Q5Dc 40-V Half-Bridge Nexfet Power Block: 1 Features 3 DescriptionJ. Carlos RGNo ratings yet

- Restricted Earth FaultDocument26 pagesRestricted Earth FaultAfsar AliNo ratings yet

- Plan History: Samsung Heavy Industries Co.,Ltd. E'-28Document29 pagesPlan History: Samsung Heavy Industries Co.,Ltd. E'-28Carlos MolinaNo ratings yet

- Datasheet (10) Fuente ConmutadaDocument11 pagesDatasheet (10) Fuente ConmutadaJose Antonio SeguraNo ratings yet