Professional Documents

Culture Documents

Base .7

Uploaded by

மணிவேல் சந்திரன்Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Base .7

Uploaded by

மணிவேல் சந்திரன்Copyright:

Available Formats

ISSN: 2277-3754 ISO 9001:2008 Certified

International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 3, September 2013

Nine-Level Cascaded H-Bridge Multilevel Inverter

Divya Subramanian, Rebiya Rasheed

Abstract The multilevel inverter utilization have been increased since the last decade. These new type of inverters are suitable in various high voltage & high power application due to their ability to synthesize waveforms with better harmonic spectrum and faithful output.. This paper presents a multilevel inverter configuration which is designed by insertion of a bidirectional switch between capacitive voltage sources and a conventional H-bridge module. The modified inverter can produce a better sinusoidal waveform by increasing the number of output voltage levels. By serial connection of two modified H-bridge modules, it is possible to produce 9 output voltage levels including zero. Multicarrier phase-shifted pulse-width modulation method is used to achieve balanced power distribution among the power cells. The analysis of the output voltage harmonics is carried out. From the results, the proposed inverter provides higher output quality with relatively lower power loss as compared to the other conventional inverters with the same output quality.

cascaded H-bridge multilevel inverter for producing nine output voltage levels and for that we are using multicarrier modulation technique. II. NINE-LEVEL CASCADED H-BRIDGE MULTILEVEL INVERTER

Index Terms Cascaded H-bridge multilevel inverter (CHB), multicarrier pulse-width modulation, phase shifted modulation, total harmonic distortion (THD). I. INTRODUCTION Multilevel power conversion has become increasingly popular in recent years due to advantages of high power quality waveforms, low electromagnetic compatibility (EMC) concerns, low switching losses, and high-voltage capability. However, it increases the number of switching devices and other components, which results in an increase of complexity problems and system cost. There are different types of multilevel circuits involved. The first topology introduced was the series H-bridge design. This was followed by the diode clamped converter, which utilized a bank of series capacitors. A later invention detailed the flying capacitor design in which the capacitors were floating rather than series-connected. Another multilevel design involves parallel connection of inverter phases through inter-phase reactors. In this design, the semiconductors block the entire dc voltage, but share the load current. Several combinational designs have also emerged some involving cascading the fundamental topologies. These designs can create higher power quality for a given number of semiconductor devices than the fundamental topologies alone due to a multiplying effect of the number of levels. The multilevel inverters are mainly classified as diode clamped, Flying capacitor inverter and cascaded multilevel inverter. The cascaded multilevel control method is very easy when compare to other multilevel inverter because it doesnt require any clamping diode and flying capacitor. In this paper, we are using a new topology of

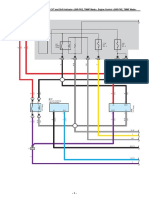

The main disadvantage of the conventional cascaded H-bridge [5] is that when the voltage level increases, the number of semiconductor switches increases and also the source required increases. In order to overcome this introduced a new topology of cascaded H-bridge. The main advantage of this topology is that the number of switches required is reduced and also the number of sources. Figure 1 shows the new cascaded five level H-bridge multilevel inverter [6]. It has additional one bidirectional switch connected between the first leg of the H-bridge and the capacitor midpoint, enabling five output voltage levels.

Fig 1. Five level cascaded H-bridge multilevel inverter

It has five output voltage levels ie Vdc, Vdc/2, 0, -Vdc/2, -Vdc. For getting the output voltage Vdc the switches S2S5 need to be turned on. Similarly for output voltage Vdc/2 switches S1S5 need to be turned on, for 0 either S3S5 or S2S4 need to be turned on; for - Vdc/2 switches S1S4 need to be turned on; for - Vdc switches S3S4 need to be turned on. The switch combinations are shown in table 1.

Table -1: Five- level cascaded h-bridge output voltage

201

ISSN: 2277-3754 ISO 9001:2008 Certified

International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 3, September 2013 In the circuit shown in fig 1, single H-bridge module is where Vref is the amplitude of the voltage reference and Vcr is capable of producing five level output voltage. Each inverter the amplitude of the carrier signal. module is capable of producing 2E, E, 0, -E, -2E. That means Multicarrier phase-shifted PWM (CPS-PWM) [7] modulation by using two bridges 9 level output voltage is produced. The is used to generate the PWM signals. The amplitude and total output voltage is sum of the outputs of the inverter frequency of all triangular carriers are the same as well as the modules and the nine voltage levels are 4E, 3E, 2E, E, 0, -E, phase shifts between adjacent carriers. Depending on the -2E, -3E, -4E. The advantages of this proposed circuit is number of cells, the carrier phase shift for each cell, cr,n can number of switches are reduced. The cost and complexity is be obtained from, cr,n = 2(n-1)/Nc , n= 1,2,.Nc (2) less in this circuit. To synthesize nine output voltage levels, it For signal generation in each cell, two voltage references and employs two independent dc voltage sources of 2E which are one carrier signal are used. Vref is defined by divided into two input sources E in order to secure an Vref = M sin t (3) additional dc voltage source of E. The inverter module having Vref1= Vref )4( a bidirectional switch produces 5-levels of output voltage (Vref2 = Vref 1/2 )5( 2E, -E, 0, E, 2E) by controlling of the switches. Since every Both references are identical but displaced by an offset output terminal of the inverter module is connected in series, equal to the carriers amplitude which is . When the voltage the output voltage becomes the sum of the terminal voltages reference is between 0<vref, vref1 is compared with the of each inverter. The circuit for nine level cascaded H-bridges triangular carrier and alternately switches S1 and S3 while is shown in figure 2, the gating signals for the inverter is maintaining S5 in the ON state to produce either vdc or 0. generated by using multicarrier modulation. Whereas, when the reference is between <vref1, vref2 is used and alternately switches S1 and S2 while maintaining S5 in the ON state to produce either vdc or vdc. As for the reference between <vref0, vref1 is used for comparison which alternately switches S1 and S2 while maintaining S4 in the ON state to produce either vdc or 0. For a voltage reference between 1<vref, vref2 is compared with the carrier to produce either vdc or vdc alternately switches S1 and S3, maintaining S4 in the ON state. It is noted that two switches, S4 and S5, only operate in each reference half cycle. This implies that both switches operate at the fundamental frequency while the others operate close to the carrier frequency. This allows the dc voltage to be switched at a low frequency so as to reduce the switching losses. Fig.3 shows the modulation scheme used for the proposed two-cell configuration and Fig. 4 shows a detail block diagram for generating the PWM signals.

Fig 2. Nine level cascaded H-bridge multilevel inverter

III. PWM MODULATION In this inverter, the sinusoidal pulse width modulation is going to use. In the Sinusoidal pulse width modulation scheme, as the switch is turned on and off several times during each half-cycle, the width of the pulses is varied to change the output voltage. Lower order harmonics can be eliminated or reduced by selecting the type of modulation for the pulse widths and the number of pulses per half-cycle. Higher order harmonics may increase, but these are of concern because they can be eliminated easily by filters. The SPWM aims at generating a sinusoidal inverter output voltage without low-order harmonics. This is possible if the sampling frequency is high compared to the fundamental output frequency of the inverter. The modulation index, M of the proposed multilevel inverter is defined by, M= ( Vref / Vcr) (1)

Fig 3. . Multicarrier phase-shifted PWM for two-cell configuration

202

ISSN: 2277-3754 ISO 9001:2008 Certified

International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 3, September 2013

Fig 4. PWM signal generation with multicarrier phase-shifted modulation

Fig 7. Circuit of cell 2

IV. SIMULATION AND RESULTS The simulation model was designed using MATLAB/Simulink Software. The gating signals for the inverter are generated by using multicarrier modulation technique. The circuit was simulated with RL load.

Fig 8 . Circuit for PWM signal generation

Fig 5 Circuit for Nine level Cascaded H-bidge Multilevel Inverter.

Fig 9. Output voltage waveform for cell 1

Fig 6 Circuit of cell 1. Fig 10 . Output voltage waveform for cell 2

203

ISSN: 2277-3754 ISO 9001:2008 Certified

International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 3, September 2013

Fig 11. . Output voltage waveform

Fig 14. Nine level cascaded H-bridge multilevel inverter with multicarrier modulation, THD=13.01%.

V. CONCLUSION Multilevel inverters have become an effective and practical solution for increasing power and reducing harmonics of ac waveforms. This project deals with the design and implementation of single-phase nine-level Cascaded H-bridge multilevel inverter for RL load with multicarrier phase-shifted PWM modulation method. The simulation of 9-level cascaded H-bridge is done. Along with it, its harmonic analysis was done. The simulation results shows that the developed nine-level Cascaded H-bridge Multilevel inverter has many merits such as reduce number of switches, lower EMI, less harmonic distortion and the THD obtained is 13.01%. ACKNOWLEDGMENT Fore mostly, I would like to express my sincere gratitude to our Principal: Dr K. S.M Panicker, for his guidance. I am also thankful to our HOD Dr.Pailo Paul for imparting fundamental idea, which helped me a lot for my project. I am extremely thankful to my guide Mrs.Rebiya Rasheed for her guidance and suggestions, I would also like to thank all my teachers and my husband Mr.Veneesh C.S who gave their full support and encouragement for doing this project. I owe my deepest gratitude to them REFERENCES

[1]

Fig 12. . Output current waveform

Fig 13. Five level cascaded H-bridge multilevel inverter with multicarrier modulation , THD=26.00%.

[2]

Nasrudin Abd. Rahim, Mohamad Fathi Mohamad Elias, Wooi Ping Hew, IEEE transaction. Industry Electronics, Design of filter to reduce harmonic distortion in industrial power system, Vol. 60, No :8, 2943-2956, August 2013. J. Selvaraj and N. A. Rahim, "Multilevel Inverter For Grid-Connected PV System Employing Digital PI Controller," IEEE Trans. Ind.Electron., vol. 56, pp. 149-158, 2009. Naderi and A. Rahmati, "Phase-Shifted Carrier PWM Technique for General Cascaded Inverters," IEEE Trans. Power Electron., vol. 23, pp. 1257-1269, 2008.

[3]

204

ISSN: 2277-3754 ISO 9001:2008 Certified

International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 3, September 2013

[4] J. Rodriguez, J.-S. Lai, and F. Z. Peng, Multilevel inverters: A survey of topologies, controls, and applications, IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724 738, Aug. 2002. [5] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Prez, A Survey on cascaded multilevel inverters, IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197-2206, July 2010. [6] S. J. Park, F. S. Kang, M. H. Lee, and C. U. Kim, A new single-phase five-level PWM inverter employing a deadbeat control scheme, IEEE Trans. Power Electron., vol. 18, no. 18, pp. 831843, May 2003. [7] N. A. Rahim, and J. Selvaraj, Multistring five-level inverter with novel PWM control scheme for PV application, IEEE Trans. Ind. Electron., vol. 57, no. 6, pp. 2111-2123, June 2010.

205

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Touareg Supplementary HeatingDocument32 pagesTouareg Supplementary HeatingAnonymous t1FCvPRSaNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Water Pipe SizingDocument40 pagesWater Pipe SizingAfzal Khan100% (2)

- Cruise Control, CVT and Shift Indicator, Engine ControlDocument27 pagesCruise Control, CVT and Shift Indicator, Engine ControlRicardoNo ratings yet

- Impressed Current Cathodic Protection Design For Eleme Petrochemical 6 and 8'' Pipeline PDFDocument16 pagesImpressed Current Cathodic Protection Design For Eleme Petrochemical 6 and 8'' Pipeline PDFobuseNo ratings yet

- IQOQGP8Document10 pagesIQOQGP8Lautaro100% (2)

- Municipal Solid Waste Project SKTGDocument3 pagesMunicipal Solid Waste Project SKTGDevanSandrasakerenNo ratings yet

- STD 149Document42 pagesSTD 149Pranav TalwarNo ratings yet

- Guia SupacDocument44 pagesGuia SupacMario Vazquez BNo ratings yet

- Manivel.C: Career ObjectiveDocument2 pagesManivel.C: Career Objectiveமணிவேல் சந்திரன்No ratings yet

- TNPSC Current Affairs December 2015 by Tnpscportal inDocument33 pagesTNPSC Current Affairs December 2015 by Tnpscportal inAntony PandiarajanNo ratings yet

- Automated Highway Speed Checker - AbstractDocument1 pageAutomated Highway Speed Checker - Abstractமணிவேல் சந்திரன்No ratings yet

- Theraiyar KarisalaiDocument52 pagesTheraiyar KarisalaiK.s. RameshNo ratings yet

- Manivel.C: Career ObjectiveDocument2 pagesManivel.C: Career Objectiveமணிவேல் சந்திரன்No ratings yet

- Kalaiarasan ResumeDocument5 pagesKalaiarasan Resumeமணிவேல் சந்திரன்No ratings yet

- Cascade Dual Buck InverterWith Phase-Shift ControlDocument11 pagesCascade Dual Buck InverterWith Phase-Shift ControlSanthosh GuduruNo ratings yet

- Wireless Based Railway Bridge Damage & Track Fault Notification With Alarm SystemsDocument5 pagesWireless Based Railway Bridge Damage & Track Fault Notification With Alarm Systemsமணிவேல் சந்திரன்100% (1)

- Automated Highway Speed Checker - AbstractDocument1 pageAutomated Highway Speed Checker - Abstractமணிவேல் சந்திரன்No ratings yet

- GSM (SMS) Controlled DC MotorDocument6 pagesGSM (SMS) Controlled DC Motortalk2neel12No ratings yet

- S.No Description Page NoDocument2 pagesS.No Description Page Noமணிவேல் சந்திரன்No ratings yet

- Automatic Railway Gate Control Using MicroDocument24 pagesAutomatic Railway Gate Control Using Microமணிவேல் சந்திரன்No ratings yet

- Automatic Room Light Controller With Visitor CounterDocument5 pagesAutomatic Room Light Controller With Visitor CounterYaser ShaikhNo ratings yet

- CE 73 Basic Dynamics and Aseismic DesignDocument27 pagesCE 73 Basic Dynamics and Aseismic Designமணிவேல் சந்திரன்100% (1)

- Attendance ManagementDocument1 pageAttendance Managementமணிவேல் சந்திரன்No ratings yet

- Automatic Room Light Controller With Visitor CounterDocument5 pagesAutomatic Room Light Controller With Visitor CounterYaser ShaikhNo ratings yet

- Title, List of Tables, Figures and Abb.Document20 pagesTitle, List of Tables, Figures and Abb.மணிவேல் சந்திரன்No ratings yet

- MicroDocument8 pagesMicroமணிவேல் சந்திரன்No ratings yet

- Attendance ManagementDocument1 pageAttendance Managementமணிவேல் சந்திரன்No ratings yet

- Manual - Ew-Combi Mk2Document8 pagesManual - Ew-Combi Mk2Trần Thùy LinhNo ratings yet

- PUPID May 2023 LoggerDocument43 pagesPUPID May 2023 LoggerAlberto FernandezNo ratings yet

- Untes Chiller HEDocument5 pagesUntes Chiller HEAnarNo ratings yet

- Inserto Clase 15KV 200a PDFDocument16 pagesInserto Clase 15KV 200a PDFjavier vargasNo ratings yet

- Synchronous Machines Question BankDocument10 pagesSynchronous Machines Question BankelecenggNo ratings yet

- 0111 SunSwitch - OFFER FOR - 1 KVA TO 8 KVA Solar Hybrid PCUDocument8 pages0111 SunSwitch - OFFER FOR - 1 KVA TO 8 KVA Solar Hybrid PCUGaurav KhannaNo ratings yet

- KV Sizer GuideDocument3 pagesKV Sizer GuideBasavaraj ManturNo ratings yet

- SiemensPowerAcademyTD Catalog EN 2016 PDFDocument14 pagesSiemensPowerAcademyTD Catalog EN 2016 PDFANINDA CHATTERJEENo ratings yet

- Mantenedor de Bateria LBC1206Document6 pagesMantenedor de Bateria LBC1206YERKO OVIEDONo ratings yet

- APCE-Oce551 Unit 1Document36 pagesAPCE-Oce551 Unit 1Bhuvanapriyan S100% (1)

- 2.627/2.626 Background Assessment QuizDocument4 pages2.627/2.626 Background Assessment QuizmusaNo ratings yet

- Magnetism PDFDocument4 pagesMagnetism PDFNiksslpadaNo ratings yet

- Multistage and Multilevel Power Electronic Converter-Based Power Supply For Plasma DBD DevicesDocument4 pagesMultistage and Multilevel Power Electronic Converter-Based Power Supply For Plasma DBD DevicesBrightworld ProjectsNo ratings yet

- A New Design Approach For of Pneumatic ConveyingDocument6 pagesA New Design Approach For of Pneumatic ConveyingpneuconNo ratings yet

- Effects of Joint Geometries On Welding of Mild Steel by Shielded Metal Arc Welding (Smaw)Document6 pagesEffects of Joint Geometries On Welding of Mild Steel by Shielded Metal Arc Welding (Smaw)Sudeep Kumar SinghNo ratings yet

- 1.2 Substation Components, Functions & RatingsDocument57 pages1.2 Substation Components, Functions & Ratings021804No ratings yet

- Fact Sheet ThreeDocument4 pagesFact Sheet ThreeRodrigo VargasNo ratings yet

- Classical Mechanics Problem SetDocument1 pageClassical Mechanics Problem SetDevanshu GargNo ratings yet

- UBL3&4 E 0 G0 ES AA0 002P - R3 - Color Schedule For Power PlantDocument12 pagesUBL3&4 E 0 G0 ES AA0 002P - R3 - Color Schedule For Power PlantAdvent ManurungNo ratings yet

- Test 8 ch8 Phy 9thDocument1 pageTest 8 ch8 Phy 9thMurtazaNo ratings yet

- of Gatorade..Document29 pagesof Gatorade..Jay ThakkarNo ratings yet

- Ew Blast Powercore 4000K 21degree SpecSheetDocument2 pagesEw Blast Powercore 4000K 21degree SpecSheetsanguinaria123No ratings yet