Professional Documents

Culture Documents

06009184

Uploaded by

Prashanth Kumar ShettyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

06009184

Uploaded by

Prashanth Kumar ShettyCopyright:

Available Formats

1430 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 59, NO.

3, MARCH 2012

DC Link Active Power Filter for

Three-Phase Diode Rectier

Xiong Du, Luowei Zhou, Senior Member, IEEE, Hao Lu, and Heng-Ming Tai, Senior Member, IEEE

AbstractIn this paper, a dc link active power lter (APF) for

three-phase diode rectier is proposed. The proposed dc link APF,

which is composed of two series-connected bidirectional boost

converters, intends to eliminate the input current harmonics. It is

paralleled at the dc link of the diode rectier and is coupled to the

ac input with three line-frequency switches. Compared with the

full power processed power factor correction (PFC) solution, the

dc link APF is partially power processed in that it only compen-

sates for the harmonic current component at the dc link. Thus, it

features with lower power processing. Moreover, it exhibits better

total harmonic distortion of the ac line current when compared

with the traditional ac side shunt APF. Voltage and current loop

models are developed for average current control, and the selection

of the current loop bandwidth is presented. Switching stresses

of the ac APF, the dc link APF, and the six-switch PFC are

also calculated and analyzed. Experimental and simulation results

demonstrate the effectiveness of this dc link APF.

Index TermsActive power lter (APF), bandwidth, compensa-

tion performance, diode rectier, power factor correction (PFC).

I. INTRODUCTION

H

ARMONIC current pollution generated by nonlinear

loads is a serious problem in power systems. Numerous

harmonic standards have been put forward on this issue, for

example, IEEE and IEC standards [1]. Since three-phase diode

rectiers are widely used in industry, such as adjustable speed

drives and dc power supplies [2][4], the harmonics generated

by the diode rectier in the line current is a main concern in

power electronics. To eliminate the harmonic current generated

by this type of harmonic source, the shunt active power lter

(APF) or series APF has been an effective solution [5][11].

However, the rating of APF is normally small because of its

partial power processing property. Hence, it generally features

with low cost and small volume. Shunt APFs are usually paral-

leled at the ac side. Therefore, both the voltage and the current

Manuscript received September 26, 2010; revised January 24, 2011,

April 26, 2011, and July 23, 2011; accepted August 15, 2011. Date of pub-

lication September 6, 2011; date of current version October 25, 2011. This

work was supported in part by Foundation for the Author of National Excellent

Doctoral Dissertation of China under Grant 200948, in part by the Program

for New Century Excellent Talents in University under Grant NCET-09-0839,

in part by the National 111 Project of China under Grant B08036, and in part

by Scientic Research Foundation of State Key Lab of Power Transmission

Equipment and System Security under Grant 2007DA10512711101.

X. Du, L. Zhou, and H. Lu are with the State Key Laboratory of Power Trans-

mission Equipment and System Security and New Technology, and the College

of Electrical Engineering, Chongqing University, Chongqing 400044, China

(e-mail: duxiong@cqu.edu.cn; zluowei@cqu.edu.cn; luhao_84@163.com).

H.-M. Tai is with the Department of Electrical Engineering, University of

Tulsa, Tulsa, OK 74104 USA (e-mail: tai@utulsa.edu).

Color versions of one or more of the gures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identier 10.1109/TIE.2011.2167112

processed by APF are with alternating values. We name the

traditional shunt APF, the ac side APF thereafter, to distinguish

with the dc link APF to be studied in this paper.

A four-quadrant inverter is commonly used in the power

stage of the ac side APF, and an ac side APF always needs

complicated harmonic current detection and control. On the

other hand, the three-phase power factor correction (PFC),

which is a full power processing solution, has been exten-

sively studied [12][19]. The most popular topology of the

three-phase PFC is a six-switch bridge. This type of PFC has

the feature of bidirectional power owing capability. In some

specic applications, unidirectional PFC topologies such as

the Vienna converter [15], [16] and the series connected dual-

boost converter [19], [20] are considered. Both bidirectional

and unidirectional three-phase PFCs are required to process all

the load power. Thus, most of them suffer from higher silicon

cost as compared with the APF solutions which require only

partial power processing. Multipulse rectiers, which employ

low frequency phase shift transformer to synthesize reasonable

line current waveform, are also reported for the reduction of the

silicon cost [17], [18]. Due to the application of low frequency

transformer, the volume is a critical limitation.

For three-phase diode rectiers, low cost harmonic elimi-

nation methods, which adopt a few passive or active compo-

nents to inject triple-order harmonic currents at the dc link of

the three-phase diode rectier for line current correction and

harmonic injection, have been reported [21][27]. The circuit

presented in [21] is a series connected dual-boost converter

with tuned LC lter which functions as a third order harmonic

current injection network. Later, the tuned LC lter is replaced

with a low frequency zigzag connected transformer so that the

parameter variation effect of the LC lter can be avoided [22].

The active switches in these two topologies need to process

all the output power at high switching frequency while the

LC lter suffers from parameter sensitivity, and low frequency

zigzag transformer still appears large volume. To eliminate

active switches, passive harmonic current injection circuits,

which combine separate LC lter and low frequency star-

delta transformer, have been proposed [23][25]. Similar to the

circuits in [21], [22], these circuits still experience parameter

sensitivity and large volume. To dodge the parameter sensitivity

effect of the passive lter network in [23][25], a compact high

frequency active current shaping network has been developed

to replace the passive lter, and three ac switches are employed

to take place of the bulky low frequency transformer [26].

However, the line current would not be proportional to the line

voltage theoretically because of only one current variable being

controlled instantaneously. This is because two independent

0278-0046/$26.00 2011 IEEE

DU et al.: DC LINK ACTIVE POWER FILTER FOR THREE-PHASE DIODE RECTIFIER 1431

phase currents are present in the three-phase three-wire system.

Hence, the line current performance is limited and the line

current total harmonic distortion (THD) is high. With the same

active current shaping network, the ac switches are replaced

with star-delta transformer for cost reduction [27]. As reported

in [26], the performance of this harmonic current injection

method is not acceptable because the line current THD is still

around 8.5%.

In this paper, we propose a dc link APF for three-phase diode

rectiers. Although the dc link lter for a single phase rec-

tier has been studied [28], [29], extension to the three phase

is not straightforward and requires new topology and control

strategy. The dc link APF studied in this paper differs from

the active dc lter in HVDC [30] in terms of the connection

structure and the function. The active dc lter is connected at

the bottom of an existing passive dc lter at the rectier station.

It is mainly used to reduce the dc current ripples and to increase

the dynamic response of the dc current ripple lter [30]. On the

other hand, the dc link APF is connected in parallel at the dc

terminal of the diode rectier and coupled with the ac input.

Its main function is to suppress the line side input current, not

to regulate the dc link performance. The proposed topology

consists of two series-connected bidirectional boost converters,

which function as harmonic current generators to compensate

for the phase currents to be in phase with the corresponding

line voltages, not just triple current injection as in [21][27].

Moreover, three line-frequency ac switches decouple the three-

phase circuit to the two-phase circuit to simplify the control

effort. Compensation performance of this three-phase dc link

APF is analyzed and is evaluated under limited switching

frequency and limited current loop bandwidth. The current

loop bandwidth selection is presented based on the frequency

domain evaluation. In addition, the voltage loop and current

loop models are developed for the control design, and switching

stress is calculated and analyzed. Performance comparison with

the ac side APF and three-phase PFC is also conducted. Sim-

ulation results and experimental results measured from a DSP-

controlled prototype are presented to verify the performance of

the proposed dc link APF.

II. PROPOSED DC LINK ACTIVE POWER FILTER

Consider a three-phase diode rectier with a dc load as

shown in Fig. 1. The dc load is modeled with a simple RL

load. It can be justied even under the output capacitor lter

condition in that an inductor is usually placed in front of

the capacitor to smooth the dc link current. If there is no

other mechanism to improve the input current quality of the

diode rectier, the input line currents are polluted with series

harmonic components. To alleviate the harmonic pollution, a

dc link APF is proposed. This dc link APF is coupled to the

ac input with three ac switches working at line frequency and

connected to the load, as shown in Fig. 1. It consists of two

series-connected bidirectional boost converters, which contain

positive part components L

p

, S

p1

, S

p2

, C

p

and negative part

components L

n

, S

n1

, S

n2

, C

n

.

The operation principle of the dc link APF can be examined

as the series connected dual-boost three-phase PFC [19], [20].

Fig. 1. Schematic of proposed dc link active power lter for three-phase diode

rectier.

Fig. 2. Line period division and ac switches conduction states.

Fig. 3. Equivalent circuit for the interval I.

The input line voltages are divided into six intervals, IVI, as

shown in Fig. 2. In each interval, only one ac switch conducts.

For example, in interval I, S

b

conducts while S

a

and S

c

are off. The dc link APF is simplied to a series-conducted

bidirectional boost converter. Fig. 3 shows the equivalent circuit

of the dc link APF for interval I.

The dc link currents have correspondence with the ac input

currents. Distinct interval produces different correspondence.

For example, the currents i

p

, i

m

, i

n

are i

a

, i

b

, and i

c

, respec-

tively, in interval I. The input voltage v

pm

of the positive boost

converter is equal to v

ab

, so is the voltage v

mn

of the negative

boost converter equal to v

bc

. The dc load is modeled with a

constant dc current source.

1432 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 59, NO. 3, MARCH 2012

If the line current i

x

can be controlled in proportion to the

corresponding line voltage in each interval such as

i

x

=

v

x

R

e

(1)

where x = {p, m, n}, v

p

, v

m

, v

n

are the voltages between node

p, m, n and node o in Fig. 1, R

e

is the equivalent phase resis-

tance. Then, the line currents also hold the same proportionality

to the corresponding line voltages [19], [20],

1

i.e.,

i

y

=

v

y

R

e

(2)

where y = {a, b, c}. v

p

and v

n

are the positive and negative

envelopes of the line voltages, and v

m

is the complement

voltage

v

p

=Max(v

a

, v

b

, v

c

) (3)

v

n

=Min(v

a

, v

b

, v

c

) (4)

v

m

=v

a

+v

b

+v

c

v

p

v

n

. (5)

In the steady state, the dc voltages of the capacitors are

assumed to be equal

v

cp

= v

cn

(6)

and their dc component is V

c

. Due to the equivalent series-

connected boost converter topology, the complementary high

frequency switches S

p1

, S

p2

and S

n1

, S

n2

can be controlled to

regulate the dc rail current i

p

and i

n

, respectively, to satisfy the

relationship (1).

When S

p1

is on and S

p2

is off, the voltage across the inductor

L

p

is positive, i.e.,

v

Lp

= v

pm

> 0. (7)

Then the inductor current i

Lp

will increase. When S

p1

is off

and S

p2

is on, the voltage across L

p

is negative

v

Lp

= v

pm

v

cp

< 0. (8)

The inductor current i

Lp

decreases. This current regulation

process also can be applied to the negative part boost topology.

Typical operation waveforms of the dc link APF rectier

are shown in Fig. 4 under the symmetrical sinusoidal input

condition. The voltages and currents are drawn with p.u. values.

The voltage base is the amplitude value of the phase voltage,

and the current base is the dc load current which is assumed

to be constant dc with 50 Hz line frequency. The top panel

illustrates the voltages v

pm

and v

nm

of the positive part and

negative part boost converter, respectively. The middle panel

displays the current waveforms in the positive boost converter.

Those in the negative part have similar waveforms and are not

shown. The bottom panel exhibits the input phase voltage and

the line current of phase a. From Fourier analysis of the line

1

Equations (1) and (2) are based on the three-phase voltages without zero-

sequence component. If the zero-sequence voltage exists in the line voltage,

then v

x

should be changed to v

x

= v

x

(v

p

+ v

m

+ v

n

)/3, and v

y

should

be changed to v

y

= v

y

(v

a

+ v

b

+ v

c

)/3 because the zero-sequence cur-

rent does not exist in the three-phase three-wire system.

Fig. 4. Typical operation waveforms of the proposed dc link APF.

current of a three-phase diode rectier with inductive load, the

phase current amplitude can be obtained by

I

m

=

2

p.u. (9)

This indicates the quantitative relationship of the currents

shown in the middle panel in Fig. 4. As can be seen from Fig. 4,

the current processed by the dc link APF is just part of the load

current. This situation enables the reduction of power rating,

like the traditional ac side APF. However, the compensation

performance of the dc link APF is much better than that of the

traditional ac side APF, which will be described in Section IV.

III. CONTROL OF DC LINK APF

A. Control Structure

Average current control [31] is employed to control the

dc link APF for digital implementation. The input voltage feed-

forward [32] is also adopted here to eliminate the input voltage

effect to the current loop. Fig. 5 shows the block diagram of the

overall current control, which consists of one outer voltage loop

and two inner current loops. V

m

is the amplitude of the carrier

signal, which is the signal employed in the sine-triangle PWM

to generate duty ratios.

The sum of the voltages from the two dc capacitors is

compared with a dc voltage reference U

ref

. The difference is

fed to the voltage loop compensator, a PI controller PI

1

to

obtain the equivalent phase conductance g

e

. Multiplying g

e

to

DU et al.: DC LINK ACTIVE POWER FILTER FOR THREE-PHASE DIODE RECTIFIER 1433

Fig. 5. Average current control with input voltage feedforward.

the respective line voltage yields the reference currents of the

positive part and the negative part boost converter

i

pref

=g

e

v

p

(10)

i

nref

=g

e

v

n

. (11)

The reference currents i

pref

and i

nref

are compared with the

sensed dc rail currents i

p

and i

n

, respectively. The differences

are fed to the inner current loop compensators G

c

, which

consists of two PI controllers PI

2

and PI

3

. The output of

the current compensator determines the duty ratios through the

PWM circuits. d

p

and d

n

are, respectively, the duty ratios of the

switches S

p1

and S

n1

. Moreover, the duty ratios of switches S

p2

and S

n2

are (1 d

p

) and (1 d

n

), respectively. The dashed

line indicates the input voltage feedforward that eliminates the

input voltage coupling effect.

The control structure is similar to that of the typical single-

phase PFC [33]. The difference lies in that the inductor current

in the single-phase PFC is controlled directly by the duty ratio

of the PFC switch, whereas the inductor currents are controlled

indirectly by the duty ratios d

p

and d

n

in the proposed structure.

Models of the voltage loop and the current loop are discussed

below.

B. Voltage Loop Model

As in the conventional cascaded loop control, the bandwidth

of the outer voltage loop is much smaller than that of the

inner current loop. Hence, dynamics of the current loop (e.g.,

inductor current) can be ignored when modeling the voltage

loop. Double averaging method [33] is applied to obtain a

simple rst-order power stage voltage model with small signal

linearization. From Fig. 3 and according to power balance,

we have

v

pm

(i

p

i

Load

) +v

mn

(i

n

i

Load

)

= Cv

cp

dv

cp

dt

+Cv

cn

dv

cn

dt

(12)

where v

cp

and v

cn

are voltage across the capacitors C

p

and C

n

,

respectively. All the time variables in (12) represent the values

averaged in one switching period. Averaging (12) for one third

of the line period yields

3V

2

p

2

g

e

3V

p

I

load

= CV

c

d(v

cp

+v

cn

)

dt

(13)

Fig. 6. Voltage loop model.

where V

p

is the amplitude of the phase voltage, and C is

the capacitance under symmetrical conditions, C

p

= C

n

= C.

Consider the perturbation on g

e

and v

cp

+v

cn

, and neglect the

perturbation of I

load

, we obtain the transfer function

G

ve

(s) =

v

cp

(s) +v

cn

(s)

g

e

(s)

=

3V

2

p

2CV

c

s

. (14)

The voltage loop model is shown in Fig. 6, in which H

v

(s) is

the voltage sensing scale for practical implementation. G

v

(s)

is the voltage compensator transfer function, represented by a

traditional PI controller.

C. Current Loop Model

In each interval shown in Fig. 2, the equivalent circuit in

Fig. 3 has symmetric structure. Thus, the current loop can be

analyzed in either the positive part or the negative part boost

converter. The positive part is selected here. When analyzing

the fast current loop, the voltage dynamics can be approximated

by a simple constant dc voltage source. Then, the output of the

voltage loop is treated as a constant admittance G

e

. The current

loop modeling method in [34] is applied to obtain the current

loop model shown in Fig. 7 with leading edge modulation. The

dashed-line represents the input voltage feedforward. Without

the input voltage feedforward, the inductor current can be

derived as

I

Lp

(s) =

G

c

(s)

V

c

V

m

1

sL

p

1 +G

c

(s)

V

c

V

m

1

sL

p

[I

pref

(s) I

Load

(s)]

+

1

sL

p

1 +G

c

(s)

V

c

V

m

1

sL

p

V

pm

(s)

=

G

c

(s)

V

c

V

m

sL

p

+G

c

(s)

V

c

V

m

[I

pref

(s) I

Load

(s)]

+

V

pm

(s)

sL

p

+G

c

(s)

V

c

V

m

.

This shows that the inductor current response is coupled with

the input voltage. Adding the feedforward part to the current

loop, the inductor current becomes

I

Lp

(s) =

V

c

V

m

G

c

(s) [I

pref

(s) I

Load

(s)]

sL

p

+

V

c

V

m

G

c

(s)

. (15)

The input voltage coupling is eliminated through the voltage

feedforward.

Control design is straightforward because both the voltage

model and the current model are simple rst-order models.

The simple PI controller can be tuned to meet the control

1434 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 59, NO. 3, MARCH 2012

Fig. 7. Current loop model.

objectives [35]. The main concern becomes the determination

of the frequency bandwidth of the voltage loop and the current

loop. Since each loop has its own control target, the voltage

loop bandwidth should be set smaller than the lowest order

voltage ripple in the dc bus voltage. In addition, the current

loop bandwidth is required to be as high as possible to improve

the current compensation performance. Generally, the current

loop bandwidth is limited to 1/5 to 1/10 of the switching

frequency [31].

Regarding the compensation performance of dc link APF, it

is desired to have higher current loop bandwidth with higher

switching frequency. On the other hand, lower current loop

bandwidth with smaller switching frequency is recommended

to account for the device switching frequency and the efciency.

The criterion for the selection of current loop bandwidth will be

presented in the next section.

IV. COMPENSATION PERFORMANCE EVALUATION

This section describes the relationship between the com-

pensation performance and the current loop bandwidth of the

proposed dc link APF and evaluates the compensation perfor-

mances of the dc link APF and the traditional ac side APF.

Both APFs have the following characteristics on compensation

performance.

1) If the current harmonic components in the line current

could be neglected with innite current loop bandwidth,

then the THD of the line current is assumed zero for the

dc link and the ac side APF.

2) For nite current loop bandwidth, only the frequency

components with harmonic orders smaller than the band-

width will be compensated.

3) The switching frequency related current ripples are ig-

nored because these harmonics are easy to be ltered

out and usually are much higher than the harmonic order

specied by the standards.

The line current in ac side APF still contains the current

harmonics with frequencies higher than the current loop band-

width, and these high frequency components directly affect the

line current THD. In contrast, for dc link APF, the compensated

harmonics with frequency less than the current loop bandwidth

will appear in the dc rail currents (i

p

and i

n

) to form the

desired current waveforms (as shown in the middle panel of

Fig. 4). That is, due to the nite current loop bandwidth, the

compensated positive part inductor current contains only nite

number of harmonics and can be expressed as

i

Lp

(t) =

N

n=0

I

Lpn

cos nt. (16)

where values of n are the integer multiples of 3 and is the fun-

damental frequency. N is the largest harmonic order of which

the frequency is smaller than the current loop bandwidth. The

relationship between the harmonic components in the dc rail

currents i

p

, i

n

and the ac line current will be developed below.

This relationship will be applied to quantify the bandwidth

effect for compensation performance on dc link APF.

Assume the line voltage has symmetrical sinusoidal wave-

form. A switch function S

fa

(t) for phase a, shown in Fig. 8,

is introduced to establish the time domain relationship between

the dc rail currents and the line current. The switch function

S

fa

(t) is given by

S

fa

(t) =

_

_

_

0

T

2

< t

T

6

1

T

6

< t

T

6

0

T

6

< t

T

2

.

(17)

T is the line period. Then, the line current can be expressed in

terms of the dc rail currents and the switch function

i

a

(t) = i

p

(t)S

fa

(t) +i

n

(t)S

fa

_

t

T

2

_

_

1 S

fa

(t) S

fa

_

t

T

2

__

[i

p

(t) +i

n

(t)] (18)

or

i

a

(t) =

_

2S

fa

(t) +S

fa

_

t

T

2

_

1

_

i

p

(t)

+

_

2S

fa

_

t

T

2

_

+S

fa

(t) 1

_

i

n

(t). (19)

Under symmetrical conditions, the dc rail currents have the

following relationship:

i

n

(t) = i

p

_

t

T

2

_

. (20)

Dene a new switch function

S(t) = 2S

fa

(t) +S

fa

_

t

T

2

_

1. (21)

Substituting (20) and (21) into (18) yields

i

a

(t) = i

p

(t)S(t) i

p

_

t

T

2

_

S

_

t

T

2

_

. (22)

The line current harmonic components can be calculated via

the frequency components of i

p

(t) and S(t) by the convolution

methods.

Ideally, i

p

(t) is periodic with period T/3. Thus, in one

period, i

p

(t) has the following expression:

i

p

(t) = I

m

cos(t),

T

6

t

T

6

. (23)

DU et al.: DC LINK ACTIVE POWER FILTER FOR THREE-PHASE DIODE RECTIFIER 1435

Fig. 8. Switch function S

fa

(t).

Its Fourier series expansion is

i

p

(t) =

n=

I

pn

e

jnt

(24)

where

I

pn

=

3

3

2

(1)

n

3

+1

1

n

2

1

I

m

(25)

and values of n are multiples of 3. The switch function S(t)

can be expressed with harmonic decomposition

S(t) =

n=

S

n

e

jnt

=

n=

2

n

sin

_

n

3

__

1 cos

_

n

3

__

e

jnt

. (26)

Values of n that are multiples of 3 cause S

n

to become zero.

Thus, no multiples of a third harmonic may exist in S(t).

From the property of Fourier expansion for periodic functions,

we have

i

p

_

t

T

2

_

=

n=

(1)

n

I

pn

e

jnt

(27)

S

_

t

T

2

_

=

n=

(1)

n

S

n

e

jnt

. (28)

Substituting (23)(28) into (22) yields the line current

i

a

(t) =

h

C

h

cos(ht). (29)

The coefcient C

h

is

C

h

=

+

l=

4I

pl

S

hl

(30)

or

C

h

= 4I

m

l=

_

3

3

2

(1)

l

3

+1

1

l

2

1

_

_

2

(h l)

sin

_

(h l)

3

__

1 cos

_

(h l)

3

___

(31)

where values of l are multiples of 3, h is odd and h = l. l is the

harmonic order of i

p

(t). When the current loop bandwidth is

innite, both l and h extend to innity. Suppose that the current

loop bandwidth is limited to N times of the fundamental line

frequency, the lower bound and upper bound in the summation

of (31) becomes N and N, respectively. It follows from

(30) that we obtain the relationship between the harmonic

components of the line current and that of the dc rail currents.

Next, we evaluate the line current performance under specic

current loop bandwidth using the relationship (30) and (31).

Ideally, the line current can be compensated by the dc link

APF to harmonic free with innite switching frequency. How-

ever, this is not the case in reality. Suppose that the current

loop bandwidth is limited to the N times of the fundamental

line frequency. Since the harmonic standard only considers the

harmonics up to the 50th order, the line current THD

dc

by the

dc link APF can be calculated as

THD

dc

=

_

50

h=5

C

2

h

C

1

(32)

C

h

is the hth harmonics from (31). Similarly, the line current

THD

ac

by the ac side APF can be expressed as

THD

ac

=

_

50

h=N+1

H

2

h

H

1

(33)

where the coefcient

H

h

=

2

h

sin

_

h

3

_

(1 cos(h)) (34)

is the amplitude of the hth harmonics [36]. It can be seen from

(32) and (33) that the harmonic components in the line current

of the ac side APF start at N + 1, whereas the harmonics starts

at 5 for the dc link APF. This is because the line current of

the dc link APF contains only the (6k 1)th harmonics, where

k is the positive integer.

Table I lists the line current THD for both dc link APF and

ac side APF under various current loop bandwidths. It shows

that under the same current loop bandwidth, compensation per-

formance of the dc link APF is much better than that of the ac

side APF. THD of the dc link APF is less than 0.5% with 1 kHz

or higher current loop bandwidth, and further improvement of

THD by increasing the bandwidth is not signicant. Therefore,

the current loop bandwidth of the dc link APF can be set in the

range of 1 kHz to 2 kHz for the line frequency of 50 Hz in the

practical implementation. Selection of the switching frequency

in the order of ten thousand Hz is reasonable and in good

agreement with the commercial IGBT power devices. Fig. 9

shows the compensated phase current waveforms by the ac side

APF and the dc link APF with 1050 Hz current loop bandwidth.

V. SWITCHING STRESS ANALYSIS

The total active switching stress of switching power convert-

ers is a key measure that determines the converter cost and

efciency [37]. This section provides the evaluation of the total

active switching stress of the proposed dc link APF, the six-

switch three-phase PFC, and the traditional shunt six-switch

three-phase APF. The results will be used to gauge the silicon

1436 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 59, NO. 3, MARCH 2012

TABLE I

COMPARISON OF COMPENSATION PERFORMANCE UNDER

DIFFERENT CURRENT LOOP BANDWIDTH

Fig. 9. Compensated phase a current. (a) ac side APF. (b) dc link APF.

cost and efciency indirectly. The total switching stress SS is

dened in [37] as

SS =

K

j=1

V

j

I

j

(35)

where K is the number of switches in the converter, V

j

is the

voltage stress (peak voltage), and I

j

the current stress (rms

current) applied to active semiconductor switch j.

Comparison is based on the conditions that these circuit

topologies have the same line voltages and the same output

power and work in the same switching frequency. In addition,

the line currents are assumed to be purely sinusoidal, and the

switching frequency related harmonics are ignored. Thus, the

line currents of these three circuits are also the same.

Both of the six-switch three-phase PFCand APF are assumed

to work at bipolar conditions with independent phase current

control. There are six high frequency switches each in these

two topologies, whereas the dc link APF consists of four

high frequency switches and three low frequency ac switches.

TABLE II

COMPARISON OF SWITCHING STRESS

TABLE III

PARAMETERS OF PASSIVE COMPONENTS

Therefore, the switching stress of dc link APF is composed of

both the high frequency switching stress and the low frequency

switching stress.

The voltage stresses of all the high frequency switches are

equal to their own dc bus voltage. For fair comparison, the same

modulation ratio M is selected for all circuits. To avoid the

nonlinearity of the modulation, M should be less than or equal

to 1. In the following, M is selected as one for simplicity of the

analysis.

In a six-switch APF or PFC, the minimum dc bus voltage is

two times the amplitude of the phase voltage. Using the p.u.

unit and modulation ratio M = 1, the dc bus voltage V

dc

has a

value of 2. Thus, the voltage stresses of both PFC and ac APF

are 2 p.u. The peak input voltage of the dual boost circuit in

Fig. 3 is 3/2, as observed from the waveforms in Fig. 4. Due to

M = 1, the dc bus voltage is 3/2. This implies that the voltage

stress of the high frequency switches in the dc link APF is also

3/2. It is also true for the low frequency ac switches.

The input/output voltage relationship with the duty ratio of

down switch at each phase for the three-phase PFC can be

expressed as [38]

d

an

=

1

2

v

a

V

dc

(36)

where d

an

is the duty ratio of the down switch in phase a.

Moreover, the duty ratio d

ap

of the up switch in phase a is

d

ap

= 1 d

an

=

1

2

+

v

a

V

dc

. (37)

Then, the current stress of phase a in the three-phase PFC can

be calculated as [37]

I

ap

=

1

T

_

T

0

i

2

a

(t)d

ap

dt (38)

I

an

=

1

T

_

T

0

i

2

a

(t)d

an

dt (39)

DU et al.: DC LINK ACTIVE POWER FILTER FOR THREE-PHASE DIODE RECTIFIER 1437

Fig. 10. Simulated steady-state response with inductive load. (a) dc link APF OFF. (b) dc link APF ON. (c) Current waveforms of positive boost converter.

(d) dc bus voltages.

where T is the line period. From the three-phase symmetry,

the current stress for other two phases will have the same

value.

Similar arguments can be applied to the three-phase ac APF.

The duty ratios of the down and up switches in phase a have the

same expression as those of three-phase PFC. Since the current

processed by the inverter is the difference between the load

current and the line current, the current stress of phase a can

be calculated as

I

ap

=

1

T

_

T

0

i

2

La

(t)d

ap

dt (40)

I

an

=

1

T

_

T

0

i

2

La

(t)d

an

dt (41)

where i

La

is the inductor current in phase a.

The same process can be applied to calculate the high fre-

quency current stress in the dc link APF, where the duty ratio

of the high frequency switches S

p1

and S

n1

in the dc link APF

can be expressed as, respectively,

d

p

=1

v

pm

V

c

(42)

d

n

=1

v

mn

V

c

. (43)

The inductor currents i

Lp

and i

Ln

are used to calculate the

current stress. For the low frequency ac switches, the currents

owing through them are portion of the line currents. Their

current stresses can be calculated based on the rms denition

directly and, thus, independent of the duty ratio.

Table II summarizes the values of switching stress for the six-

switch PFC, the six-switch APF, and the dc link APF obtained

from the voltage and current stress calculation discussed above.

As shown in Table II, the six-switch PFC has the highest total

switching stress. Its value is nearly three times that of the

ac APF and two times that of the dc link APF. The higher

total switching stress of the dc link APF than the ac APF is

mainly due to the fact that portion of the line current ows

1438 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 59, NO. 3, MARCH 2012

through the ac switch and incurs higher conduction loss in the

dc link APF. However, the high frequency switching stress of

the dc link APF is about one-third that of the ac APF. This

feature will enable the dc link APF to work more efciently

in that the high frequency switching loss usually dominates

the total loss in the switching power converter [37]. The result

demonstrates the silicon cost reduction property of the dc

link APF.

VI. SIMULATION AND EXPERIMENTAL RESULTS

A. Simulation Studies

Simulations were carried out to examine the performance

of the dc link APF to complement the experimental results.

Three cases are investigated. They are: 1) the steady-state

response; and 2) the transient response with inductive load; and

3) steady-state response with capacitive load. The parameters

used include the line frequency f = 50 Hz, line-line RMS

voltage 380 V, L

p

= L

n

= 4 mH, C

p

= C

n

= 500 F, V

cp

=

V

cn

= 550 V, and the switching frequency is 20 kHz. Inductive

dc load is a RL load where R = 20 and L = 100 mH.

Capacitive load is a RC load, where C = 200 F, R = 20 ,

and a 5 mH inductor is inserted before the RC load to smooth

the dc load current. The parameters of the passive components

in real value and in p.u. value are summarized in Table III. The

impedance base is the value of the load resistor 20 .

Simulation results of the steady-state response with inductive

load are shown in Fig. 10. Fig. 10(a) and (b) show the source

current waveforms and the load voltage and current waveforms

when the dc link APF is OFF and ON, respectively. Fig. 10(c)

shows the current of the positive part boost converter. The

dc bus voltage waveforms are shown in Fig. 10(d). THD of

the source current was 30.84% without compensation and was

reduced to 3.34% with compensation of the proposed dc link

APF. It is observed from Fig. 10(a) and (b) that both the load

voltage waveform and current waveform are nearly the same

with or without the dc link APF. This is in agreement with

the performance of the shunt ac APF; that is, APF does not

affect the performance of load voltage and load current. The dc

component of the load current is 25.66 A, and the peak-peak

300 Hz current ripple is about 0.3 A. This dc value is very close

to the dc component of the load, 25.72 A, of an ideal three-

phase diode rectier loaded by a pure resistor. It is observed

from Fig. 10(c) that the dc component of i

p

is 23.40 A, which

is also the same as the calculated value. The dc voltage sum

of the split capacitors is 1100 V, which is equal to the reference

voltage. The peak-peak voltage ripple of each capacitor is about

7 V with 150 Hz frequency, but the peak-peak ripple of the

sum of these two capacitors is reduced to about 3 V and the

frequency is 300 Hz. This is due to the nearly 180

phase shift

between v

cp

and v

cn

, which leads to harmonic cancellation.

Hence, we select (v

cp

+v

cn

) as the feedback signal in the

voltage loop of Fig. 6 because of the low ripple factor.

The transient response under dc load resistor change and

source voltage change is shown in Fig. 11. Fig. 11(a) displays

the response when the dc load resistor changes from 20 to

40 at the time instance of 0.4 s and changed back to 20 at

Fig. 11. Simulated transient responses with inductive load. (a) Load change

from 20 to 40 at 0.4s and changed back to 20 at 0.5 s. (b) Source voltage

drop 30% at 0.4 s and return to the rated value at 0.5 s.

0.5 s. Fig. 11(b) displays the response under the circumstance

that source voltage has a 30% voltage drop at 0.4 s and return

to the rated value at 0.5 s. These results of load change and

source voltage change examine the transient performance of the

control design discussed in Section III.

The voltage loop bandwidth affects the dynamic perfor-

mance. The transient response can be improved by setting the

voltage loop bandwidth higher, as illustrated in Fig. 12. In the

simulations, the dc load resistor changes from 20 to 40 at

the time instance of 0.3 s and changes back to 20 at 0.5 s.

The results shown in Fig. 12(a) and (b) are for the 15 Hz and

the 60 Hz voltage loop bandwidth, respectively. It is observed

from Fig. 12(a) that the overshoot of dc voltage is about 90 V

and the settling time is about 150 ms. On the other hand, the

overshoot is about 20 V, and the settling time is about 20 ms for

the 60 Hz voltage loop bandwidth. This demonstrates that the

dynamical performance can be improved with higher voltage

loop bandwidth.

The diode rectier with a capacitive load was also investi-

gated. The results are presented in Fig. 13. The line current

after compensation is 8.1%, which is much higher than that

in the inductive condition. The reason is that the shunt APF is

more suitable for compensating inductive load and current type

harmonic source, but not for the capacitive load or voltage type

harmonic source [39].

DU et al.: DC LINK ACTIVE POWER FILTER FOR THREE-PHASE DIODE RECTIFIER 1439

Fig. 12. Load transient simulation results. (a) With 15 Hz voltage loop

bandwidth. (b) With 60 Hz voltage loop bandwidth.

Fig. 13. Steady-state response with capacitive load.

Fig. 14. Experimental results with current loop bandwidth of 1 kHz. (a) dc

link APF OFF; (b) dc link APF ON; and (c) current waveforms of the positive

boost converter.

B. Experimental Results

A 2 kW prototype was constructed in the lab to verify

the performance of the proposed dc link APF. Most of the

parameters used in the experiment are the same as in the

simulation study, except that the dc load is a RL load with

R = 110 and L = 0.5 mH. The ac switch is implemented

by MOSFET IRFP460 and the high frequency switch by IGBT

PM75DSA120. The current is sensed by the LEM HX20-P

current sensor. Digital controller is realized by the Freescale

DSP chip MC56F8323.

Experimental results with 1 kHz current loop bandwidth are

shown in Fig. 14. Fig. 14(a) displays the current waveforms

1440 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 59, NO. 3, MARCH 2012

Fig. 15. Experimental results with 2 kHz current loop bandwidth.

when dc link APF is not functioning, and Fig. 14(b) exhibits the

waveforms when the dc link APF is working. Fig. 14(c) shows

the current waveforms of the positive part boost converter.

These current waveforms agree with those currents shown in

the middle panel of Fig. 4. The current i

Lp

processed by the

dc link APF is just partial of the load current and is much

smaller than the load current, as can be seen from Fig. 14(c).

Moreover, extensive experiments have been conducted with

increased current bandwidths. The result for 2 kHz bandwidth

is shown in Fig. 15. It can be seen from Figs. 14(b) and 15

that the time domain line currents are no difference with either

the 1 kHz or the 2 kHz bandwidth. This result veries the

conclusion drawn in Section IV that the dc link APF has already

achieved satisfactory harmonics compensation effect with

1 kHz bandwidth. Increasing the current loop bandwidth further

does not add much to the harmonics reduction.

Frequency domain analysis from the measured data is con-

ducted to quantify the bandwidth effect. For example, the line

current THD without compensation is 27.1% and is reduced to

6.1% with 1 kHz bandwidth. It is further reduced to 4.9% with

2 kHz bandwidth. The spectrum comparison with 1 and 2 kHz

bandwidths is shown in Fig. 16. It shows that amplitudes of

both line current harmonics are almost the same. The measured

THD value is larger than the value presented in Table I, which is

caused by the non-ideal condition in practical implementations.

The THD difference of 1 kHz and 2 kHz is 1.2%, which is

coincided with the performance tension of the dc link APF.

Our test result (4.9% THD) is better than 8.5% THD obtained

in [26].

The transient input currents and dc bus voltage under load

change were also tested. The results are shown in Fig. 17. The

current and voltage responses for the load R changing from

220 to 110 are shown in Fig. 17(a), and responses with

R increasing from 110 to 220 are shown in Fig. 17(b). It is

observed that the input currents move from one stable operation

state to another stable operation state. The dc bus voltage goes

back to the rated value after the transient stage. Results of

Fig. 17 were obtained from the 15 Hz voltage loop bandwidth,

which was selected to reduce the effect of the low frequency

voltage ripple from the dc bus voltage. These responses take

a few line cycles to settle down. The relative long transient

interval is due to the low voltage loop bandwidth.

Fig. 16. Spectrum comparison for different current loop bandwidth; the

purple bar is for 1 kHz and dark red bar for 2 kHz.

Fig. 17. Transient response under load change. (a) Step-up load. (b) Step-

down load.

VII. CONCLUSION

A novel harmonic reduction method, which uses the dc link

APF for three-phase diode rectier, has been presented. Aver-

age current control with input voltage feedforward is applied

to the control of this circuit. Voltage loop and current loop

models have been developed for control design. Evaluation

on the relationship between compensation performance and

current loop bandwidth has also been presented. The results

show that, under the same current loop bandwidth, the dc link

APF performs better than the ac side APF. Even though the

compensation performance of the dc link APF is inferior to that

of the three-phase PFC, it is still well above the requirements

set by the IEC 61000-3-2 Class A standard [40]. Results of

DU et al.: DC LINK ACTIVE POWER FILTER FOR THREE-PHASE DIODE RECTIFIER 1441

switching stress comparison reveal that the dc link APF has

the potential of high efciency and better silicon cost reduction

ability than the six-switch PFC. Therefore, the dc link APF and

the developed control scheme offer a high performance low cost

alternative for the harmonic elimination of three-phase diode

rectier. A major limitation of the proposed circuit is that, if

the galvanic isolation is required, the isolation transformer is

expensive and bulky due to the dc component in voltage and

current processed by the dc link APF.

REFERENCES

[1] S. M. Halpin, Comparison of IEEE and IEC harmonic standards, in

Proc. IEEE Power Eng. Soc. Gen. Meeting, Jun. 2005, pp. 22142216.

[2] T. Thasananutariya and S. Chatratana, Planning study of harmonic lter

for ASDs in industrial facilities, IEEE Trans. Ind. Appl., vol. 45, no. 1,

pp. 295302, Jan./Feb. 2009.

[3] Z. Chen and Y. Luo, Low-harmonic-input three-phase rectier with pas-

sive auxiliary circuit: Comparison and design consideration, IEEE Trans.

Ind. Electron., vol. 58, no. 6, pp. 22652273, Jun. 2011.

[4] P. J. Grbovic, P. Delarue, and P. L. Moigne, A novel three-phase diode

boost rectier using hybrid half-dc-bus-voltage rated boost converter,

IEEE Trans. Ind. Electron., vol. 58, no. 4, pp. 13161329, Apr. 2011.

[5] V. Corasaniti, M. Barbieri, P. Arnera, and M. Valla, Hybrid active lter

for reactive and harmonics compensation in a distribution network, IEEE

Trans. Ind. Electron., vol. 56, no. 3, pp. 670677, Mar. 2009.

[6] B. Singh and J. Solanki, Implementation of an adaptive control algorithm

for a three-phase shunt active lter, IEEE Trans. Ind. Electron., vol. 56,

no. 8, pp. 28112820, Aug. 2009.

[7] E. Lavopa, P. Zanchetta, M. Sumner, and F. Cupertino, Real-time esti-

mation of fundamental frequency and harmonics for active shunt power

lters in aircraft electrical systems, IEEE Trans. Ind. Electron., vol. 56,

no. 8, pp. 28752884, Aug. 2009.

[8] S. Rahmani, N. Mendalek, and K. Al-Haddad, Experimental design of

a nonlinear control technique for three-phase shunt active power lter,

IEEE Trans. Ind. Electron., vol. 57, no. 10, pp. 33643375, Oct. 2010.

[9] O. Vodyakho and C. Mi, Three-level inverter-based shunt active power

lter in three-phase three-wire and four-wire systems, IEEE Trans.

Power Electron., vol. 24, no. 5, pp. 13501363, May 2009.

[10] P. Salmeron and S. P. Litran, Improvement of the electric power quality

using series active and shunt passive lters, IEEE Trans. Power Del.,

vol. 25, no. 2, pp. 10581067, Apr. 2010.

[11] A. Bhattacharya and C. Chakraborty, A shunt active power lter with

enhanced performance using ANN-based predictive and adaptive con-

trollers, IEEE Trans. Ind. Electron., vol. 58, no. 2, pp. 421428,

Feb. 2011.

[12] A. Gensior, H. Sira-Ramirez, J. Rudolph, and H. Guldner, On some

nonlinear current controllers for three-phase boost rectiers, IEEE Trans.

Ind. Electron., vol. 56, no. 2, pp. 360370, Feb. 2009.

[13] M. H. Bierhoff and F. W. Fuchs, Active damping for three-phase PWM

rectiers with high-order line-side lters, IEEE Trans. Ind. Electron.,

vol. 56, no. 2, pp. 371379, Feb. 2009.

[14] M. L. Heldwein and J. W. Kolar, Impact of EMC lters on the power

density of modern three-phase PWM converters, IEEE Trans. Power

Electron., vol. 24, no. 6, pp. 15771588, Jun. 2009.

[15] D. Carlton, W. Dunford, and M. Edmunds, Harmonic reduction in the

3-phase 3-switches boost-delta power factor correction circuit operating in

discontinuous conduction mode, in Proc. 20th Int. Telecommun. Energy

Conf., Oct. 1998, pp. 483490.

[16] L. Dalessandro, S. D. Round, U. Drofenik, and J. W. Kolar, Discontinu-

ous space-vector modulation for three-level PWM rectiers, IEEE Trans.

Power Electron., vol. 23, no. 2, pp. 530542, Mar. 2008.

[17] F. J. Chivite-Zabalza, A. J. Forsyth, and I. Araujo-Vargas, 36-Pulse

hybrid ripple injection for high-performance aerospace rectiers, IEEE

Trans. Ind. Appl., vol. 45, no. 3, pp. 992999, May/Jun. 2009.

[18] A. le Roux, H. Mouton, and H. Akagi, DFT-based repetitive control of a

series active lter integrated with a 12-pulse diode rectier, IEEE Trans.

Power Electron., vol. 24, no. 6, pp. 15151521, Jun. 2009.

[19] J. C. Salmon, Reliable 3-phase PWM boost rectiers employing a

stacked dual boost converter subtopology, IEEE Trans. Ind. Appl.,

vol. 32, no. 3, pp. 542551, May/Jun. 1996.

[20] C. Qiao and K. M. Smedley, A general three-phase PFC controller for

rectiers with a series-connected dual-boost topology, IEEE Trans. Ind.

Appl., vol. 38, no. 1, pp. 137148, Jan./Feb. 2002.

[21] N. Mohan, A novel approach to minimize line-current harmonics in

interfacing power electronics equipment with 3-phase utility systems,

IEEE Trans. Power Del., vol. 8, no. 3, pp. 13951401, Jul. 1993.

[22] R. Naik, M. Rastogi, and N. Mohan, Third-harmonic modulated power

electronics interface with three-phase utility to provide a regulated dc

output and to minimize line-current harmonics, IEEE Trans. Ind. Appl.,

vol. 31, no. 3, pp. 598602, May/Jun. 1995.

[23] S. Kim, P. N. Enjeti, P. Packebush, and I. J. Pital, A new approach

to improve power factor and reduce harmonics in a three-phase diode

rectier type utility interface, IEEE Trans. Ind. Appl., vol. 30, no. 6,

pp. 15571564, Nov./Dec. 1994.

[24] P. Pejovic and Z. Janda, An analysis of three-phase low-harmonic recti-

ers applying the third-harmonic current injection, IEEE Trans. Power

Electron., vol. 14, no. 3, pp. 397407, Mar. 1999.

[25] P. Pejovic and Z. Janda, An improved current injection network for

three-phase high-power-factor rectiers apply the third harmonic cur-

rent injection, IEEE Trans. Ind. Electron., vol. 47, no. 2, pp. 497499,

Apr. 2000.

[26] J.-I. Itoh and I. Ashida, A novel three-phase PFC rectier using a har-

monic current injection method, IEEE Trans. Power Electron., vol. 23,

no. 2, pp. 715722, Mar. 2008.

[27] N. Vazquez, H. Rodriguez, C. Hernandez, E. Rodriguez, and J. Arau,

Three-phase rectier with active current injection and high efciency,

IEEE Trans. Ind. Electron., vol. 56, no. 1, pp. 110119, Jan. 2009.

[28] K. M. Smedley, L. Zhou, and C. Qiao, Unied constant-frequency inte-

gration control of active power ltersSteady-state and dynamics, IEEE

Trans. Power Electron., vol. 16, no. 3, pp. 428436, May 2001.

[29] O. Garca, M. Dolores Martnez-Avial, J. A. Cobos, J. Uceda,

J. Gonzalez, and J. A. Navas, Harmonic reducer converter, IEEE Trans.

Ind. Electron., vol. 50, no. 2, pp. 322327, Apr. 2003.

[30] W. Zhang, G. Asplund, A. berg, U. Jonsson, and O. Lf, Active DC

lter for HVDC systemA test installation in the Konti-Skan DC link

at Lindome converter station, IEEE Trans. Power Del., vol. 8, no. 3,

pp. 15991606, Jul. 1993.

[31] J. Sun and R. M. Bass, Modeling and practical design issues for average

current control, in Proc. IEEE Appl. Power Electron. Conf. Expo., Dallas,

TX, 1999, pp. 980986.

[32] M. Chen and J. Sun, Feedforward current control of boost single-phase

PFC converters, IEEE Trans. Power Electron., vol. 21, no. 2, pp. 338

345, Mar. 2006.

[33] V. Thottuvelil, D. Chin, and G. C. Verghese, Hierarchical approaches

to modeling high-power-factor AC-DC converters, IEEE Trans. Power

Electron., vol. 6, no. 2, pp. 179187, Apr. 1991.

[34] J. Sun, On the zero-crossing distortion in single-phase PFC converters,

IEEE Trans. Power Electron., vol. 19, no. 3, pp. 685692, May 2004.

[35] G. F. Franklin, J. D. Powell, and A. Emani-Naeini, Feedback Control of

Dynamic System, 5th ed. Upper Saddle River, NJ: Pearson, 2006.

[36] B. K. Bose, Modern Power Electronics and AC Drives, 1st ed. New

Jersey, USA: Pearson, 2002.

[37] R. W. Erickson, Fundamentals of Power Electronics, 2nd ed. Secaucus,

NJ: Kluwer, 2000.

[38] C. Qiao and K. M. Smedley, Unied constant-frequency integration

control of three-phase standard bridge boost rectiers with power-factor

correction, IEEE Trans. Ind. Electron., vol. 50, no. 1, pp. 100107,

Feb. 2003.

[39] F. Z. Peng, Harmonic sources and ltering approaches, IEEE Ind. Appl.

Mag., vol. 7, no. 4, pp. 1825, Jul./Aug. 2001.

[40] Electromagnetic Compatibility (EMC), Part 3, Int. Std. IEC61 000-3-2,

2001.

Xiong Du obtained the B.S., M.S., and Ph.D. degrees

in the electrical engineering from Chongqing Uni-

versity, Chongqing, China, in 2000, 2002, and 2005,

respectively.

He has been with Chongqing University, since

2002 and is currently a professor in the College

of Electrical Engineering, Chongqing University. He

was a visiting scholar at Rensselaer Polytechnic

Institute, Troy, NY, from July 2007 to July 2008.

His research interests include switching power con-

verters, power quality control, and renewable energy

power conversion.

Dr. Du is a recipient of the National Excellent Doctoral Dissertation of China

in 2008.

1442 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 59, NO. 3, MARCH 2012

Luowei Zhou (M04SM04) received the B.S.,

M.S., and Ph.D. degrees in electrical engineering at

Chongqing University, Chongqing, China, in 1982,

1988, and 2000, respectively.

Since 1982, he has been with the College of Elec-

trical Engineering, Chongqing University, China,

where he is now a full professor. He was a visiting

professor at the University of California, Irvine, be-

tween September 1998 and August 1999. He is the

administrative director of China Society of Power

Supply. His major elds of interest include the analy-

sis and control of power electronics circuits, realization of active power lters,

power factor correction techniques, and high frequency power conversion. He

has published more than 60 papers, holds one US patent and three China

patents, and has three patents pending.

Hao Lu received the B.S. and M.S. degrees in

electrical engineering from Chongqing University,

Chongqing, China, in 2006 and 2009, respectively.

He has been with the Delta Energy System as a

senior electronic design engineer since 2009. His re-

search interests include switching power converters

and power quality control.

Heng-Ming Tai (M87SM93) received the B.S.

degree in electrical engineering fromNational Tsing-

Hua University, Hsinchu, Taiwan, and the M.S. and

Ph.D. degrees in electrical engineering from Texas

Tech University, Lubbock, in 1987.

He is a professor in the Department of Electrical

Engineering at the University of Tulsa, Tulsa, OK.

His research interests are in the areas of signal and

image processing and industrial electronics.

Dr. Tai is a member of Eta Kappa Nu and a senior

member of IEEE.

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Process DocumentationDocument26 pagesProcess DocumentationKhaleel NazeerNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Invoice Tracker Dashboard v.1.0Document19 pagesInvoice Tracker Dashboard v.1.0علي عبدالله قاسم شلحNo ratings yet

- FreeCAD Manual 0 16Document566 pagesFreeCAD Manual 0 16Myo Aung100% (2)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Mak4462 Machine Tools: Yildiz Technical University Faculty of Mechanical Engineering Department of Mechanical EngineeringDocument12 pagesMak4462 Machine Tools: Yildiz Technical University Faculty of Mechanical Engineering Department of Mechanical EngineeringALPERENNo ratings yet

- Ti Sns50-Hba0-S01 1034097Document8 pagesTi Sns50-Hba0-S01 1034097zaleksNo ratings yet

- ProFlex4 Trainings OverviewDocument16 pagesProFlex4 Trainings Overviewart0928No ratings yet

- Worked Example Earthing CalculationDocument6 pagesWorked Example Earthing CalculationMustafa KamalNo ratings yet

- IWPT-PL-1: Index Terms - Solar Power Satellite, Wireless PowerDocument4 pagesIWPT-PL-1: Index Terms - Solar Power Satellite, Wireless PowerPrashanth Kumar ShettyNo ratings yet

- Micro GridDocument12 pagesMicro GridPrashanth Kumar ShettyNo ratings yet

- DiodeDocument4 pagesDiodePrashanth Kumar ShettyNo ratings yet

- Micro GridDocument12 pagesMicro GridPrashanth Kumar ShettyNo ratings yet

- Netpro Operation Manual 2k0 4k0 VaDocument20 pagesNetpro Operation Manual 2k0 4k0 VaDanny Dan100% (2)

- 24 PDFDocument8 pages24 PDFmohammedNo ratings yet

- Résumé For Arjun JayaramanDocument1 pageRésumé For Arjun JayaramanArjun JayaramanNo ratings yet

- Vishwakarma Institute E&TC curriculumDocument37 pagesVishwakarma Institute E&TC curriculumAbhijeet KadamNo ratings yet

- Elec Grs Pumps 203seriesDocument5 pagesElec Grs Pumps 203serieschand_yelNo ratings yet

- 1.4 NN MP Neuron ModelDocument20 pages1.4 NN MP Neuron ModelSatyam RanaNo ratings yet

- Quality Gates Ensure Project SuccessDocument7 pagesQuality Gates Ensure Project Successbelkis rosaNo ratings yet

- Holiday Accident Reduction Program: SSGT 32 Comm/ElectDocument3 pagesHoliday Accident Reduction Program: SSGT 32 Comm/ElectSteven GarrisNo ratings yet

- D ch07Document50 pagesD ch07mullai03No ratings yet

- Step 4.1 Manage Incoming Data: Resources For Implementing The WWF Project & Programme StandardsDocument9 pagesStep 4.1 Manage Incoming Data: Resources For Implementing The WWF Project & Programme StandardsTran Thi HaiNo ratings yet

- Food Processing Machinery - Fixed Deck Oven Loaders - Safety and Hygiene RequirementsDocument50 pagesFood Processing Machinery - Fixed Deck Oven Loaders - Safety and Hygiene RequirementsSantosh IngaleNo ratings yet

- MP and MC Lab Solution ManualDocument48 pagesMP and MC Lab Solution ManualsukeerthNo ratings yet

- Three-Phase Electric Power - Wikipedia, The Free EncyclopediaDocument12 pagesThree-Phase Electric Power - Wikipedia, The Free EncyclopediaMohamed RafihNo ratings yet

- Labview & MatlabDocument7 pagesLabview & MatlabSuneet SahuNo ratings yet

- Best Practices For Tensorrt PerformanceDocument20 pagesBest Practices For Tensorrt PerformanceacabaNo ratings yet

- Mixed Signal Electronics IntroductionDocument32 pagesMixed Signal Electronics IntroductionMuhammad Waqas AliNo ratings yet

- 2.manual ETR300S V1.0 EngDocument142 pages2.manual ETR300S V1.0 EngAgustinus Phatub KurniawanNo ratings yet

- Literature Review For Petrol Station Management SystemDocument7 pagesLiterature Review For Petrol Station Management Systemc5qp53eeNo ratings yet

- WachsDocument64 pagesWachsJorgeNo ratings yet

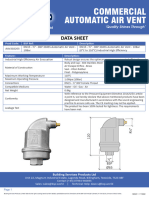

- BSP - Commercial AAV - 10bar - DataSheet - V1.1 - 11-2022Document1 pageBSP - Commercial AAV - 10bar - DataSheet - V1.1 - 11-2022j.iqubalNo ratings yet

- Control Gear Fluorescent Electronic EB-ECONOMY Electronic Ballasts For TLD LampsDocument6 pagesControl Gear Fluorescent Electronic EB-ECONOMY Electronic Ballasts For TLD LampsGary LauNo ratings yet

- ROMDAS ManualDocument327 pagesROMDAS Manualkumarnram0% (1)

- PCChips P53G Manual PDFDocument53 pagesPCChips P53G Manual PDFsander100% (1)