Professional Documents

Culture Documents

Vishay Siliconix SPICE Device Model Si4362BDY N-Channel 30-V (D-S) Reduced Q, Fast Switching WFET

Uploaded by

dreyes3773Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Vishay Siliconix SPICE Device Model Si4362BDY N-Channel 30-V (D-S) Reduced Q, Fast Switching WFET

Uploaded by

dreyes3773Copyright:

Available Formats

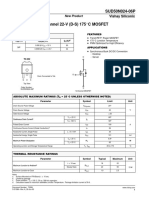

SPICE Device Model Si4362BDY Vishay Siliconix N-Channel 30-V (D-S) Reduced Qgd, Fast Switching WFET

CHARACTERISTICS

N-Channel Vertical DMOS Macro Model (Subcircuit Model) Level 3 MOS Apply for both Linear and Switching Application Accurate over the 55 to 125C Temperature Range Model the Gate Charge, Transient, and Diode Reverse Recovery Characteristics

DESCRIPTION

The attached spice model describes the typical electrical characteristics of the n-channel vertical DMOS. The subcircuit model is extracted and optimized over the 55 to 125C temperature ranges under the pulsed 0-V to 10-V gate drive. The saturated output impedance is best fit at the gate bias near the threshold voltage. A novel gate-to-drain feedback capacitance network is used to model the gate charge characteristics while avoiding convergence difficulties of the switched Cgd model. All model parameter values are optimized to provide a best fit to the measured electrical data and are not intended as an exact physical interpretation of the device.

SUBCIRCUIT MODEL SCHEMATIC

This document is intended as a SPICE modeling guideline and does not constitute a commercial product data sheet. Designers should refer to the appropriate data sheet of the same number for guaranteed specification limits. Document Number: 74137 S-52211Rev. A, 24-Oct-05 www.vishay.com 1

SPICE Device Model Si4362BDY Vishay Siliconix

SPECIFICATIONS (TJ = 25C UNLESS OTHERWISE NOTED) Parameter Static

Gate Threshold Voltage On-State Drain Current

a

Symbol

Test Condition

Simulated Data

1.1 1285 0.0037 0.0042 27 0.75

Measured Data

Unit

VGS(th) ID(on) rDS(on) gfs VSD

VDS = VGS, ID = 250 A VDS 5 V, VGS = 10 V VGS = 10 V, ID = 19.8A VGS = 4.5 V, ID = 18.2A VDS = 15 V, ID = 19.8A IS = 5A

V A 0.0038 0.0043 120 0.70 S V

Drain-Source On-State Resistancea Forward Transconductancea Diode Forward Voltagea

Dynamicb

Input Capacitance Output Capacitance Reverse Transfer Capacitance Total Gate Charge Gate-Source Charge Gate-Drain Charge Ciss Coss Crss Qg Qgs Qgd VDS = 15 V, VGS = 10 V, ID = 19.8A VDS = 15 V, VGS = 0 V, f = 1 MHz 5194 540 148 73 35 VDS = 15 V, VGS = 4.5 V, ID = 19.8A 9 6.5 4800 500 200 75 36 9 6.5 nC pF

Notes a. Pulse test; pulse width 300 s, duty cycle 2%. b. Guaranteed by design, not subject to production testing.

www.vishay.com 2

Document Number: 74137 S-52211Rev. A, 24-Oct-05

SPICE Device Model Si4362BDY Vishay Siliconix

COMPARISON OF MODEL WITH MEASURED DATA (TJ=25C UNLESS OTHERWISE NOTED)

Document Number: 74137 S-52211Rev. A, 24-Oct-05

www.vishay.com 3

You might also like

- High Voltage Direct Current Transmission: Converters, Systems and DC GridsFrom EverandHigh Voltage Direct Current Transmission: Converters, Systems and DC GridsNo ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- N Mosfet Fdv303nDocument4 pagesN Mosfet Fdv303nxlam99No ratings yet

- Datasheet FDB44N25Document8 pagesDatasheet FDB44N25jalvarez_385073No ratings yet

- Fds8958A: Dual N & P-Channel Powertrench MosfetDocument11 pagesFds8958A: Dual N & P-Channel Powertrench MosfetbyronzapetaNo ratings yet

- SPICE Device Model SQD50P06-15L: Vishay SiliconixDocument4 pagesSPICE Device Model SQD50P06-15L: Vishay SiliconixManikanta Sai KumarNo ratings yet

- MTP52N06V Datasheet - 2 PDFDocument7 pagesMTP52N06V Datasheet - 2 PDFLeonel ValençaNo ratings yet

- D13a Motor de PartidaDocument8 pagesD13a Motor de Partidaalex lottiNo ratings yet

- Datasheet Mosfet Final RF PDFDocument4 pagesDatasheet Mosfet Final RF PDFVenkatesh KarriNo ratings yet

- 80 N 06Document8 pages80 N 06Miltongrimi GrimilNo ratings yet

- 7N65 PDFDocument8 pages7N65 PDFboedagbageurNo ratings yet

- 9N90CDocument8 pages9N90CjostranNo ratings yet

- Irf 4905 PBFDocument9 pagesIrf 4905 PBFEverton RamiresNo ratings yet

- 3055 MosfetDocument8 pages3055 Mosfetmcinfo30No ratings yet

- 4800 AgmDocument5 pages4800 AgmaluiznetNo ratings yet

- AO4433 P-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionDocument4 pagesAO4433 P-Channel Enhancement Mode Field Effect Transistor: Features General Descriptionpepegotera454No ratings yet

- N-Channel Junction FET: Guangdong Yuejing High Technology CO.,LTDDocument1 pageN-Channel Junction FET: Guangdong Yuejing High Technology CO.,LTDLaura ZambranoNo ratings yet

- Power Mosfet THRU-HOLE (TO-254AA) IRFM460 500V, N-CHANNELDocument7 pagesPower Mosfet THRU-HOLE (TO-254AA) IRFM460 500V, N-CHANNELSim AbdeeNo ratings yet

- Spice Device Model Sis890Dn: Vishay SiliconixDocument4 pagesSpice Device Model Sis890Dn: Vishay Siliconixzinouu113113No ratings yet

- NDP6051 / NDB6051 N-Channel Enhancement Mode Field Effect TransistorDocument6 pagesNDP6051 / NDB6051 N-Channel Enhancement Mode Field Effect TransistorHoàng Ngọc QuyềnNo ratings yet

- Qfet Qfet Qfet Qfet: FQP55N10Document8 pagesQfet Qfet Qfet Qfet: FQP55N10andreanuovoNo ratings yet

- SPICE Device Model SQD100N04-3m6 N-Channel 40 V (D-S) 175 °C MOSFETDocument4 pagesSPICE Device Model SQD100N04-3m6 N-Channel 40 V (D-S) 175 °C MOSFETAli KeyvanNo ratings yet

- FDP 2614Document8 pagesFDP 2614HadeedAhmedSherNo ratings yet

- Datasheet IRFZ34NDocument9 pagesDatasheet IRFZ34NcandabiNo ratings yet

- Irlr 7843Document12 pagesIrlr 7843Idris LMNo ratings yet

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument12 pagesN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datameroka2000No ratings yet

- FQPF17P06: 60V P-Channel MOSFETDocument8 pagesFQPF17P06: 60V P-Channel MOSFETMahmoued YasinNo ratings yet

- FQP6N60Document8 pagesFQP6N60achuthkumarNo ratings yet

- Unisonic Technologies Co., LTD: 8A, 650V N-Channel Power MosfetDocument8 pagesUnisonic Technologies Co., LTD: 8A, 650V N-Channel Power MosfetMarcos RangelNo ratings yet

- TPO 610 MosfetDocument4 pagesTPO 610 MosfetCalinhosBaoNo ratings yet

- TPO 610 Mosfet PDFDocument4 pagesTPO 610 Mosfet PDFCalinhosBaoNo ratings yet

- Irfr3707Zpbf Irfu3707Zpbf: V R Max QGDocument11 pagesIrfr3707Zpbf Irfu3707Zpbf: V R Max QGJared RobisonNo ratings yet

- IRFPS40N60K: Smps MosfetDocument9 pagesIRFPS40N60K: Smps MosfetRoozbeh BahmanyarNo ratings yet

- 2N7002K PDFDocument3 pages2N7002K PDFhanakuNo ratings yet

- Am4502c PDFDocument8 pagesAm4502c PDFelkillyNo ratings yet

- Fqa6n70700v N-Channel MosfetDocument8 pagesFqa6n70700v N-Channel MosfetbmmostefaNo ratings yet

- SSF 7510Document5 pagesSSF 7510luis_h_t_79No ratings yet

- Sihg20N50C: Vishay SiliconixDocument8 pagesSihg20N50C: Vishay SiliconixengrmunirNo ratings yet

- Fqa5n90900v N-Channel MosfetDocument8 pagesFqa5n90900v N-Channel MosfetbmmostefaNo ratings yet

- MTW14N50EDocument8 pagesMTW14N50EroozbehxoxNo ratings yet

- MTP2955V Power MOSFET 12 Amps, 60 Volts: P-Channel TO-220Document8 pagesMTP2955V Power MOSFET 12 Amps, 60 Volts: P-Channel TO-220Rodrigo AlemánNo ratings yet

- Me 4856Document4 pagesMe 4856asadeng4318No ratings yet

- FQD2N60C / FQU2N60C: N-Channel Qfet MosfetDocument9 pagesFQD2N60C / FQU2N60C: N-Channel Qfet MosfetTomescu MarianNo ratings yet

- 4 N 60 JJJDocument8 pages4 N 60 JJJnaveed khanNo ratings yet

- Radiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELDocument8 pagesRadiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELbmmostefaNo ratings yet

- 50N024Document4 pages50N024Roozbeh BahmanyarNo ratings yet

- Si4425BDY: Vishay SiliconixDocument5 pagesSi4425BDY: Vishay SiliconixElisabeth BaraNo ratings yet

- FDS4435BZDocument6 pagesFDS4435BZCornel PislaruNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument6 pagesAdvanced Power Electronics Corp.: DescriptionMaugrys CastilloNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument6 pagesAdvanced Power Electronics Corp.: DescriptionMaugrys CastilloNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument6 pagesAdvanced Power Electronics Corp.: DescriptionMaugrys CastilloNo ratings yet

- Irfp460A, Sihfp460A: Vishay SiliconixDocument7 pagesIrfp460A, Sihfp460A: Vishay SiliconixlyorhitmaNo ratings yet

- AO4412 N-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionDocument4 pagesAO4412 N-Channel Enhancement Mode Field Effect Transistor: Features General Descriptiondreyes3773No ratings yet

- HUF75332S3Document10 pagesHUF75332S3WallyWallysNo ratings yet

- Irf7832Pbf: V R Max QGDocument10 pagesIrf7832Pbf: V R Max QGdreyes3773No ratings yet

- Irf 1407Document10 pagesIrf 1407Adilson BogadoNo ratings yet

- Dual N-Channel Enhancement Mode Field Effect Transistor: FeaturesDocument5 pagesDual N-Channel Enhancement Mode Field Effect Transistor: FeaturesBvm BvmmNo ratings yet

- DatasheetDocument4 pagesDatasheetAbdul MaliqNo ratings yet

- 600V N-Channel MOSFET: FeaturesDocument8 pages600V N-Channel MOSFET: FeaturesIldevan José100% (1)

- TPC8103Document8 pagesTPC8103dreyes3773No ratings yet

- FDMC8200SDocument12 pagesFDMC8200Sdreyes3773No ratings yet

- Fds 6875Document5 pagesFds 6875dreyes3773No ratings yet

- SI9945Document4 pagesSI9945dreyes3773No ratings yet

- Dual N-Channel, Notebook Power Supply MOSFET: June 1999Document9 pagesDual N-Channel, Notebook Power Supply MOSFET: June 1999dreyes3773No ratings yet

- AO4900 Dual N-Channel Enhancement Mode Field Effect Transistor With Schottky DiodeDocument5 pagesAO4900 Dual N-Channel Enhancement Mode Field Effect Transistor With Schottky Diodedreyes3773No ratings yet

- AO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect TransistorDocument8 pagesAO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect Transistordreyes3773No ratings yet

- S T U/D3030NLS: N-Channel Logic Level E Nhancement Mode Field E Ffect TransistorDocument9 pagesS T U/D3030NLS: N-Channel Logic Level E Nhancement Mode Field E Ffect Transistordreyes3773No ratings yet

- AO4812 Dual N-Channel Enhancement Mode Field Effect TransistorDocument4 pagesAO4812 Dual N-Channel Enhancement Mode Field Effect Transistordreyes3773No ratings yet

- Si4814DY Dual N-Channel 30-V (D-S) MOSFET With Schottky DiodeDocument8 pagesSi4814DY Dual N-Channel 30-V (D-S) MOSFET With Schottky Diodedreyes3773No ratings yet

- Irf7832Pbf: V R Max QGDocument10 pagesIrf7832Pbf: V R Max QGdreyes3773No ratings yet

- TPC8016-H: High-Efficiency DC DC Converter Applications Notebook PC Applications Portable-Equipment ApplicationsDocument7 pagesTPC8016-H: High-Efficiency DC DC Converter Applications Notebook PC Applications Portable-Equipment Applicationsdreyes3773No ratings yet

- TPC8A03-H: High Efficiency DC-DC Converter Applications Notebook PC Applications Portable Equipment ApplicationsDocument8 pagesTPC8A03-H: High Efficiency DC-DC Converter Applications Notebook PC Applications Portable Equipment Applicationsdreyes3773No ratings yet

- Si4810BDY: Vishay SiliconixDocument5 pagesSi4810BDY: Vishay Siliconixdreyes3773No ratings yet

- Si4404DY N-Channel 30-V (D-S) MOSFET: Vishay SiliconixDocument4 pagesSi4404DY N-Channel 30-V (D-S) MOSFET: Vishay Siliconixdreyes3773No ratings yet

- Rjk03B9Dpa: DatasheetDocument7 pagesRjk03B9Dpa: Datasheetdreyes3773No ratings yet

- Fdms0308Cs: N-Channel Powertrench SyncfetDocument8 pagesFdms0308Cs: N-Channel Powertrench Syncfetdreyes3773No ratings yet

- Semiconductorfet, Called A Misfet) - A Common Special Case of This Type Uses An Oxide Layer As TheDocument10 pagesSemiconductorfet, Called A Misfet) - A Common Special Case of This Type Uses An Oxide Layer As TheShoumil SachanNo ratings yet

- DSE M643 Data SheetDocument7 pagesDSE M643 Data SheetY.EbadiNo ratings yet

- 50 - 100kV - AC Dielectric Test SetDocument4 pages50 - 100kV - AC Dielectric Test SetlrpatraNo ratings yet

- PCR 406Document2 pagesPCR 406grfwrgrsNo ratings yet

- Gea S1004 PDFDocument8 pagesGea S1004 PDFmeirangongNo ratings yet

- 2220 - Miller Effect PDFDocument4 pages2220 - Miller Effect PDFEdmundBlackadderIVNo ratings yet

- Coils For Din Plug ConnectionDocument1 pageCoils For Din Plug ConnectionjcNo ratings yet

- Selection Guide Protection RelaysDocument39 pagesSelection Guide Protection RelaysBalamurugan Arumugam100% (1)

- Notes 1 Basics of RadarDocument18 pagesNotes 1 Basics of RadarPranava K BhatNo ratings yet

- Essay For BluetoothDocument3 pagesEssay For BluetoothVenkatesh SNo ratings yet

- Welding Casting Main 2021Document26 pagesWelding Casting Main 2021mohitNo ratings yet

- Philips TV 7607 Service ManualDocument257 pagesPhilips TV 7607 Service ManualPlayer NumberNo ratings yet

- R-23 Unit-2 ChemistryDocument12 pagesR-23 Unit-2 ChemistrycherukurimanojsarmaNo ratings yet

- Power Electronics: Chapter 4: Switch-Mode Dc-Ac InvertersDocument71 pagesPower Electronics: Chapter 4: Switch-Mode Dc-Ac InvertersAjay KumarNo ratings yet

- Mosfet PDFDocument13 pagesMosfet PDFTad-electronics TadelectronicsNo ratings yet

- Spark V Exp 2Document7 pagesSpark V Exp 2yogeshNo ratings yet

- Diagnostic Code List: Cerrar SISDocument3 pagesDiagnostic Code List: Cerrar SISHamilton MirandaNo ratings yet

- MC-HL MVDocument2 pagesMC-HL MVElectrificationNo ratings yet

- Design and Fabrication ofDocument9 pagesDesign and Fabrication ofKarthi Keyan R KNo ratings yet

- Korg M3 Manual en InglesDocument241 pagesKorg M3 Manual en InglesElio José Torrez VargasNo ratings yet

- Group 4 Mechatronics System: 1. All Actuators Speed Are SlowDocument10 pagesGroup 4 Mechatronics System: 1. All Actuators Speed Are SlownajafaliNo ratings yet

- Portable Test Equipment: PTE 2100 PTE 2300Document114 pagesPortable Test Equipment: PTE 2100 PTE 2300Muhammad AliNo ratings yet

- Hewlett-Packard - AN150-10 - Spectrum Analysis - Field Strenght MeasurementDocument2 pagesHewlett-Packard - AN150-10 - Spectrum Analysis - Field Strenght Measurementgbr123No ratings yet

- Control Lab Report Experiment No. 04Document2 pagesControl Lab Report Experiment No. 04Nahin AminNo ratings yet

- ELTE2.3 DBS3900 LTE TDD Basic Feature DescriptionDocument92 pagesELTE2.3 DBS3900 LTE TDD Basic Feature DescriptioneuniceikaNo ratings yet

- BITMAIN ANTMINER S7 Batch 15 With 4.73th/sDocument6 pagesBITMAIN ANTMINER S7 Batch 15 With 4.73th/scjtrybiecNo ratings yet

- Base Station SubsystemDocument72 pagesBase Station SubsystemDivya GoelNo ratings yet

- CoreIP ClockDocument81 pagesCoreIP ClockPortgasD.AceNo ratings yet

- Lithium Battery UN38.3 Test Report: Prepared ForDocument14 pagesLithium Battery UN38.3 Test Report: Prepared ForBikash Kumar MallickNo ratings yet

- Most Often Needed: Radio DiagramsDocument191 pagesMost Often Needed: Radio DiagramsbrenodesenneNo ratings yet