Professional Documents

Culture Documents

DS1220Y 16k Nonvolatile SRAM: Features Pin Assignment

Uploaded by

Chico SouzaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DS1220Y 16k Nonvolatile SRAM: Features Pin Assignment

Uploaded by

Chico SouzaCopyright:

Available Formats

Not Recommended for New Design

DS1220Y 16k Nonvolatile SRAM

www.maxim-ic.com

FEATURES

10 years minimum data retention in the absence of external power Data is automatically protected during power loss Directly replaces 2k x 8 volatile static RAM or EEPROM Unlimited write cycles Low-power CMOS JEDEC standard 24-pin DIP package Read and write access times as fast as 100 ns Full 10% operating range Optional industrial temperature range of -40C to +85C, designated IND

PIN ASSIGNMENT

A7 A6 A5 A4 A3 A2 A1 A0 DQ0 DQ1 DQ2 GND 1 2 3 4 5 6 7 8 9 10 11 12 24 23 22 21 20 19 18 17 16 15 14 13 VCC A8 A9 WE OE A10 CE DQ7 DQ6 DQ5 DQ4 DQ3

24-Pin ENCAPSULATED PACKAGE 720-mil EXTENDED

PIN DESCRIPTION

A0-A10 DQ0-DQ7 CE WE OE VCC GND - Address Inputs - Data In/Data Out - Chip Enable - Write Enable - Output Enable - Power (+5V) - Ground

DESCRIPTION

The DS1220Y 16k Nonvolatile SRAM is a 16,384-bit, fully static, nonvolatile RAM organized as 2048 words by 8 bits. Each NV SRAM has a self-contained lithium energy source and control circuitry which constantly monitors VCC for an out-of-tolerance condition. When such a condition occurs, the lithium energy source is automatically switched on and write protection is unconditionally enabled to prevent data corruption. The NV SRAM can be used in place of existing 2k x 8 SRAMs directly conforming to the popular bytewide 24-pin DIP standard. The DS1220Y also matches the pinout of the 2716 EPROM or the 2816 EEPROM, allowing direct substitution while enhancing performance. There is no limit on the number of write cycles that can be executed and no additional support circuitry is required for microprocessor interfacing.

1 of 8

081506

DS1220Y

READ MODE

The DS1220Y executes a read cycle whenever WE (Write Enable) is inactive (high) and CE (Chip Enable) and OE (Output Enable) are active (low). The unique address specified by the 11 address inputs (A0-A10) defines which of the 2048 bytes of data is to be accessed. Valid data will be available to the eight data output drivers within tACC (Access Time) after the last address input signal is stable, providing that CE and OE access times are also satisfied. If CE and OE access times are not satisfied, then data access must be measured from the later-occurring signal and the limiting parameter is either tCO for CE or tOE for OE rather than address access.

WRITE MODE

The DS1220Y executes a write cycle whenever the WE and CE signals are active (low) after address inputs are stable. The later-occurring falling edge of CE or WE will determine the start of the write cycle. The write cycle is terminated by the earlier rising edge of CE or WE . All address inputs must be kept valid throughout the write cycle. WE must return to the high state for a minimum recovery time (tWR) before another cycle can be initiated. The OE control signal should be kept inactive (high) during write cycles to avoid bus contention. However, if the output drivers are enabled ( CE and OE active) then WE will disable the outputs in tODW from its falling edge.

DATA RETENTION MODE

The DS1220Y provides full-functional capability for VCC greater than 4.5 volts and write protects at 4.25 nominal. Data is maintained in the absence of VCC without any additional support circuitry. The DS1220Y constantly monitors VCC. Should the supply voltage decay, the NV SRAM automatically write protects itself, all inputs become dont care, and all outputs become high-impedance. As VCC falls below approximately 3.0 volts, a power switching circuit connects the lithium energy source to RAM to retain data. During power-up, when VCC rises above approximately 3.0 volts, the power switching circuit connects external VCC to RAM and disconnects the lithium energy source. Normal RAM operation can resume after VCC exceeds 4.5 volts.

2 of 8

DS1220Y

ABSOLUTE MAXIMUM RATINGS*

Voltage on Any Pin Relative to Ground Operating Temperature Storage Temperature Soldering Temperature Caution: Do Not Reflow -0.3V to +7.0V 0C to 70C; -40C to +85C for IND parts -40C to +70C; -40C to +85C for IND parts +260C for 10 seconds (Wave or Hand Solder Only)

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

RECOMMENDED DC OPERATING CONDITIONS

PARAMETER Power Supply Voltage Input Logic 1 Input Logic 0 PARAMETER Input Leakage Current I/O Leakage Current CE VIH VCC Output Current @ 2.4V Output Current @ 0.4V Standby Current CE =2.2V Standby Current CE =VCC -0.5V Operating Current tCYC= 200ns (Commercial) Operating Current tCYC=200ns (Industrial) Write Protection Voltage SYMBOL VCC VIH VIL SYMBOL IIL IIO MIN 4.5 2.2 0.0 MIN -1.0 -1.0 TYP 5.0 MAX 5.5 VCC +0.8 MAX +1.0 +1.0

(TA : See Note 10)

UNITS V V V UNITS mA mA NOTES

DC ELECTRICAL CHARACTERISTICS

(TA : See Note 10; VCC = 5V 10%)

TYP NOTES

IOH IOL ICCS1 ICCS2 ICCO1 ICCO1 VTP

SYMBOL CIN CI/O

-1.0 2.0 3.0 2.0 7.0 4.0 75 85 4.25

MIN TYP 5 5 MAX 10 12

mA mA mA mA mA mA V

CAPACITANCE

PARAMETER Input Capacitance Input/Output Capacitance

(T A = 25C)

UNITS pF pF NOTES

3 of 8

DS1220Y

AC ELECTRICAL CHARACTERISTICS

PARAMETER Read Cycle Time Access Time SYM tRC tACC DS1220Y-100 MIN MAX 100 100 DS1220Y-120 MIN MAX 120 120

(TA : See Note 10; VCC =5.0V 10%)

DS1220Y-150 MIN MAX 150 150 DS1220Y-200 MIN MAX 200 200 UNITS ns ns NOTE

OE to Output Valid CE to Output Valid OE or CE to Output Active Output High Z from Deslection Output Hold from Address Change Write Cycle Time Write Pulse Width Address Setup Time Write Recovery Time Output High Z from WE Output Active from WE Data Setup Time Data Hold Time

tOE tCO tCOE tOD tOH tWC tWP tAW tWR1 tWR2 tODW tOEW tDS tDH1 tDH2 5 40 0 10 5 100 75 0 0 10 5

50 100 5 35 5 120 90 0 0 10 35 5 50 0 10

60 120 5 35 5 150 100 0 0 10 35 5 60 0 10

70 150 5 35 5 200 150 0 0 10 35 5 80 0 10

100 200

ns ns ns 5 5

35

ns ns ns ns ns ns ns

12 13 5 5 4 12 13

35

ns ns ns ns ns

4 of 8

DS1220Y

READ CYCLE

SEE NOTE 1

WRITE CYCLE 1

SEE NOTES 2, 3, 4, 6, 7, 8 AND 12

WRITE CYCLE 2

SEE NOTES 2, 3, 4, 6, 7, 8 AND 13

5 of 8

DS1220Y

POWER-DOWN/POWER-UP CONDITION

SEE NOTE 11

POWER-DOWN/POWER-UP TIMING

PARAMETER CE at VIH before Power-Down VCC Slew from VTP to 0V VCC Slew from 0V to VTP SYMBOL tPD tF tR tREC SYMBOL tDR MIN 0 100 0 MAX UNITS ms ms ms ms NOTES 11

CE at VIH after Power-Up

PARAMETER Expected Data Retention Time

2

MIN 10 MAX

(TA = 25C) UNITS NOTES years 9

WARNING:

Under no circumstance are negative undershoots, of any amplitude, allowed when device is in battery backup mode.

NOTES:

1. WE is high for a read cycle. 2. OE = VIH or VIL . If OE = VIH during a write cycle, the output buffers remain in a high impedance state. 3. tWP is specified as the logical AND of CE and WE . tWP is measured from the latter of CE or WE going low to the earlier of CE or WE going high. 4. tDS are measured from the earlier of CE or WE going high. 5. These parameters are sampled with a 5 pF load and are not 100% tested. 6. If the CE low transition occurs simultaneously with or later than the WE low transition in write cycle 1, the output buffers remain in a high impedance state during this period. 6 of 8

DS1220Y

7. If the CE high transition occurs prior to or simultaneously with the WE high transition, the output buffers remain in a high impedance state during this period. 8. If WE is low or the WE low transition occurs prior to or simultaneously with the CE low transition, the output buffers remain in a high impedance state during this period. 9. Each DS1220Y is marked with a 4-digit date code AABB. AA designates the year of manufacture. BB designates the week of manufacture. The expected tDR is defined as starting at the date of manufacture. 10. All AC and DC electrical characteristics are valid over the full operating temperature range. For commercial products, this range is 0C to 70C. For industrial products (IND), this range is -40C to +85C. 11. In a power-down condition the voltage on any pin may not exceed the voltage of VCC . 12. tWR1 , tDH1 are measured from WE going high. 13. tWR2 , tDH2 are measured from CE going high. 14. DS1220Y modules are recognized by Underwriters Laboratory (U.L.) under file E99151 (R).

DC TEST CONDITIONS

Outputs open. All voltages are referenced to ground.

AC TEST CONDITIONS

Output Load: 100pF + 1TTL Gate Input Pulse Levels: 0-3.0V Timing Measurement Reference Levels Input:1.5V Output: 1.5V Input Pulse Rise and Fall Times: 5ns

ORDERING INFORMATION

TEMPERATURE RANGE DS1220Y-100 0C to +70C DS1220Y-100+ 0C to +70C DS1220Y-100IND -40C to +85C DS1220Y-100IND+ -40C to +85C DS1220Y-120 0C to +70C DS1220Y-120+ 0C to +70C DS1220Y-150 0C to +70C DS1220Y-150+ 0C to +70C DS1220Y-200 0C to +70C DS1220Y-200+ 0C to +70C DS1220Y-200IND -40C to +85C DS1220Y-200IND+ -40C to +85C + Denotes lead-free/RoHS-compliant product. PART NUMBER SUPPLY TOLERANCE 5V 10% 5V 10% 5V 10% 5V 10% 5V 10% 5V 10% 5V 10% 5V 10% 5V 10% 5V 10% 5V 10% 5V 10% PIN/PACKAGE 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD 24 / 720 EMOD SPEED GRADE 100ns 100ns 100ns 100ns 120ns 120ns 150ns 150ns 200ns 200ns 200ns 200ns

7 of 8

DS1220Y

DS1220Y NONVOLATILE SRAM, 24-PIN 720-MIL EXTENDED MODULE

PKG DIM A IN. MM B IN. MM C IN. MM D IN. MM E IN. MM F IN. MM G IN. MM H IN MM J IN. MM K IN. MM 24-PIN MIN MAX 1.320 1.340 33.53 34.04 0.695 0.720 17.65 18.29 0.390 0.415 9.91 10.54 0.100 0.130 2.54 3.30 0.017 0.030 0.43 0.76 0.120 0.160 3.05 4.06 0.090 0.110 2.29 2.79 0.590 0.630 14.99 16.00 0.008 0.012 0.20 0.30 0.015 0.021 0.38 0.53

8 of 8

You might also like

- DS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentDocument8 pagesDS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentAndré CastroNo ratings yet

- DS1245Document12 pagesDS1245Neha DadhichNo ratings yet

- 000 0 Hy628100bllg 70Document9 pages000 0 Hy628100bllg 70Deepa DevarajNo ratings yet

- Document Title: GM76C256CDocument11 pagesDocument Title: GM76C256CFrenk EndyNo ratings yet

- Hanbit Hmn1288D: Non-Volatile Sram Module 1mbit (128K X 8-Bit), 32Pin-Dip, 5V Part No. Hmn1288DDocument9 pagesHanbit Hmn1288D: Non-Volatile Sram Module 1mbit (128K X 8-Bit), 32Pin-Dip, 5V Part No. Hmn1288DDeepa DevarajNo ratings yet

- Cypress SRAM CY62256Document11 pagesCypress SRAM CY62256MicroemissionNo ratings yet

- Hanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDocument9 pagesHanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDeepa DevarajNo ratings yet

- 2114 Sram DatasheetDocument8 pages2114 Sram DatasheetntrscribeNo ratings yet

- Atmel 8568 SEEPROM AT24C256C Datasheet PDFDocument21 pagesAtmel 8568 SEEPROM AT24C256C Datasheet PDFhanifNo ratings yet

- Datasheet CY62146DV30LDocument11 pagesDatasheet CY62146DV30LedgarlibanioNo ratings yet

- 512K (64K X 8) CMOS EPROM: Features Package TypesDocument8 pages512K (64K X 8) CMOS EPROM: Features Package Types81968No ratings yet

- Ad7524 Ep PDFDocument8 pagesAd7524 Ep PDFjlfepeNo ratings yet

- Data SheetDocument14 pagesData SheetChathur Sajeewan BasuruNo ratings yet

- CAT24C256 256 KB I C CMOS Serial Eeprom: DescriptionDocument18 pagesCAT24C256 256 KB I C CMOS Serial Eeprom: Descriptionjagadees21No ratings yet

- 27C512Document12 pages27C512technicalavrNo ratings yet

- Octal Configurable Low/High Side Driver: DescriptionDocument18 pagesOctal Configurable Low/High Side Driver: DescriptionDan Esenther100% (1)

- 4M (512K X 8) Static Ram: Cy62148V MoblDocument9 pages4M (512K X 8) Static Ram: Cy62148V MoblAurelian ZaharescuNo ratings yet

- 27C020Document11 pages27C020technicalavrNo ratings yet

- 32kx8bit CMOS SRAM: HY62256B SeriesDocument9 pages32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsrieNo ratings yet

- EEPROM 24LC512 - 21754eDocument26 pagesEEPROM 24LC512 - 21754eMarcelo Azevedo BragaNo ratings yet

- CD4029BC Presettable Binary/Decade Up/Down CounterDocument10 pagesCD4029BC Presettable Binary/Decade Up/Down CounterIbrahimEssamNo ratings yet

- CMOS Static RAM 256K (32K X 8-Bit) IDT71256S IDT71256L: Features DescriptionDocument10 pagesCMOS Static RAM 256K (32K X 8-Bit) IDT71256S IDT71256L: Features DescriptionantoninoxxxNo ratings yet

- 24LC512Document26 pages24LC512tecpowerNo ratings yet

- Intersil 82c54 - 5Document22 pagesIntersil 82c54 - 5anjanbsNo ratings yet

- 28 C 16Document10 pages28 C 16Omar Santiago AvalosNo ratings yet

- NewDocument8 pagesNewxuankien181991No ratings yet

- MemoriaDocument7 pagesMemoriaEduardo TaglialavoreNo ratings yet

- 2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial InterfaceDocument20 pages2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial Interfacejoseleomi_limaNo ratings yet

- Nte 4053Document4 pagesNte 4053Codinasound CaNo ratings yet

- Memoria Ram 6264Document14 pagesMemoria Ram 6264DOMINGOS ALADIRNo ratings yet

- AA AA AA AA A A A A A A A: 12-Bit 100 KSPS A/D Converter AD1674Document13 pagesAA AA AA AA A A A A A A A: 12-Bit 100 KSPS A/D Converter AD1674Iancu CiocioiNo ratings yet

- KM 62256Document9 pagesKM 62256roozbehxoxNo ratings yet

- EEPROMDocument16 pagesEEPROMTutankhalmoxeNo ratings yet

- CD4028BC BCD-to-Decimal Decoder: General Description FeaturesDocument6 pagesCD4028BC BCD-to-Decimal Decoder: General Description Featuresmalirezazadeh5549No ratings yet

- IS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplyDocument17 pagesIS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplywarekinNo ratings yet

- Ad 7524Document8 pagesAd 7524Giovanny ContrerasNo ratings yet

- Cmos Sram K6T1008C2E Family: Document TitleDocument11 pagesCmos Sram K6T1008C2E Family: Document TitleOmar LeonNo ratings yet

- ISL3293E, ISL3294E, ISL3295E, ISL3296E, ISL3297E, ISL3298E: 16.5kV ESD Protected, +125°C, 3.0V ToDocument17 pagesISL3293E, ISL3294E, ISL3295E, ISL3296E, ISL3297E, ISL3298E: 16.5kV ESD Protected, +125°C, 3.0V Tobndfruit1No ratings yet

- CD4094BCDocument7 pagesCD4094BCEdgar MendezNo ratings yet

- 64K (8K X 8) Cmos Eprom: Features Package TypesDocument13 pages64K (8K X 8) Cmos Eprom: Features Package TypesIngrid XytrasNo ratings yet

- HY6264A - (I) Series: 8kx8bit CMOS SRAMDocument9 pagesHY6264A - (I) Series: 8kx8bit CMOS SRAMLexuanhoa ProNo ratings yet

- Device Datasheet For CD4021Document7 pagesDevice Datasheet For CD4021bdfbNo ratings yet

- 8k X 8 RamDocument13 pages8k X 8 RamntrscribeNo ratings yet

- DS1307 Datasheet FullDocument15 pagesDS1307 Datasheet FulllamanzanadeadanNo ratings yet

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADocument6 pagesOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100No ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesAn TrìnhNo ratings yet

- CD4015BC Dual 4-Bit Static Shift Register: General Description FeaturesDocument6 pagesCD4015BC Dual 4-Bit Static Shift Register: General Description FeaturesMerényi OszkárNo ratings yet

- M48T02 150pciDocument15 pagesM48T02 150pciImran YaminNo ratings yet

- 93xx86 Varias VersionesDocument28 pages93xx86 Varias VersionesPosada Burgueño CarlosNo ratings yet

- 6116ASP20Document9 pages6116ASP20BeNz BarrigaNo ratings yet

- Adc 0804 PDFDocument18 pagesAdc 0804 PDFCinthya VillenaNo ratings yet

- 8K X 8 Bit Fast Static RAM MCM6264C: MotorolaDocument8 pages8K X 8 Bit Fast Static RAM MCM6264C: Motorolajackiie16No ratings yet

- DAC0830/DAC0832 8-Bit P Compatible, Double-Buffered D To A ConvertersDocument24 pagesDAC0830/DAC0832 8-Bit P Compatible, Double-Buffered D To A Convertersbhuvi2312No ratings yet

- 74AC74Document9 pages74AC74ciernesNo ratings yet

- 27c512 PLCC 32Document13 pages27c512 PLCC 32redtop_68No ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Ani C Bus Analyser To Let You Satisfy Your Curiosity: The Secrets of I CDocument7 pagesAni C Bus Analyser To Let You Satisfy Your Curiosity: The Secrets of I CChico SouzaNo ratings yet

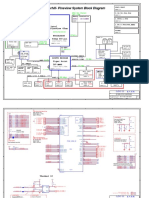

- CLEVO Tigerhill-Pineview System Block DiagramDocument26 pagesCLEVO Tigerhill-Pineview System Block DiagramChico SouzaNo ratings yet

- 64Kb Bytewide F-RAM Memory: FeaturesDocument12 pages64Kb Bytewide F-RAM Memory: FeaturesChico SouzaNo ratings yet

- Compa Q ArmadaDocument13 pagesCompa Q ArmadaChico SouzaNo ratings yet

- Weintek HMI With Built-In Modbus TCP ServerDocument18 pagesWeintek HMI With Built-In Modbus TCP ServerÁnh VũNo ratings yet

- Abdullapur (V), Abdullapurmet (M), Rangareddy (Dist) - 501505Document3 pagesAbdullapur (V), Abdullapurmet (M), Rangareddy (Dist) - 501505karthik PothurajulaNo ratings yet

- BOQ AEON Cisco-FortinetDocument16 pagesBOQ AEON Cisco-FortinetAntonNo ratings yet

- LED LCD Monitor (LED Monitor ) : Owner'S ManualDocument21 pagesLED LCD Monitor (LED Monitor ) : Owner'S ManualJuan GutiérrezNo ratings yet

- ZOTAC GeForce GTX 960 Sales Kit 1.3Document35 pagesZOTAC GeForce GTX 960 Sales Kit 1.3Herkul BoyNo ratings yet

- NX Ugdocs 10.0.2.READMEDocument2 pagesNX Ugdocs 10.0.2.READMEwalNo ratings yet

- Best Distributed-WA-CA AutoSys Workload Automation r113 ArchitectureDocument39 pagesBest Distributed-WA-CA AutoSys Workload Automation r113 Architectureharish selvamNo ratings yet

- Y10 04 P22 SlidesDocument12 pagesY10 04 P22 SlideselsieNo ratings yet

- Simulado Az700Document260 pagesSimulado Az700rotiliojpaNo ratings yet

- CBSE Class 12 Informatics Practices Question Paper Solved 2019 PDFDocument28 pagesCBSE Class 12 Informatics Practices Question Paper Solved 2019 PDFKartik Malik100% (1)

- Oracle Database 12c R2 Backup and Recovery Workshop Ed 3Document5 pagesOracle Database 12c R2 Backup and Recovery Workshop Ed 3vineetNo ratings yet

- Nuvoton PPT M2351 Security ArchitectureDocument53 pagesNuvoton PPT M2351 Security ArchitecturedrawnpoetryNo ratings yet

- MCA Syllabus 2011Document39 pagesMCA Syllabus 2011Mujthaba HassanNo ratings yet

- SSS ModBus Lib Description EDocument9 pagesSSS ModBus Lib Description Edavid reyesNo ratings yet

- Compal EH5LP - AP LA-H801P Rev 1.A (DIAGRAMAS - COM.BR)Document48 pagesCompal EH5LP - AP LA-H801P Rev 1.A (DIAGRAMAS - COM.BR)fcob13No ratings yet

- Libretto 50 CTDocument2 pagesLibretto 50 CTzack9mm2003No ratings yet

- Binary ArithmeticDocument54 pagesBinary ArithmeticRey Lacdan GlendroNo ratings yet

- Upgrading A MicroprocessrDocument10 pagesUpgrading A MicroprocessrDrift GeeNo ratings yet

- Debug External ProDebug External Processors With USBDM and Freedom Board - MCU On Eclipsecessors With USBDM and Freedom Board - MCU On EclipseDocument22 pagesDebug External ProDebug External Processors With USBDM and Freedom Board - MCU On Eclipsecessors With USBDM and Freedom Board - MCU On Eclipsealguien1972100% (1)

- 03 LCD Slide Handout 1Document3 pages03 LCD Slide Handout 1Jerico RickyNo ratings yet

- Secondary School Grade 7: Information Technology Curriculum GuideDocument27 pagesSecondary School Grade 7: Information Technology Curriculum GuideJanice Tarrosa-AvilaNo ratings yet

- ProactiveNet Release NotesDocument76 pagesProactiveNet Release NotesCharl11eNo ratings yet

- Lect 6 - OsDocument13 pagesLect 6 - OsUjala AleemNo ratings yet

- TravelMate 8372 Series Inventec BAP30 - BXP30Document41 pagesTravelMate 8372 Series Inventec BAP30 - BXP30Micropc Technology SolutionNo ratings yet

- BeeBrain V.1.2 ManualDocument19 pagesBeeBrain V.1.2 ManuallectorNo ratings yet

- Setting Up A Mikrotik Hotspot With UserManager (Step-By-Step) - Binary HeartbeatDocument16 pagesSetting Up A Mikrotik Hotspot With UserManager (Step-By-Step) - Binary HeartbeatdownloadsrkNo ratings yet

- CS8501 - Theory of Computation (Ripped From Amazon Kindle Ebooks by Sai Seena)Document520 pagesCS8501 - Theory of Computation (Ripped From Amazon Kindle Ebooks by Sai Seena)PRADEEBA V100% (1)

- geoSTATE 1.1 Ocean For Petrel - Installation Guide PDFDocument7 pagesgeoSTATE 1.1 Ocean For Petrel - Installation Guide PDFPrashantDhoteNo ratings yet

- DSC Signer Service (Ver.4.1) User GuidelinesDocument53 pagesDSC Signer Service (Ver.4.1) User GuidelinesNitish KumarNo ratings yet

- Microcontroller (1) Lab Manual: University of Science &technolegy Facualty of Engneering BiomedicalDocument23 pagesMicrocontroller (1) Lab Manual: University of Science &technolegy Facualty of Engneering BiomedicalIyyaasuu YaadataaNo ratings yet