Professional Documents

Culture Documents

ECE 546 - VLSI Systems Design Lecture 16: SRAM: Fall 2012 W. Rhett Davis NC State University

Uploaded by

Sasi Kiran SOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ECE 546 - VLSI Systems Design Lecture 16: SRAM: Fall 2012 W. Rhett Davis NC State University

Uploaded by

Sasi Kiran SCopyright:

Available Formats

Slide 1 W.

Rhett Davis NC State University ECE 546 Fall 2012

ECE 546 - VLSI Systems Design

Lecture 16: SRAM

Fall 2012

W. Rhett Davis

NC State University

with significant material from Rabaey, Chandrakasan, and Nikoli

Slide 2 W. Rhett Davis NC State University ECE 546 Fall 2012

Announcements

Re-grade Requests for Midterm due in 1 week

HW#7 Due Tuesday

Project Introduction Tuesday

Continue forming project groups

Slide 3 W. Rhett Davis NC State University ECE 546 Fall 2012

Todays Lecture

SRAM

Multi-Port SRAM

CAM

Slide 4 W. Rhett Davis NC State University ECE 546 Fall 2012

6-transistor CMOS SRAM Cell

WL

BL

V

DD

M

5

M

6

M

4

M

1

M

2

M

3

BL

Q

Q

Slide 5 W. Rhett Davis NC State University ECE 546 Fall 2012

CMOS SRAM Analysis (Read)

Assume bit-lines precharged high, Q=1, Q=0

What could go wrong?

WL

BL

V

DD

M

5

M

6

M

4

M

1

V

DD

V

DD

V

DD

BL

Q

=

1

Q

=

0

C

bit

C

bit

Slide 6 W. Rhett Davis NC State University ECE 546 Fall 2012

Read Upset Problem

Modified equations

(12.2) and (12.3)

(by Harun Demircioglu)

What are the operating

regions assumed by

these equations?

Is this valid for our

technology?

WL

BL

V

DD

M

5

M

6

M

4

M

1

V

DD V

DD

V

DD

BL

Q

=

1

Q

=

0

C

bit

C

bit

5 5

1 1

L W

L W

CR =

( ) ( ) ( )

|

|

.

|

\

| A

A A + =

|

|

.

|

\

|

A + A

2 2

2

0 1 ,

2

0 5 ,

V

V V B V V k

V

V V V B V V V k

n n T DD M n

DSATn

DSATn DD n n T DD M n

( ) ( ) ( ) ( )

( )CR B

V V CR CR V V V CR V B

V

n

n T DD DSATn n T DD DSATn n

2 1

2 1 1

2

0

2 2

0

+ + + +

~ A

Slide 7 W. Rhett Davis NC State University ECE 546 Fall 2012

CMOS SRAM Analysis (Read)

For which side of this curve does the SRAM work properly?

0

0

0.2

0.4

0.6

0.8

1

1.2

0.5 1 1.2 1.5 2

Cell Ratio (CR)

2.5 3

V

o

l

t

a

g

e

R

i

s

e

(

V

)

Slide 8 W. Rhett Davis NC State University ECE 546 Fall 2012

Read Static Noise Margin (SNM)

A more robust definition is the maximum noise voltage

needed to flip the value during a read

For simplicity on HW and Exams, we wont use this definition

At low supply voltages, Read SNM is too often negative,

due to Vt variation between transistors

As a result, supply voltages have not scaled below 1V in

advanced technologies

Source:

Calhoun &

Chandrakasan,

JSSC 2007

V from slide 6

Slide 9 W. Rhett Davis NC State University ECE 546 Fall 2012

CMOS SRAM Analysis (Write)

Assume cell contains 1, try to write 0

What needs to happen for a successful write?

BL

=

1 BL

=

0

Q

=

0

Q

=

1

M

1

M

4

M

5

M

6

V

DD

V

DD

WL

Slide 10 W. Rhett Davis NC State University ECE 546 Fall 2012

Conditions for Successful Write

Modified equations

(12.5) and (12.6)

(by Harun Demircioglu)

What are the operating

regions assumed by

these equations?

Is this valid for our

technology?

BL

=

1 BL

=

0

Q

=

0

Q

=

1

M

1

M

4

M

5

M

6

V

DD

V

DD

WL

6 6

4 4

L W

L W

PR =

( ) ( ) ( )

|

|

.

|

\

|

=

|

|

.

|

\

|

+

2 2

2

0 4 ,

2

0 6 ,

DSATp

DSATp DD Q p p T DD M p

Q

Q Q n n T DD M n

V

V V V B V V k

V

V V B V V k

( ) ( ) ( )

( )

n

DSATp

DSATp p T DD p

n

p

DSATp p n T DD DSATp p n T DD

Q

B

V

V V V B PR V B V V V B V V

V

2 1

2

1 2

2

0

2

0 0

|

|

.

|

\

|

+ +

=

Slide 11 W. Rhett Davis NC State University ECE 546 Fall 2012

CMOS SRAM Analysis (Write)

For which side of this curve does the SRAM work properly?

Slide 12 W. Rhett Davis NC State University ECE 546 Fall 2012

6T-SRAM Layout

V

DD

GND

Q

Q

WL

BL BL

M1 M3

M4 M2

M5 M6

Slide 13 W. Rhett Davis NC State University ECE 546 Fall 2012

Another Bit-Cell Layout

This bit-cell was created

by Xi Chen, Ting Zhu,

and Harun Demircioglu

for the Fall 2007 project

Best performance in

class

See their report on last

years web-page

group 35

see Project Results

Will this bit-cell still work,

now that we have

lithographic simulations?

Slide 14 W. Rhett Davis NC State University ECE 546 Fall 2012

Summary

In an SRAM

Size NMOS larger than pass-gate to avoid read-upset

Size PMOS small for successful write

Slide 15 W. Rhett Davis NC State University ECE 546 Fall 2012

Todays Lecture

SRAM

Multi-Port SRAM

CAM

Slide 16 W. Rhett Davis NC State University ECE 546 Fall 2012

Extending the SRAM Cell

This bit-cell supports

a read or write to one

location in the array

How would we

change it if we

wanted to read or

write to two

locations?

WL

BL BL

Slide 17 W. Rhett Davis NC State University ECE 546 Fall 2012

2-Port SRAM Cell

This bit-cell supports

reads and/or writes to

two locations in the

array

How could we

optimize the cell if the

second port were

read-only?

Slide 18 W. Rhett Davis NC State University ECE 546 Fall 2012

Read/Write + Read SRAM Cell (1)

What is the

advantage

of this cell?

What is the

disadvantage

of this cell?

R/WWL

R/WBL RBL

RWL

R/WBL

Slide 19 W. Rhett Davis NC State University ECE 546 Fall 2012

Read/Write + Read SRAM Cell (2)

What is the

advantage

of this cell?

What is the

disadvantage

of this cell?

R/WWL

R/WBL RBL

RWL

R/WBL

Slide 20 W. Rhett Davis NC State University ECE 546 Fall 2012

Another Approach to Multi-Ports

Use two separate single-port arrays and re-

direct logic to send requests to each

When is this advantageous?

R

o

w

D

e

c

o

d

e

r

Bit line

2

L 2 K

Word line

A

K

A

K1 1

A

L2 1

A

0

M.2

K

A

K2 1

Sense amplifiers / Drivers

Column decoder

Input-Output

(M bits)

Storage cell

R

o

w

D

e

c

o

d

e

r

Bit line

2

L 2 K

Word line

A

K

A

K1 1

A

L2 1

A

0

M.2

K

A

K2 1

Sense amplifiers / Drivers

Column decoder

Input-Output

(M bits)

Storage cell

Re-direct logic

Slide 21 W. Rhett Davis NC State University ECE 546 Fall 2012

Todays Lecture

SRAM

Multi-Port SRAM

CAM

Slide 22 W. Rhett Davis NC State University ECE 546 Fall 2012

Content-Addressable Memory (CAM)

Primary function is to look up the address of

stored data, rather than the data itself

Most often used in Internet Protocol Routers to

classify & forward packets

Similar to SRAM, but has 4 types of wires in the

array

Bit-line (BL) and Word-line (WL), used to write data

into the array

Search-Line (SL), used to drive the searched value

Match-line (ML), used to indicate a match

Ternary CAM (TCAM) also stores "don't care"

Slide 23 W. Rhett Davis NC State University ECE 546 Fall 2012

High-Level CAM Architecture

Slide 24 W. Rhett Davis NC State University ECE 546 Fall 2012

CAM Bit-Cells

Source: Pagiamtzis & Sheikholeslami, JSSC '06

NOTE: Bit-lines and access transistors removed

You might also like

- Pss Sincal SlidesDocument116 pagesPss Sincal SlidesfareshindelehNo ratings yet

- Ece546fall12 08Document31 pagesEce546fall12 08hanumantha12No ratings yet

- ECE 546 - VLSI Systems Design Lecture 10: Ratioed Logic, Pass Transistor LogicDocument32 pagesECE 546 - VLSI Systems Design Lecture 10: Ratioed Logic, Pass Transistor LogicveereshnicolyteNo ratings yet

- Lvds Receiver ThesisDocument8 pagesLvds Receiver Thesisamandabradybillings100% (1)

- Waleed K. Al-Assadi Anura P. Jayasumana Yashwant K. Malaiya Technical Report CS-96-102Document10 pagesWaleed K. Al-Assadi Anura P. Jayasumana Yashwant K. Malaiya Technical Report CS-96-102RajasekharVenkataNo ratings yet

- Design Plan NNG Feed Through CreationDocument21 pagesDesign Plan NNG Feed Through CreationNguyen HungNo ratings yet

- Release Notes Digimat 6.0.1: P. 2 P. 3 p.4 P. 6 P. 7 P. 9Document13 pagesRelease Notes Digimat 6.0.1: P. 2 P. 3 p.4 P. 6 P. 7 P. 9Israr UllahNo ratings yet

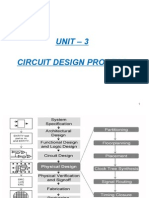

- Unit - 3 Circuit Design ProcessDocument30 pagesUnit - 3 Circuit Design ProcessNagarjun RajputNo ratings yet

- DVR Based ThesisDocument5 pagesDVR Based Thesistinajordanhuntsville100% (1)

- Survey On LCDDocument21 pagesSurvey On LCDSharath AcNo ratings yet

- Fundamentals of Quantitative Design and Analysis: A Quantitative Approach, Fifth EditionDocument24 pagesFundamentals of Quantitative Design and Analysis: A Quantitative Approach, Fifth Editionuma_saiNo ratings yet

- Chap 12Document120 pagesChap 12Phuc LxNo ratings yet

- 1 s2.0 S000437021930195X MainDocument26 pages1 s2.0 S000437021930195X MainSebastian GaleanoNo ratings yet

- EE Solutions EliotDocument39 pagesEE Solutions EliotGigi LuNo ratings yet

- EE241 Spring 2008 EE241 - Spring 2008: AnnouncementsDocument19 pagesEE241 Spring 2008 EE241 - Spring 2008: AnnouncementsitsmyturnNo ratings yet

- 8088/8086 MICROPROCESSOR Programming - Integer Instructions and ComputationsDocument11 pages8088/8086 MICROPROCESSOR Programming - Integer Instructions and Computationssai420No ratings yet

- Term Paper On VlsiDocument5 pagesTerm Paper On Vlsiaflsvagfb100% (1)

- OpenDSS Level 2 TrainingDocument79 pagesOpenDSS Level 2 TrainingMish MalkNo ratings yet

- FR-AM-4 Fundamentals of Signal Integrity G Gy: WorkshopDocument47 pagesFR-AM-4 Fundamentals of Signal Integrity G Gy: WorkshopSazzad HossainNo ratings yet

- Electronicdesign 10390 Jesd204bsimplifiedDocument5 pagesElectronicdesign 10390 Jesd204bsimplifiedSB GAYENNo ratings yet

- Chapter 1 (Fundamentals of Quantitative Design and Analysis)Document53 pagesChapter 1 (Fundamentals of Quantitative Design and Analysis)amaliah_aisyahNo ratings yet

- You Will Not Be Allowed To Call Any Tivaware/Stellarisware Functions. You Can Use The Standard I/O Port Definitions AsDocument4 pagesYou Will Not Be Allowed To Call Any Tivaware/Stellarisware Functions. You Can Use The Standard I/O Port Definitions AsSwaiftNo ratings yet

- Low Power Vlsi Design ThesisDocument8 pagesLow Power Vlsi Design Thesisafbtabxds100% (1)

- A 10-Transistor 65 NM SRAM Cell Tolerant To Single-Event UpsetsDocument9 pagesA 10-Transistor 65 NM SRAM Cell Tolerant To Single-Event UpsetsADITYA SHARMANo ratings yet

- Advanced Spanning Tree: What If ?Document14 pagesAdvanced Spanning Tree: What If ?TrịnhVạnPhướcNo ratings yet

- Sen Advances in Stochastic Mixeda Integer ProgrammingDocument58 pagesSen Advances in Stochastic Mixeda Integer Programmingmihai37No ratings yet

- Comparative Analysis of Efficient Designs of D Latch Using 32nm CMOS TechnologyDocument4 pagesComparative Analysis of Efficient Designs of D Latch Using 32nm CMOS TechnologyEditor IJTSRDNo ratings yet

- Circuits Design For Low Power: Advance Digital Integrated Circuit DesignDocument53 pagesCircuits Design For Low Power: Advance Digital Integrated Circuit Designជើងកាង ភូមិNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument55 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- Thesis Report On Low Power VlsiDocument7 pagesThesis Report On Low Power Vlsiashleylovatoalbuquerque100% (2)

- MSP430G2553 Device Erratasheet: ErrataDocument14 pagesMSP430G2553 Device Erratasheet: Erratacaled maestre oliverosNo ratings yet

- Architectural and Integration Options For 3D NAND Flash MemoriesDocument19 pagesArchitectural and Integration Options For 3D NAND Flash MemoriesHeekwan SonNo ratings yet

- ECEN 1400 Lecture 11 Seven Segment DisplayDocument10 pagesECEN 1400 Lecture 11 Seven Segment DisplayRounit RaiNo ratings yet

- IISc eDRAM Ravi 2014 PDFDocument75 pagesIISc eDRAM Ravi 2014 PDFVenkateswararao MusalaNo ratings yet

- x.25 PrezentareDocument22 pagesx.25 PrezentareBotnaru AurelNo ratings yet

- Basic TransmissionDocument116 pagesBasic TransmissionshabbinNo ratings yet

- Level 2Document120 pagesLevel 2Mariam MugheesNo ratings yet

- TimingAnalysis Presentation v1 1Document70 pagesTimingAnalysis Presentation v1 1priyanka HundekarNo ratings yet

- Modified Gate Diffusion Input Technique: A New Technique For Enhancing Performance in Full Adder CircuitsDocument8 pagesModified Gate Diffusion Input Technique: A New Technique For Enhancing Performance in Full Adder CircuitsManjunath RNo ratings yet

- Lecture 15 - P-N Junction (Cont.) March 9, 2007Document17 pagesLecture 15 - P-N Junction (Cont.) March 9, 2007Kenneth Palma CarmonaNo ratings yet

- Webinar SigrityDocument54 pagesWebinar Sigrityjagadees21No ratings yet

- VLSI Architecture Design: IEP On Technology CAD (12-17 May 2008)Document52 pagesVLSI Architecture Design: IEP On Technology CAD (12-17 May 2008)Mohammed ElNeanaeiNo ratings yet

- SVC Pre and Post Firmware Upgrade Checklist - V6Document14 pagesSVC Pre and Post Firmware Upgrade Checklist - V6kuldeep_singh_144No ratings yet

- Testing and Use of Hec-Ras 2Document18 pagesTesting and Use of Hec-Ras 2Suyudi Akbari HabibiNo ratings yet

- Mit Ms ThesisDocument4 pagesMit Ms Thesish0nuvad1sif2100% (2)

- VLSI Design: Chapter 5-1 1Document91 pagesVLSI Design: Chapter 5-1 1Vaibhav SinghNo ratings yet

- LOW Power ReportDocument16 pagesLOW Power ReportAMIT VERMANo ratings yet

- F11 Lec 12 Misc TopicsDocument19 pagesF11 Lec 12 Misc Topicsning2012No ratings yet

- Chapters 1-2. Book Intro. - Microelectronic Devices An Intuitive Approach (Analog IC Design An Intuitive Approach)Document29 pagesChapters 1-2. Book Intro. - Microelectronic Devices An Intuitive Approach (Analog IC Design An Intuitive Approach)Minh Hai RungNo ratings yet

- 03 Networks 2 PrintDocument45 pages03 Networks 2 PrinteviroyerNo ratings yet

- LCD Notes 8-Bit PDFDocument6 pagesLCD Notes 8-Bit PDFjohn doeNo ratings yet

- LCD Module User Manual Explains LMB162AFC DisplayDocument11 pagesLCD Module User Manual Explains LMB162AFC DisplayBima Richardo SihombingNo ratings yet

- Low Power VLSI Chip Design: Circuit Design TechniquesDocument13 pagesLow Power VLSI Chip Design: Circuit Design TechniquesNaveen SilveriNo ratings yet

- Redundancy, RepairDocument8 pagesRedundancy, RepairSabarish IttamveetilNo ratings yet

- Fast MATLAB Assembly of FEM Matrices in 2D and 3D: Edge ElementsDocument13 pagesFast MATLAB Assembly of FEM Matrices in 2D and 3D: Edge ElementsdibekayaNo ratings yet

- 320-2018-2 O1 v1 PDFDocument18 pages320-2018-2 O1 v1 PDFJohn SmithNo ratings yet

- Robert H. Dodds, Jr. (And Many Others!) : August 2013Document24 pagesRobert H. Dodds, Jr. (And Many Others!) : August 2013afiguerasabmNo ratings yet

- Work-In-Progress: Devos: A Learning-Based Delay Model of Voltage-Scaled CircuitsDocument2 pagesWork-In-Progress: Devos: A Learning-Based Delay Model of Voltage-Scaled CircuitsNguyen Van ToanNo ratings yet

- Design for High Performance, Low Power, and Reliable 3D Integrated CircuitsFrom EverandDesign for High Performance, Low Power, and Reliable 3D Integrated CircuitsNo ratings yet

- Ijacee Fpv3i4p1 (1) Very GoodDocument9 pagesIjacee Fpv3i4p1 (1) Very GoodSasi Kiran SNo ratings yet

- Synthesis of Reversible Circuits Based On Products of Exclusive or SumsDocument6 pagesSynthesis of Reversible Circuits Based On Products of Exclusive or SumsSasi Kiran SNo ratings yet

- Radar NotesDocument97 pagesRadar NotesUjwalKatakamNo ratings yet

- Ditgital Communication and ModulationDocument35 pagesDitgital Communication and ModulationSasi Kiran SNo ratings yet

- Electronics Lab 15Document13 pagesElectronics Lab 15ahkiaenaaaaNo ratings yet

- Thebestof FreeDocument75 pagesThebestof Freeever_siaNo ratings yet

- 6 MicrowaveDocument144 pages6 MicrowaveSahil SheikhNo ratings yet

- 6Document4 pages6Sasi Kiran SNo ratings yet

- Ijaim-70 Final NDocument5 pagesIjaim-70 Final NSasi Kiran SNo ratings yet

- 132Document5 pages132Sasi Kiran SNo ratings yet

- ContentsDocument6 pagesContentsSasi Kiran SNo ratings yet

- BC 107 Data SheetDocument8 pagesBC 107 Data SheetKeerthiPratheek ReddyNo ratings yet

- Solaire-Offgrd Pricelist 1 To 10Kwp - 2Document2 pagesSolaire-Offgrd Pricelist 1 To 10Kwp - 2Sasi Kiran SNo ratings yet

- 2 AbstractDocument1 page2 AbstractSasi Kiran SNo ratings yet

- Read/Write Stability Improvement of 8T Sram Cell Using Schmitt TriggerDocument6 pagesRead/Write Stability Improvement of 8T Sram Cell Using Schmitt TriggerSasi Kiran SNo ratings yet

- Reduction of Leakage Power in 8T Sram Cell Using Virtual GroundDocument5 pagesReduction of Leakage Power in 8T Sram Cell Using Virtual GroundSasi Kiran SNo ratings yet

- Amplifier Design Using BJTs ADocument8 pagesAmplifier Design Using BJTs Ajon_21292No ratings yet

- Analysis and Simulation of Sub-Threshold Leakage Current in P3 SRAM Cell at DSM Technology For Multimedia ApplicationsDocument3 pagesAnalysis and Simulation of Sub-Threshold Leakage Current in P3 SRAM Cell at DSM Technology For Multimedia ApplicationsIDESNo ratings yet

- 132Document5 pages132Sasi Kiran SNo ratings yet

- Performance Comparison For Different Configurations of SRAM CellsDocument4 pagesPerformance Comparison For Different Configurations of SRAM CellsSasi Kiran SNo ratings yet

- GATE 2014 Answer Keys For EC Electronics and Communication EngineeringDocument1 pageGATE 2014 Answer Keys For EC Electronics and Communication EngineeringMirishkar S GaneshNo ratings yet

- Ec: Electronics and Communication Engineering: Duration: Three HoursDocument24 pagesEc: Electronics and Communication Engineering: Duration: Three HoursKumar DeepakNo ratings yet

- Analysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorDocument10 pagesAnalysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorSrinivasAnchalaNo ratings yet

- A Survey On Leakage Power Reduction Techniques by Using Power Gating MethodologyDocument6 pagesA Survey On Leakage Power Reduction Techniques by Using Power Gating MethodologySasi Kiran SNo ratings yet

- Chapter - 2 - DC Biasing - BJTsDocument36 pagesChapter - 2 - DC Biasing - BJTsRashmi Gowda RNo ratings yet

- 5Document8 pages5Sasi Kiran SNo ratings yet

- Thebestof FreeDocument75 pagesThebestof Freeever_siaNo ratings yet

- Dou ComDocument5 pagesDou ComSasi Kiran SNo ratings yet

- Amplifier Design Using BJTs ADocument8 pagesAmplifier Design Using BJTs Ajon_21292No ratings yet

- 8515 CompleteDocument101 pages8515 Completefiddu4bvNo ratings yet

- Schematic Diagram Apartment Via: To CombinerDocument1 pageSchematic Diagram Apartment Via: To CombinerSyamsirAlamNo ratings yet

- EEE2211 Lab ManualDocument30 pagesEEE2211 Lab ManualMuhammed AslamNo ratings yet

- Base PaperDocument6 pagesBase PaperSiva KrishnaNo ratings yet

- Designing a Digital Clock CircuitDocument20 pagesDesigning a Digital Clock CircuitMenzeli Mtunzi40% (5)

- Computer OrganizationDocument4 pagesComputer OrganizationshubhamNo ratings yet

- 8086 Architecture OverviewDocument18 pages8086 Architecture OverviewLHKNo ratings yet

- VLSI Course Syllabus and PlanDocument2 pagesVLSI Course Syllabus and Plansteve johnsNo ratings yet

- Lab Report 1 Digital SystemDocument8 pagesLab Report 1 Digital Systemmuhammad adibuddinNo ratings yet

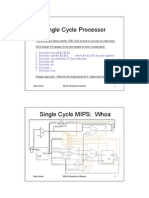

- EE361 SingleMIPSDocument19 pagesEE361 SingleMIPSThùyVũNo ratings yet

- LM 3914Document8 pagesLM 3914abbas ahmedNo ratings yet

- Microchip PolarFire FPGA and PolarFire SoC FPGA User IO User Guide VCDocument106 pagesMicrochip PolarFire FPGA and PolarFire SoC FPGA User IO User Guide VCNguyễn Duy Hà SơnNo ratings yet

- Herbert Electronics Manufactures An Integrated Transistor Circuit Board For RepeatDocument1 pageHerbert Electronics Manufactures An Integrated Transistor Circuit Board For RepeatAmit PandeyNo ratings yet

- Static Sequential XIDocument30 pagesStatic Sequential XISHOBHIT SHARMANo ratings yet

- Automatic Control System For Electric Water MotorDocument34 pagesAutomatic Control System For Electric Water MotorLipika JainNo ratings yet

- SoC or System On Chip Seminar ReportDocument25 pagesSoC or System On Chip Seminar ReportManojkumar S BNo ratings yet

- Adobe Scan Sep 20, 2020Document25 pagesAdobe Scan Sep 20, 2020SaibabuNo ratings yet

- VLSI Design Quick GuideDocument68 pagesVLSI Design Quick GuideMayur AgarwalNo ratings yet

- Yamaha - RX v457 RX v557 - HTR 5880 - DSP Ax457 - DSP Ax557 PDFDocument14 pagesYamaha - RX v457 RX v557 - HTR 5880 - DSP Ax457 - DSP Ax557 PDFHirenNo ratings yet

- CMM P6Document328 pagesCMM P6Douglas de OliveiraNo ratings yet

- Computer Skills: Cihan University-DuhokDocument5 pagesComputer Skills: Cihan University-DuhokaafrasyawNo ratings yet

- 18vlpe07 Design of Semiconductor MemoriesDocument2 pages18vlpe07 Design of Semiconductor Memorieskruthikah apNo ratings yet

- Mod1 (2) - EC464 Low Power VLSI Design-Ktustudents - inDocument40 pagesMod1 (2) - EC464 Low Power VLSI Design-Ktustudents - insurya sundarNo ratings yet

- Orcad Pspice 16Document86 pagesOrcad Pspice 16Hailin ArumigaNo ratings yet

- PIC18F Microcontroller ArchitectureDocument29 pagesPIC18F Microcontroller ArchitectureMohan NatrajanNo ratings yet

- QuestionDocument80 pagesQuestionRodalie Vale CruzNo ratings yet

- 8086 I/O Interfacing & Programming - Part I: Vtu - Edusat ProgrammeDocument19 pages8086 I/O Interfacing & Programming - Part I: Vtu - Edusat ProgrammeChethanNo ratings yet

- TCSM Synchronization and Diagnostic LogsDocument4 pagesTCSM Synchronization and Diagnostic LogsMuhammad AyatullahNo ratings yet

- Datapath Control Unit DesignDocument35 pagesDatapath Control Unit DesignOliver Barrina JaguinesNo ratings yet

- Dynamic CircuitDocument19 pagesDynamic Circuitk.jp914733No ratings yet