Professional Documents

Culture Documents

ASIC June2010

Uploaded by

rajasekarkprOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ASIC June2010

Uploaded by

rajasekarkprCopyright:

Available Formats

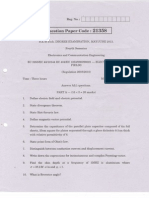

Reg. No.

Question Paper Code: J7797

M.E. DEGREE EXAMINATION, JUNE 2010 Elective VLSI Design VL9261 ASIC DESIGN (Common to M.E. Applied Electronics) (Regulation 2009) Time : Three hours Answer ALL Questions

PART A (10 2 = 20 Marks) 1. 2. 3. 4. 5. 6. 7. 8. 9. 10.

What are the different types of gate array based ASICs? Draw a circuit for a positive-enabled latch using transmission gates. List out the drawbacks of SRAM programming technology. What is metastability?

Distinguish between hard macro and soft macro. What is back annotation?

List out the objective of BIST. Define fault propagation.

Mention the objective of global routing.

What are major problems with LVS check? PART B (5 16 = 80 Marks) (6) (6) (4)

11.

(a)

(i) (ii)

Design a 4 bit carry look ahead adder. Discuss the working of Wallace tree multiplication algorithm.

(iii) Perform ( 4 ) (2) using Booths algorithm. Or (b)

1

(i)

Explain various types of programmable logic devices.

4

Or

0

(8) (10)

F = ( A B ) + (B C ) + D . Use Shannons

(ii)

Discuss the various steps involved in ASIC design flow with a neat flowchart. (8) Discuss in detail the Actel ACT logic module. Consider the function

12.

(a)

(i)

(ii)

expansion theorem to expand F with respect to B :

F = B F1 + B F2 .

1

(6)

Maximum : 100 Marks

(b)

(i)

Draw the transfer characteristics of an inverting buffer with a very high gain that has a switching threshold of 2.2 V and 300 mV hysteresis. If the center of the hysteresis shifts by 0.3 V and +0.4 V and the hysteresis varies from 260 mV to 350 mV calculate VIH(min )

and VIL (max ) . (8)

(ii) 13. (a) (i)

Write short notes on metal-metal antifuse. Compare Actel ACT1, Actel ACT2 programmable ASIC inter connect. and

Xilinx

Or (b) (i)

Explain in detail the Alteras MAX 9000 interconnect scheme and altera FLEX interconnect scheme. (10) Create a vectored instance of eight inverters inv0 through inv7. Write a netlist in internal and EDIF form and explain the contents. (6) Explain in detail the Boundary scan test.

(ii)

14.

(a)

(i) (ii)

1

2

(ii)

Write a note on low level programmable languages.

(b)

(i) (ii)

Explain steps involved in a PODEM algorithm with a suitable example. (8)

15.

(a)

(i)

Explain in detail the min-cut placement and eigenvalue placement algorithms. (10) Explain the steps involved in left edge algorithm for a two layer channel routing. (6) Or

(ii)

(b)

(i) (ii)

Write a detailed note on clock routing and power routing. Distinguish between global routing and detailed routing.

Explain in detail any two BIST architectures.

0

Or

Explain any two algorithms used for fault simulation.

0

(8) (XC 3000) (10) (6) (10) (6) (8) (10) (6)

J7797

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Project Name: Management Functions of BisconniDocument6 pagesProject Name: Management Functions of BisconniUsman RaoNo ratings yet

- Debate-Script 1Document3 pagesDebate-Script 1api-537254339No ratings yet

- Power Amplifiers - Power PointDocument33 pagesPower Amplifiers - Power PointrajasekarkprNo ratings yet

- Chapter 3Document17 pagesChapter 3rajasekarkprNo ratings yet

- JNTUA - IV ECE - LPVLSI - Unit V - Leakage Power MinimizationDocument66 pagesJNTUA - IV ECE - LPVLSI - Unit V - Leakage Power Minimizationrajasekarkpr100% (2)

- Question Bank - Lowpower VLSI Circuits - JNTUADocument3 pagesQuestion Bank - Lowpower VLSI Circuits - JNTUArajasekarkpr100% (5)

- UNIT 4 - Switched CapacitanceDocument75 pagesUNIT 4 - Switched Capacitancerajasekarkpr100% (1)

- ECE 7th Sem R2008Document29 pagesECE 7th Sem R2008rajasekarkprNo ratings yet

- List Engg CollegesDocument7 pagesList Engg CollegespoisonedstarNo ratings yet

- 13 - Emf May 2013Document3 pages13 - Emf May 2013rajasekarkprNo ratings yet

- Implementation of Stronger Aes by Using Dynamic S-Box Dependent of Master KeyDocument9 pagesImplementation of Stronger Aes by Using Dynamic S-Box Dependent of Master KeyrajasekarkprNo ratings yet

- PCI6221Document7 pagesPCI6221rajasekarkprNo ratings yet

- Cad Question Paper PDFDocument3 pagesCad Question Paper PDFrajasekarkprNo ratings yet

- CAD For VLSI Algorithms For VLSI Design Automation by GerezDocument330 pagesCAD For VLSI Algorithms For VLSI Design Automation by Gerezrajasekarkpr89% (9)

- P.G. Diploma Examination - 2010: (Vlsi Design)Document2 pagesP.G. Diploma Examination - 2010: (Vlsi Design)rajasekarkprNo ratings yet

- Bit Serial MultiplierDocument4 pagesBit Serial MultiplierrajasekarkprNo ratings yet

- Cad For Vlsi Circuits 2 PDFDocument2 pagesCad For Vlsi Circuits 2 PDFrajasekarkpr100% (1)

- IntelDocument8 pagesIntelrajasekarkprNo ratings yet

- Antenna MeasurementsDocument6 pagesAntenna MeasurementsrajasekarkprNo ratings yet

- Patient Experience Measurement: Presented by Anum HashmiDocument16 pagesPatient Experience Measurement: Presented by Anum HashmiAnumNo ratings yet

- Hussain 2020Document13 pagesHussain 2020Prince RajputNo ratings yet

- MetricsDocument50 pagesMetricsArjun VaranasiNo ratings yet

- Binding MaterialsDocument4 pagesBinding MaterialsSalih MohayaddinNo ratings yet

- SECTION 4.00: TroubleshootingDocument12 pagesSECTION 4.00: TroubleshootingMahmoudNo ratings yet

- A Smart Blind Stick For Aiding Visually Impaired PeopleDocument3 pagesA Smart Blind Stick For Aiding Visually Impaired PeopleInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- (P1) Modul DC Motor Speed Control SystemDocument13 pages(P1) Modul DC Motor Speed Control SystemTito Bambang Priambodo - 6726No ratings yet

- Fluid IIDocument2 pagesFluid IIJefara 01No ratings yet

- A.zerrouki Et El The Natural Circulation Solar Water Heater ModelDocument11 pagesA.zerrouki Et El The Natural Circulation Solar Water Heater ModelJuan-Pierre HerbothNo ratings yet

- Yazan Khatib Resume OfficialDocument3 pagesYazan Khatib Resume Officialapi-383976197No ratings yet

- TNC 426 TNC 430: User's Manual Conversational ProgrammingDocument374 pagesTNC 426 TNC 430: User's Manual Conversational ProgrammingСлоба ЈовановићNo ratings yet

- C FunctionsDocument36 pagesC FunctionsAditya PandeyNo ratings yet

- Swichtgear de Media Tension Aislado Por AireDocument33 pagesSwichtgear de Media Tension Aislado Por Airetotipo10No ratings yet

- Natural Ways To Avoid Bone Loss Around Teeth - HealthspanDocument1 pageNatural Ways To Avoid Bone Loss Around Teeth - HealthspanRotariu AlexNo ratings yet

- IOT Door Buzzer & Home Security DeviceDocument5 pagesIOT Door Buzzer & Home Security Devicekutty vickyNo ratings yet

- Checklist Applicants (1) Senior HighDocument1 pageChecklist Applicants (1) Senior HighdonNo ratings yet

- James Hardie Eaves and Soffits Installation ManualDocument32 pagesJames Hardie Eaves and Soffits Installation ManualBoraNo ratings yet

- An130b6fph (2006)Document96 pagesAn130b6fph (2006)Kira FulgencioNo ratings yet

- Regional Memorandum: Adjusted Search Timeline Activity Date RemarksDocument2 pagesRegional Memorandum: Adjusted Search Timeline Activity Date RemarksKimttrix WeizsNo ratings yet

- Fuji Micrex SXDocument73 pagesFuji Micrex SXRetno WulandariNo ratings yet

- CBE WoldiaDocument99 pagesCBE WoldiaTariku BalangoNo ratings yet

- Solution of Midterm Exam 322E Power Transmission Syst Spring 2009Document13 pagesSolution of Midterm Exam 322E Power Transmission Syst Spring 2009Aslı ÇakırNo ratings yet

- Gen Info Reviewer PDFDocument6 pagesGen Info Reviewer PDFJhocell Maureen FelicianoNo ratings yet

- Dafpus BakteriDocument3 pagesDafpus Bakterivanessa candraNo ratings yet

- Vizag Araku 2n3d Package Tour 178Document2 pagesVizag Araku 2n3d Package Tour 178Vizag TourismNo ratings yet

- Milk TesterDocument9 pagesMilk TesterUjval ParghiNo ratings yet

- Siemens - Sitrans Lr200Document192 pagesSiemens - Sitrans Lr200Jonathan Olivier Salgado NesbetNo ratings yet

- Mastering DAX - Color 1 Slide Per PageDocument309 pagesMastering DAX - Color 1 Slide Per Pagemike110*100% (1)