Professional Documents

Culture Documents

Divisor de 4 Bits en VHDL

Uploaded by

Jorge AlmaguerOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Divisor de 4 Bits en VHDL

Uploaded by

Jorge AlmaguerCopyright:

Available Formats

Diseo de Sistemas digitales TAREA 6

24 de octubre de 2011

[]

Objetivo

Disear un divisor de 4 bits.

Desarrollo

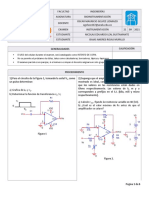

Para la implementacin del divisor se emple la siguiente configuracin encontrada en lnea la cual implementa un sumador-restador mas un arreglo en cascada mostrado a continuacin.

Pgina 2

24 de octubre de 2011

[]

Codigo sumador restador

library IEEE; use IEEE.std_logic_1164.all; entity cas is -- Controlled Add/Subtract cell port ( divisor : in std_logic; T : in std_logic; remainder_in : in std_logic; cin : in std_logic; remainder_out : out std_logic; cout : out std_logic); end entity cas; architecture behavorial of cas is signal tt : std_logic; begin -- circuits of cas tt <= T xor divisor; remainder_out <= tt xor remainder_in xor cin; cout <= (tt and remainder_in) or (tt and cin) or (remainder_in and cin); end architecture behavorial; -- of cas quotient : out std_logic_vector(3 downto 0); remainder : out std_logic_vector(3 downto 0)); end divcas4;

Cdigo divisor

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

architecture structural of divcas4 is component cas -- Controlled Add/Subtract cell port ( divisor : in std_logic; T : in std_logic; remainder_in : in std_logic; cin : in std_logic; remainder_out : out std_logic; cout : out std_logic); end component; signal T : std_logic_vector(3 downto 0); signal c36, c35, c34, c33, c25, c24, c23, c22 : std_logic; signal c14, c13, c12, c11, c03, c02, c01, c00 : std_logic; signal r36, r35, r34, r33, r25, r24, r23, r22 : std_logic; signal r14, r13, r12, r11, r03, r02, r01, r00 : std_logic; --dividend<="0000" & dividend; begin T(3) <= '1'; cas36: cas port map( divisor(3), T(3), dividend(6), c35, r36, c36); cas35: cas port map( divisor(2), T(3), dividend(5), c34, r35, c35); cas34: cas port map( divisor(1), T(3), dividend(4), c33, r34, c34); cas33: cas port map( divisor(0), T(3), dividend(3), T(3), r33, c33); Pgina 3

entity divcas4 is -- 8 bit dividend, 4 bit divisor port ( dividend : in std_logic_vector(7 downto 0); divisor : in std_logic_vector(3 downto 0);

24 de octubre de 2011

[] divisor(0), T(1), dividend(1), T(1), r11, c11); T(0) <= not r14; cas03: cas port map( divisor(3), T(0), r13 , c02, r03, c03); cas02: cas port map( divisor(2), T(0), r12 , c01, r02, c02); cas01: cas port map( divisor(1), T(0), r11 , c00, r01, c01); cas00: cas port map( divisor(0), T(0), dividend(0), T(0), r00, c00); quotient(3) <= T(2); quotient(2) <= T(1); quotient(1) <= T(0); quotient(0) <= not r03 ; remainder(3) <= r03; remainder(2) <= r02; remainder(1) <= r01; remainder(0) <= r00; end structural;

T(2) <= not r36; quotient(3) <= T(2); cas25: cas port map( divisor(3), T(2), r35 , c24, r25, c25); cas24: cas port map( divisor(2), T(2), r34 , c23, r24, c24); cas23: cas port map( divisor(1), T(2), r33 , c22, r23, c23); cas22: cas port map( divisor(0), T(2), dividend(2), T(2), r22, c22); T(1) <= not r25; cas14: cas port map( divisor(3), T(1), r24 c14); cas13: cas port map( divisor(2), T(1), r23 c13); cas12: cas port map( divisor(1), T(1), r22 c12); cas11: cas port map(

, c13, r14,

, c12, r13,

, c11, r12,

Mostrando las siguientes salidas sin embargo presenta un problema el programa mostrado a continuacin.

Pgina 4

24 de octubre de 2011

[DISEO DE SISTEMAS DIGITALES TAREA 6]

Cuando se implementan nmeros en los cuales el dividendo es menor que el divisor genera un problema en el residuo el cual se le deben restar 13 para darlo correctamente

Pgina 5

You might also like

- Antenas - Satelite AmazonasDocument421 pagesAntenas - Satelite AmazonasAlan Nelson Llanos100% (1)

- Capitulo7. Timer1 Del AVR Del ATmega32 (Español)Document22 pagesCapitulo7. Timer1 Del AVR Del ATmega32 (Español)Fortino80% (5)

- Sistemas memristivos: representación físico-matemática desde la teoría de sistemas dinámicosFrom EverandSistemas memristivos: representación físico-matemática desde la teoría de sistemas dinámicosNo ratings yet

- TV 21fu6rlDocument24 pagesTV 21fu6rlJhonatan Quiñonez33% (3)

- Fpga y PLD, VHDL y VerilogDocument6 pagesFpga y PLD, VHDL y VerilogLuis PintadoNo ratings yet

- MANUAL DE PRÁCTICAS DE SISTEMAS DIGITALES II-aDocument79 pagesMANUAL DE PRÁCTICAS DE SISTEMAS DIGITALES II-aElizabeth Manzano ZavalaNo ratings yet

- 02-4 Placa UCPDocument13 pages02-4 Placa UCPgustavo sanchezNo ratings yet

- Mecatrónica: modelado, simulación y control de sistemas físicosFrom EverandMecatrónica: modelado, simulación y control de sistemas físicosNo ratings yet

- Programaciones BascomDocument77 pagesProgramaciones BascomFercHo MDsNo ratings yet

- Trabajo Final1 - VHDLDocument7 pagesTrabajo Final1 - VHDLElyel Surco M0% (1)

- TEMA - 02 Arquitectura PIC18Document49 pagesTEMA - 02 Arquitectura PIC18Ricardo ElizaldeNo ratings yet

- Laboratorio 3 - TecladoDocument9 pagesLaboratorio 3 - TecladoManolo Camilo Ortega CondegaNo ratings yet

- Curso Microprocesadores y Micro Control Adores Unidad 1Document102 pagesCurso Microprocesadores y Micro Control Adores Unidad 1Dario Cruz ParraNo ratings yet

- Ejercicios Básicos para MicroconladoresDocument8 pagesEjercicios Básicos para MicroconladoresestanizniloNo ratings yet

- Tutorial Verilog BloqueDocument42 pagesTutorial Verilog BloqueterrysconNo ratings yet

- Conversor Digital Analógico ComercialDocument1 pageConversor Digital Analógico ComercialWendyNo ratings yet

- Reset Por Hardware en Un PicDocument1 pageReset Por Hardware en Un PicUfoLeds CncNo ratings yet

- Resistencias SemiconductorasDocument2 pagesResistencias SemiconductorasRodrigo Rojas SoberNo ratings yet

- Pic 18F4550Document11 pagesPic 18F4550seykarimNo ratings yet

- Infome de Laboratorio 2Document29 pagesInfome de Laboratorio 2Beto Bryan LinoNo ratings yet

- Multiplex OresDocument17 pagesMultiplex Oresyouacrazy100% (1)

- PID en PICDocument9 pagesPID en PICArmando Pérez ReynosoNo ratings yet

- Caracterización de Conversores ADCDocument4 pagesCaracterización de Conversores ADCJonathanNo ratings yet

- Bus I2C Sensor de TemperaturaDocument11 pagesBus I2C Sensor de TemperaturaRoss JovelNo ratings yet

- Programacion ICSPDocument3 pagesProgramacion ICSPEdilberto CarvajalNo ratings yet

- Microcontroladores PIC18F4550.Document15 pagesMicrocontroladores PIC18F4550.Gabriel Acevedo lopezNo ratings yet

- P04 Hola Mundo Con PIC18F4550Document15 pagesP04 Hola Mundo Con PIC18F4550Pamela Pacheco CabezasNo ratings yet

- VHDL y FpgaDocument33 pagesVHDL y FpgaSting Marquez VargasNo ratings yet

- Teclado Matricial 4x4 Con El PIC16F877ADocument4 pagesTeclado Matricial 4x4 Con El PIC16F877AELPICHUENo ratings yet

- Operaciones Con BitsDocument10 pagesOperaciones Con BitspatriciomelendesNo ratings yet

- Proyecto Final - Electronica DigitalDocument4 pagesProyecto Final - Electronica Digitalmguadalupe2No ratings yet

- Diseño de Una Alarma AntirroboDocument12 pagesDiseño de Una Alarma AntirrobojahemscbNo ratings yet

- Microprocesador VHDLDocument12 pagesMicroprocesador VHDLVictor Jesus Sanz FloresNo ratings yet

- Informe 1 DACDocument9 pagesInforme 1 DACJose ArmandoNo ratings yet

- Lab 4 ADCDocument6 pagesLab 4 ADCManolo Camilo Ortega CondegaNo ratings yet

- Termómetro Con 16F877ADocument9 pagesTermómetro Con 16F877ANelson S100% (1)

- Guia Flip Flop VHDLDocument16 pagesGuia Flip Flop VHDLViridiana Fernandez CarreonNo ratings yet

- Reloj DigitalDocument25 pagesReloj DigitalEdgar Segales VillcaNo ratings yet

- Electroculografía Aplicada A Manejo de Silla de RuedasDocument4 pagesElectroculografía Aplicada A Manejo de Silla de RuedasMariluna CastañoNo ratings yet

- Code Fuente - PIC18F4550Document4 pagesCode Fuente - PIC18F4550Frank's Ĵalanok'a Cruz0% (1)

- Tecnologia PCB MulticapaDocument4 pagesTecnologia PCB MulticapacarlcoxNo ratings yet

- Guía Rápida Del Ensamblador de Los Microprocesadores ATMEL-AVRDocument8 pagesGuía Rápida Del Ensamblador de Los Microprocesadores ATMEL-AVRDavid GuerraNo ratings yet

- Informe DC-DC ReductorDocument9 pagesInforme DC-DC ReductorWilliam Tamayo100% (1)

- Lenguajes de Descripción de Hardware (HDL)Document34 pagesLenguajes de Descripción de Hardware (HDL)Arturo72No ratings yet

- Sensor de ToqueDocument3 pagesSensor de ToqueOptimusTronic100% (3)

- Microcontroladores Prac. 4, 5 & 6 (Ejer. 5, 6 & 7)Document27 pagesMicrocontroladores Prac. 4, 5 & 6 (Ejer. 5, 6 & 7)Darwin EspinozaNo ratings yet

- Optimizacion de Cauces FuncionalesDocument79 pagesOptimizacion de Cauces Funcionalescupido0005No ratings yet

- Circuito Integrado RestadorDocument11 pagesCircuito Integrado RestadorBal Hdez100% (1)

- Diseño y Montaje de Un Controlador Pid de Posiciòn de Un Motor DCDocument10 pagesDiseño y Montaje de Un Controlador Pid de Posiciòn de Un Motor DCOscar Dario Cristancho SaboyaNo ratings yet

- Capitulo5. Sentencias de Control Programación Del ATmega32 (Español)Document5 pagesCapitulo5. Sentencias de Control Programación Del ATmega32 (Español)Fortino100% (4)

- PIC 18 Simulator IDEDocument44 pagesPIC 18 Simulator IDEfhidalgo_8No ratings yet

- Estimación de canal MIMO en ondas milimétricas mediante motores de juegos y aceleración por HardwareFrom EverandEstimación de canal MIMO en ondas milimétricas mediante motores de juegos y aceleración por HardwareNo ratings yet

- Tarea 6Document7 pagesTarea 6Luis SantacruzNo ratings yet

- Mecanismo de 4 BarrasDocument4 pagesMecanismo de 4 BarrasAlex ParedesNo ratings yet

- I12Document13 pagesI12Alexander LaraNo ratings yet

- Ajuste Herschel BulkleyDocument4 pagesAjuste Herschel BulkleyKasperSmerdiakovNo ratings yet

- Labo 2 Tele IiDocument29 pagesLabo 2 Tele IiCarlos MoreNo ratings yet

- Espacio de TrabajoDocument3 pagesEspacio de TrabajoSteven GaleanoNo ratings yet

- Laboratorio 4 - de La Cruz Flores - Patrick Gilbert - 20171897 - GRUPO-BDocument13 pagesLaboratorio 4 - de La Cruz Flores - Patrick Gilbert - 20171897 - GRUPO-BPatrick Gilbert De la Cruz FloresNo ratings yet

- Cinematica Inversa DMDocument5 pagesCinematica Inversa DMDiego MirandaNo ratings yet

- RECTIFICADORDocument5 pagesRECTIFICADORceleste claroNo ratings yet

- El Mito de Las Conexiones de Masa, Tierra y ChasisDocument6 pagesEl Mito de Las Conexiones de Masa, Tierra y ChasisjlcamargomadridistaNo ratings yet

- 2 SenaDocument8 pages2 SenaBlair RojasNo ratings yet

- Electronica de PotenciaDocument3 pagesElectronica de PotenciaPaulNo ratings yet

- Radio 2 - TV DigitalDocument31 pagesRadio 2 - TV DigitaljorgeNo ratings yet

- Electronica en La ActualidadDocument7 pagesElectronica en La ActualidadSebastian MorquechoNo ratings yet

- Osciladores SinusoidalesDocument109 pagesOsciladores SinusoidalesMIGUEL JESUS MEDINA GAGONo ratings yet

- 14SB1RB L2Document15 pages14SB1RB L2Alexandre Alves GomesNo ratings yet

- DSB SCDocument22 pagesDSB SCEduardo Lanchi71% (7)

- 3.2 Memoria RealDocument5 pages3.2 Memoria Realeriick96310% (1)

- Transformador Monofásico TR 28 IP20Document2 pagesTransformador Monofásico TR 28 IP20stanly_20No ratings yet

- Hoja Guia 01 PDFDocument6 pagesHoja Guia 01 PDFLuis OñaNo ratings yet

- Teoría de Control II - Lab2 20182Document3 pagesTeoría de Control II - Lab2 20182Giancarlo Figueroa OyolaNo ratings yet

- Manual Tarjeta CPLDDocument24 pagesManual Tarjeta CPLDIgnacio MoyaNo ratings yet

- Tema 5 OCW - Lineas de TransmisionDocument24 pagesTema 5 OCW - Lineas de TransmisionOscar J. BohórquezNo ratings yet

- Tarea BiosDocument3 pagesTarea BiosJOHN SEBASTIAN GUERRERO PINTONo ratings yet

- Redes de Acoplamiento de ImpedanciasDocument2 pagesRedes de Acoplamiento de ImpedanciasKatherin RodriguezNo ratings yet

- Memoria RomDocument1 pageMemoria Romochoafabiola762No ratings yet

- Examen 02 InstrumentaciónDocument6 pagesExamen 02 InstrumentaciónDario CaphistNo ratings yet

- Examen TYP Sept 06 SolucionDocument11 pagesExamen TYP Sept 06 Solucionnicolasete33No ratings yet

- Puesta en Marcha Grafica Del Iris 9600Document14 pagesPuesta en Marcha Grafica Del Iris 9600tecniofi1100% (2)

- Circuitos IntegradosDocument2 pagesCircuitos Integradosandersonkevinpromo2020No ratings yet

- Wilson Pro 70 Plus LXDocument2 pagesWilson Pro 70 Plus LXMauricioNo ratings yet

- Voz PasivaDocument2 pagesVoz Pasivajua5nNo ratings yet

- Presentacion BluetoothDocument23 pagesPresentacion BluetoothjhoniNo ratings yet

- Circuito para Secador Automático de Manos PDFDocument5 pagesCircuito para Secador Automático de Manos PDFOscar CorreaNo ratings yet

- TEMA AutotransformadorDocument7 pagesTEMA AutotransformadorDiego CseverinoNo ratings yet