Professional Documents

Culture Documents

Sec2 - Power Dist - Controller - Keypad PDF

Uploaded by

Rds Comunicaciones EirlOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sec2 - Power Dist - Controller - Keypad PDF

Uploaded by

Rds Comunicaciones EirlCopyright:

Available Formats

Commercial Series

CP140/CP160/CP180 Portable Radios

Power Distribution, Controller and Keypad Service Information

Issue: December 2003

ii

Computer Software Copyrights

The Motorola products described in this manual may include copyrighted Motorola computer programs stored in semiconductor memories or other media. Laws in the United States and other countries preserve for Motorola certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or reproduce in any form, the copyrighted computer program. Accordingly, any copyrighted Motorola computer programs contained in the Motorola products described in this manual may not be copied or reproduced in any manner without the express written permission of Motorola. Furthermore, the purchase of Motorola products shall not be deemed to grant, either directly or by implication, estoppel or otherwise, any license under the copyrights, patents or patent applications of Motorola, except for the normal non-exclusive royaltyfree license to use that arises by operation of law in the sale of a product.

iii

Table of Contents

Chapter 1 THEORY OF OPERATION

1.0 Overview.............................................................................................................. 1-1 2.0 Radio Power Distribution ..................................................................................... 1-1 3.0 Controller Circuits ................................................................................................ 1-3 3.1 General .......................................................................................................... 1-3 3.2 Microprocessor Circuitry ................................................................................ 1-4 3.3 Audio Circuitry................................................................................................ 1-8 3.4 Keypad ......................................................................................................... 1-11 3.5 Speaker and Microphone ............................................................................. 1-11 3.6 LCD Display Module .................................................................................... 1-11

Chapter 2

TROUBLESHOOTING CHARTS

1.0 Troubleshooting Flow Chart for Board and IC Signals (includes Controller, DC Regulation and Audio) .................................................. 2-1

Chapter 3

CONTROLLER SCHEMATICS

1.0 Allocation of PCBs and Schematic Diagrams...................................................... 3-1 2.0 Controller Schematics (includes Keypad and Speaker/Microphone) .................. 3-3 3.0 Keypad Board Parts List (8466565A01-O) .......................................................... 3-9

iv

Chapter 1 THEORY OF OPERATION

1.0 Overview

This chapter provides a detailed theory of operation for the controller circuits in the radio. The components of these circuits are contained on the Main Board. Refer to the RF sections of this manual for the component location details and the parts lists of the Controller Circuits. This chapter also provides details of the keypad/display and the microphone and speaker connections.

2.0

Radio Power Distribution

Accessories 20 pin Connector Audio Power Amplifier Vdda Regulator SWB+ Fuse Control On/Off Switch Low Battery Detect Antenna Switch 5V Regulator 5V RF AMP, IF AMP, RX/TX Buffers IFIC Vddd Regulator Tx Led Vdda Keypad/Option Board

UNSWB+ 7.5V Battery

Vddd

MECH. SWB+ 3.3V Reg.

MCU, ROM and EEPROM

LCD Driver

ASFIC_CMP

FRACTN VCOBIC

LI Ion

PA, Driver PCIC(ALC)

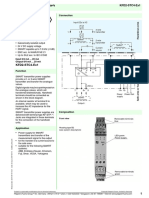

Figure 1-1 DC Power Distribution Block Diagram Figure 1-1 illustrates the DC distribution throughout the radio board. Battery voltage enters at connector J301 and is routed through fuse F301 to become USWB+. VR301 protects against ESD, and D301 provides reverse polarity protection. This voltage is routed to:

I I I I I

FET switch Q170 in the TX power control circuit (turned on during transmit) TX power amplifier module U110 (via R150) input pins of regulators U310, U320 and U330 FET switch Q493 (turned on whenever the radio is on) on-off switch S444 (part of on-off-volume control) to become SWB+

1-2

THEORY OF OPERATION

When the radio is turned on, SWB+ is present and is applied to:

I I I

transistor switch Q494 (pins 1 and 6) which turns on Q493 RX audio power amplifier U490 voltage divider R420/R421 and port PE0, a microprocessor A/D input which measures battery voltage and radio on/off status

The output of FET switch Q493 is applied to the control pins of regulators U310, U320 and U330, turning them on. The following regulators are used: Table 1-1 Voltage Regulators Reference No. U310 U320 U330 Description 5V Regulator Digital 3.3V Regulator 3V Regulator Type TK71750S LP2986 TK71730S

The 5V source is applied to:

I I I I I

RX back end circuitry synthesizer super filter input and charge pump supply RED/GRN LEDs RX audio buffer U510 portions of ASFIC U451

The 5V source is also applied to FET switches Q311 and Q312. Q311 is turned on by Q313 when RX_ENA (from U401 pin 49) is high, and supplies the "5R" source to the RF front end stages Q21Q22, and the VCO RX injection buffer Q280. Q312 is turned on by Q313 when TX_ENA (from U401 pin 50) is high, and supplies the "5T" source to the first transmitter stage Q100. The digital 3.3 volt source from U320 (D_3.3V) is applied to:

I I I I

microprocessor U401 EEPROM U402 S-RAM U403 (not used) flash ROM U404

The 3V regulated source from U330 is applied to:

I I I I

synthesizer IC U201 VCO/buffer IC U251 portions of ASFIC U451 microphone bias circuitry

While the radio is turned on, port PH3 (U401 pin 44) is held high. When the radio is turned off, SWB+ is removed and port PE0 (U401 pin 67) goes low, initiating a power-down routine. Port PH3 (pin 44) remains high, keeping the voltage regulators on via Q493 and Q494, until the operating state of the radio has been stored in EEPROM and other turn-off data functions have been completed. PH3 then goes low, turning off Q494 and Q493, and all regulated voltages are removed.

Controller Circuits

1-3

3.0

3.1

Controller Circuits

General

The controller board is the central interface between the various subsystems of the radio. It provides the following functions:

I I I I I I I

interface with controls and indicators serial bus control of major radio circuit blocks encoding and/or decoding of selective signaling formats such as PL, DPL, MDC1200 and QuikCall II interface to CPS programming via the microphone connector storage of customer-specific information such as channel frequencies, scan lists, and signaling codes storage of factory tuning parameters such as transmitter power and deviation, receiver squelch sensitivity, and audio level adjustments power-up, power-down and reset routines

In the UHF and VHF sections, the Radio Block Interconnect Diagram show the interconnections between the controller and the various other radio blocks, while the Controller Interconnect Schematic diagram (in this chapter) shows the connections between the following circuit areas which comprise the controller block:

I I I I I

microprocessor circuitry audio circuitry DC regulation circuitry rotary and pushbutton controls and switches option board interface

The majority of the circuitry described below is contained in the Microprocessor Circuit schematic diagrams. However, portions are also found in the DC Regulation and UHF/VHFAudio Circuit schematics.

1-4

THEORY OF OPERATION

3.2

Microprocessor Circuitry

The microprocessor circuitry includes microprocessor (U401) and associated EEPROM and Flash ROM memories. The following memory IC's are used: Table 1-2 Radio Memory Requirements Reference No. U402 U403 U404 Description Serial EEPROM Static RAM Flash ROM Type AT25128 (not used) AT49LV001N_70V 128K x 8 Size 16K x 8

3.2.1

Memory Usage Radio operation is controlled by software that is stored in external Flash ROM memory (U404). Radio parameters and customer specific information is stored in external EEPROM (U402). The operating status of the radio is maintained in RAM located within the microprocessor. When the radio is turned off, the operating status of the radio is written to EEPROM before operating voltage is removed from the microprocessor. Parallel communication with U403 and U404 is via:

I I I I I I

address lines A(0)-A(16), from U401 port F ADDR0-ADDR13 and port G XA14-XA16 data lines D(0)-D(7), from U401 port C DATA0-DATA7 chip-select for U403, from PH6 (U401 pin 41) chip-enable for U404, from PH7 (U401 pin 38) output enable for U404, from PA7 (U401 pin 86) write-enable for both U403 and U404, from PG7_R/W (U401 pin 4)

Serial communication with U402 is via:

I I

the SPI bus chip-select for U402, from PD6 (U401 pin 3)

3.2.2

Control and Indicator Interface Ports PI3 and PI4 are outputs which control the top-mounted LED indicator. When PI3 is high, the indicator is red. When PI4 is high, the indicator is green. When both are high, the indicator is amber. When both are low, the indicator is off. Pressing the side-mounted PTT button (S441) provides a low to port PJ0 (U401 pin 71), which indicates PTT is asserted. Side-mounted option buttons 1 and 2 (S442 and S443) are connected to Ports PJ6 (pin 77) and PJ7 (pin 78), respectively.

Controller Circuits

1-5

3.2.3

Serial Bus Control of Circuit Blocks The microprocessor communicates with other circuit blocks via a SPI (serial peripheral interface) bus using ports PD2 (data into uP), PD3 (data out of uP) and PD4 (clock). The signal names and microprocessor ports are defined in Table 1-3. Table 1-3 SPI Bus Signal Definitions Signal Name SPI-DATA_IN SPI_DATA_OUT SPI_CLK These signals are routed to:

I I I I

Microprocessor Port PD2-MISO PD3-MOSI PD4-SCK

Microprocessor Pin U401 Pin 99 U401 pin 100 U401 pin 1

the audio filter IC (U451) to control internal functions such as gain change between 25 kHz and 12.5 kHz channels, transmit or receive mode, volume adjustment, etc. the synthesizer IC U201 to load receive and transmit channel frequencies option board connector J460-1 for internal option configuration and control (not applicable to CP150/CP200 models) serial EEPROM U402 (both SPI_DATA_IN and SPI_DATA_OUT are used)

In order for each circuit block to respond only to the data intended for it, each peripheral has its own chip select (or chip enable) line. The device will only respond to data when its enable line is pulled low by one of the microprocessor ports, as follows:

I I I I

port PD5 (U401 pin 2) for the audio filter IC port PH0 (U401 pin 47) for the synthesizer IC port PH4 (U401 pin 43) for the option board/display enable (not used in CP150/CP200) port PD6 (U401 pin 3) for the serial EEPROM

3.2.4

Interface to RSS Programming The radio can be programmed, or the programmed information can be read, using a computer with CPS (Customer Programming Software) connected to the radio via a RIB (radio interface box) or with the RIB-less cable. Connection to the radio is made via the microphone connector (part of accessory connector J471). The SCI line connects the programming contact (J471 pin 6) to ports PD0_RXD (data into uP, pin 97) and PD1_TXD (data out of uP, pin 98). Transistor Q410 isolates the input and output functions by allowing PD1 to pull the line low, but does not affect incoming data from being read by port PD0. This isolation allows high-speed 2-wire programming via TP401 and TP402 for factory programming and tuning.

3.2.5

Storage of Customer-Specific Information Information that has been programmed using CPS, such as channel frequencies or selective signaling codes, are stored in the external EEPROM, where it is retained permanently (unless reprogrammed) without needing DC power applied to the microprocessor.

1-6

THEORY OF OPERATION

3.2.6

Sensing of Externally-Connected Accessories Port PJ1 is used to detect the presence of externally connected accessories. Port PJ1 (U401 pin 72) is normally low, unless accessories (lapel speaker microphone, lightweight headset, etc.) are used with the radio. This port is used to detect an accessory PTT or auto sensing of a VOX accessory. If VOX is programmed into the radio channel codeplug information, and PJ1 is high during powerup, the radio will activate VOX operation. If a low is present at port PJ1 during power-up, the radio will use this port as an external PTT indicator.

3.2.7

Microprocessor Power-Up, Power-Down and Reset Routine On power-up, the microprocessor is held in reset until the digital 3.3V regulator (U320 pin 5) provides a stable supply voltage. Once the digital supply reaches steady state and releases the reset line (U320 pin 7), the microprocessor begins to start up. The ASFIC_CMP (U451) has already started running and is providing the startup clock to the microprocessor. After reset release by all circuits, the software within the microprocessor begins executing port assignments, RAM checking, and initialization. A fixed delay of 100 ms is added to allow the audio circuitry to settle. Next, an alert beep is generated and the steady state software begins to execute (buttons are read, radio circuits are controlled). When the radio is turned off, SWB+ is removed and port PE0 (U401 pin 67) goes low, initiating a power-down routine. Port PH3 (pin 44) remains high, keeping the voltage regulators on via Q493 and Q494, until the operating state of the radio has been stored in EEPROM. PH3 then goes low, and all regulated voltages are removed. The microprocessor reset line (pin 94) can be controlled directly by the digital 3.3 V regulator (U320 pin 7), the microphone jack (part of accessory connector J471) via Q472 and Q471, and the microprocessor itself. U320 pulls the reset line low if the digital 3.3 V source loses regulation. This prevents possible MOS latch-up or overwriting of registers in the microprocessor because the reset line is higher in voltage than the microprocessor VDD ports (U401 pins 12, 39, 59, 88). The microprocessor can drive the reset line low if it detects a fault condition such as an expired watchdog timer, software attempting to execute an infinite loop, unplanned hardware inputs, static discharge, etc. Finally, the Q471 can pull the reset line low during use of the programming cable and CPS by the application of a sufficiently negative voltage to the microphone connector tip contact (J471 pin 4), however this reset method is not utilized.

3.2.8

Boot Mode Control When power-up reset occurs, the microprocessor will boot into either normal or flash mode depending on the logic level of ports MODA (U401 pin 58) and MODB (pin 57). The Flash Adapter is a programming accessory which provides negative 9 volts dc via a 1K resistor to microphone connector J471 pin 4. This turns on Q471 and Q472 via D471 and VR472, pulling MODA and MODB low and allowing booting in the flash mode by cycling power to reset the radio. Software upgrades can then performed by loading the new software code into Flash ROM U404.

Controller Circuits

1-7

3.2.9

Microprocessor 7.3975 MHz Clock The 7.3975 MHz clock signal (uP_CLK) is provided from the ASFIC_CMP (U451 pin 28). Upon startup the 16.8MHz crystal provides the signal to the ASFIC_CMP, which sends out the uP_CLK at 3.8MHz until a steady-state condition is reached and the clock is increased to 7.3975MHz for the microprocessor.

3.2.10

Battery Gauge Various battery types are available having different capacities. The different battery types contain internal resistors connected from the BATT_CHARGE contact to ground (which is routed to the microprocessor as BATT_DETECT). A voltage divider is formed with R255 producing a different DC voltage for each battery type, which is read by microprocessor port PE2 (pin 65). This allows the software to recognize the battery chemistry being used and adjust the battery gauge for best accuracy.

1-8

THEORY OF OPERATION

3.3

3.3.1

Audio Circuitry

Transmit and Receive Low-Level Audio Circuitry The majority of RX and TX audio processing is performed by U451, the Audio Filter IC (ASFIC_CMP), which provides the following functions:

I I I I I I I I I I I I

Tone PL/Digital PL encoding and decode filtering Tone PL/Digital PL rejection filter in RX audio path TX pre-emphasis amplifier TX audio modulation limiter Post-limiter (splatter) filter TX deviation adjust (digitally-controlled attenuators) Programmable microphone gain attenuator RX audio volume control (digitally controlled attenuator) Carrier squelch adjustment (digitally controlled attenuator) Microprocessor output port expansion 2.5 volt dc reference source Microprocessor clock generation (from the 16.8 MHz reference oscillator input)

The parameters of U451 that are programmable are selected by the microprocessor via the CLOCK (U451 pin 21), DATA (U451 pin 22) and chip enable (U451 pin 20) lines. RX audio buffer U510 amplifies the audio level from the DEMOD output of the IFIC before being applied to the audio filter IC input (DISC, U451 pin 2). The buffer is DC coupled to avoid corruption of low-frequency data waveforms such as DPL. Because such waveforms are polarity sensitive, this buffer is configured as a single-stage inverting amplifier (U510-1 only) for VHF models where highside first injection is used, or is configured as a two-stage non-inverting amplifier (U510-1 and -2) for UHF models using low-side first injection. The gain of the buffer is 1.5 times or 3.5 dB. Volume adjustment is performed by a digital attenuator within U451. The volume control (10KO, part of S444) is connected to D_3.3V and ground via R506 and R507. When the volume control is rotated, it varies the dc voltage applied to microprocessor A/D input port PE1 (U401 pin 66) between approximately 0 volts dc at minimum volume to 3.3 volts dc at maximum volume. Depending on this voltage, the appropriate setting of the digital volume attenuator is selected. This technique is less susceptible to noise than a conventional analog volume control.

Controller Circuits

1-9

3.3.2

Audio Power Amplifier The audio power amplifier IC U490 amplifies receiver audio from U451 pin 41 to a level sufficient to drive a loudspeaker. U490 is a bridge amplifier delivering 3.46 volts rms between pins 5 and 8 without distortion, which is sufficient to develop 500 milliwatts of audio power into the internal 24 ohm speaker or an external 24 ohm load. The audio power amplifier is muted whenever speaker audio is not required to reduce current drain. The audio amp is muted when U451 pin 14 is low. When U451 pin 14 is high, U490 pin 1 is pulled low by Q490, enabling the audio amplifier. Because the power amplifier is a bridge-type, neither speaker terminal is grounded. Care should be taken that any test equipment used to measure the speaker audio voltage does not ground either speaker output terminal, otherwise damage to the audio power amplifier IC may result. When a 24ohm load resistor is used it should be connected between the tip and the sleeve of accessory jack J471 (3.5mm port), never to ground. External SPKR plug insertion mechanically disconnects the internal speaker. Voltage measurements using test equipment that is not isolated from ground may be made from one side of the speaker or load resistor (either the tip or the sleeve of J471) to chassis ground, in which case the voltage indicated will be one half of the voltage applied to the speaker or load resistor. The Motorola RLN4460 Portable Test Set and AAPMKN4004 Programming Test Cable provide the proper interface between the radio's ungrounded audio output and ground-referenced test equipment.

3.3.3

Internal Microphone Audio Voice Path Microphone audio from internal microphone is routed from J470-1 via C475, L471, and C470 to the ASFIC_CMP mic audio input (MICINT, U451 pin 46). During transmit, Q470 is turned on by a low at U451 pin 35, providing dc bias for the internal MIC via R478. External MIC plug insertion mechanically disconnects the internal microphone. External MIC audio is coupled through L471 and C470 to the mic audio input. An input level of 10 mV at J471 pin 4 produces 200 mV at the output of U451 pin 40, which corresponds to 60% deviation.

3.3.4

PTT Circuits The internal side-mounted PTT switch (S441) is sensed directly by microprocessor port PJ0 (U401 pin 71). External mic PTT is sensed by measuring the current drawn through the accessory connector (J471-4) by the mic cartridge (which is in series with the accessory PTT switch). This current is drawn through the base (pin 5) and emitter (pin 4) of a transistor in Q470, causing its collector (pin 3) to supply a logic-high to microprocessor port PJ1 (pin 72).

3.3.5

VOX Operation VOX audio accessories do not have a PTT switch. Instead, the mic cartridge is wired directly from J471-4 to ground. If the radio has been programmed for VOX operation and the VOX accessory is plugged in prior to turning the radio on, the current drawn by the cartridge will turn on Q470 (pins 34-5) and a logic high will be seen at port PJ1 at turn-on. The microprocessor then assumes VOX operation, with PTT controlled by the presence of audio at the mic cartridge. A dc voltage proportional to the audio level at the input of the ASFIC_CMP (U451 pin 46) is fed to an A/D input of microprocessor U401 (pin 62). During VOX operation, PTT is activated when the dc level exceeds a preset threshold.

1-10

THEORY OF OPERATION

3.3.6

Battery Charging Through Microphone Jack A wall-type charging power supply may be connected to the 2.5 mm microphone jack (part of accessory connector J451). The voltage present at the tip contact (pin 4) is applied to the center charging contact of the battery via diode D470. Another diode, internal to the battery, applies this voltage to the (+) battery terminal. Only the recommended charger and battery type should be charged in this manner. Different battery types contain internal resistors connected from the BATT_CHARGE contact to ground, which is routed to the microprocessor as BATT_DETECT. A voltage divider is formed with R255 producing a DC voltage which is read by microprocessor port PE2 (pin 65). This allows the software to recognize the battery chemistry being used and adjust the battery gauge for best accuracy. The value of R255 is chosen so that the voltage at the BATT_CHARGE node (cathode of D470) is never low enough to turn on the EXT_MIC_PTT sense transistor (part of Q470).

3.3.7

Programming and Flashing Through Microphone Jack The ring contact on the 2.5 mm microphone jack is used for reading, programming or re-flashing the radio using CPS. This contact (J471 pin 6) is routed to ports PD0_RXD (data into uP, pin 97) and PD1_TXD (data out of uP, pin 98). Transistor Q410 isolates the input and output functions by allowing PD1 to pull the line low, but does not affect incoming data from being read by port PD0. To re-flash the radio (overwrite the software in the Flash ROM with new software), the radio must power up in the boot mode. This is accomplished by using a flash adapter accessory, which provides SCI communication with the programming ring contact (J471 pin 6) and also allows a negative voltage (negative 9 volts dc via a 1K resistor) to be applied to the tip contact (J471 pin 4). This voltage is sufficient to turn on the base-emitter junction (pins 1 and 2) of Q472 via L471, D471, VR472 and R471. Pin 6 of Q472 goes high, turning on Q471 (pins 3 and 4) and pulling the BOOT_ENA line (ports MODA and MODB of the microprocessor) low. Cycling power generates a reset which causes the radio to boot in the flash mode.

Controller Circuits

1-11

3.4

Keypad

The keypad block diagram is shown at Figure 1-2. Pressing a key creates two distinct voltages, KEYPAD_ROW and KEYPAD_COL. These voltages are routed to the microprocessor on the main board. The microprocessor samples the voltages to determine which key has been pressed.

28 Pin Connector (keypad Board)

Keypad Row Keypad Button Keypad Column

Keypad Row Keypad Column

28 Pin Connector (Main Board)

Keypad Row Keypad Column MCP

Figure 1-2 Keypad Block Diagram

3.5

Speaker and Microphone Assemblies

The speaker and microphone are mounted in the radio front housing. They are connected to the audio circuits on the main board, the speaker via connector J491 pins 1 & 2 and the microphone via connector J470 pins 1 & 2. Refer to the Audio Circuitry schematic diagram for details.

3.6

LCD Display Module

The display module is part of the keypad and is connected to the keypad board via a flex cable to connector J1 on the keypad board.

1-12

THEORY OF OPERATION

Chapter 2 TROUBLESHOOTING TABLES

1.0 Troubleshooting Tables for Board and IC Signals (includes Controller, DC Regulation and Audio)

This section contains detailed troubleshooting tables. These tables should be used as a guide in determining the problem areas. They are not a substitute for knowledge of circuit operation and astute troubleshooting techniques. It is advisable to refer to the related detailed circuit descriptions in the theory of operation sections prior to troubleshooting a radio. Most troubleshooting tables end up by pointing to an IC to replace. It is not always noted, but it is good practice to verify supplies and grounds to the affected IC and to trace continuity to the malfunctioning signal and related circuitry before replacing any IC. For instance, if a clock signal is not available at a destination, continuity from the source IC should be checked before replacing the source IC. IC Designator

U310 5V Regulator

Pin

1 2 3 4 5 Vin Ground

Pin Function

DC Voltage

7.48 GND 7.48 1.26 4.96 GND 1.23 0 7.48 3.23 0 3.20 7.48 7.48 GND 7.48 1.26 3.00

Comments (Condition)

Control input Bypass capacitor Vout Ground Feedback Tap (NU) Vin Vout Sense (NU) Error (reset output) Shutdown input Vin Ground Control input Bypass capacitor Vout

U320 3.3V Regulator

1 2 3 4 5 6 7 8

U330 3V Regulator

1 2 3 4 5

2-2

TROUBLESHOOTING TABLES

IC Designator

U401 Microprocessor

Pin

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 PD5_SS

Pin Function

PD4_SCK serial clock input PD6_VLIN PG7_R_W PG6_AS PG0_XA13 PB7_ADDR15 PB6_ADDR14 PB3_ADDR11 PB1_ADDR9 PB2_ADDR10 VDD VSS PBO_ADDR8 PB5_ADDR13 PG1_XA14 PG4_XA17 PG5_XA18 PG3_XA16 PG2_XA15 PB4_ADDR12 PF7_ADDR7 PF6_ADDR6 PF5_ADDR5 PF4_ADDR4 PF3_ADDR3 PF2_ADDR2 PF1_ADDR1 PFO_ADDR0 PC0_DATA0 PC1_DATA1 PC2_DATA2 PC3_DATA3 PC4_DATA4 PC5_DATA5 PC6_DATA6 PC7_DATA7

DC Voltage

0 3.23 3.23 3.21 3.23 3.23 0.026 0.028 3.06 3.05 0.16 3.23 GND 3.05 0.13 0.20 3.17 0 3.21 0.30 0.22 3.03 3.08 3.06 0.16 0.26 3.06 3.06 3.05 0.69 0.96 1.10 0.81 0.62 0.68 0.67 0.73

Comments (Condition)

ASFIC chip select EEPROM chip select

Troubleshooting Tables for Board and IC Signals (includes Controller, DC Regulation and Audio)

2-3

IC Designator

U401 Microprocessor

Pin

38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 VDDL VSSL

Pin Function

PH7_CSPROG

DC Voltage

3.05 3.23 GND 3.23 3.23 0 3.21 0 3.00 3.23 3.00 1.48 0.01 3.23 0 0 0 0 2.98 3.22 3.12 3.23 3.20 3.20 2.91 0.73 0.14 1.62 0 - 3.3 V 2.48 0 3.20 GND 3.23 0 3.23 3.23

Comments (Condition)

PH6_CSGP2 PH5_CSGP1 PH4_CSIO PH3_PW4 PH2_PW3 PH1_PW2 PH0_PW1 XIRQ PI7 PI6 PI5 PI4 PI3 PI2 PI1 PI0 MODB_VSTBY MODA_LIR AVDD PE7_AN7 PE6_AN6 PE5_AN5 PE4_AN4 PE3_AN3 PE2_AN2 PE1_AN1 PE0_AN0 VRL VRH AVSS PJ0_CSGP3 PJ1_CSGP4 PJ2 PJ3

On/off control output

Synth chip select RX enable TX enable Green LED enable Red LED enable

Lock detect from U201-4 Boot mode enable

VOX threshold detect RSSI input

Volume control wiper 33% of battery voltage

Side PTT button External MIC PTT

2-4

TROUBLESHOOTING TABLES

IC Designator

U401 Microprocessor

Pin

75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 PJ4 PJ5 PJ6 PJ7 PA0_IC3 PA1_IC2 PA2_IC1

Pin Function

DC Voltage

3.23 0 3.23 3.23 0 1.57 3.00 3.00 0 0 0 0 GND 3.23 1.60 1.70 1.40 0 0 3.20 0 3.20 3.23 1.9 0 3.23 3.23 0 3.23 GND 3.23 0 3.23 3.23

Comments (Condition)

Bottom option button Top option button

PA3_IC4_OC5_OC1 PA4_OC4_OC1 PA5_OC3_OC1 PA6_OC2_OC1 PA7_PA1_OC1 VSSR VDDR ECLK (NU) EXTAL XTAL VDDSYN XFC (NU) RESET LVOUT IRQ PD0_RXD PD1_TXD PD2_MISO PD3_MOSI Chip select Serial data out Write protect Vss Serial data in Serial clock Hold Vcc

Squelch detect input Channel activity input

Clock from U451-28 Not used

From U320

U402 EEPROM

1 2 3 4 5 6 7 8

From U401-3

Troubleshooting Tables for Board and IC Signals (includes Controller, DC Regulation and Audio)

2-5

IC Designator

U404 Flash ROM

Pin

1 2 3 4 5 6 7 8 9 A11 A9 A8 A13 A14 NC EN_WE Vcc RESET A16 A15 A12 A7 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 GND D3 D4 D5 D6 D7 EN_CE A10 EN_OE

Pin Function

DC Voltage

3.06 3.08 3.05 0.13 0.31 3.17 3.21 3.23 3.20 3.17 0.30 0.22 3.03 3.08 3.06 0 0.24 3.08 3.05 3.05 0.69 0.94 1.08 GND 0.78 0.59 0.66 0.67 0.75 3.01 0.16 0

Comments (Condition)

From U401-4

U404 Flash ROM

10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

From U401-38 From U401-86

2-6

TROUBLESHOOTING TABLES

IC Designator

U451 ASFIC_CMP

Pin

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37

Pin Function

VDD for analog circuits DISC audio input Ground for analog circuits DACU output DACR output DACG output VOX peak detector output PLCAP for DC integrator SQIN Universal audio input/output VDD for DACs SQCAP GCB2 general purpose output GCB1 general purpose output GCB0 general purpose output Squelch channel activity output Squelch detect digital output PL/low speed data I/O High speed data I/O Chip select Serial clock input Serial data input Ground for clock synthesizer Loop filter cap for clock syn PLCAP2 for LS integrator Not used Vdd for clock synthesizer Clock synthesizer output 1200 Hz ref for MDC decode GNDDO Ground for digital circuits Vdd for analog switches Vdd for digital circuits 16.8 MHz master clock input GCB3 general purpose output TX audio return from option GCB4 general purpose output

DC Voltage

3.00 1.34 GND 0 0 2.38 (typ) 2.91 0.40 0.01 0 4.95 0 0 0 3.00 0 0 1.50 3.00 3.23 0 3.23 GND 0.74 1.17 0 3.00 1.70 3.00 GND GND 4.96 3.00 1.54 3.00 0 0

Comments (Condition)

From U510

Power set (TX mode)

Audio PA_EN (unsquelched) BW select (25 kHz mode) To U401-84 To U401-83

From U401-2

Internal MIC enable

Troubleshooting Tables for Board and IC Signals (includes Controller, DC Regulation and Audio)

2-7

IC Designator

U451 ASFIC_CMP

Pin

38 39 40 41 42 43 44 45 46 47 48

Pin Function

GCB5 general purpose output RX audio send to option Modulation output RX audio out to power amp Flat TX audio return from option RX audio return to option Flat TX audio send to option Vdd for audio path I/O filters Mic audio input Ground for audio path I/O filters Ext mic audio input (not used) Unit 1 output Unit 1 (-) input Unit 1 (+) input Ground Unit 2 (+) input Unit 2 (-) input Unit 2 output Vcc Enable/shutdown Bias reference (+) input (-) input (-) output Vcc Ground (+) output Unit 1 output Unit 1 (-) input Unit 1 (+) input Ground Unit 2 (+) input Unit 2 (-) input Unit 2 output Vcc

DC Voltage

0 1.48 1.50 1.51 0.20 1.50 1.50 3.00 1.50 GND 0 2.48 2.48 2.46 GND 0.28 0.29 0 4.96 0.12 3.26 3.26 3.27 3.25 7.48 GND 3.29 1.75 1.56 1.55 GND 1.55 1.56 1.38 4.96

Comments (Condition)

To U201-10

U480 Dual Opamp

1 2 3 4 5 6 7 8

U490 Audio Power Amp

1 2 3 4 5 6 7 8

(Unsquelched) (Unsquelched) (Unsquelched) (Unsquelched) (Unsquelched) (Unsquelched) (Unsquelched)

U510 Dual Opamp

1 2 3 4 5 6 7 8

1. All voltages are measured with a high-impedance digital voltmeter and expressed in volts DC relative to ground (0V). 2. Voltages are measured with a DC input voltage of 7.50 + .02 volts DC applied to the battery connector (J301). 3. All voltages are measured in the squelched receive mode, unless otherwise indicated. 4. Voltages are identical for VHF and UHF models unless otherwise indicated.

2-8

TROUBLESHOOTING TABLES

Chapter 3 CONTROLLER/KEYPAD SCHEMATICS

1.0 Allocation of PCBs and Schematic Diagrams

The Controller circuits are contained on the printed circuit board (PCB) containing the RF circuits. This Chapter shows the schematics for the Controller circuits only, refer to the relevant RF section for details of the related RF circuits, the PCB component layouts and the complete radio parts lists. The Controller schematic diagrams and the related PCBs are shown below. Table 3-1 PCBs and Schematics

PCBs :

8486342Z13_C VHF2 8486635Z03_O UHF1 8486348Z13_C UHF1 8486634Z02_O UHF3 8466565A01_O Keypad top/bottom side SCHEMATICS Controller Interconnect Schematic Microprocessor Circuit Schematic Audio Circuit Schematic DC Regulation Schematic Keypad Schematic Speaker/Microphone Schematic & Parts List PART LIST 8466565A01_O Keypad

Page 3-7 Page 3-3 Page 3-4 Page 3-5 Page 3-6 Page 3-8 Page 3-9 Page 3-9

3-2

CONTROLLER/KEYPAD SCHEMATICS

Controller Schematics

3-3

2.0

Controller Schematics

Controller

SW_B

5V +3 V

SW_B +

5V

VS_AUDIO_SEL CNTL_PWR_SET OPT_MI C OPT_TX_AUD_FLAT_RETURN OPT_TX_AUD_RETURN OPT_TX_AUD_SEND 28 26 24 22 20 18 D3_3 V SW_B + 16 14 12 10 8 6 4 C503 1000pF 2 30 32 27 25 23 21 19 17 15 13 11 9 7 5 3 1 29 31 C405 150pF R504 100 C406 150pF R505 100 TP40 3 TP40 4 R502 100 R501 100 C500 1000pF C501 1uF CNTL_SPI_DATA_OUT SPI_DATA_OUT CNTL_SYNTH_CS SYNTH_CS CNTL_LOCK LOCK CNTL_RSSI RSSI CNTL_TX_ENA TX_ENA 1 E500 BK1005HM47 SPI_CLK 3V OPT_RX_AUD_SEND_DETECTO R OPT_RX_AUD_SEND_UNMUTED OPT_RX_AUD_RETURN VS_GAIN_SEL SPI_DATA_OUT EXT_MIC_PTT PWR_SET CNTL_DEMOD DEMO D CNTL_BW_SEL DEMOD BW_SEL PWR_SET

3V

AUDI O

BW_SEL

CNTL_MOD_OU T

MOD_OUT CNTL_16_8_MHZ 16_8_MHZ BATT_CHARGE 16_8_MHZ MOD_OUT

BOOT_ENA

ASFIC_CS

SQ_DET

CH_ACT

uP_CL K

LSI O

VOX

HSIO

F1200

RESET

SC I

CNTL_SPI_CLK SPI_CLK

J460-1 CONNECTOR ACCESSORY/KEYPA D

C403 150pF

R503 10 0 1000pF SW_B + D3_3V

C50 4

USWB

SW_B

5V

3V

5V

5R

5T

3V D3_3V CNTL_USWB+ USWB+ CNTL_5V

3V

SPI_DATA_OUT

SQ_DET

CH_ACT

EXT_MIC_PTT

BOOT_ENA

SPI_DATA_IN

ASFIC_CS

LSIO

HSIO

uP_CLK

D3_3 V

SW_B +

VOX

F120 0

5V

BATT_DETECT

SPI_CLK

RESET

SCI

NC

DISPL_COM_DATA_SEL VS_RAC OPT_DATA_READY BACKLIGHT KEYPAD_ROW KEYPAD_COL DISP_EN A OPT_EN A VS_CS VS_IN T

TP301 CNTL_5R

5V 5R CNTL_5T 5T

SYNTH_C S

CNTL_3V 3V

MICROPROCESSOR

LOCK USWB + SWB+ 5V RSSI RESET TX_EN A D3_3V 5R 3V 5T

1000pF C506

1000pF C40 2

1000pF C507

1000pF

1000pF

1000pF C407

1000pF C404

1000pF

S441 SWITCH 1 A1 3 A2

B1 2

C505

C408

C409

BATT_CHARGE RX_EN A VOLUME ON_OF F TX_EN A

B2 4

PTT RX_ENA OPT_BUTTON_ 1 OPT_BUTTON_ 2 FREQ_SEL_ 3 S440 SWITCH 8 PC3 PC0 PC1 PC2 C0 C1 9 7 1 2 4 C0 C1 FREQ_SEL_ 0 FREQ_SEL_ 1 FREQ_SEL_ 2 VOLUME ON_OFF

S442 SWITCH 1 A1 3 A2 B1 2 B2 4

DC_REGULATION

S443 SWITCH 1 A1 3 A2 B1 2 B2 4

GND1 GND

Controller Interconnect Schematic Diagram

3-4

Controller Schematics

Microprocessor

D3_3 V D3_3V D3_3V C410 10uF C411 0.1uF C412 1000pF R412 100K 6 1 3 7 5 8 VCC SCK CS 2 WP SO HOLD SI VSS 4 C413 0.1uF TP405 TP402 R410 10K 1 1 1 2 3 R419 4.7K R416 20K R417 10K C418 0.1uF

Q410

6 R411 SC I 820 C419 1000pF 1 1 SH400 SHIELD SH401 SHIELD

U402

X25128-2.7 EEPROM 1 TP401 LSI O CH_ACT SQ_DET HSI O OPT_DATA_READY uP_CLK

SPI_DATA_IN SPI_DATA_OUT SPI_CLK R400 NU DISPL_COM_DATA_SEL 0.1uF C400 NU C414

D3_3 V

R418 100K C415 C416 1000p F 1000pF NC PD6_LVIN 3 PD5_SS 2 PD4_SCK 1 PD3_MOSI 100 PD2_MISO 99 PD1_TXD 98 PD0_RXD 97 NC NC F1200 PA7_PA1_OC1 PA6_OC2_OC1 PA5_OC3_OC1 PA4_OC4_OC1 PA3_IC4_OC5_OC1 PA2_IC1 PA1_IC2 PA0_IC3 VDDSYN 92 XFC 93 LVOUT 95 86 85 84 83 82 81 80 79 EXTAL 90 XTAL 91 VRL 68 VRH 69 VDD VDDR VDDL AVDD 12 88 39 59 RESET NC D414 R413 100K R415 33K R414 33K C417 1000pF

ASFIC_CS

SYNTH_CS SW_B + BACKLIGH T 3 2 R446 10K NC A(14) A(15) A(16) A(17) A(18) 6 16 20 19 17 18 5 47 46 45 44 43 42 41 38 30 31 32 33 34 35 36 37 PG0_XA13 PG1_XA14 PG2_XA15 PG3_XA16 PG4_XA17 PG5_XA18 PG6_AS

ECLK IRQ XIRQ RESET PG7_R_W MODA_LIR MODB_VSTBY

89 96 NC 48 94 4 58 57

BOOT_ENA PTT EXT_MIC_PTT FREQ_SEL_0 FREQ_SEL_1 VS_RAC FREQ_SEL_2 FREQ_SEL_3 OPT_BUTTON_1 OPT_BUTTON_2 C446 .01uF C445 .01uF C440 .01uF C441 .01uF C442 .01uF C443 .01uF C444 .01uF C401 0.1uF

Q403

Q402

3 R445 4.7K 1

NC

2 D(0) D(1) D(2) D(3) D(4) D(5) D(6) D(7) D(7:0) D3_3 V A(18:0) C430 0.1uF C431 1000pF C432 0.1uF 8 VCC 30 EN_CE 32 EN_OE 7 EN_WE RESET 9 20 19 18 17 16 15 14 13 3 2 31 1 12 4 5 11 10 A(0) A(1) A(2) A(3) A(4) A(5) A(6) A(7) A(8) A(9) A(10) A(11) A(12) A(13) A(14) A(15) A(16) C433 1000pF D3_3V

PH0_PW 1 PH1_PW 2 PH2_PW 3 PH3_PW 4 PH4_CSI O PH5_CSGP1 PH6_CSGP2 PH7_CSPROG PC0_DATA0 PC1_DATA1 PC2_DATA2 PC3_DATA3 PC4_DATA4 PC5_DATA5 PC6_DATA6 PC7_DATA7

U401

MC68HC11FL0

71 PJ0_CSGP3 PJ1_CSGP4 72 PJ2 73 PJ3 74 PJ4 75 PJ5 76 PJ6 77 PJ7 78 PE0_AN0 PE1_AN1 PE2_AN2 PE3_AN3 PE4_AN4 PE5_AN5 PE6_AN6 PE7_AN7 PI 7 PI6 PI5 PI4 PI 3 PI 2 PI1 PI0 VSS VSSR VSSL AVSS 13 87 40 70 67 66 65 64 63 62 61 60

7 PB7_ADDR15 8 PB6_ADDR14

DISP_ENA

A(13)15 A(12) 21 A(11) 9 A(10) 11 A(9) 10 A(8) 14

22 23 24 25 26 27 28 29

PB5_ADDR13 PB4_ADDR12 PB3_ADDR11 PB2_ADDR10 PB1_ADDR9 PBO_ADDR8

PF7_ADDR7 PF6_ADDR6 PF5_ADDR5 PF4_ADDR4 PF3_ADDR3 PF2_ADDR2 PF1_ADDR1 PFO_ADDR0

ON_OFF

A(7) A(6) A(5) A(4) A(3) A(2) A(1) A(0)

NC NC

49 50 51 52 53 54 55 56

SW_B + R420 5V C420 .01uF 200K 1% R421 100K 1% SW_B+ C447 0.1uF

28 VDD A0 A1 U403 A2 A3 NU A4 SRAM A5 A6 D1 A7 D2 A8 D3 A9 D4 A10 D5 D6 A11 D7 A12 A13 D8 A14 10 9 8 7 6 5 4 3 25 24 21 23 2 26 1 A(0) A(1) A(2) A(3) A(4) A(5) A(6) A(7) A(8) A(9) A(10) A(11) A(12) A(13) A(14) 4

1 6 2 3

Q440-1

5 R440 4.7K R441 4.7K

AT49LV001N_70VI

D(0) D(1) D(2) D(3) D(4) D(5) D(6) D(7)

21 22 23 25 26 27 28 29

D3_3V

D0 D1 U404 A0 D2 FLASH A1 A2 D3 A3 D4 A4 D5 A5 D6 A6 D7 A7 6 A8 NC A9 A10 A11 A12 A13 A14 A15 A16 GND 24 R432 0 R434 NU

R430 100K D(0) 11 D(1) 12 D(2) 13 D(3) 15 D(4) 16 D(5) 17 D(6) 18 D(7) 19

Q440-2

VOLUME C422 .01uF D424 3V RB520S-30 R424 200K 1% C421 R422 100K R423 100K .01uF R425 100K 1% BATT_DETECT

R442 220 RED LED

R443 120 GREEN LED

D3_3V

D440

BRPY1204W

20 CS 22 OE 27 WE VSS 14

RSSI VO X KEYPAD_CO L KEYPAD_RO W LOCK VS_INT VS_CS OPT_ENA TX_ENA RX_ENA

R433 100K

R431 NU

A(17) A(18)

Microprocessor Circuit Schematic Diagram

Controller Schematics

3-5

R516 C512 6.8pF R512 150K NU C514 16pF R514 100K 5V_A 1 6 R522 100K 2 4 3

R523 10K

Q520

IMX1

Audio

U510-1

LM2904 R511 DEMOD 100K 5V_A R518 220K C511 220pF 2 3 4 C513 220pF 8 1 R513

Q520

C518 6 5 4 8 7 R515 0.1uF C460 0.1uF IMX1

5 VR471 OPT_RX_AUD_SEND_DETECTO R OPT_RX_AUD_RETURN R470 2.2K NC OPT_RX_AUD_SEND_UNMUTED OPT_TX_AUD_FLAT_RETURN R480 0 3V_A

U510-2

LM2904

R521 NU

R520 100K

R519 100K

C519 1uF

R517 OPT_TX_AUD_SEND OPT_TX_AUD_RETURN VS_AUDIO_SEL VS_GAIN_SEL PWR_SET VOX C451 0.1uF C452 0.1uF C453 4.7uF 10 V BW_SEL CH_ACT SQ_DET LSIO HSIO ASFIC_CS SPI_CLK SPI_DATA_OUT C456 0.1uF C457 0.1uF C458 R451 47K 0.1uF NC C455 .022uF 5V_A C454 0.1uF

12 11 10 9 8 7 6 5 4 3 2 1 SQCAP VDDDAC UIO SQIN PLCAP VOX DACG DACR DACU GND A DISC VDDA

R472 680 C470 0.1uF D471 VR472 R471 2.2K NC 5V 2

4 5

R473 680

C461 3V_A 1000pF

Q472

6 3 C477

Q471

1 2 3 4 6 RESET

3V_A

R460 24K C462 0.1uF R462 24K R464 30K C464

48 NC 47 46 45 44 43 42 41 40 39 38 37 NC

3V C463 0.1uF R463 24K C465 1000pF C471 2.2uF R476 100K C472 0.1uF A_MOD_OUT MOD_OUT C466 NU R479 100K 6 3 2 1 4 5 R475 180K R477 2.2K C467 1200pF R474 330

0.1u F R255 3.9K 1% BATT_CHARGE D470 OPT_MIC BOOT_ENA J471 ACCESSORY CONNECTOR 4 S2

3V_A

0.1uF

PLCAP2 NC VDDSYN SYN F1200 GNDDO GNDD VDDCP VDDD CLK168 GCB3 TXRTN

13 14 15 16 17 18 19 20 21 22 23 24

GCB2 GCB1 GCB0 CHACT SQDET LSIO HSIO CSX CLK DATA GND SYN LCAP

U451

30C53

MICEXT GNDRC MICINT VDDRC TXSND RXRTN AUXTN AUDIO MOD RXSND GCB5 GCB4

Q470

L471 390nH C474 150pF

C473 150pF

NC VR473 20V MMBZ5250B NC VR475 15V MMBZ5245B R478 2.2K C476 C478 C475 .022uF SCI NC VR474 MMBZ5250B 20V J470-1 1 2 MICROPHONE CONNECTOR

5 S4 6 S3 7 S1 2 M2 3 M3 1 M1

EXT_MIC_PTT

25 26 27 28 29 30 31 32 33 34 35 36

SW_B+ C493 1000pF R494 C494 330K 2.2uF

.022uF 150pF

J491-1 INTERNAL SPEAKER 1 2

3V 3V VHF R513 R515 R516 R517 Not Placed Not Placed Not Placed 0 UHF 100k 0 Not Placed Not Placed 5V

3V_A E451

16_8_MHZ Not_Placed:NU BK1005HM471 C459 F1200 Not_Placed:NU R481 100K 0.1uF 5V_ B E452 BK1005HM471 5V E453 BK1005HM471 5V_A 2 C497 0.1uF R486 100K Not_Placed:NU uP_CLK 5V_B Not_Placed:NU R482 330K 5V_B 2 3 4 LM2904 Not_Placed:NU 8 R484 2.2K Not_Placed:NU C484 Not_Placed:NU .033uF R485 100K 1 3 R487 0 C483 0.1uF R493 330K DC Level 0.3 - 0.4 V low Supply = 7.42 1/2 Supply = 3.22 1 3 2 4 C479 150pF C492 10uF 6

VCC

C488 470pF

C480 0.1uF

R469 3 J491-3 10 4 J491-4

C499 82pF

TDA854

MODE 5 INPOS OUTNEG SVR OUTPOS 8 INNEG GN D

U490

C481 .01uF

C482 .01uF

R491 0

R492 24K

C489 1 470pF R497 1MEG Not_Placed:NU R499 270K Not_Placed:NU R489 91K Not_Placed:NU C496 1uF R496 10K Not_Placed:NU

Not:Placed:NU 3 R483 150K Not_Placed:NU

U480-1

Q481

Not_Placed:NU 1

R490 2.2K Not_Placed:NU

Q482

2

5V_B

Q490

UMG5 1 5V_B 2 3 R488 330K 4 6

Not_Placed:NU

R498

D491 7

8 4

6 5

U511

UMG5 1 2 3 4 R495 5.6K C498 1uF 6

C495 1uF

47 K NC Not_Placed:NU

LM2904 Not_Placed:NU

U480-2

C490 470pF

Audio Circuit Schematic Diagram

3-6

Controller Schematics

DC Regulation

USWB+ J301 POS NEG DATA F301 VR301 MMBZ5250B C301 390pF NC 20V D301 C303 33uF C304 .01uF

U310

TK71750S 1 VIN 5 VOUT 3 CTRL 4 BYPASS GND 2 C310 .01uF 5V C311 .018uF C312 10uF C313 .01uF

3A

Q311

D3_3V 5R C314 1200pF R310 100K

BATT_CHARGE C302 390pF C305 100pF C306 .01uF

VR302 MMBZ5250B NC 20V RX_ENA R313 10K R312 20K

Q313

C315 1200pF

TP302 TX_ENA R311 100K

Q312

5T

D3_3V

R506 100

S444 SWITCH 3 HIGH 4 2 1 TAB1 TAB2 LOW 5 SWB+ R508 100K

Q493

2 3 R509 100K C323 R322 100K 6 LP2986 4 INPUT OUTPUT 5 8 SHUTDOW N 3 SENSE ERROR 7 6 TAP FEEDBACK 2

GND

C316 1200pF

VOLUME

RESET

R507 100

150pF D3_3V D3_3V

Q494

R510 330K 2 3 NC NC 4 1

U320

C320 .018uF

C321 R320 330K 1% 10uF

C322 .01uF

ON_OFF

R321 200K 1%

U330

TK71730S 1 VIN VOUT 5 3 CTRL 4 BYPASS GND 2 3V C334 10uF C333 .01uF

C331 .01uF

DC Regulation Schematic Diagram

Controller Schematics

3-7

C2 28 g2 R9

D1 D8 D6 D4 D11

C4

C5

C7 1 C8 C1

J2

g1

R5 R11 C6 C3

G2

J1 G1

R10

R6 R1 R2 R7

D9

R8

D7 D5 D3 D10

R15 R14 R13 R12 R3

D2

R4

Component Side

Solder Side

Keypad Board PCB No.8466565A01_O

3-8

Controller Schematics

J2 MAIN BOARD CONNECTOR J2-9 J2-16 J2-17 J2-10 J2-1 J2-2 J2-3 J2-4 J2-6 J2-13 J2-14 J2-15 J2-18 J2-19 J2-12 J2-21 J2-22 J2-23 J2-24 J2-25 J2-26 J2-27 J2-5 J2-7 J2-8 J2-2 J2-11 J2-20 9 16 17 10 1 2 3 4 6 13 14 15 18 19 12 21 22 23 24 25 26 27 5 7 8 8 11 20

LEDBL

KEYPAD

DATA CLK LCD_SEL Vddd

J1 DISPLAY MODULE CONNECTOR

LEDBL 9 8 7 6 5 4 3 2 1 J1-9 J1-8 J1-7 J1-6 J1-5 J1-4 J1-3 J1-2 J1-1 LEDBL GND GND GND DATA CLK LCD_SEL GND VDDD

NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC

C1 150pF DNF

C3 150pF DNF

C6 150pF DNF

C8 150pF DNF

Vddd R1 100K

Vddd R6 100K R7 13K R8 22 K R9 43 K R10 130K

Vddd

G1 J1-10 GND G2 J1-11 GND

C2 150pF

C4 0.1uF R2 13 K S18 SWITCH 1 1 2 3 R3 22 K S17 SWITCH 2 1 2 3 S19 SWITCH 3 1 2 3 S20 SWITCH UP

COL ROW C5 150pF DNF C7 150pF DNF

NC

1 2 3

J2-29 G1 J2-30 G2

REF C1 C3 C6 C8 R9 R10 R2 R3 R4 R5 C5 C7 D3 D4 D5 D6 D7 D8 R13 R14 R15

STD NOT PLACED NOT PLACED NOT PLACED NOT PLACED

LIMITED KEYPAD NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED R5 130K S2 5 SWITCH 8 1 2 3 S26 SWITCH 9 1 2 3 S2 7 SWITCH 0 1 2 3 S28 SWITCH 1 2 3 R4 43K S24 SWITCH 4 1 2 3 S2 3 SWITCH 5 1 2 3 S2 2 SWITCH 6 1 2 3 S21 SWITCH 7 1 2 3

NOT PLACED NOT PLACED

NOT PLACED NOT PLACED LEDBL NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NOT PLACED NC S3 0 SWITCH DOW N 1 2 3 S31 SWITCH F1 1 2 3 S32 SWITCH F2 1 2 3 S2 9 SWITCH # 1 2 3

D10 QSMG-H799 R11 470

QSMG-H799 D2 QSMG-H799 D11

D9

D3 QSMG-H799

D5 QSMG-H799 D6 QSMG-H799 R14 330

D7 QSMG-H799 D8 QSMG-H799 R15 33 0

D1 QSMG-H799

D4 QSMG-H799 R1 3 330

NC

NC

QSMG-H799 R12 470

Keypad Board Schematic Diagram

Keypad Board Parts List 8466565A01-O

3-9

3.0

Keypad Board Parts List 8466565A01-O

Motorola Part No.

NOTPLACED 2113740F55 NOTPLACED 2113743E20 NOTPLACED NOTPLACED NOTPLACED NOTPLACED 4809496B11 4809496B11 NOTPLACED NOTPLACED NOTPLACED NOTPLACED NOTPLACED NOTPLACED 4809496B11 4809496B11 4809496B11 0986632Z01 0909059E18 0662057A97 NOTPLACED NOTPLACED NOTPLACED NOTPLACED 0662057A97 0662057A76 0662057A81 NOTPLACED NOTPLACED 0662057A41 0662057A41 NOTPLACED NOTPLACED NOTPLACED

MK1 1

Circuit Ref

C1 C2 C3 C4 C5 C6 C7 C8 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 J1 J2 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R14 R15

Description

CAP, 150pF CAP, 150pF CAP, 150pF CAP, 0.1uF CAP, 150pF CAP, 150pF CAP, 150pF CAP, 150pF QSMG-H799 QSMG-H799 QSMG-H799 QSMG-H799 QSMG-H799 QSMG-H799 QSMG-H799 QSMG-H799 QSMG-H799 QSMG-H799 QSMG-H799 CONN_J CONN_J RES, 100K RES, 13K RES, 22K RES, 43K RES, 130K RES, 100K RES, 13K RES, 22K RES, 43K RES, 130K RES, 470 RES, 470 RES, 330 RES, 330 RES, 330

2

MATES WITH J470 ON RADIO BOARD

SP1 1 2

MATES WITH J491 ON RADIO BOARD

Reference Designator

MK1 SP1

Motorola Part No.

5085880L01 5085738Z08

Description

Microphone, electret Speaker assembly with connector

Speaker/Microphone Schematic Diagram and Parts List

3-10

Keypad Board Parts List 8466565A01-O

You might also like

- TH-K2AT/K2E/K2ET: Service ManualDocument63 pagesTH-K2AT/K2E/K2ET: Service ManualRds Comunicaciones EirlNo ratings yet

- TH-K2AT/K2E/K2ET: Service ManualDocument63 pagesTH-K2AT/K2E/K2ET: Service ManualRds Comunicaciones EirlNo ratings yet

- 70cm Collinear AntennaDocument3 pages70cm Collinear AntennaRds Comunicaciones EirlNo ratings yet

- Manual VX 2100 2200Document58 pagesManual VX 2100 2200Julia CortésNo ratings yet

- XPR 7550e XPR 7580e XPR 7350e XPR 7380e Mototrbo™ Portable: Detailed Service ManualDocument205 pagesXPR 7550e XPR 7580e XPR 7350e XPR 7380e Mototrbo™ Portable: Detailed Service ManualRds Comunicaciones Eirl50% (2)

- VX 261 Product Sheet 3Document2 pagesVX 261 Product Sheet 3Rds Comunicaciones EirlNo ratings yet

- GX1000SDocument68 pagesGX1000SRds Comunicaciones EirlNo ratings yet

- DEP450 Detailed LACR Service ManualDocument96 pagesDEP450 Detailed LACR Service ManualRds Comunicaciones Eirl56% (9)

- VX 261 Product Sheet 3Document2 pagesVX 261 Product Sheet 3Rds Comunicaciones EirlNo ratings yet

- Icom IC 718 Instruction ManualDocument62 pagesIcom IC 718 Instruction ManualYayok S. Anggoro100% (1)

- Yaesu VX 2000v Service ManualDocument59 pagesYaesu VX 2000v Service ManualDennis LeeNo ratings yet

- 90C05-C HLN9742 FlashAdapterDocument7 pages90C05-C HLN9742 FlashAdapterRds Comunicaciones EirlNo ratings yet

- O - Basic Service Manual PDFDocument98 pagesO - Basic Service Manual PDFRds Comunicaciones EirlNo ratings yet

- Sec4 UHF1 PDFDocument46 pagesSec4 UHF1 PDFRds Comunicaciones EirlNo ratings yet

- Sec5 UHF2 PDFDocument46 pagesSec5 UHF2 PDFRds Comunicaciones EirlNo ratings yet

- Sec4 UHF1 PDFDocument46 pagesSec4 UHF1 PDFRds Comunicaciones EirlNo ratings yet

- CP100 Series - DSM - 50D20 PDFDocument4 pagesCP100 Series - DSM - 50D20 PDFRds Comunicaciones EirlNo ratings yet

- Sec1 Service - Maint PDFDocument20 pagesSec1 Service - Maint PDFRds Comunicaciones EirlNo ratings yet

- Sec3 VHF PDFDocument46 pagesSec3 VHF PDFRds Comunicaciones EirlNo ratings yet

- Ft-250r Service ManualDocument33 pagesFt-250r Service ManualRds Comunicaciones EirlNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- KFD2-STC4-Ex1: SMART Transmitter Power SupplyDocument3 pagesKFD2-STC4-Ex1: SMART Transmitter Power SupplyEAlonso Castro MogollonNo ratings yet

- EE 201 Voltage/current Dividers - 1Document13 pagesEE 201 Voltage/current Dividers - 1bagru baafNo ratings yet

- DIGPRA2 Prac Tutorial Prac1Document10 pagesDIGPRA2 Prac Tutorial Prac1SBUSISONo ratings yet

- Another Look at Reflections: By: M. Walter Maxwell, W2DU/W8HKKDocument68 pagesAnother Look at Reflections: By: M. Walter Maxwell, W2DU/W8HKKgamatqm1No ratings yet

- Altera Component CreationDocument3 pagesAltera Component Creationfran0772No ratings yet

- Install PL7 on Windows 7 using XP ModeDocument2 pagesInstall PL7 on Windows 7 using XP ModesyeadtalhaaliNo ratings yet

- LB91B 47lh50ydDocument66 pagesLB91B 47lh50ydMaiaraFirminoNo ratings yet

- Fujitsu Siemens E8020D ManualDocument143 pagesFujitsu Siemens E8020D ManualPaul KupasNo ratings yet

- Roland/BOSS Products AC Adaptor InformationDocument4 pagesRoland/BOSS Products AC Adaptor InformationCristian Daniel ChelariuNo ratings yet

- LT Spice ExperimentsDocument15 pagesLT Spice ExperimentsSachin George ThomasNo ratings yet

- LAN TopologiesDocument31 pagesLAN TopologiesDinku Minda100% (1)

- LTC135 DS en V04Document2 pagesLTC135 DS en V04Nirmal mehtaNo ratings yet

- KRC4-Optional Interfaces enDocument99 pagesKRC4-Optional Interfaces encabecavil100% (2)

- Pro-Ject Essential/Phono USB: Instructions For UseDocument8 pagesPro-Ject Essential/Phono USB: Instructions For UseAleksandar KeracNo ratings yet

- HAVSO2S0022GSMDocument2 pagesHAVSO2S0022GSMNISHANNo ratings yet

- Design and Simulation of 80 KHZ High Frequency Converter Using CD 4047IC CMOSDocument6 pagesDesign and Simulation of 80 KHZ High Frequency Converter Using CD 4047IC CMOSEditor IJTSRD100% (1)

- Multiple Choice Questions For Electronics Engineering Part 1Document4 pagesMultiple Choice Questions For Electronics Engineering Part 1Anshad100% (1)

- Datasheet IT8512E F V0.4.1Document335 pagesDatasheet IT8512E F V0.4.1Krzysztof BondkaNo ratings yet

- Instruction Format PDFDocument5 pagesInstruction Format PDFG.SAIDULUNo ratings yet

- BTS Cell Down Blocked Hardware Transmission Clock AlarmsDocument2 pagesBTS Cell Down Blocked Hardware Transmission Clock AlarmsMawan MehindriNo ratings yet

- Digital System Design Syllabus For EC 3 Sem 2018 Scheme - VTU CBCS 18EC34 SyllabusDocument2 pagesDigital System Design Syllabus For EC 3 Sem 2018 Scheme - VTU CBCS 18EC34 SyllabusSYAMALA100% (1)

- Chapter 3-Diodes Rectifiers: 180 V, R 15, F 60 HZDocument31 pagesChapter 3-Diodes Rectifiers: 180 V, R 15, F 60 HZAbd Alkader AlwerNo ratings yet

- 80 Watt KU Band BUC ManualDocument53 pages80 Watt KU Band BUC ManualspeedyeduNo ratings yet

- Vol Stability SlidesDocument28 pagesVol Stability SlidessanthoshyeruvakaNo ratings yet

- FLEX 5000 Modules Specifications PDFDocument112 pagesFLEX 5000 Modules Specifications PDFFederico Franchino100% (1)

- Fan7930b 92897Document23 pagesFan7930b 92897VinhNo ratings yet

- 8086 Microprocessor TrainersDocument5 pages8086 Microprocessor TrainersMarija KalendarNo ratings yet

- BS Au 265-2-1995 (2000) Iso 6518-2-1995 PDFDocument16 pagesBS Au 265-2-1995 (2000) Iso 6518-2-1995 PDFamerNo ratings yet

- WPA-80090/8CF - : Mechanical SpecificationsDocument1 pageWPA-80090/8CF - : Mechanical Specificationsmiguelona1304No ratings yet

- Test Setup Checks Transistors' hFEs When Tight Control Is Important /TITLEDocument6 pagesTest Setup Checks Transistors' hFEs When Tight Control Is Important /TITLEjvs57No ratings yet