Professional Documents

Culture Documents

No Main 1 Footprint Checklist

Uploaded by

izzati_2607Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

No Main 1 Footprint Checklist

Uploaded by

izzati_2607Copyright:

Available Formats

No Main 1 Footprint

Sub

Description Generate the PCB footprints from PCB library. Check the footprint is match with actual sample. Check the footprint match part mechanical specification. Check holes with enough tolerance for connector pins. Check PTH hole is reserved and with enough tolerance for component guide pins. Check NPTH hole is un-plated Check that the pin number of the footprint is numbered according to the component specification. There must have the polarity indication (+ sign) for the polarize component such as LED, diode or electrolytic capacitor. Make sure pin 1 of IC is clearly indicated and not confuse with other nearby labeling. For IC, use triangle instead of dot as pin "1". For capacitor, use plus " + " as indicator. The size overlay track width and length, pls follow as in the comment. Check the pin orientation of transistor and MOSFET sometimes easily confused. Consider the footprint pad length/size for rework.

Comment

20120919 meeting suggest to use triangle as pin1.

Example: the Zener diode pad is meet the recommended footprint. But it is very hard for rework purpose.

Fiducial pad

Make sure the fiducial pad is place at the both corner of the BGA or IC and Make sure the pad is unpaste (diagonal corner of pin 1) Check the minimum track width, hole, annular ring thickness, and thermal break whether is set. It should not less than PCB manufacturer specification. Min. track width = 0.2mm Min. VIA hole diameter = 0.2mm Min. annular ring thickness = 0.15mm min. distance between track/pad/via to the board edge is met. Min = 0.254mm Check the minimum track width, hole, annular ring thickness, and thermal break whether is set. It should not less than PCB manufacturer specification. Min. track width = 0.15mm Min. VIA hole diameter = 0.25mm Min. annular ring thickness = 0.15mm Min. distance between track/pad/via to the board edge is met: 0.254mm NPTH to conductive area spacing at least 0.254mm 1. Routing a. Clearance Rule b. Routing Via-Style Rule c. Max-Min Width Rule 2. Manufacturing a. Minimum Annular Ring b. Hole Size Constraint c. Polygon Connect Style 3. Other a. Short Circuit Constraint b. Un-Routed Net Constraint Check that thermal break is set between polygon and pad with the same net name. Check that the number of layer on the PCB is done as according to the layer stack. Check that the drill hole pairs are assign according to the specification of the PCB manufacturer. (Blind via)

Pre-route

Design Rules

Layer Stack Manager

Stack holes

Make sure there are at least 2-4 stack holes at the corner of PCB. The stack hole shall meet the manufacturer requirement. Stack hole diameter = 2.5mm One of the stack holes is set as the origin and all the stack hole shall be label with coordinate. Set the Origin at one of the Stack hole. Min 2 fiducial that place diagonally the edge of PCB. (Optional: place the fiducial at the 4 corner of PCB panel). Dont save file name too long, it will cause some error when generating DRC report and etc. Always use minimum 1.6mm except there is a requirement on the PCB to be 1mm.

For TestPoint Jig.

For TestPoint Jig.

Fiducial FileName PCB Thickness

If the PCB is 1mm, an extra jig need to be made in order to match the thickness for the PCB on the conveyer.

3 Component Connector Placement

Check the footprint for each connector on the board. Ensure that the correct footprint and pitch size is used. Make sure the connectors pin assignment/polarity are match with the connected device/connector, especially the FFC connector (sometime the pin 1 signal not necessary connected to the pin 1 of connector). Verify the FFC connector should be lower or upper contact type it affects the pin 1 location. Placement of component must be aligned with other components either horizontally or vertically The connector unconnected pad/soldering pad should connect to the GROUND. make sure the components pin orientation is match with SCH.

Relay footprint pin orientation is very weird and the schematic is needed to be checked that it should match the footprint

Placment

Check the Z-height constraint on the PCB. Keep some distance between high and low profile components for rework purpose. Decoupling cap is placed as close as possible to the components. Make sure the decoupling cap is placed to the right IC. Make sure the connectors are at the right location.

Only one side of the PCB have the through hole components. TH hole components (cap/header) polarity should be in the same direction. Avoid the chip overlap EXACTLY to each others on top and bottom side. Make sure all the capacitors and resistors are at the right source/destination components. Make sure the component to component spacing have enough space. **pls refer to **refer: ISITO Board Design Guidelines_component spacing.pdf for more information. For reflow process: 0603 to 0603 pad edge to pad edge = 0.635mm (25mil) Wave process: 0603 to 0603 pad edge to pad edge = 1.27mm (50mil) Wave soldering process need more space is there is smt component, pls refer to ISITO Board Design Guidelines_component spacing.pdf to check the spacing. component side Overlay center line to center line of conveyed edge: 0.75mm Layer Tab with layer numbering. BKM: imidiate route short track n punch via for used nets. To avoid no place to punch via when doing the routing.

TH components is placed manually by people. This is to minimize the human error issue.

component to component distance

**refer: **refer: ISITO Board Design Guidelines_component spacing.pdf **refer: ISITO Board Design Guidelines_component spacing.pdf **refer: ISITO Board Design Guidelines_component spacing.pdf

refer HRT300-SCR-MAXQ-V1-R1

BKM

High Speed Signals

Diff. Pair

Start to route HighSpeed signals first before start route others normal signals. High speed signals need to be routed: a. as short as possible. b. no Stub. c. don't cross other highspeed signal at adjacent plane . d. don't cross noisy area. Ex: Crystal or switching Vreg. e. minimize transition via as much as possible. (connector pin counted as 1 transition via.) Top priority reference plane is GND. Check the shielded signal. Eg. Clock, audio and high speed signal . Make sure the high speed signals don't cross the split plane. If it must cross the split plane, use the stiching capacitor beside the split plane. Differential pair must be routed in pair or side-by-side with the width/spacing that set by PCB vendor. Put a ground Via around the differential pair when they change to others layer. The diff pair reference plane should not break or cross the split plane. Leave space at least 0.508mm air gap distance for differential pair to others signals. Matching the track length in proper way as in comment figure.

Tuning

For more information pls refer: a. High Speed USB Platform Design Guidelines.pdf b. Board design guideline for PCIE architecture.pdf

Busses

1. Use the same layer to branch out the same buses or same differential pair. Ex: Tx at same layer and all RX at another same layer.

Normal Routing

POWER/GND BKM Power Plane Polygon

No less that 90 degree angle track (for power and GND signal) Avoid T or X connection on track connection unless VIA/pad is used Don't route unnecessary bending of track Connect the track to the center of pad (especially square pad) Via hole must be set to tending - precaution: If use * instead of PlaceVia, the via will NOT be tenting Component pad close to each other and of the same net should not be connected using thick track especially the GND and Power pin to avoid the thermal distribution during soldering. Put vertical track as one layer (ex. Top layer) and horizontal track as another layer (ex. Bottom layer) for a two layer board Add via at the thermal pad of footprint. Min track width is 0.6mm or equal to pad size. BKM: Route top layer in horizontal and bottom layer in vertical or vice versa. Double click on each polygon (if any). Check that the grip size is 0.2mm and the track size is 0.254mm. Grip size = 0.2mm Track size = 0.254mm Check visually that there are thermal break between the connected pads and polygon. The thermal break clearance shall be generated according to manufacturer specification. Expected thermal break clearance = 0.254mm Actual thermal break clearance = 0.3mm Check whether the via is breaking or create the botttom neck at the GND or Power plane. Consult with Design Engineer the current load for each Power net and calculate the suitable track/plane width for each Power net. BKM: use 2x(calcualted track width0) to route the trac k or plane. Enough vias for power to flow from one layer to another layer. One (0.508mmpad&0.254mmhole) via can draw around 1.5A. Double check the overlap polygon, sometime the polygon is void by another polygon as shown in the commnet photo. Enough thermal plane for PWR dissipation plane?

DFT

Put more GND test point for test jig development Make sure the test point of some critical signal is available for testing. Obtain a list of test point from design engineer. Top paste for all test point should be unmask both in PCB and Lib. The generated Lib should be unmasked too.

Make sure some open pin from BGA IC is tied out as test point. Make sure the test point is labeled with designator. Generate the test point list for testing reference. Make sure the TestPoint footprint is set as TestPoint Bottom. No testpoint under the components. Labeling/Over lay Check that the PCB name, revision number, and the fabrication date on the PCB silk screen are label accordingly. Check that no Overlay on pad. Check that all silk screens on the top layer are not mirrored and all silk screens on the bottom layer are mirrored. Make sure all components are designated, and the designator shall be placed clearly next to the particular component. Make sure the designator not covered by component after soldering. Make sure the pin1 indicator is on via or covered by components. For small component (0603,0805)Refdes size, Height: 0.6mm, Width:0.1mm For Big component (connector, Jumper) Height: 1mm, Width:0.15mm Place Refdes in 0degree(read from Right to Left) or 90degree(read from North to South) only. Make sure those gold contact pad is un-paste. Eg. battery contact and antenna contact Make the solder mask for fine-pitch pad set to manufacturer minimum spec Solder mask override = 0.075mm Check the polarity of footprint is matching the schematic?? Example for LED in schematic, pin1 is cathode but in footprint pin1 is anode. check the diff pair track width and spacing. Refresh all the polygons. Run the DRC. Make sure no errors to be encountered unless there are acceptable known constraints. The result of the DRC shall be printed and filed. All Via are tenting. Recheck the important Connector Coordinate before tape out. Check the Product_Name and Date on PCB is correct. TopOverlay pin1 indicator is not on via. Check dangling via. Check dangling track. Double check the overlap polygon, sometime the polygon is void by another polygon as shown in the commnet photo.

Others

Finalize Single board Brd

Panelize/

Panelize board

BKM

Origin at the fiducial, place Origin(0,0) OverlayTop. For multipack, the Refdesignator is same for all duplicated PCB. Check the PCB and gerber file that all PCB are copied exactly same. Put the panel DIMENSION. The outrigger NPTH need to be 5mm from NPTH edge to outrigger edge. (need to revise) The center of fiducial to outrigger board edge need at least 3mm. BKM: Use copy , then EDIT-PasteSpecial -> copy refignator, paste special. Remember to change Document>Option>SnapX&SnapY to 0.001mm in order to paste acurrately the new duplicated brd.

20120925: requested by ISITO (You BH) 20120930: email reply by Ikhwan ISITO

Gerber

Before tape out

Make sure the put the legend on Drill drawing layer

**To add a Drill Table to the Gerber File you have to Place the String ".LEGEND" on the Drill Drawing Layer.

BKM Generate CAM files

Check the size and dimension of the PCB. It should be as specified. Dimension = 98.2mm (X) x 80.8mm (Y) Check product name and Revision on the the Drawing table. For Prototype PCB, the soldermask color is RED. And for Mass production PCB, the soldermask color is GREEN. If unsure on soldermask/solderPaste is open/closed, pls generate gerber and review the gerber files. .pcb file_name too long will cause error on generating gerber file, I did test and error on PicknPlace file. (Max= 22characters)

Check all layers Gerber has been generated. Example for 4layers board: file_name.REP file_name.GTL (Top Layer) file_name.G1 (Middle Layer 1) file_name.G2 (Middle Layer 2) file_name.GBL (Bottom Layer) file_name.GM1 (Mechanical 1) file_name.GM3 (Mechanical 3) file_name.GTO (Top Overlay) file_name.GBO (Bottom Overlay) file_name.GTS (Top Soldermask) file_name.GBS (Bottom Soldermask) file_name.GTP (Top Paste) file_name.GBP (Bottom Paste) file_name.GPT (Top Pad Master) file_name.GPB (Bottom Pad Master) file_name.GG1 (Drill Guide) file_name.GD1 (Drill Drawing) -- got the ABCD location of drill and Drill Legend. 'NC Drill Output ' file_name.DDR file_name.DRL file_name.txt 'Pick Place Output 1' Pick Place for file_name.txt Status Report.txt PCB Spec.txt

Open the Gerber file with CAM manager and make sure the layout is correct (beware of mechanical layer which will appear at every layer) Check the Readme.txt/PCB_Spec.txt has been included and describes the boards fabrication requirement details. Check the StackMark.txt is included in the files to be sent.

KingCredie PCB capability

min. Outer Track width min. Inner Track width (0.5Oz) min. PTH size

min OUter PTH_annular_ring min Inner_PTH_annular_ring min. space for Inner_track_edge to Conductive : min. space for Outer_track_edge to Conductive : min. space for track_edge to PTH_annular_ring_edge. min. space for Outer_track_edge to Pad_edge: min. space for track_edge to Polygon_edge. min. space between PTH_annular_ring_edge to PTH_annular_ring_edge. min. space between PTH_annular_ring_edge to Pad_edge. min. space between PTH_annular_ring_edge to Polygon_edge. min. space between NPTH_edge to conductive: min. space between Pad_edge to Polygon_edge.

You might also like

- SMT Manufacturability Design GuidelinesDocument25 pagesSMT Manufacturability Design GuidelinespcbppcNo ratings yet

- Design Rules Selective SolderingDocument20 pagesDesign Rules Selective SolderingemirNo ratings yet

- Printed Circuit Board (PCB) Design ChecklistDocument4 pagesPrinted Circuit Board (PCB) Design ChecklistQuickteck100% (1)

- SMT Manufacturability Design GuidelinesDocument25 pagesSMT Manufacturability Design Guidelinesizzati_2607100% (1)

- Repair Manual Rev 0 6Document28 pagesRepair Manual Rev 0 6Bob WettermannNo ratings yet

- Design Guidelines for Surface Mount TechnologyFrom EverandDesign Guidelines for Surface Mount TechnologyRating: 5 out of 5 stars5/5 (1)

- 4412A Amendment 1 (3 07)Document7 pages4412A Amendment 1 (3 07)Aani MazharNo ratings yet

- Solder Paste Printing Process - Surface Mount ProcessDocument5 pagesSolder Paste Printing Process - Surface Mount ProcessMike HHNo ratings yet

- PCB Design ProcessDocument31 pagesPCB Design ProcessMallappa PatilNo ratings yet

- SMT and Through Hole DFM GuidelinesDocument30 pagesSMT and Through Hole DFM Guidelinessmtdrkd100% (5)

- Manufacturing Process Data Management: IPC 175X Schema Version 2.0Document36 pagesManufacturing Process Data Management: IPC 175X Schema Version 2.0Vitalii SkrypnykNo ratings yet

- IPC-9850 Standard for Surface Mount Equipment CharacterizationDocument56 pagesIPC-9850 Standard for Surface Mount Equipment CharacterizationCarlos Mascioni100% (1)

- Nasa - Workmanship Standard For Surface Mount Technology - Nasa Technical Standard - Nasa-Std-8739.2 - ManualDocument84 pagesNasa - Workmanship Standard For Surface Mount Technology - Nasa Technical Standard - Nasa-Std-8739.2 - Manualhbpr9999100% (1)

- Introduction To PCBDocument15 pagesIntroduction To PCBdileepanme100% (2)

- Board Design Guidelines 2003 Rev-ADocument53 pagesBoard Design Guidelines 2003 Rev-Agre_test_takerNo ratings yet

- High Speed PCB LayoutDocument41 pagesHigh Speed PCB Layoutizzati_2607No ratings yet

- Area Ratio and Stencil Thickness CalculatorDocument6 pagesArea Ratio and Stencil Thickness Calculatorsmtdrkd100% (1)

- PCB Surface Finishes Presentation by MultekDocument54 pagesPCB Surface Finishes Presentation by Multeksmtdrkd100% (1)

- SOLDER PASTE STENCIL DESIGN GUIDEDocument17 pagesSOLDER PASTE STENCIL DESIGN GUIDEedwin100% (1)

- IPC 1720a-1stq-2010Document48 pagesIPC 1720a-1stq-2010BuiTrungNo ratings yet

- DFM GuidelinesDocument58 pagesDFM Guidelinesjav_ra993986No ratings yet

- SMT Process EngineeringDocument4 pagesSMT Process Engineeringshaktiss24_147930359No ratings yet

- IPC Industry MappingDocument47 pagesIPC Industry MappingleandrokamargoNo ratings yet

- Ipc 6013aDocument10 pagesIpc 6013abenmen73No ratings yet

- Aoi SMD As Per Ipc-A-610Document7 pagesAoi SMD As Per Ipc-A-610Satadal GuptaNo ratings yet

- IPC PCB Assembly TroubleshootingDocument391 pagesIPC PCB Assembly Troubleshootingvural100% (4)

- Introduction to Embedded Hardware DesignDocument74 pagesIntroduction to Embedded Hardware DesignNagaraju Upputuri100% (1)

- Solder Criteris IPC-610GDocument17 pagesSolder Criteris IPC-610GUbaldo JuarezNo ratings yet

- Technical Note TN - 166 FTDI Example IC PCB FootprintsDocument46 pagesTechnical Note TN - 166 FTDI Example IC PCB FootprintsSteve SmithNo ratings yet

- PCB Design TipsDocument29 pagesPCB Design Tipsizzati_2607No ratings yet

- SMT Troubleshooting GuideDocument20 pagesSMT Troubleshooting Guidedbuschel100% (2)

- IPC Standards TreeDocument1 pageIPC Standards TreeShafiq IsmathullakhanNo ratings yet

- Gerber File CreationDocument44 pagesGerber File CreationBatka Shankar100% (2)

- Design For AssemblyDocument19 pagesDesign For AssemblyJavierNo ratings yet

- SMT Generic Control PlanDocument2 pagesSMT Generic Control Plansmtdrkd81% (21)

- Requirements For Soldered Electrical and Electronic AssembliesDocument6 pagesRequirements For Soldered Electrical and Electronic AssembliesVenkateswaran venkateswaran50% (4)

- DRM-53 - Electronics Assembly Reference Guide - SampleDocument17 pagesDRM-53 - Electronics Assembly Reference Guide - SampleDjefferson Morais100% (1)

- PCB Failures Webinar: Causes & CuresDocument63 pagesPCB Failures Webinar: Causes & CuresNirud PajanustanNo ratings yet

- DLA-X3-xx - XC380-xx - X7-xx - XC780-xx - X9-xx - XC980-xx (SCH)Document36 pagesDLA-X3-xx - XC380-xx - X7-xx - XC780-xx - X9-xx - XC980-xx (SCH)ixigen2115No ratings yet

- Solder Filet and StencilDocument150 pagesSolder Filet and StencilKojOT88No ratings yet

- Ipc A 600H 2010Document36 pagesIpc A 600H 2010madslayersNo ratings yet

- Process Mapping in SMD AssemblyDocument1 pageProcess Mapping in SMD Assemblysmtdrkd100% (2)

- Signal Integrity Analysis GuidelinesDocument47 pagesSignal Integrity Analysis Guidelinesswathikomati7870No ratings yet

- Printed Circuit Board: Presented by Ruby Kumari B.SC (MATHS), B.E (ECE)Document75 pagesPrinted Circuit Board: Presented by Ruby Kumari B.SC (MATHS), B.E (ECE)Ruby Pathak100% (2)

- PCB Concepts GuideDocument296 pagesPCB Concepts GuideAli Ahmad100% (1)

- 001 B Operator TrainingDocument129 pages001 B Operator TrainingWandyy GonçalvesNo ratings yet

- Qualification Testing For PCB PDFDocument48 pagesQualification Testing For PCB PDFSempreInterNo ratings yet

- IPC A 600 Revision EDocument49 pagesIPC A 600 Revision EDotrung KienNo ratings yet

- PCB Designing Fundamentals GuideDocument42 pagesPCB Designing Fundamentals GuideChintaan PatelNo ratings yet

- Ipc 2226Document63 pagesIpc 2226Benyamin Farzaneh AghajarieNo ratings yet

- DFX GuidelinesDocument95 pagesDFX GuidelinesAkash VermaNo ratings yet

- 7711-21B Change 1 PDFDocument20 pages7711-21B Change 1 PDFAkbar BaharuddinNo ratings yet

- PCB DFM V1.1 PDFDocument43 pagesPCB DFM V1.1 PDFAbster1No ratings yet

- SMT Process GudeDocument46 pagesSMT Process GudeAlessandro CavalieriNo ratings yet

- Stencil Printing PresentationDocument45 pagesStencil Printing Presentationcdsullivan100% (1)

- PCB Design Review - TemplateDocument8 pagesPCB Design Review - TemplatenolanvanNo ratings yet

- PCB Design Presentation: Jakia AfruzDocument33 pagesPCB Design Presentation: Jakia AfruzParth MangukiyaNo ratings yet

- DFM Assembly Guidelines1 PDFDocument25 pagesDFM Assembly Guidelines1 PDFselvakumarNo ratings yet

- High Speed PCB LayoutDocument41 pagesHigh Speed PCB Layoutizzati_2607No ratings yet

- PCB Design TipsDocument29 pagesPCB Design Tipsizzati_2607No ratings yet

- PCB GuideDocument1 pagePCB GuideMallappa PatilNo ratings yet

- Altium DesignerDocument8 pagesAltium Designerizzati_2607No ratings yet

- Final Exam Ausmat 22 2010 AnswerDocument16 pagesFinal Exam Ausmat 22 2010 Answerizzati_2607No ratings yet

- Final Exam AUSMAT 20 IIDocument13 pagesFinal Exam AUSMAT 20 IIizzati_2607No ratings yet

- PMR Mat Bs Trial 16 1Document7 pagesPMR Mat Bs Trial 16 1Maha Letchumy BalakeristananNo ratings yet

- A Model For Cell Growth in Batch BioreactorsDocument128 pagesA Model For Cell Growth in Batch BioreactorsalabastrinoNo ratings yet

- G10 Q1 Health Module 3Document11 pagesG10 Q1 Health Module 3Manuel Rosales Jr.No ratings yet

- Geo Gr9 m2 Sustainable Utilisation ResourcesDocument19 pagesGeo Gr9 m2 Sustainable Utilisation ResourcesEduBoardNo ratings yet

- Self HRMDocument372 pagesSelf HRMSaad NazeerNo ratings yet

- Arrival Notice PDFDocument2 pagesArrival Notice PDFalianzalogicaNo ratings yet

- Causes and Symptoms of Vaginal Bleeding During PregnancyDocument28 pagesCauses and Symptoms of Vaginal Bleeding During PregnancyNurul AnnisaniNo ratings yet

- Medial Collateral Ligament InjuriesDocument14 pagesMedial Collateral Ligament InjuriesosamadrNo ratings yet

- Siemens in Western AustraliaDocument24 pagesSiemens in Western AustraliasstrattonNo ratings yet

- Journal Homepage: - : IntroductionDocument5 pagesJournal Homepage: - : IntroductionIJAR JOURNALNo ratings yet

- Pipe Sizing Formula & Velocity ReferenceDocument3 pagesPipe Sizing Formula & Velocity ReferenceJayakrishnan RadhakrishnanNo ratings yet

- VW Transporter T5 T6 7H - Multivan 7E Multifunction Steering Wheel Retrofit Wiring HarnessDocument13 pagesVW Transporter T5 T6 7H - Multivan 7E Multifunction Steering Wheel Retrofit Wiring HarnessNull100% (1)

- Predictive MaintenanceDocument17 pagesPredictive Maintenancejimmy_d_nasutionNo ratings yet

- Spc42xx 43xx 52xx 53xx 63xx Installation Configuration Manual enDocument296 pagesSpc42xx 43xx 52xx 53xx 63xx Installation Configuration Manual entelecothalesNo ratings yet

- ESP32 Using PWMDocument7 pagesESP32 Using PWMMarcos TrejoNo ratings yet

- Test Suite - DIGSI5Document12 pagesTest Suite - DIGSI5Matija KosNo ratings yet

- Niskama KarmaDocument4 pagesNiskama Karmachitta84No ratings yet

- Jung, Carl Gustav - Volume 9 - The Archetypes of The Collective UnconsciousDocument26 pagesJung, Carl Gustav - Volume 9 - The Archetypes of The Collective UnconsciousKris StarrNo ratings yet

- HPLC Flowmeter Calibration and MaintenanceDocument9 pagesHPLC Flowmeter Calibration and MaintenanceDCG CandyNo ratings yet

- Suplemento de Aero Controlex GroupDocument266 pagesSuplemento de Aero Controlex GroupGerardo CordovaNo ratings yet

- Organic Chemistry 9th Edition Carey Test BankDocument35 pagesOrganic Chemistry 9th Edition Carey Test Bankwool.vegetousbbvz100% (23)

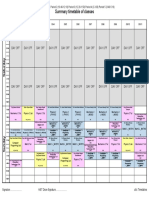

- Class Timetable Summary for Periods 1-5Document14 pagesClass Timetable Summary for Periods 1-5عبدالرحمن فهمي الشريفNo ratings yet

- T B E T P: HE OOK OF Cclesiastes OR HE ReacherDocument16 pagesT B E T P: HE OOK OF Cclesiastes OR HE ReacherDarkillangel Forlorn OmenNo ratings yet

- Baja 2020 RulebookDocument141 pagesBaja 2020 RulebookpranjalNo ratings yet

- Foods Benefit Body SystemDocument25 pagesFoods Benefit Body SystemjayandrewNo ratings yet

- Apex NC Fence OrdinanceDocument28 pagesApex NC Fence OrdinanceKeith BloemendaalNo ratings yet

- Beginner's Guide To Centrifugal Compressor Design and SimulationDocument17 pagesBeginner's Guide To Centrifugal Compressor Design and Simulationvijay_jvNo ratings yet

- Effects of body biasing on low frequency noise in MOSFETsDocument7 pagesEffects of body biasing on low frequency noise in MOSFETsVaibhav RanaNo ratings yet

- GMP Inspection Checklist - قائمة المراجعة (GMP)Document24 pagesGMP Inspection Checklist - قائمة المراجعة (GMP)michael_payne353280% (5)

- Tutorial Sheet 1-Vector CalculusDocument2 pagesTutorial Sheet 1-Vector CalculusNavya JainNo ratings yet

- Floor JansenDocument8 pagesFloor JansenDeyan Ivanov100% (1)