Professional Documents

Culture Documents

UGN3055 Datasheet

Uploaded by

Miguel Angel ReyesOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UGN3055 Datasheet

Uploaded by

Miguel Angel ReyesCopyright:

Available Formats

3055 MULTIPLEXED TWO-WIRE HALL EFFECT SENSOR IC

DISCONTINUED PRODUCT Shown for Reference Only

3055

MULTIPLEXED TWO-WIRE HALL-EFFECT SENSOR ICs

LOGIC

The UGN3055U Hall-effect sensor IC is a digital magnetic sensing IC capable of communicating over a two-wire power/signal bus. Using a sequential addressing scheme, the device responds to a signal on the bus and returns the diagnostic status of the IC, as well as the status of each monitored external magnetic field. As many as 30 devices can function on the same two-wire bus. This IC is ideal for multiple device applications where minimizing the wiring harness size is desirable or essential. The device consists of high-resolution bipolar Hall-effect switching circuitry, the output of which drives high-density CMOS logic stages. These logic stages decode the address pulse and enable a response at the appropriate address. The combination of magnetic-field or switch-status sensing, low-noise amplification of the Hall-transducer output, and high-density decoding and control logic is made possible by the development of a new device BiMOS fabrication technology. This unique magnetic sensing IC operates within specifications between -20C and +85C. Alternate magnetic and temperature specifications are available upon request. It is supplied in a 60 mil (1.54 mm) thick, three-pin plastic SIP. Each package is clearly marked with a two-digit decimal device address (xx).

Data Sheet 27680

GROUND

BUS

Dwg. PH-005

SWITCH IN

Pinning is shown viewed from branded side.

ABSOLUTE MAXIMUM RATINGS at T A = +25 C

Supply Voltage, VBUS ........................... 24 V Magnetic Flux Density, B ............ Unlimited Operating Temperature Range, TA .......................... -20C to +85C

Storage Temperature Range, TS .............................. -55C to +150C Package Power Dissipation, PD .................................... 750 mW

X

3

FEATURES

Complete Multiplexed Hall-Effect IC with Simple Sequential Addressing Protocol Allows Power and Communication Over a Two-Wire Bus (Supply/Signal and Ground) Up to 30 Hall-Effect Devices Can Share a Bus Diagnostic Capabilities Magnetic-Field or Switch-Status Sensing Low Power of BiMOS Technology Favors Battery-Powered and Mobile Applications Ideal for Automotive, Consumer, and Industrial Applications

Always order by complete part number:

UGN3055U .

3055 MULTIPLEXED TWO-WIRE HALL EFFECT SENSOR IC

OPERATIONAL CHARACTERISTIC over operating temperature range.

Electrical Characteristics Power Supply Voltage Signal Current Quiescent Current VBUS = 6 V VBUS = 9 V I QHIQL Address Range Clock Thresholds LOW to HIGH HIGH to LOW Hysteresis Clock Period Address LOW Voltage Address HIGH Voltage Power-On Reset Voltage Settling Time VBUS = 9 V VBUS = 6 V Propagation Delay LOW to HIGH HIGH to LOW Pin 3 Input Resistance No Magnetic Field (VOUT = HIGH) Mag. Field Present (VOUT = LOW) Magnetic Characteristics Magnetic Thresholds *Turn-On Turn-Off Hysteresis (BOPB RP) BOP BRP BHYS 50 -25 0 150 100 50 300 300 75 G G G Limits Symbol VBUS IS IQH IQL IQ Addr VCLH VCHL VCHYS tCLK VL VH VRST th tl tplh tphl ROUTH ROUTL Min. 12 1 6.5 0.1 VRST VCLH 2.5 100 100 10 40 Typ. 15 0.8 1.0 6 9 3.5 Max. 15 20 2.5 2.5 300 30 8.5 VCHL VBUS 5.5 10 75 50 Units V mA mA mA A V V V ms V V V s s s s k

*Alternate magnetic switch point specifications are available on request. Please contact the factory.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 W Copyright 1988, 1991, Allegro MicroSystems, Inc.

3055 MULTIPLEXED TWO-WIRE HALL EFFECT SENSOR IC

( 0.005 [0.13 mm] die placement)

ACTIVE AREA DEPTH 0.015" 0.38 mm

NOM

ELEMENT LOCATION

FUNCTIONAL BLOCK DIAGRAM

1

BUS

0.071" 1.80 mm

REG COMP

0.084" 2.13 mm

COMP

RESET

CLOCK

CMOS LOGIC

A

BRANDED SURFACE 1 2 3

SWITCH IN (OPTIONAL)

2

Dwg. MH-002A

GROUND

Dwg. FH-009

DEFINITION OF TERMS

Device Address Each bus device has a factory-specified predefined address. At present, allowable device addresses are integers from 1 to 30. LOW-to-HlGH Clock Threshold (V CLH) Minimum voltage required during the positive-going transition to increment the bus address and trigger a diagnostic response from the bus devices. This is also the maximum threshold of the on-chip comparator, which monitors the supply voltage, VBUS. HlGH-to-LOW Threshold (VHL) Maximum voltage required during the negative-going transition to trigger a signal current response from the bus devices. This is also the maximum threshold of the onchip comparator, which monitors the supply voltage, VBUS. Bus HIGH Voltage (V H) Bus HIGH voltage required for addressing. Voltage should be greater than VCLH . Address LOW Voltage (VL) Bus LOW Voltage required for addressing. Voltage should be greater than VRST and less than VCHL. Bus Reset Voltage (VRST) Voltage level required to reset individual devices. Device Quiescent Current Drain (I Q) The current drain of bus devices when active but not addressed. IQH is the maximum quiescent current drain when the device is not addressed and is at V H . IQL is the maximum quiescent current drain when the device is not addressed and is at V L. Diagnostic Phase Period on the bus when the address voltage is at VH . During this period, a correctly addressed device responds by increasing its current drain on the bus. This response from the device is called the diagnostic response and the bus current increase is called the diagnostic current. Signal Phase Period on the bus when the address voltage is at VL. During this period, a correctly addressed device that detects a magnetic field greater than magnetic Operate Point, BOP, responds by maintaining a current drain of IS on the bus. This response from the device is called the signal response and the bus current increase is called the signal current. Device Address Response Current (I S) Current returned by the bus devices during the diagnostic and the signal responses of the bus devices. This is accomplished by enabling the constant current source (CCS). Magnetic Operate Point (B OP) Minimum magnetic field required to switch ON the Hall amplifier and switching circuitry of the addressed device. This circuitry is only active when the device is addressed. Magnetic Release Point (B RP) Magnetic field required to switch OFF the Hall amplifier and switching circuitry after the output has switched ON. This is due to magnetic memory in the switching circuitry. However, when a device is deactivated by changing the current bus address, all magnetic memory is lost. Magnetic Hysteresis (BHYS) Difference between the BOP and BRP magnetic field thresholds.

3055 MULTIPLEXED TWO-WIRE HALL EFFECT SENSOR IC

ADDRESSING PROTOCOL The device may be addressed by modulating the supply voltage as shown in Figure 1. A preferred addressing protocol is as follows: the bus supply voltage is brought down to 0V so that all devices on the bus may be reset. The voltage is then raised to the address LOW voltage (V L) and the bus quiescent current is measured. The bus is then toggled between VL and VH (address HIGH voltage), with each positive transition representing an increment in the bus address. After each voltage transition, the bus current is monitored to check for diagnostic and signal responses from sensor ICs. Device Addressing When a device detects a bus address equal to its factory programmed address, it reFIGURE 1 sponds with an increase in its supply current drain (called I S during the HIGH portion of the address cycle). This response may be used as an indication that the device is alive and well on the bus and is also called the diagnostic response. If the device detects an ambient magnetic field, it also responds with IS during the low portion of the address cycle. This response from the device is called the signal response. When the next positive transition is detected, the device becomes disabled, and its contribution to the bus signal current returns to I Q. Bus Current Figure 1 displays the above described addressing protocol. The top trace represents the bus voltage transitions as controlled by the bus driver (see applications note for an optimal bus driver schematic). The second trace represents the bus current contribution of device (address 02). The diagnostic response from the device indicates that it detected its address on the bus; however, no signal response current is returned, which indicates that sufficient magnetic field is not detected at the chip surface. The third trace represents the current drain of device 03 when a magnetic field is detected. Note both the diagnostic and signal response from the device. The last trace represents

BUS TIMING D1

V V H CLH

DIAGNOSTIC ADDRESS 01

DIAGNOSTIC ADDRESS 02

DIAGNOSTIC ADDRESS 03

DIAGNOSTIC ADDRESS 04

DIAGNOSTIC ADDRESS n

DIAGNOSTIC ADDRESS 01

BUS VOLTAGE

CHL V L

RESET

RST 0 t plh t phl

RESET

IS

Device 02 DIAGNOSTIC CURRENT

Device 02 CURRENT WITH NO MAGNETIC FIELD

I QL I QH 0

IS

Device 03 DIAGNOSTIC AND SIGNAL CURRENTS

Device 03 CURRENT WITH MAGNETIC FIELD

I QL I QH 0

TOTAL BUS CURRENT WITH MAGNETIC FIELD AT Device 03

Device 01 NOT PRESENT

n I QL n I QH 0

Device 01 NOT PRESENT

Dwg. WH-005

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

3055 MULTIPLEXED TWO-WIRE HALL EFFECT SENSOR IC

the overall bus current drain. When no devices are addressed, the net bus current drain is the sum of quiescent currents of all devices on the bus (for n devices, the bus quiescent current drain is n * I Q). Bus Issues At present, a maximum of 30 active devices can coexist on the same bus, each with a different address. Address 0 is reserved for bus current calibration in software. This feature allows for fail-safe detection of signal current and eliminates detection problems caused by low signal current (IS), the operation of devices at various ambient temperatures, lot-to-lot variation of quiescent current, and the addition and replacement of devices to the bus while in the field. Address 31 is designed to be inactive to allow for further address expansion of the bus (to 62 maximum addresses). In order to repeat the address cycle, the bus must be reset as shown in Figure 1 by bringing the supply voltage to below VRST . Devices have been designed not to wrap-around. Magnetic Sensing The device IC has been designed to respond to an external magnetic field whose magnetic strength is greater than BOP. It accomplishes this by amplifying the output of an on-chip Hall transducer and feeding it into a threshold detector. In order that bus current is kept to a minimum, the transducer and amplification circuitry is kept powered down until the device is addressed. Hence, the magnetic status is evaluated only when the device is addressed. External Switch Sensing The third pin of the IC (pin 3) may be used to detect the status of an external switch when magnetic field sensing is not desired (and in the absence of a magnetic field). The allowable states for the switch are open and closed (shorted to device ground). APPLICATIONS NOTES Magnetic Actuation The left side of Figure 2 shows the wiring of the UGN3055U when used as a magnetic threshold detector. Pin 1 of the device is wired to the positive terminal of the bus, pin 2 is connected to the bus negative terminal, and pin 3 has no connection. Mechanical Actuation The right side of Figure 2 shows the wiring of the UGN3055U when used to detect the status of a mechanical switch. In this case, pin 3 is connected to the positive terminal of the switch. The negative side of the switch is connected to the negative terminal of the bus. When the mechanical switch is closed (shorted to ground) and the correct bus address is detected by the IC, the device responds with a signal current. If the switch is open, only a diagnostic current is returned. FIGURE 2

DEVICE CONNECTIONS

POSITIVE BUS SUPPLY

NC SWITCH BUS RETURN

Dwg. EH-004

3055 MULTIPLEXED TWO-WIRE HALL EFFECT DEVICE IC

FIGURE 3

BUS INTERCONNECTION

MICROPROCESSOR

UGN3055U

INTERFACE

ADDRESS RESET ANALOG OUT

MULTIPLEXED TWO-WIRE HALL EFFECT DEVICE IC

(POSITIVE) BUS SUPPLY

AND

UGS3055U

28 29

01

02

30

BUS RETURN

Dwg. EH-005

Bus Configuration A maximum of 30 devices may be connected across the same two wire bus as shown in Figure 3. It is recommended that the devices use a dedicated digital ground wire to minimize the effects of changing ground potential (as in the case of chassis ground in the automotive industry). The bus was not designed to require two-wire twisted-pair wiring to the devices; however, in areas of extreme EMI (electro-magnetic interference), it may be advisable to install a small bypass capacitor (0.01 F for example) between the supply and ground terminals of each device instead of using the more expensive wiring. Bus Driver It is recommended that the bus be controlled by microprocessor-based hardware for the following reasons: Device address information may be stored in ROM in the form of a look up table. Bus faults can be pinpointed by the microprocessor by comparing the diagnostic response to the expected response in the ROM look up table. The microprocessor, along with an A/D converter, can also be used to self calibrate the quiescent currents in the bus and hence be able to easily detect a signal response.

The microprocessor can also be used to filter out random line noise by digitally filtering the bus responses. The microprocessor can easily keep track of the signal responses, initiate the appropriate action; e.g., light a lamp, sound an alarm, and also pinpoint the location of the signal. Optimally, the microprocessor is used to control bus-driving circuitry that will accept TTL level inputs to drive the bus and will return an analog voltage representation of the bus current. Interface Schematic The bus driver is easily designed using a few operational amplifiers, resistors, and transistors. Figure 4 shows a schematic of a recommended bus driver circuit that is capable of providing 6 V to 9 V transitions, resetting the bus, and providing an analog measurement of the current for use by the A/D input of the microprocessor. In Figure 4, the Address pin provides a TTL-compatible input that is used to control the Bus supply. A HIGH (5 V) input switches Q1 ON and sets the bus voltage to 6 V through the resistor divider R4, R5, and the Zener Z1. A LOW input switches OFF Q2 and sets the bus voltage to 9 V. This voltage is fed into the positive input of the operational amplifier OP1 and is buffered and made available at Bus Supply (or device supply). Bus reset control is also available in the form of a TTL-compatible input. When this input, which is marked Reset, is HIGH, Q2 is switched ON and the positive input of the op amp is set to the saturation voltage of the transistor (approximately 0 V). This resets the bus. A linear reading of the bus current is made possible by amplifying the voltage generated across R6 (which is IBUS * R6). The amplifier, OP2, is a standard differential amplifier of gain R9/R7 (provided that R7 = R8, R9 = R10). The gain of the total transimpedance amplifier is given by: V OUT = IBUS * R6 * R9/R7 This voltage is available at the terminal marked Analog Out.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

3055 MULTIPLEXED TWO-WIRE HALL EFFECT SENSOR IC

Bus Control Software The processing of the bus current (available at Analog Out) is best done by feeding it into the A/D input of a microprocessor. If the flexibility provided by a microprocessor is not desired, this signal could be fed into threshold detection circuitry; e.g., comparator, and the output used to drive a display. Related References 1. G. AVERY, Two Terminal Hall. Sensor, ASSIGNEE: Sprague Electric Company, North Adams, MA, United States. Patent number 4,374,333; Feb. 1983. 2. T. WROBLEWSKI and F. MEISTERFIELD, Switch Status Monitoring System, Single Wire Bus, Smart Sensor Arrangement There Of, ASSIGNEE: Chrysler Motor Corporation, Highland Park, Ml, United States. Patent number 4,677,308; June 1987.

FIGURE 4

BUS INTERFACE SCHEMATIC

+15 V

1 k 10 k R 4 9V Z1 0.001 F 20 k R5 ADDRESS 5 k Q1 RESET 5 k 50 k R8 50 k R7

1 2 3 1 2 3

1 k Q3 OP 1 BUS SUPPLY 50 R 6 Q2

NC SWITCH

100 k R 9

BUS RETURN

ANALOG OUT OP 2 100 k R 10

Dwg. EH-003A

3055 MULTIPLEXED TWO-WIRE HALL EFFECT SENSOR IC

Dimensions in Inches (controlling dimensions)

Dimensions in Millimeters (for reference only)

0.183 0.178 0.063 0.059

4.65 4.52 1.60 1.50

0.181 0.176 45 0.086

MAX

4.60 4.47 45 2.18

MAX

0.018

0.46

0.560

MIN

0.015

14.22

MIN

0.38

0.016

SEE NOTE SEE NOTE

0.41

0.050 0.100

Dwg. MH-003C in

1.27 2.54

Dwg. MH-003C mm

NOTES: 1. Tolerances on package height and width represent allowable mold offsets. Dimensions given are measured at the widest point (parting line). 2. Exact body and lead configuration at vendors option within limits shown. 3. Height does not include mold gate flash. 4. Recommended minimum PWB hole diameter to clear transition area is 0.035 (0.89 mm). 5. Where no tolerance is specified, dimension is nominal. 6. Minimum lead length was 0.500 (12.70 mm). If existing product to the original specifications is not acceptable, contact sales office before ordering.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the design of its products. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Vansco VMM Diagnostics Rev 6 - CUBEXDocument27 pagesVansco VMM Diagnostics Rev 6 - CUBEXHector Sepulveda Orellana100% (3)

- E L RelayDocument31 pagesE L RelayBal SubramaniNo ratings yet

- Us 495582Document3 pagesUs 495582frust diamondNo ratings yet

- Presentation on Power Distribution System of a Thermal Power PlantDocument48 pagesPresentation on Power Distribution System of a Thermal Power PlantsreekanthbammidiNo ratings yet

- Cell Phone DetectorDocument22 pagesCell Phone DetectorKarthik Sharma Ponugupati100% (3)

- Trucon AssociatesDocument16 pagesTrucon AssociatessanchaNo ratings yet

- Commissioning of DAVRDocument70 pagesCommissioning of DAVRPMG Bhuswal Project100% (1)

- SCADADocument57 pagesSCADAkailasamvv100% (1)

- DCpower SuplyDocument12 pagesDCpower Suplymm30973097No ratings yet

- 2VAA002134 - en S Control NTDI02 Digital IO Termination UnitDocument47 pages2VAA002134 - en S Control NTDI02 Digital IO Termination UnitanbarasanNo ratings yet

- Voltage Divider ExperimentDocument14 pagesVoltage Divider ExperimentDave Vic Solis100% (2)

- Fundamentals of Floating Measurements and Isolated Input Oscilloscopes - Tektronix - 3AW - 19134 - 2 - MR - LetterDocument8 pagesFundamentals of Floating Measurements and Isolated Input Oscilloscopes - Tektronix - 3AW - 19134 - 2 - MR - LetterluroguitaNo ratings yet

- A3150Document12 pagesA3150Pham LongNo ratings yet

- ACS755 050 DatasheetDocument10 pagesACS755 050 DatasheetejmelchiorsNo ratings yet

- 132KV 2 Line Metering PanelDocument11 pages132KV 2 Line Metering PanelUsman RasheedNo ratings yet

- Basic Measurement PiezoeletricDocument6 pagesBasic Measurement PiezoeletricALEX_INSPETORNo ratings yet

- AD654Document12 pagesAD654Christopher RiceNo ratings yet

- 3 Wire SensorsDocument8 pages3 Wire SensorsInduAutomationNo ratings yet

- Fundamentals of Floating Measurements and Isolated Input OsciiloscopesDocument8 pagesFundamentals of Floating Measurements and Isolated Input OsciiloscopesKatherine MccoyNo ratings yet

- 2 Ask, PSK, FSKDocument15 pages2 Ask, PSK, FSKI AM A PROGRAMMERNo ratings yet

- Dual Current-Sense Amplifi Ers Simplify H-Bridge Load MonitoringDocument2 pagesDual Current-Sense Amplifi Ers Simplify H-Bridge Load MonitoringJorge GuerreroNo ratings yet

- 325 OscilloscpeDocument3 pages325 OscilloscpeHammad JamesNo ratings yet

- Lab EquipmentsDocument7 pagesLab EquipmentsIbne FazalNo ratings yet

- MillMinder Audio Signal MonitorDocument15 pagesMillMinder Audio Signal Monitorescorpion311No ratings yet

- Simple PWM Boost Controller: Power Management Features DescriptionDocument11 pagesSimple PWM Boost Controller: Power Management Features DescriptionJoe MiguelNo ratings yet

- Low Power Single Chip PstatDocument2 pagesLow Power Single Chip PstatKay ReimersNo ratings yet

- Instrumentation AmplifierDocument3 pagesInstrumentation AmplifierFreddy LlusionNo ratings yet

- Analog and Digital Ic'S Short Questions With AnswersDocument41 pagesAnalog and Digital Ic'S Short Questions With Answerspriya adhavanNo ratings yet

- E645Document14 pagesE645Hillary McgowanNo ratings yet

- ADE7953 EnergyMeterDocument2 pagesADE7953 EnergyMeterKram Nhoj TabatabNo ratings yet

- Ratiometric, Linear Hall-Effect Sensors For High-Temperature OperationDocument13 pagesRatiometric, Linear Hall-Effect Sensors For High-Temperature OperationLuiz JesusNo ratings yet

- Harest PDFDocument76 pagesHarest PDFAmedeo GalluccioNo ratings yet

- A Fully Isolated Delta-Sigma ADC For Shunt Based Current SensingDocument9 pagesA Fully Isolated Delta-Sigma ADC For Shunt Based Current Sensingpramani90No ratings yet

- Panasonic LCD (2012) TX-l55wt50 (La34)Document67 pagesPanasonic LCD (2012) TX-l55wt50 (La34)Jacob EvansNo ratings yet

- JFBKL: ApplicationsDocument11 pagesJFBKL: ApplicationsAnandha PadmanabhanNo ratings yet

- Balluff Inductive Prox Basic Info & Wiring DiagramsDocument14 pagesBalluff Inductive Prox Basic Info & Wiring DiagramssurezzvNo ratings yet

- Cable Fault DetectorDocument25 pagesCable Fault DetectorHarshalNo ratings yet

- User Manual ISOLTESTER-DIGDocument23 pagesUser Manual ISOLTESTER-DIGJuan Alberto Cayetano GomezNo ratings yet

- Ivc102 DatasheetDocument15 pagesIvc102 DatasheetChristian CândidoNo ratings yet

- UNIT8Document30 pagesUNIT8Karthik VNo ratings yet

- A 3423 Hall Effect EncordorDocument9 pagesA 3423 Hall Effect Encordortabassam7801No ratings yet

- Dual Trace Oscilloscope Block Diagram & SpecsDocument8 pagesDual Trace Oscilloscope Block Diagram & SpecsSudip MondalNo ratings yet

- P MC3x0 GB 22444000 Ver 6.04Document4 pagesP MC3x0 GB 22444000 Ver 6.04we12321No ratings yet

- 555 Timer As Mono Stable Multi VibratorDocument8 pages555 Timer As Mono Stable Multi VibratorchrisgeclayNo ratings yet

- Wireless I CDocument3 pagesWireless I CkenbobalajiNo ratings yet

- Sensors WAGoDocument28 pagesSensors WAGoankit_rathi_19No ratings yet

- A132XDocument10 pagesA132XAndres CamachoiNo ratings yet

- IEEE 1850 GroundGridCalcsDocument11 pagesIEEE 1850 GroundGridCalcsaabts1413No ratings yet

- Voltage Controlled Oscillator - Usage of VCO, Working and ApplicationDocument6 pagesVoltage Controlled Oscillator - Usage of VCO, Working and ApplicationseemabNo ratings yet

- Signal Conditioning Tutorial: Figure 1. Signal Conditioning Is An Important Component of A PC-based DAQ SystemDocument5 pagesSignal Conditioning Tutorial: Figure 1. Signal Conditioning Is An Important Component of A PC-based DAQ SystemYehia ElmansyNo ratings yet

- Micro VoltmeterDocument6 pagesMicro Voltmeteranto_hardianto443No ratings yet

- AnshuDocument26 pagesAnshuAnubha ChaudharyNo ratings yet

- Op AmpsDocument22 pagesOp AmpsKrishnaveni DhulipalaNo ratings yet

- Industrial ElectronicsDocument65 pagesIndustrial ElectronicsDivya SurapaneniNo ratings yet

- RDM 680 ManualDocument20 pagesRDM 680 Manualpbs0707No ratings yet

- Experiment No: 01 Voltage Controlled OscillatorDocument7 pagesExperiment No: 01 Voltage Controlled OscillatorSafia SohailNo ratings yet

- Measure AC Signals and Harmonics with PZ96L-3EHDocument15 pagesMeasure AC Signals and Harmonics with PZ96L-3EHadrianomajoneNo ratings yet

- 4200 Pulsed-IV ApplicationsGuideDocument75 pages4200 Pulsed-IV ApplicationsGuideStefan-Marian IordacheNo ratings yet

- 10884Document13 pages10884karthikeidNo ratings yet

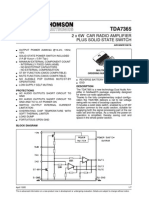

- 2 X 6W Car Radio Amplifier Plus Solid State Switch: Protections DescriptionDocument8 pages2 X 6W Car Radio Amplifier Plus Solid State Switch: Protections DescriptionMiloud ChouguiNo ratings yet

- EX - NO:03 Comparator Circuits DateDocument7 pagesEX - NO:03 Comparator Circuits DateVijayakumar KNo ratings yet

- 128122-Accelerometer & VelomitorTransducerOperationDocument22 pages128122-Accelerometer & VelomitorTransducerOperationNorman MoralesNo ratings yet

- Countable vs Uncountable NounsDocument12 pagesCountable vs Uncountable NounsMiguel Angel ReyesNo ratings yet

- English Grammar - Tenses TableDocument5 pagesEnglish Grammar - Tenses TableGeorgopoulos NikosNo ratings yet

- EB7781393Document92 pagesEB7781393subrata.chakrabarti2544No ratings yet

- Objetivo: Configurar DHCP en Sus Diferentes VariantesDocument5 pagesObjetivo: Configurar DHCP en Sus Diferentes VariantesMiguel Angel ReyesNo ratings yet

- Convo Luci OnDocument5 pagesConvo Luci OnMiguel Angel ReyesNo ratings yet

- Philips fw-m777 PDFDocument79 pagesPhilips fw-m777 PDFaries2010mxNo ratings yet

- 2N3819 JFET Spec SheetDocument5 pages2N3819 JFET Spec SheetMiguel Angel ReyesNo ratings yet

- Các kí hiệu trong bản vẽ thiết kế nhà máy nhiệt điệnDocument6 pagesCác kí hiệu trong bản vẽ thiết kế nhà máy nhiệt điệnthanhphong2782No ratings yet

- 8130 Rack MonitorDocument2 pages8130 Rack MonitorIsaías Ro ENo ratings yet

- AC Motor ConnectionsDocument6 pagesAC Motor ConnectionsJ_WhitneyNo ratings yet

- m400 DatasheetDocument7 pagesm400 DatasheetFranco MaderaNo ratings yet

- Eurosmccatalogues PDFDocument360 pagesEurosmccatalogues PDFchichid2009No ratings yet

- Label-1800 & UBR - Indoor CabinetDocument2 pagesLabel-1800 & UBR - Indoor CabinetWanhosi Nirvani NirvaniNo ratings yet

- Thermodynamics LabDocument8 pagesThermodynamics Labmohammad. 21No ratings yet

- Inverting Amplifier:: To Study The Following Op-Amp CircuitsDocument11 pagesInverting Amplifier:: To Study The Following Op-Amp CircuitsUMESH RAJ25No ratings yet

- No Option A Option B Option C Option DDocument4 pagesNo Option A Option B Option C Option DRushangNo ratings yet

- 3G2080 TL2803G Reference-Manual-Extended R001 enDocument52 pages3G2080 TL2803G Reference-Manual-Extended R001 enDragus IonelNo ratings yet

- CH 7Document53 pagesCH 7Gautam TamangNo ratings yet

- Cadence Lab ReportDocument12 pagesCadence Lab ReportAnkur MorNo ratings yet

- Untitled DiagramDocument1 pageUntitled DiagramirfanNo ratings yet

- The Multi - Tester: Technology and Livelihood Education-Grade 9 Quarter 2, Week 3Document8 pagesThe Multi - Tester: Technology and Livelihood Education-Grade 9 Quarter 2, Week 3Sori Dens0% (1)

- Literature ReviewDocument9 pagesLiterature Reviewshuvro911No ratings yet

- Section 12 Metal Inert-Active Gas Welding (MIG MAG GMAW)Document12 pagesSection 12 Metal Inert-Active Gas Welding (MIG MAG GMAW)S GoudaNo ratings yet

- Question 961019Document11 pagesQuestion 961019rajaNo ratings yet

- 2 Tannoy Studio Monitors 1985Document17 pages2 Tannoy Studio Monitors 1985Григорий БоржковскийNo ratings yet

- Harmonic Filtering of High-Power 12-Pulse Rectifier Loads With A Selective Hybrid Filter SystemDocument10 pagesHarmonic Filtering of High-Power 12-Pulse Rectifier Loads With A Selective Hybrid Filter Systemnareshkumar KNo ratings yet

- 7SG11 Argus 7 Complete Technical ManualDocument73 pages7SG11 Argus 7 Complete Technical Manualvivek2159No ratings yet

- 3S MTDocument9 pages3S MTThomas GarzaNo ratings yet

- Sibabrata DasDocument4 pagesSibabrata DasjaydiphajraNo ratings yet

- Ft411mkii ManualDocument32 pagesFt411mkii ManualManuel GomesNo ratings yet

- Sensata Fact SheetDocument2 pagesSensata Fact SheetVenugopal SikhaNo ratings yet

- Service Manual: Digital HD Videocassette RecorderDocument78 pagesService Manual: Digital HD Videocassette RecorderthewarapperumaiuNo ratings yet