Professional Documents

Culture Documents

Moaaz AHMED Convex Project

Uploaded by

Moaaz AhmedCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Moaaz AHMED Convex Project

Uploaded by

Moaaz AhmedCopyright:

Available Formats

1

gm/Id based optimal design of a CMOS OTA via geometric programming

Moaaz Ahmed [Student I.D. 20081256] ELEC 5470: Convex Optimization, Final Project Report Department of Electronics and Computer Engineering The Hong Kong University of Science and Technology, Hong Kong

Index Terms gm/Id based sizing methodology, geometric programming, analog circuit optimization, OTA design

I. I NTRODUCTION

Operational ampliers are the basic building block in analog circuit design. They nd wide array of applications in RF design, lters, analog-to-digital converters, communication systems and biomedical systems design. Designers nd it increasingly difcult to come up with an optimum design of an operational amplier meeting competing performance requirements (i.e. gain, bandwidth, noise, power, area, signal swings, slew rate etc.) especially at submicron/nanometer CMOS processes. The increasing design complexity coupled with stringent deadlines (to stay competitive in market) can only be managed by the use of computer aided design. The aforementioned challenges could be overcome by automating the design of important analog blocks with an added advantage of nding an optimum solution in terms of a given objective (power, area or speed). Many authors have tried to overcome this challenge and these efforts could be traced back to more than thirty years. We may classify the analog design automation efforts in two categories. In one, the circuit topology is xed and only optimal device sizing is performed [4], [11] [5] [8]. The other approach is more general for it also automate the selection of an optimum circuit topology. Our projects targets the rst category. The main issue with the automatic sizing problem is the fundamental tradeoff between device models accuracy and the posynomial formulation required to enable convex optimization for analog design via geometric programming (GP). BSIM4 SPICE equations that capture accurate device behavior contain hundreds of parameters rendering them impossible to use in any practical optimization framework. Whereas the approaches taking simplied device models enabling equations with fewer parameters, for instance, long-channel square-law model followed by [4] [6] and many others fail in modern scaled processes because short-channel effects start dominating below 250nm channel lengths. In 1996 Selveira et al proposed a new design methodology based on a unied treatment of all regions of operations of the MOS transistor [7]. Two approaches have been taken to implement the design of high performance analog circuits in nanometer CMOS processes using gm/Id methodology. The rst approach takes advantage of real measurements or spice simulation data derived from advanced BSIM models arranged in lookup tables. The second makes use of models supposed to be accurate and simple enough to pave the way towards reliable analytical expressions of the transconductance over drain current (gm/Id) ratios. We took the second approach and express the

equations in posynomial form so as to perform optimization of an operational amplier via geometric programming and harness the power of convex optimization.

II. OVERVIEW OF EXISTING WORK

A geometric program or a GP is a special type of mathematical optimization problem which can be expressed in standard form as following: minimize

x

f0 (x) fi (x) 1, gl (x) = 1, xi > 0, i = 1, . . . , m (1) l = 1, . . . , p i = 1, . . . , n

subject to

Where fi are posynomial functions that represent inequality constraints and gl are monomial functions which represents equality constraints. A posynomial function is dened as:

K k=1

nk 1 k 2 k ck x x2 . . . , x , n 1

f (x1 , . . . , xn ) =

xi > 0 .

(2)

Posynomial functions are real-valued functions of n real, positive variables xi with nonnegative coefcients ck 0 and any real exponents i,j R. A single term posynomial is called a monomial, i.e.,

n 1 2 g (x1 , . . . , xn ) = c1 x 1 x 2 . . . , xn ,

xi > 0.

(3)

As evident, a GP in standard form is not convex; however, it can easily be transformed into convex problem by change of variable and a transformation of objective and constrained function as shown by [9] minimize

y Ko k=1

p0 (y ) = log

exp(aT 0k y + bok ) exp(aT ik y + bik ) 0, (4)

subject to

pi (y ) = log ql (y ) = aT ly

Ki k=1

i = 1, 2, . . . , m l = 1, 2, . . . , p

+ bl = 0 ,

In 1985 J. P. Fishburn and Dunlop rst observed that transistor sizing problem could be formulated as a convex problem to minimize the area, critical path or their product for digital circuits [1]. Their method called TILOP optimize the sizing of few adder and ip-op structures based on Elmore delay model which later turns out to be a GP problem. Sapatnekar et. al. in 1993 improved on the existing approaches by proposing new iCONTRAST algorithm based on convex programming which guaranteed to nd the global minimum solution [2]. The major advantage of their approach was the removal of explicit delay constraints thereby reducing the exponential problem size and enabling them to optimize digital circuits with hundreds of transistors. The rst application of convex optimization to analog circuit design traces back to 1993 [6] when Maulik et. al. presented a method for automatically sizing the transistors in cell-level analog circuits (e.g., op amps, comparators, etc.) using constrained optimization technique. All knowledge about device behavior is embedded within an encapsulated device evaluator which simplies the description of the analog circuit that must be provided by an expert designer, and makes that description independent of the specic device type and technology. The use of constrained optimization allows the KCL and KVL constraints that determine the dc operating point of a circuit to be formulated and solved for simultaneously with the performance constraints. Their formulation eliminates the need to determine the dc operating

point separately by formulating the KCL constraints in their optimization problem which are simultaneously satised during the optimization process. The shortfall in their approach is the necessity to obtain analytical performance equations from an expert designer for every new circuit topology. In 1997 Hershenson and Boyd introduced a new method for determining component values and transistors dimensions using geometric programming [3]. They observe that most of the design objectives and constraints in Op Amp design have a special form, i.e. they are posynomial functions of the design variables which enable them to express the amplier design problem as a special form of optimization problem called geometric programming [4]. However they didnt use the second order effects and implemented their design in 1.2um CMOS process using long-channel square-law model assumptions. Their methodology wouldnt be able to generate acceptable results if implemented in modern sub nanometer regimes. In 2001, Mandal and Visvanathan proposed an improved methodology to optimize the design of an operational amplier taking into account second order effect [5]. But their method lacks a unied approach as they tackled the problem in successive steps by combining relaxed dc formulation and casual dc analysis which also makes their method time consuming. To circumvent the disadvantages of device model inaccuracies, Kim et. al. proposed to model transistor parameter behavior using piecewise linear models, hence improving accuracy [8]. In addition, they also devise a technique to relax posynomial equality (non-convex) constraint with inequality constraint to enable the GP formulation and help improve the bias point calculation. In 2007, Xin Li et. al. proposed a new robust analog design (ROAD) approach to locally optimize analog/RF circuits based on accurate transistor-level simulations under large process and environmental variations [11]. ROAD works in two steps: rst an initial nominal design is created using traditional optimization methods like [4] through a rapid but coarse search over the entire design space. In second step, ROAD is applied with detailed device/variation models to perform a more ne-grained search and optimizes the worst case circuit performance, considering all process and environmental variations. Recently, A.K. Singh et. al. seek to combine the accuracy of SPICE simulations with the global optimality of GP-based methods [12]. The central idea is to numerically capture the error between exact device behavior (via SPICE) and GP models and use these measured errors to design a robust optimization problem that takes into account specically these errors. This enable them to nd a feasible, but possibly suboptimal point. Then rening around this point, a higher accuracy GP model is obtained which could be nally robustied according to the tting errors between the GP model and SPICE.

III. C RITICISM OF THE EXISTING WORK

The work of Maulik et. al. is signicant in the context of being the rst to apply convex optimization in designing cell-level analog circuits via GP formulation [6]. The use of constrained optimization allows the KCL and KVL constraints that determine the dc operating point of a circuit to be formulated and solved for simultaneously with the circuit-level performance constraints. Although, they were able to show some encouraging results by optimally designing few basic ampliers but their methodology is based on too many assumptions or simplications to be applicable to modern scaled transistors. Hershensen and Boyd presented a systematic approach to optimize operational ampliers and extend their method to optimally design a pipelined ADC and even RF circuits by expressing design constraints and MOS model equations in posynomial form [3][4]. They also devised a novel approach to handle the effect of process mismatch and temperature variations by incorporating new constraints to improve reliability and yield. Such manner of design for process robustness is practical only because GP can readily handle thousands of constraints and solve the problem

in few minutes taking advantage of newly developed interior point methods. Unfortunately, their approach is based on square-law quadratic model to evaluate transistor bias points which makes it grossly erroneous as the results could be well up to 50 percent off the intended design target in scaled transistors. Mandal et. al. [5] try to overcome the above challenge by formulating and solving the problem as a sequence of (convex) geometric programs. The central idea is to rst solve the GP formulation by using long-channel quadratic model as in [3] [4] and then update the quadratic model parameters using the higher order transistor models through BSIM simulations. In other words, the formulation of [4] is just the rst step of their approach. This difference is crucial in scaled transistors since the models required to support their methodology need to support the GP formulation only in their rst order effects, while the models of second order behavior can be arbitrary. The sequential convex programming formulation is made possible by taking advantage of many other approaches which makes the approach time and computational intensive and also make it possible to fail in nding a feasible solution. Although the SCP provides a sequence of iterants that are globally optimal solutions of convex subproblems but it should be borne in mind that this does not guarantee that the nal solution is the global optimum of the original sizing problem. Kim et. al. [8] suggest improvements in device modeling for GP-based analog design optimization by using piecewise linear PWL models and claim that the method is capable of creating accurate device models in deep submicron technology by demonstrating the results in 0.18 micron technology. Unfortunately, this improved t may lead to nonposynomial and, in particular, nonconvex constraints. Furthermore they try to show that bias-related nonconvex constraints can be enabled by exploiting monotonicity, which reduces the bias estimation error. Our approach can handle bias estimation more accurately with no need to approximate or relax the posynomial equality constraint as their approach introduce some error. Their third argument to achieve robust optimization by taking modeling error into account for worst case errors. This can be highly overconservative because it may introduce robustness where none is needed. As a consequence, the feasible space of the optimization may be unduly and signicantly reduced, resulting in degraded performance, or in the worst case, an inability to nd a SPICE-simulation feasible solution. Whereas ROAD [11] also works in two steps: rst a coarse but rapid scan over entire design space using traditional optimization based on simplied MOS models and later a ne-tuned process robustness enabled optimization routine using SPICE simulations. The major drawback of this approach is that it uses a local renement strategy and perform renement and retting in a very small region around the current solution, thus nding a locally optimal solution which do not necessarily provide a global optima. Our approach is superior in that it requires single-shot GP formulation such that the global optimality is guaranteed. The central theme is to employ gm/Id based analytical equations which are simple enough to enable GP compatibility and accurate enough to match SPICE accuracy. Thus we do not need to resort to statistical rening methods and/or divide the given optimization problem in multiple subproblems and risk infeasibility. A crucial component of ROAD is a novel projection based scheme for quadratic (both polynomial and posynomial) performance modeling, which allows to scale well to large problem sizes. Recent paper of Singh et. al. propose a novel optimization strategy that explicitly handles the error of the model in the course of optimization by enabling the successive renement of transistor models within gradually reducing ranges of operating conditions and dimensions [12]. However the need to generate a large number of tting parameters (gm , gds , Cgs , Cgd , Cdb , etc) through SPICE iterations require excessive computation time and render the method inefcient or even unapplicable for dynamic, latching and high-frequency circuits where these small-signal parameters change rapidly.

IV. N EW CONTRIBUTION

Our idea is to combine the gm/Id based design methodology with geometric programming to perform analog circuit optimization in a simplied but efcient manner. All previous equation-based sizing approaches are based

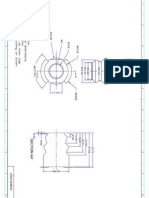

Fig. 1.

Schematics of the classic two-stage op-amp.

on square-law model which ignores higher order effects and is inapplicable to modern short-channel devices. Since current in a MOSFET is due to diffusion in week inversion and drift in strong inversion. Classic square-law is based on ideal drift model and applies only on the onset of strong inversion. For week inversion, the exponential diffusion current model similar to that of BJT is commonly employed. But there is no model available that accurately traces the transition region between week and strong inversion which is often found to give optimum results in terms of both speed and power consumption [10]. The gm/Id based sizing methodology [7] [10] has attracted a great deal of attention from the research community due to its validity in all regions of operations including the previously ignored moderate inversion region. The gm/Id methodology could be utilized through two approaches; one is based on actual spice simulation results arranged in lookup tables which is called semi-empirical approach. The other one is based on EKV model and we call it model-based approach. Although EKV model is based on charge-sheet model but it has been shown in [10] that it matches SPICE accuracy when its three fundamental parameters are allowed to vary with bias and gate lengths which reects short channel and higher order effects. We also followed the approach of [4] [8] in setting design constraints for the classic two-stage miller OTA as shown in Fig. 1. For symmetry and matching considerations, the input differential pair M1-M2 and current mirror transistors M3-M4 must be identical which means: W1 = W2 , L1 = L2 , W 3 = W4 , L3 = L4 (5)

Similarly, the biasing transistors of the current load M5 , M7 and M8 must also match, i.e. have the same length: L5 = L7 = L8 (6)

The six equality constraints in (5) and (6) have monomial expressions which are readily handled in geometric

1 programming by expressing them as monomial equality constraints such as W1 W2 = 1.

Lithography limitations and layout rules impose minimum sizes on the transistors: Lmin Li Lmax , Wmin Wi Wmax , i = 1, . . . , 8. (7)

1 These 32 constraints can be expressed as posynomial constraints such as Lmin L 1 1, and so on.

The op-amp die area can be expressed in the form of following summation: A = 0 + 1 Cc + 2

8 i=1

Wi Li .

(8)

Where 0 0 gives the xed area, 1 1 is the ratio of capacitor area to capacitance, and the constant 2 1 (if it is not one) can take into account wiring in the drain and source area. This expression for the area is a posynomial function of the design parameters, so we can impose an upper bound on the area, i.e.,A Amax , or use the area as the objective to be minimized. For minimum input offset voltage, the drain voltages of M3 and M4 must be equal, ensuring that the current I5 is split equally between input differential pair . This happens when the current densities of M3 , M4 , and M6 are equal, i.e.,

1 1 1 W3 L W4 L 1 W5 L 3 4 5 1 = 1 = 1 2 W7 L7 W6 L6 W6 L6

(9)

Above constraints are equality constraints between monomials which are easily handled by GP. Now we consider constraints involving bias conditions, including the effects of common-mode input voltage and output signal swing. The quiescent power of the op-amp is also determined by the bias conditions. [4] use standard long channel, square-law model for the MOS transistors which ignores second order effects and generate grossly erroneous results for short-channel devices. This is where we make our contribution by using gm/Id based EKV model with its parameters allowed to vary with bias and channel length to incorporate the higher order effects and reect the SPICE accuracy in generating drain current and bias voltages. Biasing equation can be expressed into two categories, one circuit specic and the other device model based. Since we are using the same Miller OTA, our circuit design equations are the same. Transistors M5 and M7 form a current mirror with transistor M8 . Their currents are given by: I5 =

1 W5 L 5 1 Ibias , W8 L8

I7 =

1 W7 L 7 1 Ibias W8 L8

(10)

Clearly I5 and I7 are monomials in the design variables. The current through current load M5 is split equally between input differential pair M1-M2 such that: I1 =

1 I5 1 W5 L 5 = 1 Ibias 2 2 W8 L 8

(11)

which is again a monomial. We shall use I1 , 15 and I7 in order to express other constraints keeping in mind that these bias currents can simply be eliminated (i.e., expressed directly in terms of the design variables) using (10) and (11). The bias conditions are that each transistor M1 , /IdotsM8 should remain in saturation for all possible values of the input common-mode voltage and the output voltage swing. The bias constraints given below are derived from long-channel square-law model and yield inaccurate results in short-channel channel devices. These biasing constraints have been replaced by gm/Id model based analytical equations to improve the accuracy of optimization problem. Transistor M1 and M2 : The lowest input common-mode input voltage impose the hardest constraint on transistor M1 to remain in saturation such that: I1 L3 Vcm,min VSS VT P VT N . p Cox /2W3 (12)

The systematic offset condition (9) makes the drain voltage of M1 equal to the drain voltage of M2 . Hence, the saturation condition for M2 is the same as that of M1 . The minimum value of Vcm,min can be derived by M1 and M2 entering the linear/triode region. Transistor M3 and M4 : Since M3 is a diode-connected transistor with its Vgd,3 = 0, it always remain in saturation. Similar to the above differential pair case, the systematic offset condition also implies that the drain voltage of M4 remains equal to the drain voltage of M3 . Thus M4 will also keep in saturation. Transistor M5 : The highest common-mode input voltage, V cm, max imposes the toughest constraint on transistor M5 to keep in saturation such that: I1 L1 I5 L5 + VDD Vcm,max + VT P . p Cox /2W1 p Cox /2W5 The maximum limit of Vcm,max is determined by M5 entering the linear/triode region. Transistor M6 : For M6 to keep in saturation, the tightest constraint occurs when the output voltage is at its minimum value Vout,min such that: I7 L6 Vout,min VSS . p Cox /2W6 (14)

(13)

Transistor M7 : For transistor M7 , the most stringent consition occurs when the output voltage is at its maximum value Vout,max such that: I7 L7 VDD Vout,max . p Cox /2W7 (15)

Transistor M8 : Transistor M8 is also a diode-connected with Vgd,8 = 0 so it will always remain in saturation. To ensure that the transistors always keep in saturation and away from subthreshold region under process variations, it is necessary to operate them with some minimum gate overdrive voltage. For any transistor this constraint can be imposed as: Vgs CT = ID Li Voverdrive,min p,n Cox /2Wi i = 1, . . . , 8. (16)

The above constrains is also derived from long-channel square-law model which would be replaced by EKV model expression. Nevertheless, both forms are in monomial form, so we may impose an upper bound or an equality constraint depending on requirement. The quiescent power of this OTA (operational transconductance amplier, a precise term for this kind of op-amp without output stage) is give by: P = (VDD VSS )(Ibias + I5 = I7 ) (17)

Which is a posynomial function of the design variables. Thus, we can impose an upper bound on power consumption P or take it as an objective to be minimized. After including dimension, symmetry, matching and bias constraints, let us now drive gain, bandwidth and stability (i.e. phase margin and poles) constraints. The transfer function of the two-stage OTA can be written as: H (s) = Av 1 (1 + s/p1 )(1 + s/p2 )(1 + s/p3 )(1 + s/p4 ) (18)

Here Av is the open loop voltage gain at dc, p1 is the dominant pole, p2 is the output pole, p3 is the mirror pole and p4 is the pole arising from the compensation circuit. The open-loop voltage gain derived from square-law model may be expressed as following: Av = ( gm6 2Cox gm2 )( )= gds2 + gds4 gds6 + gds7 (n + p )2 n p

W2 W6 L2 L6 I1 I7

(19)

which is a monomial function of the design variables. Next, to keep discussion short, the four poles in terms of small signal parameter gm , parasitics and load capacitances can be written as: p1 = gm1 Av Cc (20)

p2 =

gm6 C1 Cc + C1 CT L + Cc CT L

(21)

where C1 is the capacitance at the gate of M6 and given by, C1 = Cgs6 + Cdb2 + Cdb4 + Cgd2 + Cgd4 , and CT L , is the total capacitance at the output node and given as, CT L = CL + Cdb6 + Cdb7 + Cgd6 + Cgd7 . p3 = gm3 C2 (22)

where C2 is the capacitance at the gate of M3 and given by, C2 = Cgs3 + Cgs4 + Cdb1 + Cdb3 + Cgd1 . p4 = gm6 C1 (23)

Here, the dominant pole p1 is monomial, and the parasitic poles p2 , p3 and p4 are all inverse posynomials. Since the open-loop gain Av is a monomial, we may strictly constrain it to some desired value or impose some upper and lower bounds in the form: Amin Av Amax In almost all designs p1 will be dominant pole, so the 3dB bandwidth may be accurately dened as: 3dB = P1 = gm1 Av Cc (25) (24)

To ensure stability, the op-amp needs to satisfy phase margin, PM constraints given by [12]: PM = fU GB 2 fU GB fU GB 0.75( ) 2 p2 p3 p4 (26)

where fU GB is the unity gain frequency commonly known as unity gain bandwidth and is given by: fU GB = gm1 2Cc (27)

To ensure a minimum slew rate SRmin , we can impose following two constraints: Cc 1 , 2I1 SRmin Cc + CT L 1 I7 SRmin CM RR = 2Cox 2gm1 gm3 = (gds3 + gds1 )gds5 (n + p )p n p W1 W3 2 L1 L3 I5 (29) (28)

The common-mode rejection ratio (CMRR) can be approximated as:

Fig. 2.

Evaluating the sub-threshold slope factor n at VS = 0, note that n does not depend on VD .

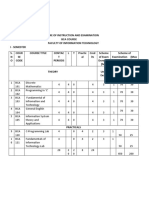

V. N UMERICAL RESULTS

In this section we showed the gm/Id curves generated from chartered 0.18um CMOS process to extract EKV model parameters, i.e. subthreshold slope factor n, specic current IS and threshold voltage VT o . These parameters are then used to drive W/L ratios and express them in posynomial form as shown below in equation (30): W Is 2 1 1 = = Is 21 n1 UT Cox 2 L 2nUT Cox Similarly, gm/Id may be expressed in terms of EKV model parameters as: gm 1 1 = Id nUT 1 + qF (31) (30)

VI. C ONCLUSIONS

In this project the analytical equations of the gm/Id model-based sizing methodology are being incorporated to optimally design a two stage operational amplier via geometric programming. The gm/Id model based equations have been expressed in posynomial forms as shown by (30) and (31). However, complete MATLAB code is not yet fully functional to generate the performance results for due comparison with other approaches. The good thing is that all these references take classical two-stage op-amp as a validation vehicle for unied and fair comparison. The fact that gm/Id based analytical model is valid in all regions of inversion assures a true globally optimal design by capturing the transistor behaviour with SPICE accuracy. Previous methods approximate the actual transistor behaviour with either simplied models (ignoring second order effects altogether)or try to minimize the resulting posynomial tting errors. Due to the poor posynomial t, standard GP can return grossly infeasible solutions. Previous researchers tend to minimize the tting error by either dividing the given problem in multiple subproblems or sequentially update the coarse rst-order model parameters with higher order simulations to nd a convergent and globally optimal solution but their claim of global optimality cannot be substantiated for the problem no longer

10

Fig. 3.

Dependence of threshold voltage VT 0 on VD at VS = 0, signifying the drain induced barrier lowering DIBL effect.

Fig. 4.

computing specic current at VS = 0, note the behaviour of channel length modulation with VD at different gate lengths.

remains single-shot convex. These methods not only become prohibitively slow with increasing circuit complexity but they also risk failure to even nd a feasible solution. Our approach rely on the physical meaning of gm/Id ratio and often locate the optimal solution in moderate

11

inversion region. Other approaches fail to converge owing to the breakdown or disconnect of both square-law and sub-threshold models in moderate inversion and the lack of any physical model applicable to moderate inversion region. This project try to explore a simple and accurate yet efcient method to overcome this challenge for robust optimization of analog circuit design.

R EFERENCES

[1] J. P. Fishburn and A. E. Dunlop, TILOS: A posynomial programming approach to transistor sizing, in Proc. Int. Conf. ComputerAided Design, 1985, pp. 326328. [2] S. S. Sapatnekar, V. B. Rao, P. M. Vaidya, and S. M. Kang, An exact solution to the transistor sizing problem for CMOS circuits using convex optimization, IEEE Trans. Computer-Aided Design, vol. 12, pp. 16211634, Nov. 1993. [3] M. M. Hershenson, S. P. Boyd, and T. H. Lee, CMOS operational amplier design and optimization via geometric programming. In Proc. First Intern. Workshop on Design of Mixed-Mode Integrated Circuits and Applications, pp. 15-18. 1997. [4] M. M. Hershenson, S. P. Boyd, and T. H. Lee, GPCAD: A tool for CMOS op-amp synthesis, in Proc. Int. Conf. Computer-Aided Design, 1998, pp. 296303. [5] Mandal, P.; Visvanathan, V., CMOS op-amp sizing using a geometric programming formulation, Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol.20, no.1, pp.22,38, Jan. 2001. [6] P. C. Maulik, L. R. Carley, and D. J. Allstot, Sizing of cell level analog circuits using constrained optimization techniques, IEEE J. Solid-State Circuits, vol. SC-28, pp. 233241, Mar. 1993. [7] Silveira, F.; Flandre, D.; Jespers, P.G.A., A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA, Solid-State Circuits, IEEE Journal of , vol.31, no.9, pp.1314,1319, Sep 1996. [8] Jintae Kim; Jaeseo Lee; Vandenberghe, L.; Yang, C.-K.K., Techniques for improving the accuracy of geometric-programming based analog circuit design optimization, Computer Aided Design, 2004. ICCAD-2004. IEEE/ACM International Conference on , vol., no., pp.863,870, 7-11 Nov. 2004. [9] S. Boyd, S.-J. Kim, L. Vandenberghe, and A. Hassibi, A Tutorial on Geometric Programming, Optimization and Engineering, 8(1):67-127, 2007. [10] Paul Jespers, The gm/ID Methodology, a Sizing Tool for Low-Voltage Analog CMOS Circuits: The Semi-Empirical and Compact Model Approaches. Springer Publishing Company, Incorporated, 2009. [11] Xin Li; Gopalakrishnan, P.; Yang Xu; Pileggi, L.T., Robust Analog/RF Circuit Design With Projection-Based Performance Modeling, Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol.26, no.1, pp.2,15, Jan. 2007. [12] Singh, A.K.; Ragab, K.; Lok, M.; Caramanis, C.; Orshansky, M., Predictable Equation-Based Analog Optimization Based on Explicit Capture of Modeling Error Statistics, Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol.31, no.10, pp.1485,1498, Oct. 2012.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Lab 5 PDFDocument3 pagesLab 5 PDFMuddassir AhmedNo ratings yet

- 3 - KV VHDL P1aDocument7 pages3 - KV VHDL P1aChandreshSinghNo ratings yet

- X PowderDocument122 pagesX PowderMoaaz AhmedNo ratings yet

- PHD ProposalDocument1 pagePHD ProposalMoaaz AhmedNo ratings yet

- 42-Improvement in Dielectric Properties of Low TemperatureDocument5 pages42-Improvement in Dielectric Properties of Low TemperatureMoaaz AhmedNo ratings yet

- Applying - Ms Progs in Foreign Unis & ScholarshipsDocument110 pagesApplying - Ms Progs in Foreign Unis & ScholarshipsMoaaz AhmedNo ratings yet

- Special Report Soi Wafer Technology For Cmos Ics: Robert Simonton President, Simonton AssociatesDocument11 pagesSpecial Report Soi Wafer Technology For Cmos Ics: Robert Simonton President, Simonton AssociatesMoaaz AhmedNo ratings yet

- Cold ShieldDocument1 pageCold ShieldMoaaz AhmedNo ratings yet

- Frequency Reuse, Cell Separation, and Capacity Analysis of VHF Digital Link Mode 3 TDMADocument23 pagesFrequency Reuse, Cell Separation, and Capacity Analysis of VHF Digital Link Mode 3 TDMAAshishch67No ratings yet

- CMOS Image Sensors 2010 ReportDocument5 pagesCMOS Image Sensors 2010 ReportMoaaz AhmedNo ratings yet

- 08 Antonio CerdeiraDocument57 pages08 Antonio CerdeiraMoaaz AhmedNo ratings yet

- How To Share Folders in Ubuntu & Access Them From Windows 7Document12 pagesHow To Share Folders in Ubuntu & Access Them From Windows 7Zenin EasaNo ratings yet

- Quickguide ProteusDocument7 pagesQuickguide ProteusdavidemirraNo ratings yet

- TOS EdtechDocument2 pagesTOS EdtechLeovhic Tomboc OliciaNo ratings yet

- Python Programming ppt0Document25 pagesPython Programming ppt0Fiker FikerwessenuNo ratings yet

- BcaDocument68 pagesBcaLoadingNo ratings yet

- Introduction To Management Science 8th Edition by Bernard W. Taylor IIIDocument58 pagesIntroduction To Management Science 8th Edition by Bernard W. Taylor IIIdsatyanegaraNo ratings yet

- ID of PG-2nd Year Student For Scholarship-9th September 2013Document18 pagesID of PG-2nd Year Student For Scholarship-9th September 2013nira365No ratings yet

- Cheat Sheet Hibernate Performance Tuning PDFDocument6 pagesCheat Sheet Hibernate Performance Tuning PDFdanielisozaki100% (1)

- Soalan Projek PSPD LatestDocument9 pagesSoalan Projek PSPD LatestAzlan AliNo ratings yet

- Waterfall To Agile GuideDocument14 pagesWaterfall To Agile GuideabdulonnetNo ratings yet

- Linear Programming Models in ServicesDocument14 pagesLinear Programming Models in ServicesHarsh GuptaNo ratings yet

- Mark ZukerbergDocument6 pagesMark ZukerbergAbhay Shankar BharadwajNo ratings yet

- PDFPCDocument27 pagesPDFPCmadsonengNo ratings yet

- Hamza Hanif DLD Lab #2Document6 pagesHamza Hanif DLD Lab #2Hamza KhanNo ratings yet

- Introduction To Excel Cooling Load Calculations Using RTS MethodDocument6 pagesIntroduction To Excel Cooling Load Calculations Using RTS MethodMelvyn Koa WingNo ratings yet

- OracleEloqua Emails UserGuide PDFDocument215 pagesOracleEloqua Emails UserGuide PDFAvinash BmNo ratings yet

- नामांकन म / Enrollment No: 146Document2 pagesनामांकन म / Enrollment No: 146Mukesh MistriNo ratings yet

- How To Interface A Microchip PIC MCU With A Hobby RC Servo, Paulo E. MerlotiDocument18 pagesHow To Interface A Microchip PIC MCU With A Hobby RC Servo, Paulo E. MerlotiMarco Medina100% (1)

- AIX Admin PDFDocument262 pagesAIX Admin PDFsourabhNo ratings yet

- Memory Management in SolarisDocument4 pagesMemory Management in Solarisjohnmerc1234No ratings yet

- Internet Communication in School PartnershipsDocument43 pagesInternet Communication in School PartnershipsDanish AzharNo ratings yet

- Sequence DetectorDocument25 pagesSequence DetectorYudish Nandraj KistoNo ratings yet

- Amount 2 Words - ASK TOM OracleDocument48 pagesAmount 2 Words - ASK TOM OraclesovitNo ratings yet

- Isilon Network Design Considerations PDFDocument44 pagesIsilon Network Design Considerations PDFDavid GiriNo ratings yet

- Data Structures With C NotesDocument118 pagesData Structures With C NotesDheeraj NambiarNo ratings yet

- VMware Technical Journal - Summer 2013Document64 pagesVMware Technical Journal - Summer 2013cheese70No ratings yet

- Twin Rotor Observer ImplementationDocument7 pagesTwin Rotor Observer Implementationtidjani86No ratings yet

- Mysql Connectivity Using Java ProcedureDocument67 pagesMysql Connectivity Using Java Procedureraji rameshNo ratings yet