Professional Documents

Culture Documents

Informe Polarizacion JFET

Uploaded by

Arley QuijanoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Informe Polarizacion JFET

Uploaded by

Arley QuijanoCopyright:

Available Formats

Laboratorio no. 4 Electrnica II Polarizacin FET polarizacin fija, auto polarizacin y polarizacin por divisin de tensin.

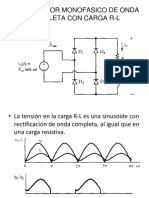

Los transistores de efecto de campo (FET) tiene ciertas caractersticas diferentes a los BJT como la forma de controlarlos ya que se controlan por el VGS, una impedancia de entrada alta, inmunidad a la radiacin, genera menos ruido, mayor estabilidad trmica y algunas desventajas como menos ancho de banda y ganancia menor a la del BJT. I. Objetivo general. que la tensin VGS debe ser negativa en un NJFET (positiva en un PJFET) que exige unos circuitos de polarizacin caractersticos para este tipo de dispositivos. En este apartado se presentan uno de los circuitos ms utilizados: polarizacin simple fija (Figura 153), se utiliza una fuente de tensin externa para generar una VGS<0.

Identificar las caractersticas de un transistor FET comparando los datos medidos y los de la tabla de datos suministrados por el fabricante. II. Objetivos especficos. - Utilizando la polarizacin fija encontrar los valores de IDSS (ID mximo) y VP (VGS mximo). - Graficar ID/VGS para encontrar los valores de IDQ (corriente ptima para el trabajo de trabajo del transistor) y VGSQ (voltaje ptimo para el trabajo de trabajo del transistor). - Realizar la auto polarizacin y comprobar que los datos encontrados de IDQ y VDSQ son los correctos.

POLARIZACIN MEDIANTE DIVISOR DE VOLTAJE. Tal como lo hicimos para el BJT, la polarizacin del JFET se puede realizar por divisor de voltaje.

III.

Marco terico:

CONFIGURACIN DE POLARIZACIN FIJA. Los circuitos bsicos que se utilizan para polarizar los BJT se pueden emplear para los MOSFET. EL JFET tiene el inconveniente de Su construccin bsica es exactamente la misma, pero el anlisis en DC es muy diferente. Puesto que, la corriente de la compuerta (IG) es de cero amperios mientras

que para el BJT la corriente de la base (IB) afecta los niveles de DC de la corriente y del voltaje tanto para el circuito de entrada como el de salida. Pues IB proporcionaba la relacin entre el circuito de entrada y el de salida mientras que el VGS har lo mismo para el JFET.

Cuando ID sea cero el valor de VGS ser igual a VG y cuando VGS sea cero, ID ser igual a la relacin VG sobre RS. De acuerdo a la figura No. 5.4, si RS se incrementa, entonces la recta cruzar por un valor menor de ID cuando VGS sea cero. Pero esto ocasionar niveles menores de estabilidad de los ID y ms negativos de VGS. VDS = VDD ID (RD + RS) (5.4) IR1 = IR2 = VDD / (R1 +R2) (5.5)

Polarizacin por divisor de voltaje de un JFET

Grfica de JFET polarizado por divisor de voltaje. Tomado de: http://datateca.unad.edu.co/contenidos/20141 9/contLinea/leccin_21_configuraciones_de_p olarizacin_del_fet.html

Entonces, realizando el anlisis de la misma forma que para un BJT, tenemos: VG = R2 * VDD / R1 + R2 (5.1) Luego, aplicando las leyes de Kirchhoff, y teniendo en cuenta que IR2 = IR1, entonces podremos encontrar el valor del voltaje de la compuerta: VG. VG VGS VRS = 0 (5.2) VGS = VG VRS Sustituyendo a VRS = IS * RS = IDRS, tenemos: VGS = VG IDRS (5.3) Los valores VG y RS los fija la red. Y la ecuacin No. 5.3 corresponde a una lnea recta en el plano de ID VGS.

IV.

Diagrama polarizacin fija.

elctrico

Medidas experimentales: Polarizacin fija. Auto polarizacin: La usamos para hallar los valores de IDSS y VP. Como la corriente en G debe ser muy pequea RG debe ser muy grande RG>500K. y basndonos en la hoja de datos asumimos IDSS=3.1mA y el voltaje VDS=10v. VDD=15v IDSS=3.1mA VDS=10v VD=5v VS=0v RD= VD/IDSS=5v/3.1mA=1.61Kohm VG=VGS+VS=VGS+0=VGS En esta configuracin encontramos que cuando VGS=0 ID es mximo (IDSS) y cuando IDSS=0 VGS es mximo (VP). ID=IDSS (1-(VGS/VP))

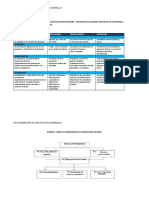

ID(mA) IDSS 3,1 2,37 1,74 1,21 0,775 0,435 0,193 0,048 0

VGS(v) 0 -0,2 -0,4 -0,6 -0,8 -1 -1,2 -1,4 -1,6

4 3 2 1 0 -2 -1.5 -1 -0.5 0

Medidas experimentales: Auto polarizacin.

Voltaje drenaje fuente(VDS)

Voltaje en fuente (VS)

V.

Diagrama elctrico polarizacin.

auto

Voltaje

de

drenaje

(VD) Ahora para encontrar los valores de IDQ y VDSQ tenemos que VGS=-IDRS tomamos un valor de ID y un valor de VGS trazamos una lnea y en el punto donde se intersecta la curva y la lnea queda IDQ y VDSQ.

En nuestro caso para ID=0 VGS=0 Para VGS=VP -ID=VGS/RS=-1.6v/1.5K=1,06mA

VG=VGS+IDRS VG= -0,88V+1,5V=0,62V VG=VDD (RG2/(RG1+RG2)) VGRG1+VGRG2=VDDRG2 RG1=VDDRG2-VGRG2/VG RG2=1Mohm RG1=1Mohm (15V-0,69)/O,62 RG1=23,19Mohm Medidas experimentales: Trazamos la lnea y encontramos IDQ=0.65mA y VDSQ=-0.88v. Diseo auto polarizacin: VDD=15v, VDS=10v, VS=VDD/10=1,5v, VS=3,5v, VP=-1,6v, IDSS=3,1mA, IDQ=0.65mA y VDSQ=-0,88v. IS=ID RD=VD/IDQ=5,38Kohm RS=VS/IDQ=2,30kohm VI. Diagrama elctrico polarizacin por divisin de tencin. Polarizacin por divisor de tencin.

Voltaje drenaje-fuente (VDS)

Diseo polarizacin por divisin de tencin: VDD=15v, VDS=10v, VS=VDD/10=1,5v, VS=3,5v, VP=-1,6v, IDSS=3,1mA, IDQ=0.65mA y VDSQ=-0,88v. IS=ID RD=VD/IDQ=5,38Kohm RS=VS/IDQ=2,30kohm

Corriente de drenaje (ID) Voltaje drenaje (VD)

VII. Voltaje fuente (VS) VIII. -

Conclusiones:

Bibliografas.

Circuitos micro electrnicos anlisis y diseo RASHID.

You might also like

- Laboratorio de Polarizacion Del Fet PDFDocument14 pagesLaboratorio de Polarizacion Del Fet PDFJuan Carlos Gonzales ArosteNo ratings yet

- Ejercicios 4 I 2019 503Document3 pagesEjercicios 4 I 2019 503Miguel Angel Lara NisttahuzNo ratings yet

- TransistoresIIDocument5 pagesTransistoresIILuis Enrique PichardoNo ratings yet

- Preguntas de La Guia 1 de DiodosDocument2 pagesPreguntas de La Guia 1 de Diodosedwinri100% (2)

- CVF Convertidores de voltaje a frecuenciaDocument3 pagesCVF Convertidores de voltaje a frecuenciaDaniel HolguínNo ratings yet

- Curva Caracteristica y Parametros Del UJTDocument12 pagesCurva Caracteristica y Parametros Del UJTCésar Augusto Núñez Donado0% (3)

- Filtro Por CondensadorDocument13 pagesFiltro Por CondensadorYesid Salcedo JimenezNo ratings yet

- Informe Lab - 2 ElectronicaDocument11 pagesInforme Lab - 2 ElectronicaJUAN JOSE RODRIGUEZ VICTORIANo ratings yet

- Circuitos Recortadores de OndaDocument3 pagesCircuitos Recortadores de OndaInés MasaquizaNo ratings yet

- Amplificadores de Potencia Ejercicios 22Document30 pagesAmplificadores de Potencia Ejercicios 22Fernando RubioNo ratings yet

- Amplificadores Multietapa-Breidi SalgadoDocument21 pagesAmplificadores Multietapa-Breidi Salgadocleverman1No ratings yet

- Amplificador PDT-circuito análisisDocument1 pageAmplificador PDT-circuito análisisjoseguitarNo ratings yet

- Rectificador monofásico onda completa carga RL-generadorDocument14 pagesRectificador monofásico onda completa carga RL-generadorANA BELEN MORENO CORDOVANo ratings yet

- Rectificación Monofásica de Conmutación Natural Sin FiltrosDocument18 pagesRectificación Monofásica de Conmutación Natural Sin FiltrosVickFrNo ratings yet

- Simulacion Armonicos ProteusDocument5 pagesSimulacion Armonicos ProteusDARIELNo ratings yet

- Definicion Espejo de CorrienteDocument26 pagesDefinicion Espejo de Corrienteman soloNo ratings yet

- Laboratorio #1Document6 pagesLaboratorio #1Hosmmer RojasNo ratings yet

- Analisis Del Transistor BJT en Pequena S PDFDocument7 pagesAnalisis Del Transistor BJT en Pequena S PDFSergio MirandaNo ratings yet

- Rectificadores y FiltrosDocument28 pagesRectificadores y FiltrosVictor Manuel CanahuiriNo ratings yet

- Voltimetro LuminosoDocument14 pagesVoltimetro LuminosoGuillermoOlea0% (1)

- Amplificador de Dos EtapasDocument3 pagesAmplificador de Dos EtapasJuanse Rosero100% (1)

- Diseño Oscilador ColpittsDocument6 pagesDiseño Oscilador ColpittsKARLA LILIANA PENAGOS VIATELANo ratings yet

- Diseño de Fuente de DC Con Filtro LCDocument6 pagesDiseño de Fuente de DC Con Filtro LCХьюго Хоакин Кость0% (1)

- Rectificación Media Onda y Ecuaciones. 2021Document32 pagesRectificación Media Onda y Ecuaciones. 2021Jorge AngelNo ratings yet

- Informe 3 Jfet y MosfetDocument8 pagesInforme 3 Jfet y MosfetapusiqNo ratings yet

- Laboratorio 06 - QPSKDocument11 pagesLaboratorio 06 - QPSKMichael HughesNo ratings yet

- Fuente de Voltaje Regulable Con LM317HDocument6 pagesFuente de Voltaje Regulable Con LM317HJose Efren Rojas AlmanzaNo ratings yet

- Amplificadores MultietapaDocument4 pagesAmplificadores MultietapaEdixon Leon0% (1)

- SCR en Ac y DCDocument6 pagesSCR en Ac y DCManu AceNo ratings yet

- Filtro Pasa BajoDocument9 pagesFiltro Pasa BajoCristian PazmiñoNo ratings yet

- Transistor Como Amplificador de OndasDocument4 pagesTransistor Como Amplificador de OndastomkitoNo ratings yet

- Fuente de Voltaje (Mejia)Document18 pagesFuente de Voltaje (Mejia)ofcc60No ratings yet

- Sistemas de medición y elementos finales de controlDocument428 pagesSistemas de medición y elementos finales de controlAlexis ArellanoNo ratings yet

- SD Hoja Guia 9 2020BDocument2 pagesSD Hoja Guia 9 2020BAlexander LaraNo ratings yet

- Experimento #2 FiltrosDocument11 pagesExperimento #2 FiltrosArturo CarlosNo ratings yet

- Práctica 5 Colector ComunDocument14 pagesPráctica 5 Colector ComunRamiro Avalos VegaNo ratings yet

- Ejercicios Propuestos Unidad I ELCIIDocument3 pagesEjercicios Propuestos Unidad I ELCIIPacoVivasNo ratings yet

- Informe Rectificadores ControladosDocument9 pagesInforme Rectificadores ControladosGiovanny LduNo ratings yet

- Laboratorio 4-Polarización de Un JFETDocument3 pagesLaboratorio 4-Polarización de Un JFETEfrain VernazaNo ratings yet

- Guía completa sobre PWM: qué es, cómo funciona y aplicacionesDocument3 pagesGuía completa sobre PWM: qué es, cómo funciona y aplicacionesAxel AlmeidaNo ratings yet

- Filtro Inductivo y Filtro PiDocument6 pagesFiltro Inductivo y Filtro PiSalvador Romero0% (1)

- Polarizacion Del FetDocument7 pagesPolarizacion Del Fetpedro aparicioNo ratings yet

- Fuente RegulableDocument6 pagesFuente RegulableIsrael R HdzNo ratings yet

- Trabajo en ProteusDocument9 pagesTrabajo en ProteusMICHILOT SULCA CHRISTIAN ANTONIONo ratings yet

- Circuitos de Deteccion de Cruce Por Cero Con Acondicionamiento de SeñalDocument2 pagesCircuitos de Deteccion de Cruce Por Cero Con Acondicionamiento de SeñalSamuel Chimborazo100% (1)

- El Transistor Como AmplificadorDocument4 pagesEl Transistor Como AmplificadorMARTIN RODOLFO LIZOLA GOMEZNo ratings yet

- Introduccion ACII OndasDocument18 pagesIntroduccion ACII OndasSebastián SalamancaNo ratings yet

- Rectificador de Onda CompletaDocument13 pagesRectificador de Onda CompletaEquipo100% (1)

- Teoría de Muestreo, Discretización, y Reconstrucción de SeñalesDocument10 pagesTeoría de Muestreo, Discretización, y Reconstrucción de SeñalesEdward Javier PatiñoNo ratings yet

- 3 Filtrado y RizadoDocument5 pages3 Filtrado y Rizadosimon valencia lozano100% (1)

- Filtrado Con CapacitorDocument3 pagesFiltrado Con CapacitorEsner CamargoNo ratings yet

- P11 Circuitos Resonantes SerieDocument25 pagesP11 Circuitos Resonantes SerieromoNo ratings yet

- Laboratorio 2: Espejo Sencilla de Corriente + WilsonDocument4 pagesLaboratorio 2: Espejo Sencilla de Corriente + WilsonCarlos Hortúa CalderónNo ratings yet

- Ensayo Tipos de OsciladoresDocument17 pagesEnsayo Tipos de OsciladoresMiguel Angel Flores MojicaNo ratings yet

- Método de detección de cero mediante puente de WheatstoneDocument6 pagesMétodo de detección de cero mediante puente de WheatstoneTomás AlejandroNo ratings yet

- Informe 04 - Amplificador Bipolar Clase AB. Andrés Duque PDFDocument3 pagesInforme 04 - Amplificador Bipolar Clase AB. Andrés Duque PDFJose Daniel Maldonado0% (1)

- Informe Polarizacion JFETDocument6 pagesInforme Polarizacion JFETLaura Gómez.No ratings yet

- Clase 4. Electronica 1 Cap6 FETDocument22 pagesClase 4. Electronica 1 Cap6 FETHersson D AlemanNo ratings yet

- Práctica 8Document7 pagesPráctica 8Daniel González RojasNo ratings yet

- JFETDocument35 pagesJFETJuan Báez Rebollo0% (1)

- Curso de Oleoturismo JaenDocument2 pagesCurso de Oleoturismo JaenacarpiodNo ratings yet

- MediosDocument10 pagesMediosJohanna JimenezNo ratings yet

- Barcelona LauraDocument21 pagesBarcelona LauracfescuredoNo ratings yet

- 2-Manual Operador de ToursDocument69 pages2-Manual Operador de ToursSonny Sanchez PerezNo ratings yet

- Maquinas AsincronasDocument89 pagesMaquinas AsincronasOmar Alamilla DavilaNo ratings yet

- Asientos de Ajuste o Ajuste Contable 18 Nov Clase 27Document3 pagesAsientos de Ajuste o Ajuste Contable 18 Nov Clase 27Katerin Cristina Zapata MaciasNo ratings yet

- Cultivo de MangoDocument31 pagesCultivo de MangoArmando MacalopuNo ratings yet

- TRD Agua y Alcantarillado Perfil OrcotunaDocument21 pagesTRD Agua y Alcantarillado Perfil OrcotunaMilton BarzaNo ratings yet

- Certificado de Deposito y Bono de PrendaDocument15 pagesCertificado de Deposito y Bono de PrendaFeyo Vega100% (1)

- 2009 Carpeta de Trabajos Practicos Integrada UBA - UNLDocument128 pages2009 Carpeta de Trabajos Practicos Integrada UBA - UNLAriel Horacio Ferrari44% (9)

- Teoria de Orbitales MolecularesDocument13 pagesTeoria de Orbitales MolecularesDalia Soria100% (1)

- Com 0484, 271105 Primer Informe de Gobierno de Eugenio Hernández FloresDocument2 pagesCom 0484, 271105 Primer Informe de Gobierno de Eugenio Hernández FloresEugenio Hernández100% (1)

- Visita Al Museo Casa de La Moneda (1) .Docx2.docx FinalDocument11 pagesVisita Al Museo Casa de La Moneda (1) .Docx2.docx FinalJerykson Camilo Aunta VasquezNo ratings yet

- Lista Chequeo Constructora 2016Document6 pagesLista Chequeo Constructora 2016Olivia Isabel Palma ZuritaNo ratings yet

- Demanda laboral por despido sin causaDocument2 pagesDemanda laboral por despido sin causaantonellarey056No ratings yet

- Proyecto de Educ VialDocument3 pagesProyecto de Educ VialjohanapatriciapachecNo ratings yet

- Estrategias y Tatica de Marketing para Cada Etapa Del Ciclo de Vida Del ProductoDocument2 pagesEstrategias y Tatica de Marketing para Cada Etapa Del Ciclo de Vida Del ProductoJuan Karlos Chucuya AguilarNo ratings yet

- 8 Párrafo Comparativo (EXPOSICION ORAL)Document1 page8 Párrafo Comparativo (EXPOSICION ORAL)ericajlNo ratings yet

- Contador público transacciones abrilDocument6 pagesContador público transacciones abrilWendy MaradiagaNo ratings yet

- 1-010-Lucia Solis SullcahuamanDocument24 pages1-010-Lucia Solis Sullcahuamanalexander poalNo ratings yet

- Americna Glass ProductsDocument41 pagesAmericna Glass ProductsIvan Palacio Reyes100% (1)

- Contrato de Compraventa de Un TerrenoDocument1 pageContrato de Compraventa de Un TerrenoPaul GrefaNo ratings yet

- Ccu ChileDocument5 pagesCcu ChileVictor Manuel Céspedes Durán100% (1)

- 1 TDR Ficha Técnica Mejoramiento y Ampliacion Del Sistema de Agua Potable y Saneamiento en Las Comunidades de Jardin de Huerta y Union Santa Maria, Distrito de ChupaDocument17 pages1 TDR Ficha Técnica Mejoramiento y Ampliacion Del Sistema de Agua Potable y Saneamiento en Las Comunidades de Jardin de Huerta y Union Santa Maria, Distrito de ChupaJohn YucraNo ratings yet

- Factura 145Document2 pagesFactura 145AlejandroCavicchioliNo ratings yet

- Prueba de Vacío Dinámico de un Motor C.IDocument17 pagesPrueba de Vacío Dinámico de un Motor C.IEdwin RomaNo ratings yet

- Mapa ConceptualDocument2 pagesMapa ConceptualHENRY EDUARDO100% (6)

- Laguna de HuaypoDocument5 pagesLaguna de HuaypoJhonatan Tacuri MesccoNo ratings yet

- Matriz de Marco LógicoDocument10 pagesMatriz de Marco LógicoMagalyNo ratings yet