Professional Documents

Culture Documents

H-Bridge 5 Level Inverter Using PWM Technique

Uploaded by

Kolan Vamshi Kiran ReddyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

H-Bridge 5 Level Inverter Using PWM Technique

Uploaded by

Kolan Vamshi Kiran ReddyCopyright:

Available Formats

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CHAPTER 1 INTRODUCTION

The inverters which produce an output voltage or a current with levels either 0 or +V or -V are known as two level inverters. In high-power and high-voltage applications these two-level inverters however have some limitations in operating at high frequency mainly due to switching losses and constraints of device rating. This is where multilevel inverters are advantageous. Increasing the number of voltage levels in the inverter without requiring higher rating on individual devices can increase power rating. The unique structure of multilevel voltage source inverters allows them to reach high voltages with low harmonics without the use of transformers or series-connected synchronizedswitching devices. The harmonic content of the output voltage waveform decreases significantly The three level inverter offers several advantages over the more common two level inverter. As compared to two level inverters, three level inverters have smaller output voltage steps that mitigate motor issues due to long power cables between the inverter and the motor. These issues include surge voltages and rate of voltage rise at the motor terminals and motor shaft bearing currents. In addition, the cleaner output waveform provides an effective switching frequency twice that of the actual switching frequency. Should an output filter be required, the components will be smaller and less costly than for an equivalent rated two level inverter. Most often the NPC inverter is used for higher voltage inverters. Advantages of this multilevel approach include good power quality, good electromagnetic compatibility (EMC), low switching losses, and high voltage capability. The main disadvantages of this technique are that a larger number of switching semiconductors are required for lower-voltage systems and the small voltage steps must be supplied on the dc side either by a capacitor bank or isolated voltage sources. The first topology introduced was the series H-bridge design.

AIET

EEE

Page 1

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CHAPTER 2 INVERTER

2.1. INTRODUCTION: DEFINITION: Converts DC to AC power by switching the DC input voltage (or current) in a pre-determined sequence so as to generate AC voltage (or current) output.

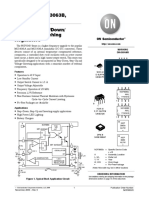

Fig.2.1. General block diagram of Inverter Based on their operation the inverters can be broadly classified into

Voltage Source Inverters (VSI) Current Source Inverters (CSI)

Fig.2.2. Block Diagram of VSI and CSI Inverters

AIET

EEE

Page 2

CASCADED H-BRIDGE MULTI LEVEL INVERTER

VSI: A voltage source inverter is one where the independently controlled ac output is a voltage waveform. Voltage source inverter or voltage fed inverter is one in which the dc source has small or negligible impedance. In other words the voltage source inverter has stiff dc voltage source at its input terminals. CSI: A current source inverter is one where the independently controlled ac output is a current waveform. A current fed inverter or current source inverter is fed with adjustable current from a DC source, DC source of high impedance. On the basis of connections of semiconductor devices, inverters are classified as Bridge inverters Series inverters Parallel inverters

Some industrial applications of inverters are for adjustable- speed ac drives, induction heating, stand by air-craft power supplies, UPS (uninterruptible power supplies) for computers, hvdc transmission lines etc.

AIET

EEE

Page 3

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CHAPTER 3 MULTILEVEL INVERTERS

3.1. Introduction Inverter: Inverters convert DC power into AC power through waves called either sine waves or modified sine waves. Sine waves are the waves that are typically found in power from a power plant. Modified sine waves are made to simulate sine waves. Inverters with modified sine waves work well for backup power in houses and are much less expensive. Although there are several types of inverters, all standard inverters use only one switch, or in other words, one power circuit. Multilevel Inverter: Multilevel inverters are a a source of high power, often used in industrial applications and can use either sine or modified sine waves. Instead of using one converter to convert an AC current into a DC current, a multilevel inverter uses a series of semiconductor power converters (usually two to three) thus generating higher voltage. While with an inverter you would transfer energy with the flip of one switch, with a multilevel inverter you would have to flip several switches, each switch requiring a circuit. These multiple switches and circuits usually make multilevel inverters more expensive than inverters. Numerous industrial applications have begun to require higher power apparatus in recent years. Some medium voltage motor drives and utility applications require medium voltage and megawatt power level. For a medium voltage grid, it is troublesome to connect only one power semiconductor switch directly. As a result, a multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations. A multilevel converter not only achieves high power ratings, but also enables the use of renewable energy sources. Renewable energy sources such as photovoltaic, wind, and fuel cells can be easily interfaced to a multilevel converter system for a high power application The concept of multilevel converters has been introduced since 1975. The term multilevel began with the three-level converter. Subsequently, several multilevel converter topologies have been developed.

AIET

EEE

Page 4

CASCADED H-BRIDGE MULTI LEVEL INVERTER

However, the elementary concept of a multilevel converter to achieve higher power is to use a series of power semiconductor switches with several lower voltage dc sources to perform the power conversion by synthesizing a staircase voltage waveform. Capacitors, batteries, and renewable energy voltage sources can be used as the multiple dc voltage sources. The commutation of the power switches aggregate these multiple dc sources in order to achieve high voltage at the output; however, the rated voltage of the power semiconductor switches depends only upon the rating of the dc voltage sources to which they are connected. A multilevel converter has several advantages over a conventional two-level converter that uses high switching frequency pulse width modulation (PWM). The attractive features of a multilevel converter can be briefly summarized as follows. Staircase waveform quality: Multilevel converters not only can generate the output voltages with very low distortion, but also can reduce the dv/dt stresses; therefore electromagnetic compatibility (EMC) problems can be reduced. Common-mode (CM) voltage: Multilevel converters produce smaller CM voltage; therefore, the stress in the bearings of a motor connected to a multilevel motor drive can be reduced. Furthermore, CM voltage can be eliminated by using advanced modulation strategies such as that proposed in . Input current: Multilevel converters can draw input current with low distortion. Switching frequency: Multilevel converters can operate at both fundamental switching frequency and high switching frequency PWM. It should be noted that lower switching frequency usually means lower switching loss and higher efficiency. Unfortunately, multilevel converters do have some disadvantages. One particular disadvantage is the greater number of power semiconductor switches needed. Although lower voltage rated switches can be utilized in a multilevel converter, each switch requires a related gate drive circuit. This may cause the overall system to be more expensive and complex. Plentiful multilevel converter topologies have been proposed during the last two decades.

AIET

EEE

Page 5

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Contemporary research has engaged novel converter topologies and unique modulation schemes. Moreover, three different major multilevel converter structures have been reporter in the literature: cascaded H-bridges converter with separate dc sources, diode clamped (neutralclamped), and flying capacitors (capacitor clamped). Moreover, abundant modulation techniques and control paradigms have been developed for multilevel converters such as sinusoidal pulse width modulation (SPWM), selective harmonic elimination (SHE-PWM), space vector modulation (SVM), and others. In addition, many multilevel converter applications focus on industrial medium-voltage motor drives, utility interface for renewable energy systems, flexible AC transmission system (FACTS), and traction drive systems.

AIET

EEE

Page 6

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CHAPTER 4 Types of Multi-level Inverters

4.1. Introduction The general structure of multi-level converter is to synthesize a near sinusoidal voltage from several levels of dc voltages, typically from capacitor voltage sources. As number of levels increases, the synthesized output waveform has more steps, which provides a staircase wave that approaches a desired waveform. Also, as steps are added to waveform, the harmonic distortion of the output wave decreases, approaching zero as the number of voltage levels increases. The Multi-level inverters can be classified into three types. Diode - clamped Multi-level inverter Flying - capacitor Multi-level inverter

Cascade Multi-level inverter

4.2. Diode- clamped Multi - level inverter A diode - clamped (m-level) inverter (DCMLI) typically consists of (m-1) capacitor on the dc bus and produces m levels on the phase voltages. Figure shows full bridge fivelevel diode clamped converter. The numbering order of the switches is Sa1, Sa2, Sa3, Sa4, The dc the bus voltage consists of four capacitors C1, C2, C3, and C4. voltage across each capacitor is V dc/4, and each Sa1, Sa2, Sa3, Sa4. For a dc

voltage Vdc,

devices voltage stress is limited to one capacitor voltage level V dc/4 through clamping diodes. An m-level inverter leg requires (m-1) capacitors, 2(m-1) switching devices and (m-1) X (m-1) clamping diodes. Principle of operation: To produce a stair case output, let us consider only one leg of five level inverter, as shown in Figure 4.1. A single phase bridge with one leg Diodeclamped Multi - level inverter

AIET

EEE

Page 7

CASCADED H-BRIDGE MULTI LEVEL INVERTER

The steps to synthesize the five level voltages are as follows a) Voltage level Van= V dc; turn on all upper switches S1, S2 , S3 and S4. b) Voltage level Van= V dc/2, turn on the switches S2, S3, S4 and S1. c) Voltage level Van= 0, turn on the switches S3, S4, S1 and S2. d) Voltage level Van= - V dc/2 turn on the switches S4, S1, S2, S3. e) Voltage level Van= - V dc; turn on all lower switches S1, S2 ,S3 and S4.

Fig.4.1.Shows Diode- clamped Multi - level inverter Advantages:

AIET

When the number of levels is high enough , the harmonic content is Low enough to avoid the filters. Inverter efficiency is high because all devices are switching at the Fundamental frequency. The control method is simple.

EEE Page 8

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Disadvantages: Excessive clamping diodes are required when the number of levels is high. It is difficult to control the real power flow of the individual Converter in multi-

level converter system

4.3. Flying capacitor multilevel inverter: A single phase full bridge n-level inverter based on flying capacitors. Each phase like has an identical structure. Assuming that each capacitor has the same voltage rating, the series connection of the capacitors indicates the voltage level between calming points. All phase legs share the DC link capacitors C1 to Cn. Principle of operation: To produce a staircase output voltage, the switching instants of MOSFETS will be shown below. 1 )Voltage level Van = Vdc/2, turn on all upper switches S1 - S4 .

2) Voltage level Van = Vdc/4, there are three combinations. Turn on switches S1, S2, S3 and S1. (Van = Vdc/2 of upper C4s - Vdc/4 of C1s).

Turn on switches S2, S3, S4 and S4. (Van =3Vdc/4 of upper C3s - Vdc/2 of C4s). Turn on switches S1, S3, S4 and S3. (Van= Vdc/2 of upper C4s -3Vdc/4 or C3s + Vdc/2 of upper C2). 3) Voltage level Van= 0, turn on upper switches S3, S4, and lower switchS1, S2.

AIET

EEE

Page 9

CASCADED H-BRIDGE MULTI LEVEL INVERTER

4) Voltage level Van= -Vdc/4, turn on upper switch S1 and lower switchesS1, S2 and S3. 5) Voltage level Van= -Vdc/2, turn on all lower switches S1, S2, S3 and S4.

Fig.4.2. Shows Flying capacitor multilevel inverter Advantages: a) Large amount of storage capacitors can provide provide capabilities during Power outages.

b) These inverters levels. c) With the

switch combination redundancy for balancing different voltage

number of voltages levels increased, the harmonic content is low enough to

avoid the filters. d) Both real and reactive power flow can be controlled.

AIET

EEE

Page 10

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Disadvantages: a) An excessive number of storage capacitors are required when the Number of levels is the bulky power capacitors

high. High-level inverters are more difficult to Package with and expensive too.

b) The inverter control can be very complicated and losses are high for real power Transmission.

switching Frequency and

switching

4.4. Cascaded Multi-level inverter: A relatively new converter structure called Cascaded Multi-level inverter, can avoid extra clamping diodes or voltage balancing capacitors. The converter topology used here is based on the series connection of single phase inverters with separate DC sources. The different topologies by with H-bridge are designed are: Cascaded H-bridge Hybrid H-bridge

4.4.1. Hybride H-bridge: Figure 4.3. shows the basic block of cascade H-bridge Multi-level inverter and its associated switching instants. As shown its consists of four power devices and a

DC source. The switching states for four power devices are constant i.e., When S1 is on, S2 cannot be on and vice versa. Similarly with S3 and S4.

AIET

EEE

Page 11

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Fig.4.3. Shows Hybride H-Bridge 4.4.2. Cascaded H-bridge: A hybrid H-bridge inverter consists of a series of H-bridge inverter units. The general function of this Multi-level inverter is to synthesize a desired voltage form several DC sources (SDCSs). Each SDCS is connected to an H-bridge inverter. The AC

terminal voltages of different level inverters are connected in series. Unlike diode clamp or flying capacitors inverters the hybrid H-bridge inverter does not require any voltage clamping diodes or voltage-balancing capacitors.

Fig.4.4. Shows Cascaded H-bridge

AIET

EEE

Page 12

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Advantages: 1. Requires the least number of components among all multi-level Converter to achieve the same number voltage levels. 2. Modularized circuit layout and packaging is possible because each Level has the structure, and there are no extra clamping diodes or Voltage balancing capacitors. 3.Soft switching can be used in this structure to avoid bulky and loss resistor, capacitor, diode, snubbers.

Disadvantages: The limitation of h-bridge is the provision of the isolated power supply for each

individual H-bridge cell. For applications, where, isolated power supply cannot be provided, the requirement of capacitors and complexity of its control increases as the number of voltage levels increases, which restricts its applications.

4.5. Applications: 1. Reactive power compensator: When power, the phase voltage a Multi-level inverter draws pure reactive

and current are 90

degrees apart, and the capacitor charge and

discharge can be balanced. Such a converter, when serving for reactive power compensation is called Static Var Generator. The multi-level structure allows the entire converter to be

directly connected to a high voltage distribution or transmission system without the need of a step down transformer. All the three Multi - level inverters can be used in reactive power compensation without having voltage unbalanced problem. 2. Back to Back intertie: Inter connection of two Multi-level inverter with a DC link in between is called as a Back to back intertie. In this type of circuit the left hand side converter servers as rectifier, while the right hand side serves as the

AIET

EEE

Page 13

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Inverter. The purpose of the back to back intertie is to connect to synchronous systems of different frequencies. It can be treated as a) Frequency connector b) Phase shifter c) A power flow controller. 3. Utility compatible adjustable speed drives: An speed drives requires unity power ideal utility compatible adjustable

factor, negligible harmonics and high efficiency. By

extended the back to back intertie, the multi-level inverter can be used for a utility compatible adjustable speed drive with the input as constant frequency AC source and the output has the variable frequency AC source. The major differences when using as a utility compatible adjustable speed drives and for back to back intertie, are the control design and size of capacitor.

4.6. CONCLUSION In this chapter design of multi-level inverter discussed in detail, relevant waveforms are presented and analyzed. From this analysis it can be concluded that multilevel inverters offer a low total harmonic distortion and high efficiency. Multi-level inverters are suitable for high voltages and high current application and also have higher efficiency because the devices can be switched at a lower frequency

AIET

EEE

Page 14

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CHAPTER 5 PULSE MODULATION SCHEMES

5.1. Different Pulse Modulation Schemes 5.1.1. PULSE AMPLITUDE MODULATION Pulse Amplitude Modulation refers to a method of carrying information on a train of pulses, the information being encoded in the amplitude of pulses. In other words the pulse amplitude is modulated according to the varying amplitude of analog signal. 5.1.2. PULSE WIDTH MODULATION Pulse Width Modulation refers to a method of carrying information on a train of pulses, the information being encoded in the width of the pulses. The pulses have constant amplitude but their duration varies in direct proportion to the amplitude of analog signal. 5.1.3. PULSE POSITION MODULATION The amplitude and width of the pulse is kept constant in the system. The position of each pulse, in relation to the position of a recurrent reference pulse, is varied by each instantaneous sampled value of the modulating wave. PPM has the advantage of requiring constant transmitter power since the pulses are of constant amplitude and duration. 5.1.4. PULSE CODE MODULATION To obtain PCM from an analog waveform at the source (transmitter), the analog signal amplitude is sampled at regular time intervals. The sampling rate (number of samples per second), is several times the maximum frequency of the analog waveform. The amplitude of the analog signal at each sample is rounded off to the nearest binary level (quantization).

AIET

EEE

Page 15

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Fig.5.1. (a) Analog signal, s (t). (b) Pulse-amplitude modulation. (c) Pulse-width modulation. (d) Pulse position modulation The Number of levels is always a power of 2 (4, 8, 16, 32, 64,). These numbers can be represented by two, three, four, five, six or more binary digits.PCM is a general scheme for transmitting analog data in a digital and binary way, independent of the complexity of the analog waveform. With PCM all forms of analog data like video, voice, music and telemetry can be transferred. 5.2. ADVANTAGES OF PWM The output voltage control is easier with PWM than other schemes and can be achieved without any additional components. The lower order harmonics are either minimized or eliminated altogether. The filtering requirements are minimized as lower order harmonics are eliminated and higher order harmonics are filtered easily. It has very low power consumption. The entire control circuit can be digitized which reduces the susceptibility of the circuit to interference.

AIET

EEE

Page 16

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CHAPTER 6 PULSE WIDTH MODULATION

PWM is the most popular method for producing a controlled output for inverters. They are quite popular in industrial applications.

Fig.6.1. sine modulated and unmodulated signal 6.1. LINEAR MODULATION The simplest method is to vary the ON time proportionally with the modulating signal. Its advantage is that it is easy to demodulate. The modulating or information signal can be recovered by low pass filtering. A low frequency (fm) sine wave modulating the width of a fixed frequency (fs) pulse train is shown in the figure 3. As can be seen a low pass filter can extract the modulating signal (fm).

6.2. Fig.Linear Modulation

AIET

EEE

Page 17

CASCADED H-BRIDGE MULTI LEVEL INVERTER

6.2. SAW TOOTH PWM A fixed frequency PWM can be generated by comparing with a linear slope waveform like a saw tooth waveform. As seen in the figure the output goes high when the sine wave amplitude is greater than saw tooth. It can be achieved by comparator with logic HIGH when non-inverting input is greater than the inverting one.

Fig.6.3. Saw Tooth PWM

AIET

EEE

Page 18

CASCADED H-BRIDGE MULTI LEVEL INVERTER

6.3. REGULAR SAMPLED PWM This scheme works by generating a switching edge at the intercept of carrier and modulating signal. In the figure 5 intercepts of sampled sine values with the triangular wave gives the edges of the pulses.

Fig.6.4. Regular Sampled PWM

AIET

EEE

Page 19

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CHAPTER 7 SINGLE PHASE PWM INVERTERS

In many industrial applications, to control the output voltage of the inverters is necessary for the following reasons To adjust with variations of dc input voltage To regulate voltage of inverters To satisfy the contain volts and frequency control requirement

There are various techniques to vary the inverter gain. The most efficient method of Controlling the gain (and output voltage) is to incorporate pulse width modulation (PWM) Control within the inverters. The commonly used techniques are a) Single Pulse width Modulation b) Multiple Pulse width Modulation c) Sinusoidal Pulse width Modulation d) Modified sinusoidal Pulse width Modulation e) Phase-displacement control. The PWM techniques given above vary with respect to the harmonic content in their output voltages. 7.1. SINGLE PULSE WIDTH MODULATION In this control, theres only one pulse per half cycle and the width of the pulse is varied to control the inverter output. The gating signals are generated by comparing a rectangular reference signal of the amplitude Ar with triangular carrier wave of amplitude Ac, the frequency of the carrier wave determines the fundamental frequency of output voltage. By varying Ar from 0 to Ac, the

AIET

EEE

Page 20

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Pulse width can be varied from 0 to 100 percent. The ratio of Ar to Ac is the control variable and defined as the modulation index. 7.2. MULTIPLE PULSE WIDTH MODULATION The harmonic content can be reduced by using several pulses in each half cycle of output voltage. The generation of gating signals for turning ON and OFF transistors by comparing a reference signal with a triangular carrier wave. The frequency Fc, determines the number of pulses per half cycle. The modulation index controls the output voltage. This type of modulation is also known as uniform pulse width modulation (UPWM). 7.3. SINUSOIDAL PULSE WIDTH MODULATION Instead of, maintaining the width of all pulses of same as in case of multiple pulse width modulation, the width of each pulse is varied in proportion to the amplitude of a sine wave evaluated at the centre of the same pulse. The distortion factor and lower order harmonics are reduced significantly. The gating signals are generated by comparing a sinusoidal reference signal with a triangular carrier wave of frequency Fc. The frequency of reference signal Fr, determines the inverter output frequency and its peak amplitude Ar, controls the modulation index M, and rms output voltage Vo. The number of pulses per half cycle depends on carrier frequency.

AIET

EEE

Page 21

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CHAPTER 8 SIMULATION OF MULTI-LEVEL INVERTERS

Introduction: The multi-level inverter system when is a very promising device in AC power drives

both reduced content and high power are required. Up to now several multi-

level topologies have been introduced. The main topologies are diode clamped inverter, flying capacitor inverter, hybrid H-bridge inverter in order to generate a high voltage waveform using low voltage devices. In this chapter, we are considering the simulation of Hbridge inverters. Compared with diode clamped inverter and flying capacitor inverter , H-bridge inverters requires the least number of components to achieve the same number of voltage levels and H-bridge inverters does not require any extra clamping diodes or voltage balancing capacitors. Optimized circuit layout and packaging are

possible in H-bridge multi-level inverter because each level has the same structure.

The general structure of the H-bridge multi-level inverter is to synthesize a near sinusoidal voltage form several levels of DC voltages. As the number of levels are increased, the synthesize output waveform has more steps which produce a

staircase wave that approaches the desired waveform. Also as the steps are added to the waveform the harmonic distortion of the output wave decreases.

This can be observed from the figure following which are generated by simulating a single phase H-Bridge Multi level inverter using MATLAB SIMULINK for Three ,Five and Seven level multilevel inverter and compared the THD which are Tabulated below

AIET

EEE

Page 22

CASCADED H-BRIDGE MULTI LEVEL INVERTER

8.1.SIMULATION OF THREE LEVEL MULTI-LEVEL INVERTER

Fig.8.1. SIMULATION OF THREE LEVEL MULTI-LEVEL INVERTER

AIET

EEE

Page 23

CASCADED H-BRIDGE MULTI LEVEL INVERTER

OUTPUT WAVE FORMS OF THREE LEVEL MULTI_LEVEL INVERTER

Fig.8.2.Single Phase Three Level H-Bridge Inverter output wave form

Fig.8.3. Single Phase Three Level H-Bridge Inverter Harmonics

AIET

EEE

Page 24

CASCADED H-BRIDGE MULTI LEVEL INVERTER

8.2.SIMULATION OF FIVE LEVEL MULTI-LEVEL INVERTER

Fig.8.4. SIMULATION OF FIVE LEVEL MULTI-LEVEL INVERTER

AIET

EEE

Page 25

CASCADED H-BRIDGE MULTI LEVEL INVERTER

OUTPUT WAVE FORMS OF FIVE LEVEL MULTI-LEVEL INVERTER

Fig.8.5. Single Phase Five level H-Bridge inverter output waveform

Fig.8.6. Single Phase Five Level H-Bridge Inverter Harmonics

AIET

EEE

Page 26

CASCADED H-BRIDGE MULTI LEVEL INVERTER

8.3.SIMULATION OF SEVEN LEVEL MULTI-LEVEL INVERTER

Fig.8.7. SIMULATION OF SEVEN LEVEL MULTI-LEVEL INVERTER

AIET

EEE

Page 27

CASCADED H-BRIDGE MULTI LEVEL INVERTER

OUTPUT WAVE FORMS OF SEVEN LEVEL MULTI-LEVEL INVERTER

Fig.8.8. Single Phase Seven level H-Bridge inverter output waveform

Fig.8.9. Single Phase Seven Level H-Bridge Inverter Harmonics

AIET

EEE

Page 28

CASCADED H-BRIDGE MULTI LEVEL INVERTER

8.4. Comparison of Different Multi-level Inverters

The 3rd, 5th , 7th and 9th harmonic ( normalized components ) of a H-Bridge Multilevel inverter for different number of levels are tabulated in table 8.1.

From

the above table we can observe that the harmonic content as well as the Distortion (THD) factors gets reduced as the number of levels

Total Harmonic

increased in a Single phase H-Bridge Multi-level inverter . This leads sinusoidal voltage waveform. We can also observe the

to a better and

great reduction of harmonic

content in three-level H-Bridge inverter

AIET

EEE

Page 29

CASCADED H-BRIDGE MULTI LEVEL INVERTER

CONCLUSION

We hereby technology applications description conclude in of of that Multi-level industry. In inverters this is a the very promising and

the power

project, mentioned

advantages and a

Multi-Level different

Inverters are inverter

detailed

multi-level

topologies

is presented. Single

Phase H-Bridge Inverter & Three Phase H-Bridge Inverters functioning is realized virtually using MATLAB SIMULINK. A detailed Multi-Level

Inverter is presented from which we concluded that the harmonic content is greatly Inverter reduced is in Multi-Level Inverter. A single and phase Cascade H-Bridge

designed

explained. The components to use in the practical Inverter are described in detail.

implementation of H-Bridge

AIET

EEE

Page 30

CASCADED H-BRIDGE MULTI LEVEL INVERTER

Reference

[1] Power Electronics Circuits, Devices & Applications , Muhammad H. Rashid,Third Edition, Prentice Hall India. [2] Linear Integrated Circuits, D.roy Choudary, Shail B.Jain, Second Edition, New Age International Publishers. [3] Multi-level Converter-A New Breed of Power Converters, Jih-Sheng Lai and Fang Zheng Peng, IEEE Trans. Ind, Applicant Vol.32 [4] Opamps & Linear Integrated Circuits , Ramakanth Gayakward, PHI Publications. [5] Power Electronic for Technology, Ashfaq Ahmed, PEARSON Education.

AIET

EEE

Page 31

You might also like

- Resonant TransformerDocument15 pagesResonant TransformerfelogonzaNo ratings yet

- Pe Final Ex SS 2010-2011Document8 pagesPe Final Ex SS 2010-2011Saif Uddin100% (1)

- Lab Report Solayman Ewu - CompressDocument12 pagesLab Report Solayman Ewu - CompressVic100% (1)

- Smart Series 2022Document350 pagesSmart Series 2022Dilawar TanvirNo ratings yet

- Datos Técnicos RefrigeradorDocument25 pagesDatos Técnicos RefrigeradorMiguel Mancilla100% (2)

- Cascaded H Bridge Multilevel Inverter Modelling and SimulationDocument34 pagesCascaded H Bridge Multilevel Inverter Modelling and SimulationPriyanka GuptaNo ratings yet

- Design of Single Phase H-Bridge Multilevel Inverter Using Microcontroller Atmel 89c51Document52 pagesDesign of Single Phase H-Bridge Multilevel Inverter Using Microcontroller Atmel 89c51Sabir VeNo ratings yet

- Multilevel Inverter 3-Level Topologies D PDFDocument39 pagesMultilevel Inverter 3-Level Topologies D PDFSUNIL MANJHINo ratings yet

- Power Supplies: Transducers AC and DC Diodes CapacitorsDocument10 pagesPower Supplies: Transducers AC and DC Diodes CapacitorsJose C. Lita JrNo ratings yet

- Energy Efficient TRansformersDocument19 pagesEnergy Efficient TRansformersMahidhar TalapaneniNo ratings yet

- (Elearnica - Ir) - An Energy Transmission System For An Artificial Heart Using Leakage InductaDocument10 pages(Elearnica - Ir) - An Energy Transmission System For An Artificial Heart Using Leakage Inductashizghul89b100% (1)

- Transformer: Rapid ElectronicsDocument5 pagesTransformer: Rapid ElectronicsMayaa KhanNo ratings yet

- Hybrid Cascaded Multilevel Converter With Reduced Total Harmonic DistortionDocument38 pagesHybrid Cascaded Multilevel Converter With Reduced Total Harmonic DistortionSwaroop100% (1)

- Last PDF of Project ReportDocument18 pagesLast PDF of Project ReportRAVINA MANGAL100% (1)

- SMPS PresentationDocument33 pagesSMPS PresentationGeorge AntonyNo ratings yet

- Chapter On1 and Two-1Document25 pagesChapter On1 and Two-1Roqeebat OdunayoNo ratings yet

- Basic Electrical EngineeringDocument22 pagesBasic Electrical EngineeringLipi SinghNo ratings yet

- Advancements in Inverter TechnologyDocument9 pagesAdvancements in Inverter TechnologyAyush KumarNo ratings yet

- Analysis and Design of Power Electronic Transformer For Medium Voltage LevelsDocument5 pagesAnalysis and Design of Power Electronic Transformer For Medium Voltage LevelsSobia SaadiaNo ratings yet

- Induction Type RelaysDocument8 pagesInduction Type RelayshilalsherNo ratings yet

- AlternatorDocument8 pagesAlternatorBoreda RahulNo ratings yet

- Application of Power Diode in Power ElectronicsDocument18 pagesApplication of Power Diode in Power ElectronicsSahale Shera Lutse 18BEE0376No ratings yet

- Unit 4 Power Quality Management in Smart Grid Emc - Electromagnetic CompatibilityDocument18 pagesUnit 4 Power Quality Management in Smart Grid Emc - Electromagnetic CompatibilityMathumathi TNo ratings yet

- Transformer - Wikipedia, The Free EncyclopediaDocument32 pagesTransformer - Wikipedia, The Free EncyclopediaParvezKhanNo ratings yet

- Snubber Circuits With ExplantionDocument9 pagesSnubber Circuits With ExplantioncoolsinghrkNo ratings yet

- Static RelaysDocument11 pagesStatic RelaysBharathwaj SreedharNo ratings yet

- Edc Project Report: Prof. Garima SolankiDocument32 pagesEdc Project Report: Prof. Garima SolankiAnime X100% (1)

- Design and Construction of A 2000W Inverter: Lawal Sodiq Olamilekan 03191100Document20 pagesDesign and Construction of A 2000W Inverter: Lawal Sodiq Olamilekan 03191100Da Saint100% (1)

- (Experiment 3) BJT - Common Emiter Amplifier PDFDocument9 pages(Experiment 3) BJT - Common Emiter Amplifier PDFArik JuniarNo ratings yet

- 17ee82 - Ida - Mod 4 NotesDocument18 pages17ee82 - Ida - Mod 4 NotesManish Kumar SahaniNo ratings yet

- MINIPROJECTHARTLEYOSCILLATORDocument15 pagesMINIPROJECTHARTLEYOSCILLATORPramod SultaneNo ratings yet

- Short Transmission LineDocument18 pagesShort Transmission LineNaga AnanthNo ratings yet

- Uninterrupted Power SupplyDocument14 pagesUninterrupted Power SupplyAnand KumarNo ratings yet

- Praharsh PPT (Modelling of Unified Power Flow Controller) GGDocument16 pagesPraharsh PPT (Modelling of Unified Power Flow Controller) GGPraharsh MishraNo ratings yet

- Power Electronic Inverter - ReportDocument9 pagesPower Electronic Inverter - ReportPrateek AgarwalNo ratings yet

- Lab 13-Under Voltage and Over Voltage Monitoring Numerical RelayDocument5 pagesLab 13-Under Voltage and Over Voltage Monitoring Numerical RelayAliza Sharif100% (1)

- Transmission LineDocument11 pagesTransmission LineDeni RistiantoNo ratings yet

- EM - 2010 - M - Power - Factor PDFDocument7 pagesEM - 2010 - M - Power - Factor PDFagustantoNo ratings yet

- Power Star InverterDocument9 pagesPower Star InverterronniedakingpouNo ratings yet

- Three Phase Fault Analysis With Auto Reset For Temporary Fault and Trip ForDocument16 pagesThree Phase Fault Analysis With Auto Reset For Temporary Fault and Trip ForFirstLearnNo ratings yet

- Direct Vs Alternating Current: BelowDocument5 pagesDirect Vs Alternating Current: Belowtgs100No ratings yet

- Base Driving For Power BJT SivaDocument16 pagesBase Driving For Power BJT SivaSachin SivaNo ratings yet

- Nptel: High Voltage DC Transmission - Web CourseDocument2 pagesNptel: High Voltage DC Transmission - Web Coursekmd_venkatsubbu0% (1)

- 3 Phase Cascaded H-Bridge InverterDocument7 pages3 Phase Cascaded H-Bridge InverterAnil ShahNo ratings yet

- Speeed ControlDocument3 pagesSpeeed ControlChristine GomezNo ratings yet

- International Refereed Journal of Engineering and Science (IRJES)Document8 pagesInternational Refereed Journal of Engineering and Science (IRJES)www.irjes.comNo ratings yet

- DCMTDocument37 pagesDCMTGloria HolcombNo ratings yet

- Short Circuit Detector - Abstract-1Document1 pageShort Circuit Detector - Abstract-1KARTHIK KUMAR MNo ratings yet

- Report On HVDCDocument18 pagesReport On HVDCBARUN SINGHNo ratings yet

- Question Bank EMDDocument23 pagesQuestion Bank EMDd_rajmtechNo ratings yet

- EE309 Notes 07 PDFDocument4 pagesEE309 Notes 07 PDFbals123456100% (1)

- Reduced Voltage Starting Using Part Winding Technique of 3-Phase Cage Rotor Induction MotorDocument8 pagesReduced Voltage Starting Using Part Winding Technique of 3-Phase Cage Rotor Induction MotorKennethNo ratings yet

- Power Electronics 2 MarkDocument5 pagesPower Electronics 2 MarkPrakash Mahendran100% (2)

- 3 Point StarterDocument16 pages3 Point StarterSameer Sharma0% (1)

- Sweep Frequency GeneratorsDocument2 pagesSweep Frequency GeneratorswiraNo ratings yet

- Investigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsFrom EverandInvestigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsNo ratings yet

- Theory of Microwave Valves: International Series of Monographs on Electronics and InstrumentationFrom EverandTheory of Microwave Valves: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- Integration of Green and Renewable Energy in Electric Power SystemsFrom EverandIntegration of Green and Renewable Energy in Electric Power SystemsNo ratings yet

- Cascade H-Bridge Multi Level InverterDocument3 pagesCascade H-Bridge Multi Level InverterKolan Vamshi Kiran ReddyNo ratings yet

- MSC Thesis R Kleiterp ReportDocument157 pagesMSC Thesis R Kleiterp ReportKolan Vamshi Kiran ReddyNo ratings yet

- Iv Year I Sem.r09Document10 pagesIv Year I Sem.r09Kolan Vamshi Kiran ReddyNo ratings yet

- Iii Year I Sem.r09Document5 pagesIii Year I Sem.r09Kolan Vamshi Kiran ReddyNo ratings yet

- Ii Year I SemDocument5 pagesIi Year I SemKolan Vamshi Kiran ReddyNo ratings yet

- I Year R09Document8 pagesI Year R09Kolan Vamshi Kiran ReddyNo ratings yet

- 04.10.20 Cta-4Document37 pages04.10.20 Cta-4Goury ShankarNo ratings yet

- 1 s2.0 S235214651930242X MainDocument8 pages1 s2.0 S235214651930242X MainAndre Novent ChenadyNo ratings yet

- Virginia Transformer - Developments in Traction TransformersDocument10 pagesVirginia Transformer - Developments in Traction TransformersTshepo Sharky SebeNo ratings yet

- All Our SolutionsDocument41 pagesAll Our SolutionssreedeviishNo ratings yet

- Optically Coupled 20 Ma Current Loop Receiver: HCPL-4200Document13 pagesOptically Coupled 20 Ma Current Loop Receiver: HCPL-4200bigm94iNo ratings yet

- Advanced Voltage Mode Pulse Width Modulator: Description FeaturesDocument24 pagesAdvanced Voltage Mode Pulse Width Modulator: Description Featuresvanhuong87No ratings yet

- High-Efficiency Hybrid Resonant Converter With Wide-Input Regulation For Photovoltaic Applications-1Document76 pagesHigh-Efficiency Hybrid Resonant Converter With Wide-Input Regulation For Photovoltaic Applications-1VINAYNo ratings yet

- CHAPTER 2 - Oscillator PDFDocument26 pagesCHAPTER 2 - Oscillator PDFMuhd Deen0% (2)

- 17 Samss 502 PDFDocument30 pages17 Samss 502 PDFFlorin Daniel AnghelNo ratings yet

- General Physics 2 Week 4 Day 2 Dielectric and Potential Energy in CapacitorsDocument19 pagesGeneral Physics 2 Week 4 Day 2 Dielectric and Potential Energy in Capacitorscoffeeandu07No ratings yet

- AC CircuitsEE 03 01 To EE 03 04 QuestionnaireDocument3 pagesAC CircuitsEE 03 01 To EE 03 04 QuestionnaireCelina RoxasNo ratings yet

- F5 Elevator Drive Manual - V1.72Document180 pagesF5 Elevator Drive Manual - V1.72Hongquan SuNo ratings yet

- Design and Fabrication of A Non Dissipative Charge Equalization Converter For Battery Stack Used in Hybrid Electric VehicleDocument8 pagesDesign and Fabrication of A Non Dissipative Charge Equalization Converter For Battery Stack Used in Hybrid Electric VehicleRa muNo ratings yet

- Advantages of Bundled Conductors in Transmission LinesDocument5 pagesAdvantages of Bundled Conductors in Transmission Linesf3ziii100% (1)

- Semiconductors - Module - 02 (2.5 LED 2.6 LASER DIODA)Document40 pagesSemiconductors - Module - 02 (2.5 LED 2.6 LASER DIODA)Niken Arina PratiwiNo ratings yet

- Sbas 022 DDocument27 pagesSbas 022 DWilson Yecit OrtizNo ratings yet

- Taming The Trap Dipole: A Self-Supported Dipole For 10/15/17 Meters Can Be A Fine Thing-If It's Designed RightDocument3 pagesTaming The Trap Dipole: A Self-Supported Dipole For 10/15/17 Meters Can Be A Fine Thing-If It's Designed Rightattila balintNo ratings yet

- Nisarg CSCDocument34 pagesNisarg CSCNarendra MehtaNo ratings yet

- APA-1 (100Q) (Electrostatics, DC Circuits, Capacitors, Magnetism) (JEE 2020)Document22 pagesAPA-1 (100Q) (Electrostatics, DC Circuits, Capacitors, Magnetism) (JEE 2020)Vedant TodiNo ratings yet

- Physics II Problems PDFDocument1 pagePhysics II Problems PDFBOSS BOSSNo ratings yet

- WW High Fidelity Guide 1977Document168 pagesWW High Fidelity Guide 1977John Samuel Mamani Menacho100% (1)

- Viper50/Sp Viper50A/Asp: Smps Primary I.CDocument20 pagesViper50/Sp Viper50A/Asp: Smps Primary I.CRalie RalevNo ratings yet

- Final Miniproject ReportDocument55 pagesFinal Miniproject ReportYogesh PalkarNo ratings yet

- A Study On Overvoltages in Wind Tower Due To Direct Lightning StrokeDocument6 pagesA Study On Overvoltages in Wind Tower Due To Direct Lightning Strokebal3xNo ratings yet

- Test ManualDocument66 pagesTest ManualAakoji Devikumar100% (3)

- NCP3063, NCP3063B, NCV3063 1.5 A, Step-Up/Down/ Inverting Switching RegulatorsDocument19 pagesNCP3063, NCP3063B, NCV3063 1.5 A, Step-Up/Down/ Inverting Switching RegulatorschawkigenieNo ratings yet

- CPC 100 - VT Ratio Measurement With 12kVDocument9 pagesCPC 100 - VT Ratio Measurement With 12kVSivakumar NatarajanNo ratings yet

- MFJ 269 CalibrationDocument7 pagesMFJ 269 CalibrationclistenesrosasNo ratings yet