Professional Documents

Culture Documents

CMOS-MEMS Integration Processes and Techniques

Uploaded by

xpeprisheyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CMOS-MEMS Integration Processes and Techniques

Uploaded by

xpeprisheyCopyright:

Available Formats

CMOS-MEMS integration

Jan Erik Ramstad Institute for Informatics University of Oslo janera@fys.uio.no 27th March 2006

Contents

1 Essay background 2 Processes 2.1 CMOS-MEMS process steps . . . . . . . . . . . . . 2.2 CMOS Process-sequence . . . . . . . . . . . . . . . 2.3 MEMS Process . . . . . . . . . . . . . . . . . . . . . 3 Materials 4 CMOS-MEMS parameters 4.1 CMOS-MEMS compability . . 4.2 Pre-CMOS Micromachining . 4.3 Intra-CMOS Micromachining 4.4 Post-CMOS Micromachining 5 Existing CMOS-MEMS products 6 Circuit and system integration 7 Discussion and analysis 8 Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 1 2 2 2 3 4 4 5 5 6 7 8 8 8

2 Processes

MEMS evolved from CMOS processes in the late 90s, and MEMS has since then been behind CMOS in process technology. This development is thoroughly described in [2]. Because of the technology trend, CMOS has larger wafer sizes than MEMS. Some manufacturers have used laser equipment to cut the CMOS wafer to match MEMS wafer sizes. This enables the possibility to use MEMS process technologies to make MEMS structures in the CMOS wafer. This is known as PostCMOS Micromachining. However, the cutting of wafer size led to an inefcient economy. This is because number of dies per wafer was reduced dramatically, and the yield was reduced. CMOS compabilitiy as discussed in [2], indicates that CMOS is the dominant semiconductor technology. This means that MEMS has to adapt to CMOS and not the other way around. Still, this leaves three different choices of producing CMOSMEMS systems: 1. Pre-CMOS Micromachining 2. Intra-CMOS Micromachining 3. Post-CMOS Micromachining These three micromachining processes are hereby dened as modules. A set of fabrication steps of CMOS or MEMS is also dened as a module. For intra-CMOS, a MEMS module is made rst, then a CMOS module is made, and nally a nishing MEMS module is processed. Pre-CMOS indicates a MEMS module processed before the CMOS is made, and vice versa for post-CMOS. Pre-, intra- and post-CMOS all have in common that the production of the MEMS is adapted to the CMOS processes. This means that the CMOS process may have to modify the original CMOS process in order to perform MEMS process steps. It is also possible to make the CMOS and MEMS parts seperately in foundries specialized on CMOS or MEMS. Seperate manufacturing of MEMS and CMOS requires proper connection between the CMOS and MEMS parts, as well as minimal inuence on the CMOS part if the MEMS module is fabricated after the CMOS module. To efciently design and implement MEMS systems, reference [2] suggests a CMOS compatible path. This is due to the importance of using IPs (Intellectual Properties) and embedded software to set up the whole system. Reference [2] suggests to use Canvendish Kinetics to produce a monolithic IC. This manufacturing is based on a post-CMOS process to create a System on a Chip (SoC). Design IPs for the MEMS elements and an embedded MEMS process module are used. There are design IPs for the CMOS infrastructure as well. Because the CMOS technology is the contraint in this type of process, not all MEMS elements can be implemented.

Essay background

The intention of this essay is to investigate the possibilities of integrating MEMS and CMOS together in one or two seperate processes. There are a variety of factors which are to be taken into account when designing a CMOS-MEMS integrated circuit. Some reasons for designing CMOS-MEMS [1] are shown below: No discrete components Less parts assembly and packaging High quality factor (Q) High operational frequency Possibility for mixing and ltering to be performed simultaneously This essay will try to take a look at available processes, materials for the design, parameteres for both CMOS and MEMS, the possibilities for full circuit integration as well as reviewing existing CMOS-MEMS product. The essay will have its focus towards RF MEMS related processes.

2.1 CMOS-MEMS process steps

The following techniques are central in CMOS-MEMS processes described in [3]. These steps are explained because they will place a limiting factor on how to implement the MEMS structure (before or after the CMOS circuit). Chemical vapor deposition, CPD Can be performed at low pressure (LPCVD), atmosphere pressure (APCVD) or with a plasma (PECVD). 10nm to 10 m thickness. Can deposit oxides at temperatures between 300C and 900 C Physical vapor deposition, PVD 10nm to 10 m deposition of oxides or thin lms. Thermal oxidation High temperature (900C -1200C ) deposition of oxide layers Patterning The use of photolitography is very similar for both CMOS and MEMS. The difference is that CMOS has developed extremely small mask sizes, while the MEMS photolitography is far behind these mask sizes. MEMS photolitography does not have the same need to scale down the mask sizes. Both process modules utilizes UV light being exposed to a substrate covered with a photoresist. Positive or negative resists will dene the areas which are to be etched away. Annealing Annealing is a process step which is often used in both CMOS and MEMS. Annealing means to expose a newly deposited or implanted material of high temperature for a certain period of time. The reason to perform annealing can be to reduce stress. Annealing is also often known as to soft-bake the wafer.

Figure 1: Cross-section of simplied CMOS process

may change. Because of this, it is essential that high temperature process steps in the MEMS process are avoided. 5. The microelectronic circuit is connected by using interconnects. The metal layers are deposited by sputtering, and the amount of layers can vary from 3 to 8. Note that metal is very sensible for succeeding high temperature steps. 6. Finally the passivation layer is deposited by using low pressure chemical vapor deposition. If MEMS is to be implemented after the CMOS circuit, the passivation layer may have its residual stress adapted for the MEMS structure.

2.2 CMOS Process-sequence

To integrate MEMS with CMOS [3], it is essential to know the process-sequence of CMOS. Figure 1 shows a very basic ow on how to create microelectronics in CMOS. The idea is to show which process steps the CMOS needs to undergo and to then indicate how to sucessfully implement MEMS structures based on these techniques. For example, it is essential that the CMOS is not harmed if MEMS is integrated after CMOS is made. It is important not to apply excess heat or stress which is above the limits for the CMOS circuit. Figure 1 is based on making a simple pMOS transistor. 1. First we dope our substrate with a light p-doped material by implanting a light concentration of for example Boron, which is an acceptor material. 2. The next step is to implant the n-well. The temperature for implanting the well is based on a high temperature over a few hours. 3. The growth of SiO2 is done thermally. The deposition of polysilicon is done chemically with low pressure and is done in a furnace at a temperature of 600C . Polysilicon might also be used for MEMS as structure layers and must be carefully deposited not to disturbe the doping distributions of CMOS circuit. 4. In this example, Boron is implanted to make the source and drain areas. Boron will diffuse into the substrate. Another high temperature process is necessary for annealing. This is the last high temperature step for CMOS, and if CMOS is further exposed to high temperatures, the doping distributions may be altered and then the circuit characteristics

2.3 MEMS Process

This section intends to describe some of the most important process steps in MEMS. There are two main micromachining methods: Bulk micromachining and Surface micromachining. Bulk Micromachining: Consists of etching into the silicon substrate There are two ways to etch into the substrate: Isotropic etch This type of etch has the same etch rate in all directions, thus leaving a big undercut under the mask. HN A is the most common etch solution and is a mixture of HF , HNO3 and CH3 COOH . XeF2 can be used to dry etch silicon with very good selectivity, though with rough surfaces. Anisotropic etch Most common etch type used to etch through the substrate, resulting in a release etch of a MEMS structure. Because single-crystalline silicon has different etch rates in the different directions, the etching will

Figure 2: Simplied MEMS bulk micromachining

vary in the planes. It turns out that the (111) plane is the slowest plane to etch when a (100) silicon wafer is used. The (111) plane intersects the surface at an angle of 54.74 . This allows the possibility for making various amounts of structures. However, the drawback of anisotropic wet etch is the steep angle which results in more occupation of Si area for thick structures. KOH (Potassium hydroxide) is the most common etch solution used for anisotropic etching. KOH etches SiO2 at a higher rate than SiN , which is why silicon nitride is often used as a mask. The undercut under the mask is very low. Tetramethyl ammoniumhydroxide (TMAH ) is an alternative etch solution. Anisotropic dry etch results in a better aspect ratio than anisotropic wet etch. Figure 2 shows bulk wet etching steps. DRIE - Deep Reactive Ion Etch This process step is developed by Bosch [4]. A high density plasma( SF6 ) is used to etch, and after some etching a polymer covers the sidewalls so the sidewells do not etch. The process consists of alternating plasma etching and polymer-assisted sidewall protection steps. A high aspect ration (AR) is possible by using this process, and thus it is possible to create deep structures because the DRIE process does not depend on the crystal orientation of the silicon. This is an expensive process step. Surface Micromachining This type of micromachining consists of depositing thin lms on the substrate and selectively remove certain layers to release a structure. For example, a cantilever beam can be released by removing a sacricial silicon dioxide lm. It is important to use certain techniques to avoid stiction (the cantilever beeing stuck to the substrate after the release step). Deposition of metal layers can be done using low tempereature physical vapor deposition technique. Polymer lms are then used as sacricial layers. Figure 3 shows a very simplied surface ow chart [3].

Figure 3: Simplied MEMS surface micromachining

3 Materials

To be able to integrate MEMS into CMOS (CMOS-MEMS), it is important that the materials offered from the IC foundry are capable MEMS materials [3]. CMOS has always focused on electrical conduction and insulation, while MEMS materials rely heavily on mechanical, chemical and thermal characteristics. A set of test structures must be implemented in order to characterize the CMOS materials and to see if they are good enough as MEMS materials. A test structure is a diagnostic device which contains necessary functions in order to extract material properties. There are four main test structure tests: Simple geometry test, robustness test (mechanical and fracture), minimal micromechanical structuring (minimize undesired complication of the process when using MEMS process steps) and simple measurement method (electrical and optical testing). The following list shows the most important materials used in the processes: Silicon, Si Most common substrate material. Can be doped to change electrical properties. Single-crystal silicon has excellent

mechanical properties. The amount of doping in the silicon depends on the microfabrication to be done. For example, a membrane of a pressure sensor requires low p-doped silicon to be able to etch fast enough with KOH solutions. Polysilicon Used as gate material for MOSFETs. Is also used as electrode, thermoelectric material and as resistor materials for piezorestitive sensing. Metal layers Used as interconnects, electrodes, thermistors. Aluminum, titaniun tungsten are most used and are deposited by sputtering. Copper is used in state of the art CMOS technology because of lower resistance and higher electromigration resistance. Electromigration is the transport of ions in a conductor due to momentum transfer between conducting electrons and diffusing metal atoms. A high electromigration will allow high current densities. Insulator layers and masks: Silicon dioxide, SiO2 - Etch resistant Silicon nitride, SiNx - More resistant to chemical etch than SiO2 Polymers - Used as photoresist, dielectric material or passivation layer. Electrical restitivity, thermal conductivity and thermal capacity are important parameters for MEMS. These parameters can be tested by making test structures where the parameters can be extracted out from the behaviour. For example, a micromachined van der Pauw structure can be created to measure in-plane thermal conductivities of thin lms. The structure consists of a four armed greek cross structure suspended over a micromachined cavity. Another example is to extract the thermal response coefcient by applying a range of frequencies [5]. An important part for MEMS sub-systems is to extract mechanical material properties. A set of test models are applied in order to determine the mechanical properties of the materials. Parameters for load-deection, strain deformation, residual stress, Poissons ratio can be achieved from Finite Element Method analysis or from test structures. Examples of test structures can be square diaphragms or long diaphragms. MIT [6] or Sandia National Laboratories extracts Youngs modulus and pull-in voltage for a set of structure by performing electrostatic tests on beams [7]. For RF MEMS, thermoelastic friction may cause irreversible heat generation. This may limit the quality factor of micromechanical resonators. Still, there are many factors in CMOS-MEMS which limits the optimal functionality of the system when considering material behaviour. The CMOS technology has excellent geometric and electrical characteristics. The additional mechanical and thermal material characterization of MEMS is less mature than CMOS, thus making it a challenge to successfully implement optimal microstructures with given material parameters [3].

modied in a way which would inuence characteristics and yield of the circuits. There are a few CMOS process steps which may affect the following MEMS steps in an undesired way. Because of this, some CMOS steps may have to be modied. Such process modications must be thoroughly qualied. Because of this, it is important to introduce minor process modications to the foundry. Strongly doped p-type substrate for the CMOS circuit is important in order to avoid latch-up. This will affect anisotropic etch rates and etch directions. Reduced pdoped epitaxial layers will reduce this problem. Excess interstitial oxygen concentration is present in order to reduce metal impurities in CMOS processing. This excess oxygen concentration will affect anisotropic etch quality, leaving rough edges or cavities. The problem can be solved by either using an etch-stop ring around the membrane or using an electroplated metal ring. Reducing excess oxygen concentration is possible, but external gettering must be employed to reduce crystal defects on the back of the wafer. A getter is a small circular trough or channel lled with metals that oxidize quickly. It is important not to employ high temperature MEMS process steps if the CMOS circuitry is made rst. Use LPCVD to deposit polysilicon and the annealing step afterwards must be within the so called thermal budget. For interconnects, CMOS often use aluminium. Because aluminum only withstands 450 C, there are a few choices: The rst one is to deposit aluminium after MEMS circuitry (if possible). The other choice is to have a thermal budget of 450 C. The third choice is to use another material for interconnects other than aluminum. At the end of the CMOS process, a passivation layer is deposited. This passivation layer may be modied in order to match residual stress with layers from the MEMS process. It is important that the stress proles match in order to not introduce compressive or tensile stress. Also, stress in the passivation layer may inuence the underlying metal interconnects. The design of a fully integrated system can be done using CMOS processes and CMOS design programs. In order to be able to create MEMS structures, certain rules in the program must be violated because the design software does not understand the process modication. For example, the design program will not allow making a via without having metal below and top of it. It is possible to avoid these rule violations by expanding the standard design rule set with the new MEMS modications, but this will be time consuming. For complex MEMS designs, this is preferable. CMOS-MEMS consists of electronic circuits with one or more micromechanical transducers. IC designers use electronic design automation (EDA), while MEMS designers typically use nite element modeling software. In order to simulate CMOS with transducers, behavioral models for the transducer models must be made. Because transducers contain several signal domains, lumped element circuit models of the transducer must be developed manually. An example of a software designed to handle these types of systems is INTEGRATOR from Coventor. This software will perform mechanical simulations and then export these simulations to standard circuit simulators. For layout-versus-schematics (LVS), these libraries must also be extended in order to include the MEMS elements [3].

CMOS-MEMS parameters

4.1 CMOS-MEMS compability

Reference [3] indicates an important factor when designing CMOS-MEMS. The CMOS process sequence must not be

Figure 5: Intra-CMOS module

ness. A post-CMOS fabrication module is performed to access the etched cavity by dry etch the wafer from the front or anisotropic etch the wafer from the back. Another bonding technique is to use glass anodic bonding to protect integrated transducer elements located in an anisotropic etched cavity [8].

Figure 4: Pre-CMOS module

4.2 Pre-CMOS Micromachining

By fabricating the MEMS structures before the CMOS circuitry, it is possible to deposit polysilicon structures with annealing afterwards at temperatures up to 1100 C. This type of fabrication requires well dened and smooth surfaces for the CMOS circuitry, as well as proper interconnects between the MEMS and CMOS. For example, the substrate may be etched to create a trench for a following microstructure made in polysilicon. A polysilicon interconnect layer is made to make a connection with the CMOS circuitry which is located besides the MEMS structure, or on top of the non-etched part of the substrate. PreCMOS micromachining does not require much modications from the CMOS process. It is also possible to build polysilicon structures on top of the silicon substrate instead of in an etched trench. In that case, the CMOS circuitry is located on top of an epitaxial silicon layer. A seal layer sandwich is deposited to protect the MEMS structures during the CMOS process. A simplied pre-CMOS process is shown in gure 4 [3]. It is possible to use silicon-on-insulator (SOI) wafers to create single crystalline micromechanical structures. By doing this, it is possible to make thicker structural layers, thus making the structures more robust. Using this technique, the structural layers must be released during a post-CMOS process. Using pre- and post-CMOS modules, it is preferable that the CMOS circuit is made in one fabrication step. MIT has developed a pre-CMOS technique incorporating wafer bonding to seal cavities and protect the MEMS structures. A cavity is etched into a handle silicon wafer which is then silicon fusion bonded with an epi-wafer with a dened thick-

As a summary, the pre-CMOS fabrication module does not interrupt the CMOS process, nor does it place any constraints on the thermal budget of the CMOS process. There are many choices of CMOS technologies, but this approach requires much development and preparation of the micromachined wafers. The MEMS wafers are the start material and must have proper contact to the following CMOS circuit. In addition to this, there will most probably be a requirement of post-CMOS processing in order to release devices [3].

4.3 Intra-CMOS Micromachining

This type of fabrication consists of making the MEMS structures before the CMOS interconnect metal lines. This makes it possible to correctly anneal polysilicon at high temperatures to get the proper stress prole in the polysilicon structure. The thickness of the polysilicon can be 2-4 m. As an example, Analog Devices uses 13 masks for the electronics and 11 masks for the mechanical structures. Diffused n+ runners (vias) are implemented to connect with the MEMS structure. A LPCVD nitride layer and borophosphosilicate glass layer is deposited over the CMOS circuit, making an area ready for the MEMS structure. To avoid stiction when dry releasing the microstructure, a pedestal is made to keep the structure up. The pedestal is removed after the release step [9]. Inneon technologies has a capacitive sensor made from a polysilicon layer from a 0.8 m BiCMOS process. The main part of the pressure sensor structure is made during the BiCMOS process module. The micromachined module consists of releasing the polysilicon membrane and seal the cavity. After this, the BiCMOS process allows the formation of aluminum interconnects. Figure 5 is based on this BiCMOS process [10].

Technical University of Aachen and the Fraunhofer Institute IMS creates a pressure sensor during an intra-CMOS module. Deposition of SiNx , sacricial oxide layer and polysilicon structure layer is performed after implantation of source and drain areas. Then the polysilicon membrane is released by an HF etch. This technique allows the construction of an array of polysilicon membranes in parallell for measuring different pressure ranges [11]. Bosch and Fraunhofer Institute ISiT proposes a way to implement thick polysilicon structures without inuencing the source/drain doping characteristics. A surface micromachined accelerometer is made by depositing a sandwich of a sacricial oxide and a LPCVD polysilicon layer. An epitaxial layer forms the circuit areas, and then an epi-poly layer is grown with the LPCVD polysilicon layer, creating a 10 m thick structure with excellent mechanical properties [12]. IBMs T.J. Watson Research Center avoids high temperature steps by creating dielectric lms using PECVD at about 400 C. Microstructures are removed by removing an organical sacricial layer using oxygen plasma [13]. In summary, this fabrication module brings many constraints to the CMOS technology, thus making it harder to proceed to more advanced CMOS technologies. In addition, it is preferable to have fabrication and micromachining at the same foundry. The critical factor is the high temperature steps required for fabrication of microstructures, thus violating the thermal budget of the CMOS process. This fabrication module is not favorable [3].

Figure 6: Two post CMOS processes

4.4 Post-CMOS Micromachining

Post-CMOS is a module where the CMOS circuit has been made in advance, and the MEMS structures is inserted afterwards. As an example, a CMOS-MEMS process suggested in [1] uses micromachining processes after the CMOS circuit is made. In short, the Bosh DRIE process and an isotropic etch is used to create a beam structure. This type of fabrication uses additional metal layers, which in turn can be used to create thick beams. Smaller gaps between electrodes can be made by reducing the sidewall polymer from the DRIE etch. The sidewall polymer can be reduced by using an extra mask over the aluminum in the non-MEMS areas. Copper interconnect is between the MEMS and CMOS circuit. By using these processes, [1] indicates the following advantages: Split electrode designs (two electrodes: Input and output) Integration with electronics Short bond wires in PCB design allows RF mixing in GHz Gain is inverse proportional to the damping which is related to Q. Q factor is reduced if air pressure is increased. Reference [3] indicates that post-CMOS can be performed at a dedicated MEMS foundry. Doing this, it is important to stay below the thermal budget. PECVD, sputtering, electroplating, wet and dry bulk and surface micromachining processes are suited for post-CMOS. Post-CMOS can be performed in two ways: Building microstructures on top of the CMOS substrate (1) or using micromachine techniques to modify the CMOS layers (2).

1. Add layers on top of completed CMOS wafer: This type of fabrication consists of using surface micromachining techniques. It can be performed with low temperature modules (100-150 C) with PVD, electroplating or CVD processes over 300 C. It is important to have a smooth surface to deposit on and good electrical contact with the CMOS circuit. The CMOS may be surrounding the MEMS or be located underneath the microstructures. By using metal-silicon contacts and tungsten interconnect in CMOS, it it possible to perform high temperature MEMS processes. A passivation layer planarizes the wafer and protects the circuit below. The passivation layer may consist of phosphosilicate glass (PSG) and low-stress LPCVD SiN . Rapid thermal annealing may be performed, but still there might be a change in the doping proles of the transistors. [3] The high temperature process occurs when using polysilicon as a structural layer. This may be solved by using an alloy: Polycrystalline silicon-germanium which can reduce the temperature processes to 450C , which is below the thermal budget. Using PECVD to deposit poly-SiGe has increased deposition rates. Investigation of Poly-SiGe is described in [14]. Poly-SiGe might be a future structural material for post-CMOS as long as deposition stress and annealing parameters are improved. The top part of gure 6 is a post-CMOS microstructure made on top of a CMOS circuit based on this Poly-SiGe process. By using PVD, the temperature can be further reduced to 350 C. The silicon structural layer with TiW enables a MEMS structure with low electrical resititivity where the structural layer is released by dry etching. Another possibility is to use electroplating to form a microstructure by selectively electroplating in open mold areas. Electroplated processes are performed in room temperatures, however the control of thin lm stress and stress gradients are very important. Instead of

adding layers on top of the CMOS substrate, it is possible to manufacture CMOS and MEMS wafers seperately, and then solder bond the MEMS wafer on the CMOS wafer [3]. 2. Modify CMOS layers to make microstructures The bottom part of gure 6 on the preceding page shows how microstructures can be made with CMOS layers [1]. This requires less process steps both for release of structure and deposition steps. This process resembles bulk etching, and many commercial devices using this technique are piezorestitive pressure sensors. The CMOS process may be slightly modied to improve the doping prole for piezoresistors. It is popular to back etch the silicon substrate to make a cavity for membranes or cantilevers. Anisotropic KOH etch or etch stop can be used to make the cavity. Using SOI from CMOS offers the possibility to use a buried oxied layer as an etch stop. Using p++ etch-stop techniques requires an intra-CMOS module to diffuse highly doped p-regions. A special wafer holder can be used to protect the front of the wafer which contains the CMOS circuit. Then the back of the wafer is wet etched. Anisotropic wet etch with electrochemical etch stop requires a contact potential. In either case, the wafers must be manually placed in the mechanical holder, which is a slow production process. This is done because this is the most reliable process to protect the front side of the wafer. DRIE etching is an alternative, providing excellent aspect ratio. The equipment to do this, however, is expensive. It is also possible to wet etch and dry etch the substrate from the front side, for example by using electrochemical etch-stop [3]. An interesting bulk micromachining technology from Carnegie Mellon University utilizes the top metal interconnect as an etch mask for the microstructure denition. By doing this, the CMOS technology masks will dene the length and width of beam, thus creating smaller structures than normal. A sandwich of dielectrics with polysilicon and metal layers is made and the structure is released by two dry etching steps. Anisotropic etch will etch areas not protected by the metal mask, while isotropic etch will underetch the oxide and thus releasing the structures. This technique, however, is exposed to large residual stress and stress gradients in between the dielectric layer sandwich. By using DRIE etch at the front, and anisotropic etch on the back of the wafer, this problem is solved. Anisotropic etch at the front removes SiO2 not protected by the top metal layer. The resulting thickness of the structure is 10-100 m [15]. A surface-micromachining technique developed in Zurich is used to remove thin lms of the CMOS process selectively. The process is known as SALE, sacricial aluminum etching. It consists of removing metal layers from the CMOS process to release microstructures. The microstructures consists of intermetal dielectric, the upper metallization layer and the passivation. It is also possible to make a nanocantilever by using laser beam litography on an aluminum etch mask. The polysilicon cantilever is released by removing eld oxide layer beneath the cantilever [16]. Conclusion of Post-CMOS micromachining: Post-CMOS microfabrication is the most exible fabrication module, especially because the CMOS and MEMS circuits may be made seperately. The constraints are: Bulk-CMOS micromachining requires a certain substrate material. New substrate materials must be thoroughly qualied.

The planarity of area for the MEMS device is important. Increasing amount of metallization layers may increase topographic variations. Because of this it is important to have proper planarization steps. The CMOS process introduces a thermal budget which the following MEMS fabrication module must keep below. This thermal budget is set from metallization layers and doping proles of the transistors. The advantages of post-CMOS are: The MEMS structure may be placed on top or beside the CMOS circuitry The CMOS process can follow the CMOS development track in order to reduce area of the microelectronic circuit. It is possible to use two different foundries for the CMOS and MEMS circuits. No expensive re-qualication of the CMOS process

5 Existing CMOS-MEMS products

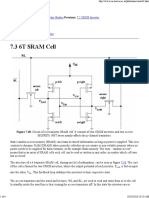

Reference [17] explains how the digital micromirror device from Texas Instruments can be manufactured by using low temperature processes only. One pixel from the mirror display is made by alternating layers of aluminum and air gaps. The mirror is placed above a CMOS SRAM cell. It is important that the surface is planarized properly. The aluminum layers are sputtered, and the mirror is released by etching the polymer sacricial layer using a plasma etcher. Antistiction layers prevents stiction, and landing pads avoid short circuit when tilting the mirror. Reference [18] shows how Analog Devices make their integrated sensors. Analog Devices has extremely well qualied analog design processes and expertise, which allows Analog Devices to create integrated sensors with analog outputs. External off-chip circuitry must handle advanced signalconditioning and calibration. Analog Devices is an expert on this eld, but in case of construction of CMOS-MEMS from a less known foundry, a digital output should be created. Figure 7 on the next page shows an example of a resonantbeam oscillator [3]. A cantilever can be used as a loop lter in an oscillator. A feedback circuit is required to determine resonance frequency. The MEMS structure must be able to actuate, and there is also a requirement for a deection sensor. Further on, the output signal can be enhanced by a Wheatstone-bridge. A differential amplier amplies the signal with a limiting value in order to avoid saturation from DC-offset of the Wheatstone-bridge. A high-pass lter removes offset, 1/f noise from the amplier and thermal crosstalk. A second amplier and high pass lter sends the differential signal to a comparator. A digital delay line after the comparator is used to adjust the phase of the feedback loop. University of Michigan have developed a Silicon-on-Glass accelerometer. The accelerometer is fully CMOS compatible and consists of a post-CMOS fabrication module. A high aspect ratio with 120 m thick single-crystal silicon proof mass and 3.4 m lateral sense gaps. The glass substrate is anodically bonded to the frontside of a CMOS die. Deep Reactive Ion Etch is used to etch the microstructure. The microelectronics consists of a switched-capacitor and an oversampled sigma-delta modulator to read capacitance changes [19].

The package of a CMOS-MEMS die requires special attention due the MEMS structure which needs external measurement equipment. RF MEMS requires hermetic sealing for high-Q resonators to avoid air damping. Packaging and testing consists of a little more than one third of the total costs [3].

7 Discussion and analysis

Making CMOS-MEMS often requires a dedicated CMOS process. For newly etablished companies, the only possibility to construct the CMOS circuit is to use an external foundry, then to make the MEMS at another foundry. Another possibility is to use foundries which accept multi-wafer projects. Multi-wafer projects are wafer batches where external participants (research institutes, universities, companies) may get their designs produced. A CMOS-MEMS multiwafer project would include both CMOS and MEMS at the same foundry. Many multiwafer projects are included in the Europractice arrangement. Material and process choices limit the compability for CMOS-MEMS. Commercially, on-chip solutions are often used because it is more efcient to do so, both economically and scientically. Sensors like the mirror display from TI is an example of CMOS-MEMS which must be on the same wafer in order to function correctly [3]. Pre or post CMOS are clearly preferred. Post-CMOS is often selected because the CMOS process may be completed, and the wafer may be sent somewhere else for MEMS processing. By doing this, CMOS and MEMS may be processed in each one of their respective foundries.

Figure 7: Resonant beam

Reference [20] describes a fully differential square frame resonator with high working frequencies. The in-plane resonator has been fabricated directly on a conventional CMOS substrate with on-chip differential ampliers. The CMOS process has a 0.35- m feature size, and the MEMS is manufactured with a post-CMOS module. The CMOS chip consists of four metal layers. RIE etch of CHF3 O2 etches dielectric layers not covered by metal layers. The top metal layers will dene the thickness of the structure. Isotropic silicon etch with an SF6 plasma undercuts and releases the structure.

Circuit and system integration

The digital circuitry follows the CMOS development track. The analog circuitry has transistor sizes which are larger because of transconductance, noise and matching. RF design has an advantage in the steady progress of the CMOS development track due to an increase in transit frequency and reduction in parasitic capacitance. This has drastically increased the frequency range for RF MEMS. The fabrication of masks places a huge constrain on scaling between MEMS and CMOS, and it also increases the complexity of the mask development cycle. The mask development must be determined from simulations and experiments due to the lack of software integration tools. The interface between the CMOS-MEMS chip and the off-chip data processing unit can be done in three ways. Analog output places a big challenge in the conditioning of the signal off-chip without noise and perfomance degration. Digital output requires a microcontroller or FPGA for acquiring the signal. High-volume producers of CMOS and MEMS use complete systems where the sensed signal is thorougly processed. A standard digital interface display and analog read-out circuitry is normal. There is a trend going towards this system-on-chip module. Fully differential designs are preferred because the perfomance of integrated microsystems can be improved. The signal-to-noise ratio is improved by including lters. Digitalto-analog converters may also be used to tune the circuit (for example actuation), this enables the possibility to calibrate the integrated system. Using ADCs and DACs places a demand in accurate voltage references. Using a diode voltage and a voltage that is proportional to absolute temperature creates a temperature independent voltage reference approximately close to the bandgap voltage of silicon. Impedance matching to the wire bonds is an important factor in packaging.

8 Conclusion

The integration of CMOS and MEMS together has been a eld of investigation and research for a long time. The trend has been to make CMOS and MEMS seperately and then wire bonding the two dies together in one package. The reason for this is because the MEMS processes are behind the CMOS development, as well as the costs for integrating them together. Therefore the trend has been to make CMOS and MEMS seperately, where only Analog Devices and Texas Instruments has been the only companies to volume produce CMOS-MEMS products. Making CMOS and MEMS on the same die requires preparation and modication of an existing CMOS process. It is both challenging and expensive to do this. Depending on the product to be made, the result may outweigh the effort to integrate CMOS and MEMS. Excluding discrete components, less packaging, less requirement for signal matching between CMOS and MEMS are all parameters that indicates that integrating CMOS and MEMS is a benet. RF MEMS in particular benets from the fact that less wire bonding increases the frequency range for the system because of the CMOS development as well as reduction of parasitic capacitances. Pre- and Post-CMOS are the most promising modules to integrate the two parts. Pre-CMOS has its advantages by placing no constraints on the CMOS part, and it has no thermal budget to stay below during the MEMS module. Post-CMOS is more exible because the MEMS structure can be placed on top or beside the CMOS, the CMOS may follow the CMOS development track, and it is also possible to manufacture the two modules at respective foundries. Modication of

the CMOS processes, mask development, system integration software tools, foundry processing and costs are the most constraining factors of integrating CMOS and MEMS. The making of a RF MEMS circuit with integrated microelectronics can be performed with the following candidates: INTEGRAM from QinetiQ, ASIMPS from MEMSCAP or Dalsas intelligent MEMS process.

References

[1] F. Chen, U. et al, CMOS-MEMS Resonant RF Mixer-lters , Micro Electro Mechanical Systems, 2005. MEMS2005. 18th IEEE International Conference on 30 Jan.-3 Feb. 2005 Page(s):24-27 [2] M. Beunder, Choosing a CMOS Compatible MEMS Manufacturing Approach , Cavendish Kinetics B.V.,CEO The Netherlands.,COMS 2004 [3] O. Brand, G.K. Fedder, CMOS-MEMS , Advanced Micro & nanosystems, Volume 2, WILEY-VCH Verlag GmbH & Co. KGaA, 2005, chapter 1,2,5 and 11. rmer, et al, Method of anisotropically etching silicon , [4] F. L a German Patent DE 4241045, US Patent 5501893, 1994 [5] L.J. Van der Pauw Philips Res. Rep. , 13, 1-9, 1958. [6] P.M. Osterberg, S.D. Senturia, J. Microelectromech. Syst. , 11, 512-520, 1997. [7] B.D. Jensen, et al, Proc. MSM 99, San Juan, Puerto Rico , pp. 206-209, 1999. [8] L. Parameswaran, et al, A merged MEMS-CMOS process using silicon wafer bonding , Proc. IEEE IEDM 95, pp. 613616, 1995. [9] T.A. Core, et al, Fabrication technology for an integrated surface micromachined sensor , Solid State Technol., 39-47, 1993. [10] T. Scheiter, et al, Full integration of a pressure-sensor system into a standard BiCMOS process , Sens. Actuators A, 67, 211214, 1998. [11] H. Dudaicevs, et al, Surface micromachined pressure sensors with integrated CMOS read-out electronics , Sens. Actuators A, 45, 157-163, 1994. [12] M. Offenberg, et al, Novel process for a monolothic integrated accelerometer , Proc. Transducers 95, pp. 589-592, 1995. [13] C. V. Jahnes, et al, Simultaneous fabrication of RF MEMS switches and resonators using copper based CMOS interconnect manufacturing methods , Proc. IEEE Microelectromechanical Systems Conference (MEMS 2004), pp. 789-792, 2004 [14] A E. Franke Polycrystalline silicon-germanium lms for integrated microstructures , J. Microelectromechan. Syst. 2003, 12, 160-171, 2003. [15] G.K. Fedder., et al, Laminated high-aspect-ratio microstructures in a conventional CMOS process , Sens. Actuation A, 57, 103-110, 1996. [16] O. Paul, et al, Sacricial aluminum etching for CMOS microstructures , Proc. IEEE MEMS 97, pp. 523-528, 1997. ller, et al, Solid-State Sensors, actuators and microsys[17] T. Mu tems , 2005. Digest of Technical Papers, Volume 2, 5-9 June 2005 Page(s):2074-2077 Vol.2 [18] J.A. Geen, et al, Single-chip surface micromachined integrated gyroscope with 50/h Allan deviation , IEEE J. Solid-State Circuits, 37, 1860-1866, 2002 [19] J. Chae, et al, A hybrid silicon-on-glass (SOG) lateral microaccelerometer with CMOS readout circuitry , Proceedings of the 15th IEEE international Conference on Micro Electro Mechanical Systems (MEMS 2002), Las Vegas, NV, pp. 623626, 2002. [20] C-C. Lo, et al, Assessment of silicon wafter material for the fabrication of integrated circuit sensors , J. Electrochem. Soc., 147, 1604-1611, 2000

You might also like

- CMOS Process FlowDocument35 pagesCMOS Process Flowag21937570No ratings yet

- CCD Detectors LectureDocument69 pagesCCD Detectors Lecturebozadeda100% (1)

- MIM Cap ModelDocument4 pagesMIM Cap ModelDuc DucNo ratings yet

- CMOS Design RulesDocument21 pagesCMOS Design Rulesrakheep123No ratings yet

- Question PDFDocument12 pagesQuestion PDFjushwanth100% (1)

- VLSI DesignDocument11 pagesVLSI DesignKennyNo ratings yet

- A Dynamic Analysis of The Dickson Charge Pump CircuitDocument10 pagesA Dynamic Analysis of The Dickson Charge Pump CircuitSoumik SarkarNo ratings yet

- Modeling and Simulation of Operational Amplifier Using Verilog - AmsDocument5 pagesModeling and Simulation of Operational Amplifier Using Verilog - Amsangelo_lopez1993No ratings yet

- Dual Gate BucketDocument8 pagesDual Gate BucketVigneswaran VigneshNo ratings yet

- Design and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierDocument5 pagesDesign and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierChristian Montano GalvezNo ratings yet

- Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceDocument8 pagesPerformance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceAnonymous kw8Yrp0R5r100% (1)

- Cmos Two Stage OpamppublishedDocument5 pagesCmos Two Stage Opamppublisheddeepak pandeyNo ratings yet

- Design of 12-Bit DAC Using CMOS TechnologyDocument5 pagesDesign of 12-Bit DAC Using CMOS TechnologysanthoshNo ratings yet

- Nuclear Science & Engineering: Presentation On Carbon Nanotube Field Effect Transistor - Prashant Ranjan 2k14/NSE/21Document17 pagesNuclear Science & Engineering: Presentation On Carbon Nanotube Field Effect Transistor - Prashant Ranjan 2k14/NSE/21ranjan_prashant52No ratings yet

- Two-Stage Operational Amplifier Design Using Gm/Id MethodDocument7 pagesTwo-Stage Operational Amplifier Design Using Gm/Id Methodabhinav kumarNo ratings yet

- Design of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Document2 pagesDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Shahin ShahNo ratings yet

- Yuan - 2010 - Lecture 11 CMOS Imaging SensorDocument44 pagesYuan - 2010 - Lecture 11 CMOS Imaging SensorAmaniDarwishNo ratings yet

- Voltage Scaling for Dynamic Power ReductionDocument94 pagesVoltage Scaling for Dynamic Power Reductionvbharathi072100% (1)

- VLSI I - V CharacteristicsDocument46 pagesVLSI I - V CharacteristicsMALATHI .LNo ratings yet

- Assembly Language and Computer Organization ExplainedDocument68 pagesAssembly Language and Computer Organization ExplainedNicolas AmezquitaNo ratings yet

- Mod1VLSI TECHNOLOGY1Document65 pagesMod1VLSI TECHNOLOGY1Jomon VargheseNo ratings yet

- Amplifier Project GradDocument5 pagesAmplifier Project Gradمحمد قاسم نفل سميرNo ratings yet

- Simulation, Analysis and Comparison of SET and CMOS Hybrid CircuitsDocument6 pagesSimulation, Analysis and Comparison of SET and CMOS Hybrid CircuitsColin ValentineNo ratings yet

- CCD Toshiba TCD1304d - DatasheetDocument15 pagesCCD Toshiba TCD1304d - DatasheetdiasyuriNo ratings yet

- Design, Fabrication and Testing of Analog IC AmplifiersDocument17 pagesDesign, Fabrication and Testing of Analog IC AmplifiersNurul Hanim HashimNo ratings yet

- VLSI DESIGN Bit PaperDocument2 pagesVLSI DESIGN Bit Papervenkiscribd444No ratings yet

- Toshiba TCD1304AP CCD Array PDFDocument15 pagesToshiba TCD1304AP CCD Array PDFLazScibdNo ratings yet

- Verilog HDL: A Guide To Digital Design DS TH I and SynthesisDocument62 pagesVerilog HDL: A Guide To Digital Design DS TH I and SynthesisSharan ChaitanyaNo ratings yet

- 7.3 6T SRAM Cell: 7.4 Ring Oscillator 7. Case Studies 7.2 CMOS InverterDocument4 pages7.3 6T SRAM Cell: 7.4 Ring Oscillator 7. Case Studies 7.2 CMOS InverterGowtham SpNo ratings yet

- Semiconductor Devices-Module-1 PDFDocument60 pagesSemiconductor Devices-Module-1 PDFShivam KumarNo ratings yet

- Layout of CMOS Analog CircuitsDocument0 pagesLayout of CMOS Analog CircuitsarammartNo ratings yet

- Photoelectric Effect in CCD (Charge Coupled Devices)Document20 pagesPhotoelectric Effect in CCD (Charge Coupled Devices)MohsensorNo ratings yet

- CMOS Translinear CellsDocument4 pagesCMOS Translinear CellsSumitChoudharyNo ratings yet

- CMFB DesignDocument4 pagesCMFB Designaminkhan83No ratings yet

- Preventing Latch Up - NationalDocument2 pagesPreventing Latch Up - Nationalkvpk_vlsiNo ratings yet

- Understanding About CMOS Fabrication TechnologyDocument4 pagesUnderstanding About CMOS Fabrication TechnologyJayesh RaghuwanshiNo ratings yet

- L18 Matching LayoutDocument41 pagesL18 Matching LayouttejanossamNo ratings yet

- Application-Specific Integrated Circuits (ASICs)Document5 pagesApplication-Specific Integrated Circuits (ASICs)ijeteeditor100% (1)

- Ir DropDocument7 pagesIr DropAamir ShaikNo ratings yet

- Microelectronics For Students PDFDocument27 pagesMicroelectronics For Students PDFJONNA ACABONo ratings yet

- Modeling of A CMOS Active Pixel Image Sensor: Towards Sensor Integration With Microfluidic DevicesDocument63 pagesModeling of A CMOS Active Pixel Image Sensor: Towards Sensor Integration With Microfluidic DevicesMatVPNo ratings yet

- Kimoto SiC Overview PDFDocument28 pagesKimoto SiC Overview PDFAlberto CastellazziNo ratings yet

- Brunda V (1PE15EC039) Jigyasa N. Maheshwari (1PE15EC060) : Project Report Phase 1Document43 pagesBrunda V (1PE15EC039) Jigyasa N. Maheshwari (1PE15EC060) : Project Report Phase 1Nikhil NikiNo ratings yet

- CXD1265 - CCD Camera Timing GeneratorDocument24 pagesCXD1265 - CCD Camera Timing Generator40818248No ratings yet

- CMOS BasicsDocument41 pagesCMOS BasicsYeshoda MallikarjunaNo ratings yet

- Cmos Electronic PDFDocument356 pagesCmos Electronic PDFJustin WilliamsNo ratings yet

- Stick Diagram BasicsDocument26 pagesStick Diagram Basicssanju012100% (1)

- Fundamentals of Rapid Prototyping TechnologiesDocument65 pagesFundamentals of Rapid Prototyping TechnologiesNurhuda Hayati0% (1)

- Fabrication of MOSFETDocument48 pagesFabrication of MOSFETYogesh TiwariNo ratings yet

- Density of States and Fermi Energy ConceptsDocument25 pagesDensity of States and Fermi Energy ConceptssptbalaNo ratings yet

- Noise Tutorial: Low-Frequency CMOS Analog Design: Rafael J. Betancourt-ZamoraDocument30 pagesNoise Tutorial: Low-Frequency CMOS Analog Design: Rafael J. Betancourt-ZamoraPaul ShineNo ratings yet

- Unit 2 - CMOS Logic, Fabrication and LayoutDocument34 pagesUnit 2 - CMOS Logic, Fabrication and LayoutphillipNo ratings yet

- Lecture - Slides - 2.8 The Three-Terminal MOS Structure - Part 1Document6 pagesLecture - Slides - 2.8 The Three-Terminal MOS Structure - Part 1Cesar Santiago Bolaño SalazarNo ratings yet

- Super Source FollowerDocument27 pagesSuper Source Followerkhlsakfn100% (2)

- Cmos Analog Ic Design Course Plan NewDocument9 pagesCmos Analog Ic Design Course Plan Newjim2001No ratings yet

- CMOS Compatible Bulk Micromachining: John Ojur Dennis, Farooq Ahmad and M. Haris KhirDocument20 pagesCMOS Compatible Bulk Micromachining: John Ojur Dennis, Farooq Ahmad and M. Haris KhirAlexandra MunteanuNo ratings yet

- Introducere in Sisteme Micro-Electro-Mecanice (MEMS)Document27 pagesIntroducere in Sisteme Micro-Electro-Mecanice (MEMS)razvanjuvNo ratings yet

- Chapter IIIDocument43 pagesChapter IIIJerry boyNo ratings yet

- DEC50143 CHAPTER 2 - PART C - EditDocument49 pagesDEC50143 CHAPTER 2 - PART C - Edity meNo ratings yet

- Self-healing Ceramic Matrix Composites: A MonographFrom EverandSelf-healing Ceramic Matrix Composites: A MonographNo ratings yet

- Bank Locker Security Using GSMDocument4 pagesBank Locker Security Using GSMxpeprisheyNo ratings yet

- TI CAN Bus TutorialDocument15 pagesTI CAN Bus TutorialMohamedHassanNo ratings yet

- Tutorial SimcouplerDocument10 pagesTutorial SimcouplerJosé Luis Camargo OlivaresNo ratings yet

- Usb ProtocolDocument27 pagesUsb Protocolxpeprishey100% (2)

- Robust Audio Steganography Using Direct-Sequence Spread Spectrum TechnologyDocument6 pagesRobust Audio Steganography Using Direct-Sequence Spread Spectrum TechnologyPrakhar ShuklaNo ratings yet

- Analyzing The Effect of Gain Time On Soft-Task Scheduling Policies in Real-Time SystemsDocument14 pagesAnalyzing The Effect of Gain Time On Soft-Task Scheduling Policies in Real-Time SystemsxpeprisheyNo ratings yet

- RTS Nptel MaterialDocument30 pagesRTS Nptel MaterialBavya MohanNo ratings yet

- Ethernet (Ieee 802Document22 pagesEthernet (Ieee 802xpeprishey100% (2)

- 27 MulticoreDocument67 pages27 MulticoreKush ChaudharyNo ratings yet

- Development of Smart Blind StickDocument7 pagesDevelopment of Smart Blind StickxpeprisheyNo ratings yet

- Embedded InternetDocument31 pagesEmbedded InternetxpeprisheyNo ratings yet

- Ultrasonic Car ParkingDocument7 pagesUltrasonic Car Parkingxpeprishey100% (3)

- Iris RecognitionDocument5 pagesIris RecognitionxpeprisheyNo ratings yet

- Spread Spectrum Audio Watermarking Scheme Based On Psychoacoustic ModelDocument5 pagesSpread Spectrum Audio Watermarking Scheme Based On Psychoacoustic ModelxpeprisheyNo ratings yet

- Trial PMR Pahang 2010 English (p1)Document9 pagesTrial PMR Pahang 2010 English (p1)abdfattah50% (2)

- F-1audio Watermarking in The FFT Domain Using Perceptual MaskingDocument5 pagesF-1audio Watermarking in The FFT Domain Using Perceptual MaskingxpeprisheyNo ratings yet

- DFF and register Verilog codeDocument39 pagesDFF and register Verilog codeAswinCvrnNo ratings yet

- Reversible Resampling of Integer SignalsDocument10 pagesReversible Resampling of Integer SignalsxpeprisheyNo ratings yet

- Real-Time CommunicationDocument21 pagesReal-Time Communicationxpeprishey100% (1)

- Reversible Resampling of Integer SignalsDocument10 pagesReversible Resampling of Integer SignalsxpeprisheyNo ratings yet

- Signature Identification MATLAB SynopsisDocument21 pagesSignature Identification MATLAB SynopsisAditya Mehar67% (3)

- Principles of Audio WatermarkingDocument3 pagesPrinciples of Audio WatermarkingxpeprisheyNo ratings yet

- Signature Identification MATLAB SynopsisDocument21 pagesSignature Identification MATLAB SynopsisAditya Mehar67% (3)

- F-1audio Watermarking in The FFT Domain Using Perceptual MaskingDocument5 pagesF-1audio Watermarking in The FFT Domain Using Perceptual MaskingxpeprisheyNo ratings yet

- Real-Time CommunicationDocument21 pagesReal-Time Communicationxpeprishey100% (1)

- 89s51 DatasheetDocument27 pages89s51 DatasheetazizboysNo ratings yet

- CAN ProtocolDocument9 pagesCAN ProtocolMalu Mohan100% (1)

- Brand HaloDocument3 pagesBrand HaloxpeprisheyNo ratings yet

- Need and Benefits of TrainingDocument22 pagesNeed and Benefits of TrainingxpeprisheyNo ratings yet

- Lifecycle of An Entrepreneurial VentureDocument20 pagesLifecycle of An Entrepreneurial Venturexpeprishey100% (3)

- EC302Document27 pagesEC302api-3853441No ratings yet

- Stick DiagramDocument24 pagesStick DiagramHasan SadatNo ratings yet

- Module 4 Exam 19 Electronic Fundamentals AnswersDocument3 pagesModule 4 Exam 19 Electronic Fundamentals AnswersHshsjNo ratings yet

- III B.Tech Power Electronics Lecture NotesDocument197 pagesIII B.Tech Power Electronics Lecture NotesArunkuma81No ratings yet

- 4.1 INTRODUCTION TO ELECTRONICS SyllabusDocument22 pages4.1 INTRODUCTION TO ELECTRONICS SyllabusTynoh MusukuNo ratings yet

- 半导体物理与器件第四版课后习题答案5Document13 pages半导体物理与器件第四版课后习题答案5DavidNo ratings yet

- SILICA NXP Discretes Selection GuideDocument86 pagesSILICA NXP Discretes Selection Guidebuggy buggerNo ratings yet

- Sources of Local Variation and Device Mismatch ModelingDocument4 pagesSources of Local Variation and Device Mismatch ModelingnadeemjuttNo ratings yet

- LED in PhysicsDocument10 pagesLED in PhysicsArian SalemNo ratings yet

- VLSI Circuit Design Processes: Stick Diagrams and ScalingDocument21 pagesVLSI Circuit Design Processes: Stick Diagrams and Scaling121910401008 PRATIK ADHIKARYNo ratings yet

- BC337-16/25/40 BC338-16/25/40 NPN Transistor Preliminary Small Signal DiodeDocument3 pagesBC337-16/25/40 BC338-16/25/40 NPN Transistor Preliminary Small Signal DiodeRajesh PrabhuNo ratings yet

- Talukdar2019 Article ANovelExtendedSourceTFETWithΔpDocument9 pagesTalukdar2019 Article ANovelExtendedSourceTFETWithΔpkavicharan MummaneniNo ratings yet

- Semiconductor Devices Physics PN Junction Diode CharacteristicsDocument17 pagesSemiconductor Devices Physics PN Junction Diode Characteristicsg_groupNo ratings yet

- Four Types: GAS Laser Semiconductor Laser Doped Insulator Dye Laser in Semiconductor Laser, The Action Is The Result of Three Key ProcessesDocument13 pagesFour Types: GAS Laser Semiconductor Laser Doped Insulator Dye Laser in Semiconductor Laser, The Action Is The Result of Three Key ProcessesMd Jahirul IslamNo ratings yet

- Semiconductor PhysicsDocument37 pagesSemiconductor Physicsgirishkumardarisi254No ratings yet

- Study Guide Solid State Electronics Teacher EditableDocument8 pagesStudy Guide Solid State Electronics Teacher EditablethamerNo ratings yet

- Fet Canal N 5amp 500V TK5A50DDocument5 pagesFet Canal N 5amp 500V TK5A50DAntonio ChavezNo ratings yet

- J 6812Document5 pagesJ 6812mauito27No ratings yet

- BD130 NPN Silicon Transistor Power Linerar and Switching ApplicationsDocument3 pagesBD130 NPN Silicon Transistor Power Linerar and Switching ApplicationsDabro FabioNo ratings yet

- SZ.818.015C100 Last Mutation: 201202211410SSTADocument7 pagesSZ.818.015C100 Last Mutation: 201202211410SSTAQuang Huy HàNo ratings yet

- Solar Cells: History, Working Principle and Fabrication Process, Ultimate UsesDocument8 pagesSolar Cells: History, Working Principle and Fabrication Process, Ultimate UsesPRATYAKSHA SHEKHARNo ratings yet

- ECE 027 - Simulation Activity 3.1 THE BIPOLAR JUNCTION TRANSISTOR FAMILIARIZATION AND CHARACTERISTICSDocument10 pagesECE 027 - Simulation Activity 3.1 THE BIPOLAR JUNCTION TRANSISTOR FAMILIARIZATION AND CHARACTERISTICSEmerson EspelaNo ratings yet

- Elect Dev Cir Capitulo 5 Part1Document63 pagesElect Dev Cir Capitulo 5 Part1Jaime VargasNo ratings yet

- Accurately Modeling GaAs MESFETs for Circuit SimulationDocument9 pagesAccurately Modeling GaAs MESFETs for Circuit SimulationManuel GaytanNo ratings yet

- 04 Inverter 6up PDFDocument11 pages04 Inverter 6up PDFutpalNo ratings yet

- 24V 1A Flyback Fairchild WWW - Iranswitching.irDocument1 page24V 1A Flyback Fairchild WWW - Iranswitching.irSaeid MirNo ratings yet

- MOSFET Current Mirror PDFDocument27 pagesMOSFET Current Mirror PDFaliNo ratings yet

- D1402Document3 pagesD1402ban4444No ratings yet

- Micro Project On Transistor As A SwitchDocument15 pagesMicro Project On Transistor As A SwitchAyushi Rahane50% (4)

- Lecture-7,8 Special Purpose DiodesDocument131 pagesLecture-7,8 Special Purpose DiodesDhananjayLekshmiNarayanNo ratings yet