Professional Documents

Culture Documents

04285962, DJS

Uploaded by

Deepu ChinnaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

04285962, DJS

Uploaded by

Deepu ChinnaCopyright:

Available Formats

2600 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO.

5, OCTOBER 2007

A Dual Five-Level Inverter-Fed Induction Motor

Drive With Common-Mode Voltage Elimination

and DC-Link Capacitor Voltage Balancing Using

Only the Switching-State RedundancyPart I

P. N. Tekwani, Student Member, IEEE, R. S. Kanchan, Student Member, IEEE, and

K. Gopakumar, Senior Member, IEEE

AbstractFor a dual ve-level inverter-fed induction motor

(IM) drive, effects of dc-neutral currents on dc-link capacitor

voltage uctuations are analyzed in this paper. Operating limita-

tions in achieving the dual task of common-mode voltage elimi-

nation and dc-link capacitor voltage balancing with a single dc

power supply are further investigated for the proposed drive.

In this paper, an open-loop control scheme, which uses only the

availability of redundant switching states for the inverter control,

is presented. Limitation of proposed open-loop control to take

corrective action for any existing unbalance in capacitor voltages

calls for a closed-loop control scheme, which is presented in

Part II of this paper.

Index TermsCommon-mode voltage (CMV) elimination,

dc-link capacitor voltage balancing, induction motor (IM) drive,

multilevel inverter, open-loop control, switching-state redundancy.

I. INTRODUCTION

M

ULTILEVEL inverters are suitable for high-voltage

high-power applications, because of the possibility of

multilevel output voltage system with low voltage levels

[1][7]. But due to pulsewidth-modulation (PWM) control the

presence of alternating common-mode voltage (CMV), which

results in bearing currents and ground leakage currents is a very

well known phenomenon in the PWM inverter-fed induction

motor (IM) drive systems. Also, inherent unbalance in the

dc-link capacitor voltages of neutral-point-clamped (NPC) a

multilevel inverter causes lower order harmonics at the inverter

output, torque pulsation, and increased voltage stress on power

switching devices. In most of the literature, the problems

of CMV [8][11] and dc-link capacitor voltage unbalance

[12][18] are dealt with as separate entities. A dual inverter-

fed open-end winding IM structure offers a greater number of

redundant switching state combinations compared to that of

the single inverter-fed drive of the same output voltage levels

[10], [11]. Exploiting this advantage, complete elimination of

CMV is achieved in [10] and [11] for three-level and ve-

level inverter-fed open-end winding IM drives, respectively.

Inherent limitations of multilevel inverters for achieving the

Manuscript received October 1, 2005; revised January 11, 2006. Abstract

published on the Internet January 14, 2007.

The authors are with the Centre for Electronics Design and Technology,

Indian Institute of Science, Bangalore 560012, India (e-mail: pntek@cedt.

iisc.ernet.in; rkanchan@cedt.iisc.ernet.in; kgopa@cedt.iisc.ernet.in).

Digital Object Identier 10.1109/TIE.2007.892633

dc-link capacitor voltage balancing are described in [12]. It

has been reported in [12] and [13] that with the presence

of a larger number of dc-link capacitors (dc-neutral points),

the task of capacitor voltage balancing becomes inherently

more complicated (especially at the higher modulation indices)

with increasing levels of multilevel NPC inverters. Capacitor

voltage balancing schemes presented in [13][15] for a ve-

level NPCinverter, suggest the use of extra hardware in addition

to the space vector PWM (SVPWM) or carrier-based PWM

control techniques. This extra hardware may be in the form

of buckboost converters (dc-choppers) [13], [14] or back-to-

back connection of multilevel NPC-controlled front-end con-

verter and a multilevel NPC inverter [15]. A ve-level inverter

topology with self voltage balancing presented in [9], with

simulation results only, requires 20 switching devices and six

additional capacitors per pole. It has been concluded in [17]

that voltage balancing of dc-link capacitors in a four-level

NPC inverter with single dc power supply is not possible,

even if there is no restriction for the selection of redundant

vectors. The SVPWM control scheme presented in [18] for dc-

link capacitor voltage balancing in a NPC ve-level inverter

provides frequency of capacitor voltage ripple three-times the

frequency of ac load current. Concurrent achievement of neu-

tral point balancing and CMV cancellation in the three-level

NPC inverter is reported in [19] at the additional cost of a

buckboost converter. The control scheme described in [20], for

a three-level inverter-fed open-end winding IM drive, achieves

this dual task without using additional hardware. This part

of the paper presents a dual ve-level inverter-fed open-end

winding IM drive for CMV elimination and dc-link capacitor

voltage balancing in the entire modulation range. An open-loop

control scheme, which uses only the availability of redundant

switching states for inverter voltage vectors, is presented. The

proposed scheme does not need additional power circuit hard-

ware such as a buckboost converter or controlled front-end

converter.

II. PROPOSED FIVE-LEVEL INVERTER-FED IM DRIVE

WITH CMV ELIMINATION

The power schematic of the proposed dual inverter-fed open-

end-winding IM drive is shown in Fig. 1, where each of the

ve-level inverters (inverter A and inverter A

) is formed by

cascading a three-level NPC inverter with two conventional

0278-0046/$25.00 2007 IEEE

TEKWANI et al.: INDUCTION MOTOR DRIVE WITH VOLTAGE ELIMINATION AND VOLTAGE BALANCINGPART I 2601

Fig. 1. Power schematic of the proposed dual ve-level inverter-fed open-end-

winding IM drive.

two-level inverters [11]. Hence, the proposed inverter offers a

simple power-bus structure and needs a fewer number of diodes

compared to the traditional ve-level NPC inverter [11]. Also,

the proposed cascaded structure can be easily extended in a

modular fashion for realizing much higher levels for multi-

level inverters. The required blocking voltage capability of an

individual device is V

dc

/8 for S

11

, S

14

, S

41

, and S

44

and

V

dc

/5.33 [i.e., 3V

dc

/(2 8)] for S

21

, S

34

, S

24

, and S

31

in

Fig. 1. If V

AO

, V

BO

, and V

CO

are the pole voltages of inverter

A, and V

A

O

, V

B

O

, and V

C

O

are the pole voltages of inverter

A

(Fig. 1), then the voltage space vector for inverter A and

inverter A

can be represented as (1). Equation (2) gives the

machine phase voltages. Switching states and voltage vectors

of inverter A or inverter A

are shown in Fig. 2(a) [11]. The

combined voltage space vector for Fig. 1 is expressed in (3).

The CMV generated by inverter Aand inverter A

are expressed

in (4) [10], [11]. Hence, the resultant CMV in the drive system

(Fig. 1) can be represented as in (5). Thus, we have

V

SR1

=v

AO

+ v

BO

e

j120

+ v

CO

e

j240

V

SR2

=v

A

O

+ v

B

O

e

j120

+ v

C

O

e

j240

(1)

v

AA

=v

AO

v

A

v

BB

=v

BO

v

B

v

CC

=v

CO

v

C

O

(2)

V

SR

=v

AA

+ v

BB

e

j120

+ v

CC

e

j240

(3)

v

CMA

=(v

AO

+ v

BO

+ v

CO

)/3

v

CMA

=(v

A

O

+ v

B

O

+ v

C

O

)/3 (4)

v

CM

=v

CMA

v

CMA

. (5)

For the individual ve-level inverter, a total of 19 switching

states (and corresponding voltage vectors), which generate zero

CMV, are shown shaded in Fig. 2(a). When these 19 switching

states are exclusively used to switch inverter A and inverter A

,

a combined ve-level inverter voltage space vector structure

with zero CMV can be obtained, as shown in Fig. 2(b) [11].

Consequently, inverter Aand inverter A

are supplied with com-

mon dc links in Fig. 1 [11]. The switching-state combinations

(generating zero CMV) for different voltage vectors in the 30

segment D

1

O

3

of Fig. 2(b) are shown in Table I [11].

Fig. 2. (a) Switching states and voltage vectors of the ve-level inverter

(inverter A or inverter A

); a total of 19 switching states and corresponding

voltage vectors generating zero CMV are shown shaded. (b) Combined inverter

voltage vector locations with zero CMV (a total of 61 voltage space vectors

form 96 triangular sectors resulting in a ve-level inverter voltage space vector

structure).

III. ANALYSIS OF DC-LINK CAPACITOR VOLTAGE

VARIATIONS AND CONDITIONS FOR

VOLTAGE BALANCING

For Fig. 1, the preferred practical approach is to provide

a single dc power supply of voltage V

dc

/2, as shown in

Fig. 3(a), where each inverter leg is represented as a single-pole

ve-throw switch. The inverter switching functions are dened

as S

A

, S

B

, and S

C

and S

A

, S

B

, and S

C

for the legs of

inverter A and inverter A

, respectively. The switching function

for each leg of the inverter can attain any value out of 0, 1, 2,

3, and 4 [Fig. 3(a)] based on the connection of that leg with

any of the ve different voltage levels 2, 1, 0, 1, and 2,

respectively. The motor phase currents are denoted as i

A

, i

B

,

and i

C

. The total current drawn by the dual inverter from the

lower dc bus, lower dc neutral, middle dc neutral, upper dc

neutral, and upper dc bus are referred to as i

0

, i

1

, i

2

, i

3

, and i

4

,

2602 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 5, OCTOBER 2007

TABLE I

SWITCHING-STATE COMBINATIONS, WHICH PRODUCE ZERO CMV, FOR DIFFERENT VOLTAGE VECTORS IN A 30

SEGMENT D

1

O

3

OF FIG. 2(b)

respectively. Similarly, inverter A currents are referred to as

i

0A

, i

1A

, i

2A

, i

3A

, and i

4A

, whereas inverter A

currents are

referred to as i

0A

, i

1A

, i

2A

, i

3A

, and i

4A

. Rectier current is

represented by i

R

. Voltages across the capacitors C1, C2, C3,

and C4 are denoted as v

C1

, v

C2

, v

C3

, and v

C4

, respectively.

For the system schematic shown in Fig. 3(a), the pole voltage

with respect to the lower dc bus for inverter A (v

AL

, v

BL

, v

CL

)

and inverter A

(v

A

L

, v

B

L

, v

CB

L

), can be expressed in terms

of switching functions and capacitor voltages, as shown in

(6) and (7), respectively, where () is the Dirac delta func-

tion [14]. Hence, for the normal operation of the drive (i.e.,

v

C1

= v

C2

= v

C3

= v

C4

= V

dc

/8), the inverter pole voltage

with respect to the lower dc bus is proportional to the numeric

value of the inverter switching function for that pole (leg), as

shown in (8). The currents drawn from the nodes of the dc

link can be represented in terms of the motor phase currents

as a dual of (6) and (7) and are shown in matrix form in (9)

for inverter A and inverter A

, respectively. Using (9), the total

currents drawn from the dc-link nodes can be represented as

a sum of the currents drawn by the individual inverters (10).

Considering the balanced three-phase load for Fig. 3(a), the

sum of the motor phase currents as well as the dc-link node

currents can be considered as zero (i.e., i

A

+ i

B

+ i

C

= 0, and

i

0

+ i

1

+ i

2

+ i

3

+ i

4

= 0). Now, substituting i

C

= i

A

i

B

and removing the dependent variable i

4

, (10) is simplied

to (11). For Fig. 3(a), now, the currents owing through the

capacitors can be represented as in (12). Hence, for C1 =

C2 = C3 = C4 = C, the dc-link capacitors voltages can be

represented in terms of dc-link node currents and rectier

current as in (13). Using (13), the difference between voltages

of the adjacent capacitors of Fig. 3(a) can be given as in (14).

From (11) and (14), the dependency of difference between the

voltages of the adjacent capacitors of the dc link on the inverter

switching functions can be obtained as shown in (15). It is

evident from (14) that the individual net currents drawn from

the dc-link nodes 1, 0, and 1 [Fig. 3(a)] are responsible

for capacitor voltage unbalances. Thus, the balanced dc-link

condition (i.e., v

43

= v

32

= v

21

= 0) occurs only when

the individual net currents drawn from the upper, middle, and

lower dc neutrals of Fig. 3(a) are zero (i.e., i

3

= i

2

= i

1

= 0).

From (15), it can be seen that whenever the switching functions

S

A

, S

B

, S

C

and S

A

, S

B

, S

C

attain the value equal to 3, 2,

or 1, there exists a tendency of capacitor voltage variations,

because of the ow of dc-neutral currents i

3

, i

2

, and i

1

. See

(6)(15) on the next page.

IV. EFFECTS OF SWITCHING-STATE COMBINATIONS ON

BALANCING OF CAPACITOR VOLTAGES

For ease of analysis, all the inverter voltage vectors of

Fig. 2(b) are divided into ve main groups, as shown in

Table II. The effects of redundant switching-state combina-

tions of voltage vectors (Table I), belonging to each of these

ve groups, on the charging and discharging of dc-link ca-

pacitors are studied. Based on the connections of machine

phase winding terminals with the dc-link nodes [Fig. 3(a)], the

currents drawn from the dc-link nodes to the machine phase

windings and vice versa are assigned with proper signs, as

given in Table III. All the switching-state combinations of

voltage vector O

(Fig. 2(b) and Table I) do not cause any

effect on the capacitor voltages, as they do not connect the

motor phase windings across any of the capacitors of the

dc link. Hence, for the capacitor voltage balancing point of

view, all the switching-state combinations of O

(ZV group,

Table II) are equivalently represented as z, z, z in terms

of currents owing through the dc-link nodes 1, 0, and

1 [i.e., i

3

, i

2

, and i

1

, Fig. 3(a)], respectively, where z

indicates zero current.

Fig. 3(b) shows the connections of machine phase wind-

ings with dc-link nodes for some of the redundant switching-

state combinations of voltage vector A

1

of the 2LV group

(Tables I and II). Based on Table III, for the switching-state

combination 10 1, 000 [of A

1

, Fig. 3(b)], the dc-link node

currents i

3

, i

2

, i

1

[Fig. 3(a)] can be equivalently represented

as i

A

, (i

A

i

C

), i

C

, respectively, in terms of the machine

phase currents. From this equivalent representation and (14), it

is found that 10 1, 000 causes, increase in v

43

= v

C4

v

C3

proportional to current i

A

, increase or decrease in v

32

=

v

C3

v

C2

based on the resultant amplitude of (i

A

i

C

),

and decrease in v

21

= v

C2

v

C1

proportional to i

C

. Sim-

ilarly, based on Table III, 000, 101 of A

1

[Fig. 3(b)] can

be equivalently represented as i

C

, (i

A

+ i

C

), i

A

. It is

evident from their equivalent representations, that switching-

state combinations 10 1, 000 and 000, 101 cause the

TEKWANI et al.: INDUCTION MOTOR DRIVE WITH VOLTAGE ELIMINATION AND VOLTAGE BALANCINGPART I 2603

v

AL

=(s

A

1)v

C1

+ (s

A

2)(v

C1

+ v

C2

) + (s

A

3)(v

C1

+ v

C2

+ v

C3

)

+ (s

A

4)(v

C1

+ v

C2

+ v

C3

+ v

C4

)

v

BL

=(s

B

1)v

C1

+ (s

B

2)(v

C1

+ v

C2

) + (s

B

3)(v

C1

+ v

C2

+ v

C3

)

+ (s

B

4)(v

C1

+ v

C2

+ v

C3

+ v

C4

)

v

CL

=(s

C

1)v

C1

+ (s

C

2)(v

C1

+ v

C2

) + (s

C

3)(v

C1

+ v

C2

+ v

C3

)

+ (s

C

4)(v

C1

+ v

C2

+ v

C3

+ v

C4

) (6)

v

A

L

=(s

A

1)v

C1

+ (s

A

2)(v

C1

+ v

C2

) + (s

A

3)(v

C1

+ v

C2

+ v

C3

)

+ (s

A

4)(v

C1

+ v

C2

+ v

C3

+ v

C4

)

v

B

L

=(s

B

1)v

C1

+ (s

B

2)(v

C1

+ v

C2

) + (s

B

3)(v

C1

+ v

C2

+ v

C3

)

+ (s

B

4)(v

C1

+ v

C2

+ v

C3

+ v

C4

)

v

C

L

=(s

C

1)v

C1

+ (s

C

2)(v

C1

+ v

C2

) + (s

C

3)(v

C1

+ v

C2

+ v

C3

)

+ (s

C

4)(v

C1

+ v

C2

+ v

C3

+ v

C4

) (7)

v

AL

=

V

dc

8

4

k=1

k(s

A

k) =

V

dc

8

s

A

(8)

_

_

i

0A

i

1A

i

2A

i

3A

i

4A

_

_

=

_

_

(s

A

0) (s

B

0) (s

C

0)

(s

A

1) (s

B

1) (s

C

1)

(s

A

2) (s

B

2) (s

C

2)

(s

A

3) (s

B

3) (s

C

3)

(s

A

4) (s

B

4) (s

C

4)

_

_

_

_

i

A

i

B

i

C

_

_

_

_

i

0A

i

1A

i

2A

i

3A

i

4A

_

=

_

_

(s

A

0) (s

B

0) (s

C

0)

(s

A

1) (s

B

1) (s

C

1)

(s

A

2) (s

B

2) (s

C

2)

(s

A

3) (s

B

3) (s

C

3)

(s

A

4) (s

B

4) (s

C

4)

_

_

_

_

i

A

i

B

i

C

_

_

(9)

_

_

i

0

i

1

i

2

i

3

i

4

_

_

=

_

_

(s

A

0) (s

A

0) (s

B

0) (s

B

0) (s

C

0) (s

C

0)

(s

A

1) (s

A

1) (s

B

1) (s

B

1) (s

C

1) (s

C

1)

(s

A

2) (s

A

2) (s

B

2) (s

B

2) (s

C

2) (s

C

2)

(s

A

3) (s

A

3) (s

B

3) (s

B

3) (s

C

3) (s

C

3)

(s

A

4) (s

A

4) (s

B

4) (s

B

4) (s

C

4) (s

C

4)

_

_

_

_

i

A

i

B

i

C

_

_

(10)

_

_

i

0

i

1

i

2

i

3

_

_ =

_

_

[(s

A

0)(s

C

0)][(s

A

0)(s

C

0)] [(s

B

0)(s

C

0)][(s

B

0)(s

C

0)]

[(s

A

1)(s

C

1)][(s

A

1)(s

C

1)] [(s

B

1)(s

C

1)][(s

B

1)(s

C

1)]

[(s

A

2)(s

C

2)][(s

A

2)(s

C

2)] [(s

B

2)(s

C

2)][(s

B

2)(s

C

2)]

[(s

A

3)(s

C

3)][(s

A

3)(s

C

3)] [(s

B

3)(s

C

3)][(s

B

3)(s

C

3)]

_

_

_

i

A

i

B

_

(11)

i

C4

=i

R

i

4

= i

R

+ (i

0

+ i

1

+ i

2

+ i

3

) i

C3

= i

C4

i

3

i

C2

= i

C3

i

2

i

C1

= i

C2

i

1

(12)

_

_

v

C4

v

C3

v

C2

v

C1

_

_ =

1

C

_

_

_

_

_

1 0 0 0

0 1 0 0

0 0 1 0

0 0 0 1

_

_

_

_

i

C4

i

C3

i

C2

i

C1

_

_dt

_

_

=

1

C

_

_

_

_

_

1 1 1 1 1

1 0 1 1 1

1 0 0 1 1

1 0 0 0 1

_

_

_

_

i

R

i

3

i

2

i

1

i

0

_

_

dt

_

_

(13)

v

43

=v

C4

v

C3

=

1

C

_

i

3

dt v

32

= v

C3

v

C2

=

1

C

_

i

2

dt v

21

= v

C2

v

C1

=

1

C

_

i

1

dt (14)

v

43

=

1

C

_

(([(s

A

3) (s

C

3)] [(s

A

3) (s

C

3)]) i

A

+([(s

B

3) (s

C

3)] [(s

B

3) (s

C

3)]) i

B

) dt

v

32

=

1

C

_

(([(s

A

2) (s

C

2)] [(s

A

2) (s

C

2)]) i

A

+([(s

B

2) (s

C

2)] [(s

B

2) (s

C

2)]) i

B

) dt

v

21

=

1

C

_

(([(s

A

1) (s

C

1)] [(s

A

1) (s

C

1)]) i

A

+([(s

B

1) (s

C

1)] [(s

B

1) (s

C

1)]) i

B

) dt (15)

2604 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 5, OCTOBER 2007

Fig. 3. (a) System schematic and ve-level dc-bus terminology for the pro-

posed IM drive structure with a single dc power supply. (b) One of the MNDS

and ULNDS pairs of switching-state combinations for voltage vector A

1

of the

2LVgroup with their dc-neutral currents in terms of the machine phase currents.

equal and opposite currents (i

A

i

C

) and (i

A

+ i

C

),

respectively, through the middle dc neutral [i.e., current i

2

,

Fig. 3(a)]. Hence, it is clear from (14) that these two switching-

state combinations produce exactly opposite effects on the

charge balancing of the inner two capacitors of the dc link

(i.e., on v

32

= v

C3

v

C2

). Therefore, 10 1, 000 and

000, 101 [Fig. 3(b)] are termed as a pair of the middle dc-

neutral dual switching-state combinations (MNDS) of A

1

.

Similarly, the switching-state combinations 10 1, 000

and 20 2, 10 1 [of A

1

, Fig. 3(b)], with equivalent rep-

resentations i

A

, (i

A

i

C

), i

C

and i

A

, z, i

C

, respec-

tively (Table III), produce exactly opposite effects [based on

(14)] on the voltage balancing of upper two capacitors of the

dc link (i.e., on v

43

= v

C4

v

C3

), as well as on the voltage

balancing of lower two capacitors of the dc link (i.e., on v

21

=

v

C2

v

C1

). Hence, 10 1, 000 and 20 2, 10 1 con-

stitute a pair of the upper and lower dc-neutral dual switching-

state combinations (ULNDS). All the different possible MNDS

as well as ULNDS pairs for all the voltage vectors of Fig. 2(b)

are found in a similar way. A summary of available MNDS

Fig. 3. (Continued.) (c) Selection of redundant switching-state combinations

for voltage vector A

1

in successive sampling intervals (shown with their

dc-neutral currents in terms of the machine phase currents). (d) Sequence

of switching state combinations (with their dc-neutral currents in terms of

the machine phase currents) to examine the possibility of capacitor voltage

balancing within two sampling intervals when reference voltage space vector

is in a sector formed by B

1

, B

2

, and C

2

(four-level operation).

TABLE II

GROUPING OF INVERTER VOLTAGE VECTORS OF FIG. 2(b)

and ULNDS pairs for active vectors in segment D

1

O

3

of

Fig. 2(b) is provided in Table IV. A number inside the bracket

in the second and third columns of Table IV, respectively,

indicates a total number of MNDS and ULNDS pairs available

for that particular voltage vector.

TEKWANI et al.: INDUCTION MOTOR DRIVE WITH VOLTAGE ELIMINATION AND VOLTAGE BALANCINGPART I 2605

TABLE III

ASSIGNMENT OF SIGNS TO THE MACHINE PHASE

CURRENTS FOR THE ANALYSIS

TABLE IV

AVAILABILITY OF MNDS AND ULNDS PAIRS IN

SEGMENT D

1

O

3

OF FIG. 2(b)

V. EXPLORATION OF CAPACITOR VOLTAGE BALANCING

WITH A SINGLE DC POWER SUPPLY

For the position of a reference voltage vector in a sector

formed by voltage vectors A

1

, B

1

, and B

2

of Fig. 2(b) (three-

level operation), Fig. 3(c) shows the selection of redundant

switching-state combinations for A

1

(Table I) during successive

sampling intervals of PWM control. Based on Table III, for the

following four redundant switching-state combinations 10

1, 000, 20 2, 10 1, 000, 101, and 101, 202 of

A

1

, the dc-neutral currents i

3

, i

2

, i

1

can be equivalently rep-

resented as i

A

, (i

A

i

C

), i

C

, i

A

, z, i

C

, i

C

, (i

A

+

i

C

), i

A

, and i

C

, z, i

A

, respectively, in terms of the machine

phase currents. As a combined effect of these four redundant

switching-state combinations, at the end of four sampling

periods, the net current ow through the individual dc neu-

tral becomes zero, and hence, i

3

, i

2

, i

1

can be equivalently

represented as z, z, z, which is the condition for dc-link

capacitor voltage balancing (14). Similarly, it is found that

only by proper selection of MNDS or ULNDS pair (or a

combination of both as appropriately in a sector) of any voltage

vector of 2LV and 3LV groups (Table II) can the net current

through all the three dc neutrals [Fig. 3(a)] be changed to

zero within two, or a maximum of four, sampling intervals.

Hence, for the two-level and three-level modes of operation

of the drive [Fig. 3(a)], the capacitor voltage balancing can be

achieved without any additional hardware, similar to the way

proposed in [20].

It is evident from Table IV that the possibility of getting

MNDS and, especially, the ULNDS pairs, for each voltage

vector, reduces inherently as one moves from the center (ZV

group, Table II) to successive outer triangular sectors (up to the

5LV group, Table II) of Fig. 2(b). It is found that, for most of the

voltage vectors of 4LV and 5LV groups, the sequential switch-

ing of redundant switching-state combinations of any voltage

vector alone does not provide zero net currents through each

of the three dc neutrals [Fig. 3(a)]. Fig. 3(d) shows a selected

sequence of switching-state combinations for two consecutive

sampling intervals, when the reference voltage vector is consid-

ered in a sector formed by B

1

, B

2

, and C

2

of Fig. 2(b) (four-

level operation). In Fig. 3(d), SEQ is a proposed digital signal,

which is synchronized with the PWM sampling interval T

S

, and

has a period equal to 2T

S

and a duty ratio equal to 50% [20].

In Fig. 3(d), P_S means positive sequence duration (SEQ is

high), whereas N_S means negative sequence duration (SEQ is

low) [20]. Based on the equivalent representations of switching-

state combinations shown in Fig. 3(d), it can be found that the

net values of dc-neutral currents after the 2T

S

duration result

into an equivalent representation x, z, x, where x = (i

A

2i

B

i

C

) can be a nonzero value. This makes the problem of

dc-link capacitor voltage unbalance (with CMV elimination)

unsolvable for four-level and ve-level modes of operation of

the IM drive shown in Fig. 3(a). Similar inherent limitations at

the higher modulation range have been pointed out in the litera-

ture [12][14], [17] for achieving the dc-link capacitor voltage

balancing alone in conventional NPCmultilevel inverters (using

a single dc power supply). The addition of extra hardware in

the form of buckboost converter [13], [14], [19] or controlled

front-end converter [15] is suggested to solve the problem of

capacitor voltage balancing alone in NPC ve-level inverters.

VI. PROPOSED FIVE-LEVEL INVERTER SCHEME WITH

TWO DC POWER SUPPLIES

As shown in Fig. 1, it is proposed to introduce a dc power

supply of V

dc

/4 for supplying the inner two capacitors (C3 and

C2), in association with the dc power supply of V

dc

/2. Now,

for the sequence of Fig. 3(d), with the equivalent representation

x, z, x for i

3

, i

2

, i

1

, the voltage difference between C3

and C2 [from (14)] becomes zero within a 2T

S

period (16),

and consequently, C3 and C2 share the equal voltage (17).

From (14) and (17), the sum of the two voltage differences

v

43

and v

21

can be given as in (18). However, the equal

and opposite values of dc-neutral currents i

3

and i

1

(x and

x, respectively) make the sum of v

43

and v

21

equal

to zero, as shown in (19). Hence, from (14), (17), and (19),

it is clear that all the four capacitors carry the same amount of

voltage V

dc

/8 (20). We have

v

32

=v

C3

v

C2

=

1

C

_

i

2

dt = 0 (16)

v

C3

=v

C2

= V

dc

/8 (17)

v

43

+ v

21

=v

C4

v

C1

=

1

C

_

(i

3

+ i

1

)dt (18)

v

43

+ v

21

=v

C4

v

C1

=

1

C

_

(x x)dt = 0 (19)

v

C4

=v

C3

= v

C2

= v

C1

= V

dc

/8. (20)

Hence, with the proposed power schematic of Fig. 1, the con-

dition x, z, x also provides balancing of capacitor voltages,

where x can be zero or any nonzero value.

A. Open-Loop Control Scheme for DC-Link Capacitor

Voltage Balancing

An open-loop control scheme (based on only the switching-

state redundancy) is proposed for the power circuit of Fig. 1

2606 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 5, OCTOBER 2007

TABLE V

CHOSEN SWITCHING-STATE COMBINATIONS FOR VOLTAGE VECTORS IN THE 30

SEGMENT D

1

O

3

OF FIG. 2(b) FOR OPEN-LOOP CONTROL

to maintain the dc-link capacitor voltage balancing. Table V

shows the chosen switching-state combinations for two consec-

utive sampling intervals. These switching-state combinations

are selected in such a way that the average voltage unbalance

caused in one sampling interval (P_S duration) is nullied in

the next sampling interval (N_S duration). It is evident from

the last column of Table V that, in a maximum of two sampling

intervals, the dc-neutral currents attain the balancing condition

x, z, x, where x is zero or any nonzero value. Proper

switching-state combinations (for P_S and N_S durations) for

all other voltage vectors of Fig. 2(b) are also found in a similar

way. Hence, capacitor voltage balancing can be achieved by

the proposed open-loop control scheme for the full modula-

tion range. As only the availability of redundant switching-

state combinations for inverter voltage vectors is exploited, the

output fundamental voltage of the inverter is not disturbed, and

the scheme does not need any extra power circuit hardware

(buckboost converter or controlled front-end converter). The

switching-state combination selection for all the voltage vectors

of the proposed open-loop control scheme (Table V) is done in

such a way that at any given instant, all the six pole voltages

of Fig. 1 remain identical (with proper phase shift) throughout

the operating range of the drive. At the same time, care is also

taken in selection that during two-level and three-level modes

of operation, the middle two capacitors C3 and C2 (supplied by

V

dc

/2, Fig. 1) are only supplying the currents to the machine.

Hence, in two-level and three-level modes of operation of the

proposed IM drive, the upper and lower capacitors of the dc

link (i.e., C4 and C1, Fig. 1) are not supplying currents to the

machine.

VII. EXPERIMENTAL RESULTS AND DISCUSSION

The proposed ve-level inverter scheme (Fig. 1) is tested

on a laboratory prototype of a 1.5-kW open-end-winding

IM drive with V/f control. A digital signal processor TI

TMX320F240PQ and a complex programmable logic device

XILINX XC95108-20PC84C are used for implementing the

proposed open-loop control scheme. A total dc-link voltage

(V

dc

/2) of around 120 V is used for the inverter. The carrier

frequency used for PWM generation is limited to 1.25 kHz.

The pole voltage and phase voltage waveforms and their nor-

Fig. 4. (a) Five-level operation: pole voltage (v

AO

: upper trace, v

A

O

: lower

trace) and machine phase voltage (v

AA

: middle trace) [Y -axis : 1 div. =

100 V, X-axis : 1 div. = 5 ms]. (b) Normalized harmonic spectrum of pole

and phase voltage of Fig. 4(a) [X-axis: order of harmonic, Y -axis: normalized

amplitude].

malized harmonic spectrums [fast Fourier transforms (FFTs)]

for inverter operation in linear as well as overmodulation range

are presented in Fig. 4(a)(d). It can be observed from Fig. 4(a)

(ve-level operation) that the pole voltages v

AO

and v

A

O

are

symmetric and are out of phase with each other, as expected.

The contents of any even harmonics in the pole voltages

cancel each other in the phase voltage [Fig. 4(b)], and the

TEKWANI et al.: INDUCTION MOTOR DRIVE WITH VOLTAGE ELIMINATION AND VOLTAGE BALANCINGPART I 2607

Fig. 4. (Continued.) (c) 24 step mode of operation: pole voltage (v

AO

: upper

trace, v

A

O

: lower trace) and machine phase voltage (v

AA

: middle trace)

[Y -axis : 1 div. = 100 V, X-axis : 1 div. = 5 ms]. (d) Normalized harmonic

spectrum of pole and phase voltage of Fig. 4(c) [X-axis: order of harmonic,

Y -axis: normalized amplitude].

fundamental component of the pole voltages add up in the phase

voltage. Fig. 4(c) shows the waveforms of pole voltages and

phase voltage for the operation of the drive in overmodulation

(24-step mode). The 24-step operation is characterized by the

23rd and 25th harmonic frequency components in the pole as

well as in the phase voltage FFTs [Fig. 4(d)]. The FFTs of

pole voltage and phase voltage [Fig. 4(b) and (d)] show the

absence of triplen harmonic components, conrming the elim-

ination of CMV. The traces of machine phase voltage (v

AA

),

machine phase current (i

A

), and the dc-link capacitor voltages

are presented in Fig. 5 for transient operating condition of the

drive when a ve-level speed command is given. In Fig. 5(a),

waveforms of the machine phase voltage (upper trace) and the

machine phase current (lower trace) show smooth transitions of

operating levels of the inverter during starting. Fig. 5(b) shows

that C2 and C3 share the equal voltage, whereas equal sharing

of voltage between C1 and C4 is evident from Fig. 5(c). It is

also clear from Fig. 5(b) and (c) that all the four capacitors

of the dc link share the equal voltage. It is quite evident from

experimental results of Figs. 4(a) and 5(c) that the proposed

open-loop controller is able to maintain the dc-link capaci-

tor voltage balancing in association with CMV elimination

throughout the operating range of the drive.

Fig. 5. Starting of drive with speed command of a ve-level operation.

(a) Machine phase voltage (v

AA

) and machine phase current (i

A

) [Y -axis;

upper trace: 1 div. = 50 V, lower trace: 1 div. = 2 A]. (b) Capacitor voltages

v

C2

, and v

C3

[Y -axis: 1 div. = 20 V]. (c) Capacitor voltages v

C1

, and v

C4

[Y -axis: 1 div. = 20 V], X-axis: [1 div. = 2 s].

Fig. 6. Limitation of the open-loop control scheme to take the corrective

action to bring back the balanced state of capacitor voltages during the ve-

level mode of operation (simulation results).

VIII. LIMITATION OF OPEN-LOOP CONTROL SCHEME

The proposed open-loop controller is unable to take any

corrective action toward reducing the unbalance in the capacitor

voltages that may arise in practice due to asynchronous PWM

with low switching frequency, unbalanced load currents, mis-

match in power device characteristics, etc. Simulation results

presented in Fig. 6(a) and (b) show that the gradual divergence

in capacitor voltages (due to disabling the open-loop controller)

cannot be brought back to the balanced condition by again

enabling the open-loop control action (the presence of CMV in

Fig. 6(c) is due to the unbalance in capacitor voltages). This

situation demands for a closed-loop controller that not only

2608 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 5, OCTOBER 2007

stops the further unbalancing of capacitor voltages, but also

takes the corrective actions to bring back the capacitor voltages

into the balanced state as well. Such a closed-loop controller is

described in detail in Part II of this paper.

IX. CONCLUSION

A dual ve-level inverter-fed open-end-winding IM drive

for the dual task of CMV elimination and dc-link capacitor

voltage balancing in the entire modulation range is proposed in

this paper. An open-loop control scheme, which uses only the

availability of redundant switching states for inverter voltage

vectors, is presented. The output fundamental voltage of the

inverter is not disturbed, and the scheme does not need any

extra power circuit hardware such as buckboost converter or

controlled front-end converter. A closed-loop control scheme

to take care of the limitation of the proposed open-loop scheme

is presented in Part II of this paper.

REFERENCES

[1] I.-D. Kim, E.-C. Nho, H.-G. Kim, and J. S. Ko, A generalized

undeland snubber for ying capacitor multilevel inverter and converter,

IEEE Trans. Ind. Electron., vol. 51, no. 6, pp. 12901296, Dec. 2004.

[2] J. Rodriguez, J. Pontt, S. Kouro, and P. Correa, Direct torque control

with imposed switching frequency in an 11-level cascaded inverter, IEEE

Trans. Ind. Electron., vol. 51, no. 4, pp. 827833, Aug. 2004.

[3] M. Glinka and R. Marquardt, A new AC/AC multi-level converter

family, IEEE Trans. Ind. Electron., vol. 52, no. 3, pp. 662669, Jun. 2005.

[4] D.-W. Kang, B.-K. Lee, J.-H. Jeon, T.-J. Kim, and D.-S. Hyun, A sym-

metric carrier technique of CRPWMfor voltage-balance method of ying-

capacitor multilevel inverter, IEEE Trans. Ind. Electron., vol. 52, no. 3,

pp. 879888, Jun. 2005.

[5] G. Ceglia, V. Guzman, C. Sanchez, F. Ibanez, J. Walter, and

M. I. Gimenez, A new simplied multilevel inverter topology for DC-AC

conversion, IEEE Trans. Ind. Electron., vol. 21, no. 5, pp. 13111319,

Sep. 2006.

[6] A. Chen and X. He, Research on hybrid-clamped multilevel-inverter

topologies, IEEE Trans. Ind. Electron., vol. 53, no. 6, pp. 18981907,

Dec. 2006.

[7] V. T. Somasekhar, K. Gopakumar, M. R. Baiju, K. K. Mohapatra, and

L. Umanand, A multilevel inverter system for an induction motor with

open-end windings, IEEE Trans. Ind. Electron., vol. 52, no. 3, pp. 824

836, Jun. 2005.

[8] J. Rodriguez, J. Pontt, P. Correa, P. Cortes, and C. Silva, A new modu-

lation method to reduce common-mode voltages in multilevel inverters,

IEEE Trans. Ind. Electron., vol. 51, no. 4, pp. 834839, Aug. 2004.

[9] P. C. Loh, D. G. Holmes, Y. Fukuta, and T. A. Lipo, Reduced common-

mode modulation strategies for cascaded multilevel inverters, IEEE

Trans. Ind. Appl., vol. 39, no. 5, pp. 13861395, Sep./Oct. 2003.

[10] R. S. Kanchan, P. N. Tekwani, M. R. Baiju, K. Gopakumar, and A. Pittet,

Three-level inverter conguration with common-mode elimination for

induction motor drive, Proc. Inst. Electr. Eng.Electr. Power Appl.,

vol. 152, no. 2, pp. 261270, Mar. 2005.

[11] P. N. Tekwani, R. S. Kanchan, K. Gopakumar, and A. Vezzini, A ve-

level inverter topology with common-mode voltage elimination for induc-

tion motor drives, in Proc. 11th EPE, Dresden, Germany, Sep. 1114,

2005, pp. 110. No. 003.

[12] C. Newton and M. Sumner, Neutral point control for multi-level invert-

ers: Theory, design and operational limitations, in Proc. IEEE IAS Conf.,

New Orleans, LA, Oct. 59, 1997, pp. 13361343.

[13] C. Newton and M. Summer, Novel technique for maintaining balanced

internal DC link voltages in diode clamped ve-level inverters, Proc.

Inst. Electr. Eng.Electr. Power Appl., vol. 146, no. 3, pp. 341349, May

1999.

[14] N. S. Choi, J. G. Cho, and G. H. Cho, A general circuit topology of

multilevel inverter, in Proc. 22nd Annu. IEEE PESC, Jun. 2427, 1991,

pp. 96103.

[15] T. Ishida, K. Matsuse, T. Miyamota, K. Sasagawa, and L. Huang, Fun-

damental characteristics of ve-level double converter with adjustable DC

voltages for induction motor drives, IEEE Trans. Ind. Electron., vol. 49,

no. 4, pp. 775782, Aug. 2002.

[16] F. Z. Peng, A generalized multilevel inverter topology with self volt-

age balancing, IEEE Trans. Ind. Appl., vol. 37, no. 2, pp. 611618,

Mar./Apr. 2001.

[17] J. Pou, R. Pindado, and D. Boroyevich, Voltage-balance limits in four-

level diode-clamped converters with passive front ends, IEEE Trans. Ind.

Electron., vol. 52, no. 1, pp. 190196, Feb. 2005.

[18] M. Botao, L. Conhwei, Z. Yang, and L. Fahai, New SVPWM control

scheme for three-phase diode clamping multilevel inverter with balanced

DC voltages, in Proc. 28th Annu. IEEE IECON, Nov. 58, 2002, vol. 2,

pp. 903907.

[19] A. V. Jouanne, S. Dai, and H. Zhang, A multilevel inverter approach

providing DC-link balancing, ride-through enhancement, and common-

mode voltage elimination, IEEE Trans. Ind. Electron., vol. 49, no. 4,

pp. 739745, Aug. 2002.

[20] R. S. Kanchan, P. N. Tekwani, and K. Gopakumar, Three-level inverter

scheme with common-mode voltage elimination and DC-link capacitor

voltage balancing for an open end winding induction motor drive, in

Proc. IEEE IEMDC, San Antonio, TX, Oct. 1518, 2005, pp. 14451452.

[21] G. Sinha and T. A. Lipo, A four-level inverter based drive with a passive

front end, IEEE Trans. Power Electron., vol. 15, no. 2, pp. 285294,

Mar. 2000.

P. N. Tekwani (S04) received the B.E. degree (Uni.

First) in power electronics from Lukhdhirji Engi-

neering College, Morbi, India, in 1995, and the M.E.

degree in electrical engineering (First Rank) from the

Maharaja Syajirao University of Baroda, Vadodara,

India, in 2000. He is currently working toward the

Ph.D. degree at the Centre for Electronics Design and

Technology, Indian Institute of Science, Bangalore,

India.

He was with Amtech Electronics Pvt. Ltd.,

Gandhinagar, India, from 1995 to 1996. From 1996

to 2001, he was with the Electrical Research and Development Association,

Vadodara. Since 2001, he has been a member of the Faculty at the Nirma

Institute of Technology, Ahmedabad, India.

R. S. Kanchan (S04) received the B.E. degree

in electrical engineering from Walchand College of

Engineering, Sangali, India, in 1998, the M.Tech.

degree in electrical engineering from the Indian

Institute of Technology, Bombay, India, in 2000, and

the Ph.D. degree from the Indian Institute of Science,

Bangalore, India, in 2005.

He was with Tata Steel Company from 2000

to 2002. Currently, he is a Research Associate at

the Centre for Electronics Design and Technology,

Indian Institute of Science.

K. Gopakumar (M94SM96) received the B.E.,

M.Sc.(Eng.), and Ph.D. degrees from the Indian

Institute of Science, Bangalore, India, in 1980, 1984,

and 1994, respectively.

He was with the Indian Space Research Organiza-

tion from 1984 to 1987. He is currently an Associate

Professor at the Centre for Electronics Design and

Technology, Indian Institute of Science. His elds of

interest include power converters, PWM techniques,

and ac drives.

Dr. Gopakumar is an Associate Editor of the IEEE

TRANSACTIONS ON INDUSTRIAL ELECTRONICS.

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- CAT Ground Engaging ToolsDocument35 pagesCAT Ground Engaging ToolsJimmy Nuñez VarasNo ratings yet

- A Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InverterDocument10 pagesA Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InvertererdemsecenNo ratings yet

- Power Electronics NotesDocument91 pagesPower Electronics NotesTaimur Musharraf89% (46)

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- A Novel Scheme To Eliminate Common Mode Voltage in Multilevel InvertersDocument4 pagesA Novel Scheme To Eliminate Common Mode Voltage in Multilevel InvertersJavier MaldonadoNo ratings yet

- KINETIC THEORY OF GASES TUTORIALDocument6 pagesKINETIC THEORY OF GASES TUTORIALMat SyafiqNo ratings yet

- Basic PLCDocument77 pagesBasic PLCrpshvju100% (1)

- Artifact and Thingamy by David MitchellDocument8 pagesArtifact and Thingamy by David MitchellPedro PriorNo ratings yet

- Rotary Twin Scew Brochure UK HRDocument20 pagesRotary Twin Scew Brochure UK HRNguyễn Hữu DũngNo ratings yet

- A Is (Facts) (SVG) ,: AbstractDocument9 pagesA Is (Facts) (SVG) ,: AbstractSherif M. DabourNo ratings yet

- A SVM Based Four-Level Open-End Winding-Induction Motor Drive With Voltage Balancing of DC-link Capacitors Using SVM Based HCC Front-End ConverterDocument5 pagesA SVM Based Four-Level Open-End Winding-Induction Motor Drive With Voltage Balancing of DC-link Capacitors Using SVM Based HCC Front-End ConverterGanesh ChallaNo ratings yet

- Zero-Steady-State-Error Input-Current Controller For Regenerative Multilevel Converters Based On Single-Phase CellsDocument8 pagesZero-Steady-State-Error Input-Current Controller For Regenerative Multilevel Converters Based On Single-Phase CellssghfqweNo ratings yet

- An SVM Algorithm To Balance The Capacitor Voltages of The Three-Level NPC APFDocument9 pagesAn SVM Algorithm To Balance The Capacitor Voltages of The Three-Level NPC APFTran Quoc HoanNo ratings yet

- Space-Vector Modulated Multilevel Matrix Converter: Meng Yeong Lee, Patrick Wheeler, and Christian KlumpnerDocument10 pagesSpace-Vector Modulated Multilevel Matrix Converter: Meng Yeong Lee, Patrick Wheeler, and Christian KlumpnerakankshiNo ratings yet

- Multi-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LDocument6 pagesMulti-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LveguruprasadNo ratings yet

- Simulation and Controller Design of An Interline Power Flow Controller in EMTP RVDocument8 pagesSimulation and Controller Design of An Interline Power Flow Controller in EMTP RVSuresh Sampath SNo ratings yet

- Control VectorialDocument6 pagesControl VectorialdanipedoNo ratings yet

- Design of Single Phase Cyclo-Converter Using Cascaded Multilevel InverterDocument5 pagesDesign of Single Phase Cyclo-Converter Using Cascaded Multilevel InverterInternational Organization of Scientific Research (IOSR)No ratings yet

- Modelling and Control of a Flying-Capacitor InverterDocument9 pagesModelling and Control of a Flying-Capacitor InverterMariem KammounNo ratings yet

- Single-Phase Five-Level Inverter With Less Number of Power Elements For Grid ConnectionDocument7 pagesSingle-Phase Five-Level Inverter With Less Number of Power Elements For Grid Connectionvinay kumarNo ratings yet

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDocument5 pagesImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNo ratings yet

- An Optimized Control Method Based On Dual Three-Level Inverters For Open-End Winding Induction Motor DrivesDocument9 pagesAn Optimized Control Method Based On Dual Three-Level Inverters For Open-End Winding Induction Motor DrivesCharles KellyNo ratings yet

- International Journal of Computational Engineering Research (IJCER)Document7 pagesInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)No ratings yet

- Multipulse Converters and Controls For HVDC and FACTS SystemsDocument9 pagesMultipulse Converters and Controls For HVDC and FACTS SystemssanjusNo ratings yet

- Modelado DC DCDocument8 pagesModelado DC DCAndrés Vanegas GuillénNo ratings yet

- A Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsDocument9 pagesA Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsInternational Journal of Engineering Inventions (IJEI)No ratings yet

- A Generalized Multilevel Inverter TopologyDocument8 pagesA Generalized Multilevel Inverter TopologyMinh NhậtNo ratings yet

- Performance Optimization of A Photovoltaic Water-Pumping SystemDocument8 pagesPerformance Optimization of A Photovoltaic Water-Pumping SystemKamal HimourNo ratings yet

- A Nine-Level Inverter System For An Open-End Winding Induction Motor DriveDocument6 pagesA Nine-Level Inverter System For An Open-End Winding Induction Motor DriveGanesh ChallaNo ratings yet

- A Space Vector-Based Rectifier Regulator For AC DC AC ConvertersDocument7 pagesA Space Vector-Based Rectifier Regulator For AC DC AC ConvertersSofia FrlNo ratings yet

- An Analysis and Survey of Multilevel Inverters Topologies, Controls, and ApplicationsDocument10 pagesAn Analysis and Survey of Multilevel Inverters Topologies, Controls, and ApplicationsDr-Ismayil CNo ratings yet

- A Novel Dynamic Voltage Restorer Based On Matrix ConvertersDocument7 pagesA Novel Dynamic Voltage Restorer Based On Matrix ConvertersAbdulwahid Al-safanyNo ratings yet

- Novel Seven - Level Flying Capacitor Based Active Neutral Point Clamped Converter Using Photovoltaic Energy GenerationDocument4 pagesNovel Seven - Level Flying Capacitor Based Active Neutral Point Clamped Converter Using Photovoltaic Energy GenerationInnovative Research PublicationsNo ratings yet

- A New Five-Level Inverter System For An Induction Motor With Open-End WindingsDocument6 pagesA New Five-Level Inverter System For An Induction Motor With Open-End WindingsGanesh ChallaNo ratings yet

- DC To Ac Conversion InversionDocument15 pagesDC To Ac Conversion InversionfxsolomonNo ratings yet

- Design and Implementation Three-Arms Rectifier Inverter of A Single PhaseDocument6 pagesDesign and Implementation Three-Arms Rectifier Inverter of A Single Phasecelo81No ratings yet

- Auto ZigzagDocument9 pagesAuto Zigzaggeetha babuNo ratings yet

- Common Mode VoltageDocument10 pagesCommon Mode VoltageManigandan212No ratings yet

- A Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM StrategyDocument2 pagesA Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM Strategyskumar_61719No ratings yet

- Three-Level Inverter Speed Control of Induction MotorDocument12 pagesThree-Level Inverter Speed Control of Induction MotorMallikarjunBhiradeNo ratings yet

- Inverter and Its TopologiesDocument14 pagesInverter and Its TopologiesAvnesh SuryavanshiNo ratings yet

- A Novel Current Controlled Space Vector Modulation Based Control Scheme For Reducing Torque Ripple in Brushless DC DrivesDocument7 pagesA Novel Current Controlled Space Vector Modulation Based Control Scheme For Reducing Torque Ripple in Brushless DC DrivesKoukou AmkoukouNo ratings yet

- Q02201300137Document8 pagesQ02201300137Vikas PatelNo ratings yet

- Switching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor DriveDocument6 pagesSwitching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor Drivevinay kumarNo ratings yet

- Two-Stage Inverter Reduces Switching LossesDocument6 pagesTwo-Stage Inverter Reduces Switching LosseshismarcheNo ratings yet

- 06125602Document6 pages06125602Ahmad Sadam SyaeroziNo ratings yet

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDocument12 pagesLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadNo ratings yet

- Space-Vector Modulation in A Two-Phase Induction Motor Drive For Constant-Power OperationDocument8 pagesSpace-Vector Modulation in A Two-Phase Induction Motor Drive For Constant-Power OperationinfodotzNo ratings yet

- Feed-Forward Space Vector Modulation For Single-Phase Multilevel Cascaded Converters With Any DC Voltage RatioDocument11 pagesFeed-Forward Space Vector Modulation For Single-Phase Multilevel Cascaded Converters With Any DC Voltage RatiosatydeshNo ratings yet

- ANN Switched Z-Source Inverter Based PV Generation System: AbstractDocument9 pagesANN Switched Z-Source Inverter Based PV Generation System: AbstractsathishNo ratings yet

- Total Harmonics Distortion Investigation in Multilevel InvertersDocument8 pagesTotal Harmonics Distortion Investigation in Multilevel InvertersAJER JOURNALNo ratings yet

- Charge Pump Design HVDocument16 pagesCharge Pump Design HVMohammed BelkheiriNo ratings yet

- Harmonic Reduction in Parallel Inverters Using THIPWMDocument6 pagesHarmonic Reduction in Parallel Inverters Using THIPWMAhmed JanadNo ratings yet

- Modeling and Control of an Advanced Static Var Compensator Using Three-Level InverterDocument6 pagesModeling and Control of an Advanced Static Var Compensator Using Three-Level InverterRaviraj KumbharNo ratings yet

- 4 Gaiceanu2014Document6 pages4 Gaiceanu2014HernandaBudiSantosoNo ratings yet

- Unit-2-Converter and HVDC System ControlDocument13 pagesUnit-2-Converter and HVDC System Controlravikumar_ranganNo ratings yet

- International Journal of Engineering Research and DevelopmentDocument7 pagesInternational Journal of Engineering Research and DevelopmentIJERDNo ratings yet

- Statespace Model FWD ConverterDocument4 pagesStatespace Model FWD ConverterrogerozNo ratings yet

- DC Motors Speed Control - ModDocument9 pagesDC Motors Speed Control - ModAnuja VargheseNo ratings yet

- Modelling and Simulation of High Step Up DC To AC Converter For Microsource ApplicationDocument5 pagesModelling and Simulation of High Step Up DC To AC Converter For Microsource ApplicationtheijesNo ratings yet

- Modified Z-Source Single-Phase Inverter for PM Motor DrivesDocument6 pagesModified Z-Source Single-Phase Inverter for PM Motor DrivesPRACHI KATARENo ratings yet

- Feed Forward Controller For Compensation of DC-Link Capacitor Unbalance Voltages and Ripple Reduction Based BLDCM Drive SystemDocument6 pagesFeed Forward Controller For Compensation of DC-Link Capacitor Unbalance Voltages and Ripple Reduction Based BLDCM Drive SystemSiddharth Jayashekar KNo ratings yet

- Paper 4 - p302Document6 pagesPaper 4 - p302Sherif M. DabourNo ratings yet

- Common Voltage Eliminating of SVM Diode Clamping Three-Level Inverter Connected To GridDocument4 pagesCommon Voltage Eliminating of SVM Diode Clamping Three-Level Inverter Connected To GridveguruprasadNo ratings yet

- Pressure Switch PresentationDocument21 pagesPressure Switch PresentationDeepu ChinnaNo ratings yet

- Cascaded H-Bridge Multilevel Inverter Using Inverted Sine Wave PWM Technique PDFDocument6 pagesCascaded H-Bridge Multilevel Inverter Using Inverted Sine Wave PWM Technique PDFDeepu Chinna100% (1)

- 8.3.14 Addendum JWM (Elec) EnghindiDocument2 pages8.3.14 Addendum JWM (Elec) EnghindiAmit PaulNo ratings yet

- D EEPU05491634Document4 pagesD EEPU05491634Deepu ChinnaNo ratings yet

- FactspresentationDocument31 pagesFactspresentationDeepu ChinnaNo ratings yet

- Pesc 2008 HaiwenDocument5 pagesPesc 2008 Haiwenthienvuong90No ratings yet

- Solar&PVDocument12 pagesSolar&PVPatrick SmithNo ratings yet

- Improved Active Power Filter Performance For Renewable Power Generation SystemsDocument8 pagesImproved Active Power Filter Performance For Renewable Power Generation SystemsKuncham SateeshNo ratings yet

- 46 Multileveltopology PDFDocument5 pages46 Multileveltopology PDFDeepu ChinnaNo ratings yet

- ESWU05545880Document3 pagesESWU05545880Deepu ChinnaNo ratings yet

- Inverter 04487800Document8 pagesInverter 04487800Deepu ChinnaNo ratings yet

- INV04503992Document6 pagesINV04503992Deepu ChinnaNo ratings yet

- 01431858HGHDocument6 pages01431858HGHDeepu ChinnaNo ratings yet

- 01433011DFSSDocument7 pages01433011DFSSDeepu ChinnaNo ratings yet

- Multilevel Inverters A Survey of Topologies Control and ApplicationsDocument15 pagesMultilevel Inverters A Survey of Topologies Control and Applicationstochi8267No ratings yet

- 04285963Document9 pages04285963Deepu ChinnaNo ratings yet

- A Generalized Multilevel Inverter TopologyDocument8 pagesA Generalized Multilevel Inverter TopologyHamid KhaleghiNo ratings yet

- 00585865GGGDocument8 pages00585865GGGDeepu ChinnaNo ratings yet

- Basic Lawsx 4Document9 pagesBasic Lawsx 4Deepu ChinnaNo ratings yet

- Energy Storage X 4Document12 pagesEnergy Storage X 4Deepu ChinnaNo ratings yet

- Analysis Methods X 4Document14 pagesAnalysis Methods X 4Deepu ChinnaNo ratings yet

- EE113 Course Notes Electronic CircuitsDocument268 pagesEE113 Course Notes Electronic Circuitspowerdeadlifter100% (1)

- Basic Concepts X 4Document6 pagesBasic Concepts X 4Deepu ChinnaNo ratings yet

- Interview TipsDocument15 pagesInterview Tipssaurabhrawal100No ratings yet

- Circuit Theorems X 4Document13 pagesCircuit Theorems X 4Deepu ChinnaNo ratings yet

- High Sensitive LPG Sensor With Gas Leak AlertDocument23 pagesHigh Sensitive LPG Sensor With Gas Leak AlertDeepu Chinna100% (2)

- Single Phase Fully Controlled ConverterDocument10 pagesSingle Phase Fully Controlled ConverterDeepu Chinna75% (4)

- Draft Initial Study - San Joaquin Apartments and Precinct Improvements ProjectDocument190 pagesDraft Initial Study - San Joaquin Apartments and Precinct Improvements Projectapi-249457935No ratings yet

- Sap ThufingteDocument10 pagesSap ThufingtehangsinfNo ratings yet

- Fake News Poems by Martin Ott Book PreviewDocument21 pagesFake News Poems by Martin Ott Book PreviewBlazeVOX [books]No ratings yet

- SRS Design Guidelines PDFDocument46 pagesSRS Design Guidelines PDFLia FernandaNo ratings yet

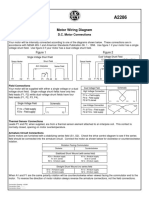

- Motor Wiring Diagram: D.C. Motor ConnectionsDocument1 pageMotor Wiring Diagram: D.C. Motor Connectionsczds6594No ratings yet

- Tutorial On The ITU GDocument7 pagesTutorial On The ITU GCh RambabuNo ratings yet

- Lightwave Maya 3D TutorialsDocument8 pagesLightwave Maya 3D TutorialsrandfranNo ratings yet

- Final Decision W - Cover Letter, 7-14-22Document19 pagesFinal Decision W - Cover Letter, 7-14-22Helen BennettNo ratings yet

- Pitch Manual SpecializedDocument20 pagesPitch Manual SpecializedRoberto Gomez100% (1)

- Idioms & Phrases Till CGL T1 2016Document25 pagesIdioms & Phrases Till CGL T1 2016mannar.mani.2000100% (1)

- Stability Calculation of Embedded Bolts For Drop Arm Arrangement For ACC Location Inside TunnelDocument7 pagesStability Calculation of Embedded Bolts For Drop Arm Arrangement For ACC Location Inside TunnelSamwailNo ratings yet

- Monodisperse Droplet Generators As Potential Atomizers For Spray Drying Technology PDFDocument11 pagesMonodisperse Droplet Generators As Potential Atomizers For Spray Drying Technology PDFfishvalNo ratings yet

- 3D Area Clearance Strategies for Roughing ComponentsDocument6 pages3D Area Clearance Strategies for Roughing ComponentsMohamedHassanNo ratings yet

- India - Wikipedia, The Free EncyclopediaDocument40 pagesIndia - Wikipedia, The Free EncyclopediaPrashanth KrishNo ratings yet

- Tetracyclines: Dr. Md. Rageeb Md. Usman Associate Professor Department of PharmacognosyDocument21 pagesTetracyclines: Dr. Md. Rageeb Md. Usman Associate Professor Department of PharmacognosyAnonymous TCbZigVqNo ratings yet

- Sri Radhakrishna SwamijiDocument43 pagesSri Radhakrishna SwamijiNarayana IyengarNo ratings yet

- WOOD Investor Presentation 3Q21Document65 pagesWOOD Investor Presentation 3Q21Koko HadiwanaNo ratings yet

- JK Paper Q4FY11 Earnings Call TranscriptDocument10 pagesJK Paper Q4FY11 Earnings Call TranscriptkallllllooooNo ratings yet

- Detection and Attribution Methodologies Overview: Appendix CDocument9 pagesDetection and Attribution Methodologies Overview: Appendix CDinesh GaikwadNo ratings yet

- Introduction To Finite Element Methods (2001) (En) (489s)Document489 pagesIntroduction To Finite Element Methods (2001) (En) (489s)green77parkNo ratings yet

- Handout Tematik MukhidDocument72 pagesHandout Tematik MukhidJaya ExpressNo ratings yet

- Cs8791 Cloud Computing Unit2 NotesDocument37 pagesCs8791 Cloud Computing Unit2 NotesTeju MelapattuNo ratings yet

- Acuity Assessment in Obstetrical TriageDocument9 pagesAcuity Assessment in Obstetrical TriageFikriNo ratings yet

- Accomplishment Report Yes-O NDCMC 2013Document9 pagesAccomplishment Report Yes-O NDCMC 2013Jerro Dumaya CatipayNo ratings yet

- Uhf Leaky Feeder Rev CDocument4 pagesUhf Leaky Feeder Rev CLuis Isaac PadillaNo ratings yet