Professional Documents

Culture Documents

Mos Chara

Uploaded by

Vamshidhar Reddy YallaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Mos Chara

Uploaded by

Vamshidhar Reddy YallaCopyright:

Available Formats

6.

012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-1

Lecture 9 - MOSFET (I) MOSFET I-V Characteristics March 6, 2003 Contents: 1. MOSFET: cross-section, layout, symbols 2. Qualitative operation 3. I-V characteristics

Reading assignment: Howe and Sodini, Ch. 4, 4.1-4.3 Announcements: Quiz #1, March 12, 7:30-9:30 PM, Walker Memorial; covers Lectures #1-9; open book; must have calculator.

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-2

Key questions How can carrier inversion be exploited to make a transistor? How does a MOSFET work? How does one construct a simple rst-order model for the current-voltage characteristics of a MOSFET?

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-3

1. MOSFET: layout, cross-section, symbols

body source gate n+ p+ n+ p n+ polysilicon gate drain

inversion layer channel

gate oxide

p+

n+

n+

n+

n+

Key elements: inversion layer under gate (depending on gate voltage) heavily-doped regions reach underneath gate inversion layer electrically connects source and drain 4-terminal device: body voltage important

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-4

2 Circuit symbols Two complementary devices: n-channel device (n-MOSFET) on p-Si substrate (uses electron inversion layer) p-channel device (p-MOSFET) on n-Si substrate (uses hole inversion layer)

IDn

D + VDS > 0 G

IDn

D + S + _ B G IDp VSG

S _

G +

VSB

B VSD > 0 D G IDp B

B + VBS VGS _ _ S

(a) n-channel MOSFET

(b) p-channel MOSFET

Drain

n+ Bulk or Body

Source

p+ Bulk or Body

Gate

Gate Drain

n p+

Source

n+

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-5

2. Qualitative operation Water analogy of MOSFET: Source: water reservoir Drain: water reservoir Gate: gate between source and drain reservoirs

VDS VGS G ID VGS VDS

S n+

D n+

water

inversion layer depletion region p

source

gate

drain

Want to understand MOSFET operation as a function of: gate-to-source voltage (gate height over source water level) drain-to-source voltage (water level dierence between reservoirs) Initially consider source tied up to body (substrate or back).

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-6

Three regimes of operation: 2 Cut-o regime: MOSFET: VGS < VT , VGD < VT with VDS > 0. Water analogy: gate closed; no water can ow regardless of relative height of source and drain reservoirs.

VGS<VT S

VGD<VT D

n+ p depletion region

n+ no inversion layer anywhere

no water flow

ID = 0

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-7

2 Linear or Triode regime: MOSFET: VGS > VT , VGD > VT , with VDS > 0. Water analogy: gate open but small dierence in height between source and drain; water ows.

VGS>VT S G VGD>VT D

n+ p depletion region inversion layer everywhere

n+

Electrons drift from source to drain electrical current! VGS |Qn| ID VDS Ey ID

ID small VDS ID small VDS

VGS>VT

VDS

0 0 VDS

0 VT VGS

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-8

2 Saturation regime: MOSFET: VGS > VT , VGD < VT (VDS > 0). Water analogy: gate open; water ows from source to drain, but free-drop on drain side total ow independent of relative reservoir height!

VGS>VT S G VGD<VT D

n+ p depletion region

n+

inversion layer "pinched-off" at drain side

ID independent of VDS : ID = IDsat

VGDsat=VT ID saturation

linear

0 0 VDSsat=VGS-VT VDS

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-9

3. I-V characteristics Geometry of problem:

VDS ID G VGS>VT

S n+ VBS=0 p

D n+

inversion layer depletion region 0 B y

2 General expression of channel current Current can only ow in y -direction: Jy = Q n ( y ) v y ( y ) Total channel current: Iy = W Qn(y )vy (y ) Drain terminal current is equal to minus channel current: ID = W Qn(y )vy (y )

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-10

ID = W Qn(y )vy (y ) Rewrite in terms of voltage at channel location y , Vc(y ): If electric eld is not too big: vy (y ) nEy (y ) = n dVc(y ) dy

For Qn(y ) use charge-control relation at location y : Qn(y ) = Cox[VGS Vc(y ) VT ] for VGS Vc(y ) VT . All together: ID = W nCox(VGS Vc(y ) VT ) dVc(y ) dy

Simple linear rst-order dierential equation with one unknown, the channel voltage Vc(y ).

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-11

Solve by separating variables: ID dy = W nCox(VGS Vc VT )dVc Integrate along the channel in the linear regime: -for y = 0, Vc(0) = 0 -for y = L, Vc(L) = VDS (linear regime) Then: ID or: W VDS ID = nCox(VGS VT )VDS L 2

L 0 dy

= W nCox

VDS (VGS 0

Vc VT )dVc

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-12

For small VDS : ID Key dependencies: VDS ID (higher lateral electric eld) VGS ID (higher electron concentration) L ID (lower lateral electric eld) W ID (wider conduction channel)

ID small VDS ID small VDS

W nCox(VGS VT )VDS L

VGS>VT

VDS

0 0 VDS

0 VT VGS

This is the linear or triode regime.

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-13

In general, ID = W VDS nCox(VGS VT )VDS L 2

Equation valid if VGS Vc(y ) VT at every y . Worst point is y = L, where Vc(y ) = VDS , hence, equation valid if VGS VDS VT , or: VDS VGS VT

ID

VDS=VGS-VT

VGS

VGS=VT 0 0 VDS

term responsible for bend over of ID : VDS 2

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-14

To understand why ID bends over, must understand rst channel debiasing:

|Qn| Cox(VGS-VT)

0 0 |Ey| L

0 0 Vc VDS L y

0 0 VGS-Vc(y) VGS

local gate overdrive

VDS

VT 0 L y

Along channel from source to drain: y Vc(y ) |Qn(y )| |Ey (y )| Local channel overdrive reduced closer to drain.

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-15

Impact of VDS :

|Qn|

VDS=0

VDS 0 0 L y

|Ey|

VDS

VDS=0

0 0 Vc L y

VDS

VDS=0

0 0

As VDS , channel debiasing more prominent ID rises more slowly with VDS

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-16

1.5 46.5 NMOSFET Output characteristics (VGS = 0 3 V, VGS = 0.5 V ):

Zoom close to origin:

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-17

Transfer characteristics (VDS = 0.1 V ):

6.012 - Microelectronic Devices and Circuits - Spring 2003

Lecture 9-18

Key conclusions The MOSFET is a eld-eect transistor: the amount of charge in the inversion layer is controlled by the eld-eect action of the gate the charge in the inversion layer is mobile conduction possible between source and drain In the linear regime: VGS ID : more electrons in the channel VDS ID : stronger eld pulling electrons out of the source Channel debiasing: inversion layer thins down from source to drain current saturation as VDS approaches: VDSsat = VGS VT

You might also like

- MTech Power Electronics Syllabus NIT TiruchirappalliDocument16 pagesMTech Power Electronics Syllabus NIT TiruchirappallisurabhidivyaNo ratings yet

- Modelling of PV Electrical CharacteristicsDocument7 pagesModelling of PV Electrical CharacteristicsabagreNo ratings yet

- Buck Converter Bykiran - 2012Document99 pagesBuck Converter Bykiran - 2012Artin HykoNo ratings yet

- Sliding Mode ControlDocument8 pagesSliding Mode ControlVamshidhar Reddy YallaNo ratings yet

- Interrupts of Pic16f876Document15 pagesInterrupts of Pic16f876Vamshidhar Reddy YallaNo ratings yet

- Variable Structure Systems With Sliding ModesDocument11 pagesVariable Structure Systems With Sliding ModesNguyen Quang VinhNo ratings yet

- Design and Implementation of Digital Trigger Circuit For ConverterDocument6 pagesDesign and Implementation of Digital Trigger Circuit For ConverterBilal Ali AhmadNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5782)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- IC Technology: Dr. Sachin D. Pabale Matosri College of Engineering and Research Centre, NasikDocument154 pagesIC Technology: Dr. Sachin D. Pabale Matosri College of Engineering and Research Centre, NasikRockRahilNo ratings yet

- DS Uf3sc065007k4s-1667973Document13 pagesDS Uf3sc065007k4s-1667973Nanang BaliNo ratings yet

- Appendix - Equations v3Document4 pagesAppendix - Equations v3ALEN chiaNo ratings yet

- Scaling of MosfetDocument16 pagesScaling of MosfetVikasNo ratings yet

- Common Base Characteristics of NPN TransistorDocument18 pagesCommon Base Characteristics of NPN TransistorHenry Oppong100% (2)

- Gujarat Technological University Bachelor of Engineering Subject Code: 3110016 Basic Electronics 1 YearDocument3 pagesGujarat Technological University Bachelor of Engineering Subject Code: 3110016 Basic Electronics 1 YearGeopolitics PostNo ratings yet

- Chapter 2 Digital Logic and FamiliesDocument43 pagesChapter 2 Digital Logic and FamiliesSan Maharjan50% (2)

- Datasheet c2335fDocument3 pagesDatasheet c2335fLuisa Antonia Valladares EyzaguirreNo ratings yet

- CMOS Fabrication ProcessDocument10 pagesCMOS Fabrication ProcessJohnMatthewBancilNo ratings yet

- Frequency Response of Mosfet The Expanded Hybrid Equivalent Circuit of The Bipolar Transistor High-Frequency ResponseDocument37 pagesFrequency Response of Mosfet The Expanded Hybrid Equivalent Circuit of The Bipolar Transistor High-Frequency ResponseMuthukrishnan Vijayan VijayanNo ratings yet

- Visvesvarya National Institute of Technology Nagpur: ECE BTECH 15-19 Device Modelling Lab Assignment 4Document21 pagesVisvesvarya National Institute of Technology Nagpur: ECE BTECH 15-19 Device Modelling Lab Assignment 4Ishan DarwhekarNo ratings yet

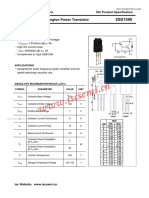

- isc Silicon NPN Darlington Power Transistor SpecificationDocument2 pagesisc Silicon NPN Darlington Power Transistor SpecificationDidier DoradoNo ratings yet

- Monitor Sony GDM-500PSDocument26 pagesMonitor Sony GDM-500PStipudelacablutvNo ratings yet

- BJT Transistor Operation and CharacteristicsDocument21 pagesBJT Transistor Operation and CharacteristicsDr-Ahmed ElkoranyNo ratings yet

- TIP142T TIP147T: Complementary Silicon Power Darlington TransistorsDocument4 pagesTIP142T TIP147T: Complementary Silicon Power Darlington TransistorsMates IoanNo ratings yet

- U 3Document13 pagesU 3Maheshwar Reddy100% (1)

- ASIC by Sebastian SmithDocument506 pagesASIC by Sebastian SmithKiberleab TadesseNo ratings yet

- Transistor TestingDocument2 pagesTransistor TestingKannan AlagumuthiahNo ratings yet

- CH 08Document29 pagesCH 08miathegirl9No ratings yet

- Advantages and Disadvantages of BJTs and MOSFETsDocument3 pagesAdvantages and Disadvantages of BJTs and MOSFETscuongspvl2713No ratings yet

- 1.CMOS VLSI DesignDocument2 pages1.CMOS VLSI DesignSYAMALANo ratings yet

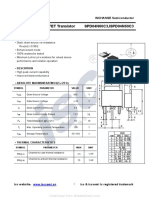

- Isc N-Channel MOSFET Transistor SPD04N60C3, ISPD04N60C3: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor SPD04N60C3, ISPD04N60C3: INCHANGE Semiconductorjavier venturaNo ratings yet

- CMOS FabricationDocument38 pagesCMOS FabricationPrajeeth Babu KodruNo ratings yet

- 03 BJT-Basics PDFDocument13 pages03 BJT-Basics PDFMd ArifNo ratings yet

- Standard Power MOSFET: IRFP 254 V 250 V I 23 A R 0.14Document2 pagesStandard Power MOSFET: IRFP 254 V 250 V I 23 A R 0.14Fran Javi Vila DiazNo ratings yet

- NIKO-SEM Power MOSFET Selection GuideDocument5 pagesNIKO-SEM Power MOSFET Selection GuideroozbehxoxNo ratings yet

- Concepts in VLSI Design: Combinational CircuitsDocument38 pagesConcepts in VLSI Design: Combinational CircuitsAbhishek BhardwajNo ratings yet

- Chapter 10 Field Effect TransistorsDocument48 pagesChapter 10 Field Effect TransistorsanjugaduNo ratings yet

- Ec8252 Edc QB OnlyDocument26 pagesEc8252 Edc QB OnlyPraveen KumarNo ratings yet

- CH 5Document119 pagesCH 5Nooruddin SheikNo ratings yet