Professional Documents

Culture Documents

CD4514BC

Uploaded by

atif.kamalCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CD4514BC

Uploaded by

atif.kamalCopyright:

Available Formats

CD4514BC CD4515BC 4-Bit Latched/4-to-16 Line Decoders

October 1987 Revised August 2000

CD4514BC CD4515BC 4-Bit Latched/4-to-16 Line Decoders

General Description

The CD4514BC and CD4515BC are 4-to-16 line decoders with latched inputs implemented with complementary MOS (CMOS) circuits constructed with N- and P-channel enhancement mode transistors. These circuits are primarily used in decoding applications where low power dissipation and/or high noise immunity is required. The CD4514BC (output active high option) presents a logical 1 at the selected output, whereas the CD4515BC presents a logical 0 at the selected output. The input latches are RS type flip-flops, which hold the last input data presented prior to the strobe transition from 1 to 0. This input data is decoded and the corresponding output is activated. An output inhibit line is also available.

Features

I Wide supply voltage range: I Low power TTL: fan out of 2 compatibility: driving 74L I Low quiescent power dissipation: 0.025 W/package @ 5.0 VDC I Single supply operation I Input impedance = 1012 typically I Plug-in replacement for MC14514, MC14515 3.0V to 15V I High noise immunity: 0.45 VDD (typ.)

Ordering Code:

Order Number CD4514BCWM CD4514BCN CD4515BCWM CD4515BCN Package Number M24B N24A M24B N24A Package Diagram 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600 Wide 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600 Wide

Devices also available in Tape and Reel. Specify by appending suffix letter X to the ordering code.

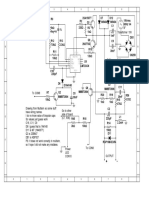

Connection Diagram

Top View

2000 Fairchild Semiconductor Corporation

DS005994

www.fairchildsemi.com

CD4514BC CD4515BC

Truth Table

Decode Truth Table (Strobe = 1) Data Inputs Inhibit 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

X = Dont Care

Selected Output A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X CD4514 = Logic 1 CD4515 = Logic 0 S0 S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15 All Outputs = 0, CD4514 All Outputs = 1, CD4515

D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 X

C 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 X

B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 X

Logic Diagram

www.fairchildsemi.com

CD4514BC CD4515BC

Absolute Maximum Ratings(Note 1)

(Note 2) DC Supply Voltage (VDD ) Input Voltage (VIN) Storage Temperature Range (TS) Power Dissipation (PD) Dual-In-Line Small Outline Lead Temperature (TL) (Soldering, 10 seconds) 260C 700 mW 500 mW

Recommended Operating Conditions (Note 2)

DC Supply Voltage (VDD) Input Voltage (VIN) Operating Temperature Range (TA) CD4514BC, CD4515BC 3V to 15V 0V to VDD

0.5V to +18V 0.5V to VDD + 0.5V 65C to +150C

40C to +85C

Note 1: Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. Except for Operating Temperature Range they are not meant to imply that the devices should be operated at these limits. The tables of Recommended Operating Conditions and Electrical Characteristics provide conditions for actual device operation. Note 2: VSS = 0V unless otherwise specified.

DC Electrical Characteristics (Note 2)

CD4514BC, CD4515BC Symbol IDD Parameter Quiescent Device Current VOL LOW Level Output Voltage Conditions VDD = 5V, VIN = VDD or V SS VDD = 10V, VIN = VDD or V SS VDD = 15V, VIN = VDD or V SS VIL = 0V, VIH = VDD, |IO| < 1 A VDD = 5V VDD = 10V VDD = 15V VOH HIGH Level Output Voltage VIL = 0V, VIH = VDD, |IO| < 1 A VDD = 5V VDD = 10V VDD = 15V VIL LOW Level Input Voltage |IO| < 1 A VDD = 5V, VO = 0.5V or 4.5V VDD = 10V, VO = 1.0V or 9.0V VDD = 15V, VO = 1.5V or 13.5V VIH HIGH Level Input Voltage |IO| < 1 A VDD = 5V, VO = 0.5V or 4.5V VDD = 10V, VO = 1.0V or 9.0V VDD = 15V, VO = 1.5V or 13.5V IOL LOW Level Output Current (Note 3) IOH HIGH Level Output Current (Note 3) IIN Input Current VDD = 5V, VO = 0.4V VDD = 10V, VO = 0.5V VDD = 15V, VO = 1.5V VDD = 5V, VO = 4.6V VDD = 10V, VO = 9.5V VDD = 15V, VO = 13.5V VDD = 15V, VIN = 0V VDD = 15V, VIN = 15V

Note 3: IOH and IOL are tested one output at a time.

40C Min Max 20 40 80 Min

+25C Typ 0.005 0.010 0.015 Max 20 40 80

+85C Min Max 150 300 600

Units A A A

0.05 0.05 0.05

0 0 0

0.05 0.05 0.05

0.05 0.05 0.05

V V V

4.95 9.95 14.95 1.5 3.0 4.0 3.5 7.0 11.0 0.52 1.3 3.6 0.52 1.3 3.6 0.3 0.3

4.95 9.95 14.95

5.0 10.0 15.0 2.25 4.50 6.75 1.5 3.0 4.0

4.95 9.95 14.95 1.5 3.0 4.0 3.5 7.0 11.0 0.36 0.90 2.4 0.36 0.90 2.4 0.3 0.3 1.0 1.0

V V V V V V V V V mA mA mA mA mA mA A A

3.5 7.0 11.0 0.44 1.1 3.0 0.44 1.1 3.0

2.75 5.50 8.25 0.88 2.25 8.8 0.88 2.25 8.8 105 105

www.fairchildsemi.com

CD4514BC CD4515BC

AC Electrical Characteristics

Symbol tTHL, tTLH Parameter Transition Times

(Note 4)

Conditions Min Typ 100 50 40 550 225 150 400 150 100 125 50 38 175 50 38 150 5 7.5 Max 200 100 80 1100 450 300 800 300 200 250 100 75 350 100 75 Units ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns pF pF

All types CL = 50 pF, TA = 25C, tr = tf = 20 ns unless otherwise specified VDD = 5V VDD = 10V VDD = 15V tPLH, tPHL Propagation Delay Times VDD = 5V VDD = 10V VDD = 15V tPLH, tPHL Inhibit Propagation Delay Times tSU Setup Time VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V tWH Strobe Pulse Width VDD = 5V VDD = 10V VDD = 15V CPD CIN Power Dissipation Capacitance Input Capacitance Per Package (Note 5) Any Input (Note 6)

Note 4: AC Parameters are guaranteed by DC correlated testing. Note 5: CPD determines the no load AC power consumption of any CMOS device. For complete explanation, see Family Characteristics application note, AN-90. Note 6: Capacitance is guaranteed by periodic testing.

www.fairchildsemi.com

CD4514BC CD4515BC

AC Test Circuit and Switching Time Waveforms

FIGURE 1.

www.fairchildsemi.com

CD4514BC CD4515BC

Applications

Two CD4512 8-channel data selectors are used here with the CD4514B 4-bit latch/decoder to effect a complex data routing system. A total of 16 inputs from data registers are selected and transferred via a 3-STATE data bus to a data distributor for rearrangement and entry into 16 output registers. In this way sequential data can be re-routed or intermixed according to patterns determined by data select and distribution inputs. Data is placed into the routing scheme via the 8 inputs on both CD4512 data selectors. One register is assigned to each input. The signals on A0, A1 and A2 choose 1-of-8 inputs for transfer out to the 3-STATE data bus. A fourth signal, labelled Dis, disables one of the CD4512 selectors, assuring transfer of data from only one register. In addition to a choice of input registers, 116, the rate of transfer of the sequential information can also be varied. That is, if the CD4512 were addressed at a rate that is 8 times faster than the shift frequency of the input registers, the most significant bit (MSB) from each register could be selected for transfer to the data bus. Therefore, all of the most significant bits from all of the registers can be transferred to the data bus before the next most significant bit is presented for transfer by the input registers. Information from the 3-STATE bus is redistributed by the CD4514B 4-bit latch/decoder. Using the 4-bit address, INAIND, the information on the inhibit line can be transferred to the addressed output line to the desired output registers, AP. This distribution of data bits to the output registers can be made in many complex patterns. For example, all of the most significant bits from the input registers can be routed into output register A, all of the next most significant bits into register B, etc. In this way horizontal, vertical, or other methods of data slicing can be implemented.

www.fairchildsemi.com

CD4514BC CD4515BC

Physical Dimensions inches (millimeters) unless otherwise noted

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide Package Number M24B

www.fairchildsemi.com

CD4514BC CD4515BC 4-Bit Latched/4-to-16 Line Decoders

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600 Wide Package Number N24A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. www.fairchildsemi.com 8 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

You might also like

- Math Teacher Resume Dark BlueDocument2 pagesMath Teacher Resume Dark BlueasmedmirandaNo ratings yet

- Performing Logic Operations With Boolean ValuesDocument5 pagesPerforming Logic Operations With Boolean ValuesasmedmirandaNo ratings yet

- User'S Manual: JY992D84901CDocument5 pagesUser'S Manual: JY992D84901CasmedmirandaNo ratings yet

- Contador 959 - 000Document1 pageContador 959 - 000asmedmirandaNo ratings yet

- PCB Wizard 3 Tutorial 3: Drawing A Test Probe CircuitDocument10 pagesPCB Wizard 3 Tutorial 3: Drawing A Test Probe CircuitasmedmirandaNo ratings yet

- Performing Logic Operations With Boolean ValuesDocument5 pagesPerforming Logic Operations With Boolean ValuesasmedmirandaNo ratings yet

- S4a Sample03 PDFDocument4 pagesS4a Sample03 PDFasmedmirandaNo ratings yet

- Esquema Arduino UNO R3Document1 pageEsquema Arduino UNO R3stangne1No ratings yet

- Atanua Guia Uso BasicsDocument7 pagesAtanua Guia Uso BasicsasmedmirandaNo ratings yet

- Atanua Guia Uso BasicsDocument7 pagesAtanua Guia Uso BasicsasmedmirandaNo ratings yet

- TECnologo ELECTRONICADocument1 pageTECnologo ELECTRONICAasmedmirandaNo ratings yet

- SCR 400 A 600 Volts 10 AmperesDocument2 pagesSCR 400 A 600 Volts 10 AmperesJess AJNo ratings yet

- Elc 343 - Term Project #8Document2 pagesElc 343 - Term Project #8asmedmirandaNo ratings yet

- 7 SkillsDocument1 page7 SkillsasmedmirandaNo ratings yet

- 853D - V1Document1 page853D - V1asmedmirandaNo ratings yet

- Display en BarrasDocument1 pageDisplay en BarrasasmedmirandaNo ratings yet

- Relay Flash LucesDocument1 pageRelay Flash LucesasmedmirandaNo ratings yet

- LCD CFAH2002A - 1 - To - 1Document1 pageLCD CFAH2002A - 1 - To - 1asmedmirandaNo ratings yet

- Consent Form and Terms of Use For Residents of Dominican Republic For Services of ISOFT SANIDAD DOMINICANA S.R.L. (CSC Dominican Republic)Document4 pagesConsent Form and Terms of Use For Residents of Dominican Republic For Services of ISOFT SANIDAD DOMINICANA S.R.L. (CSC Dominican Republic)asmedmirandaNo ratings yet

- Dicle Levendis RFID Attendance System PDFDocument10 pagesDicle Levendis RFID Attendance System PDFasmedmirandaNo ratings yet

- Maze SolvingDocument5 pagesMaze SolvingViet NguyenNo ratings yet

- Maestro HexapodDocument21 pagesMaestro HexapodPraveen YadavNo ratings yet

- Sla7024m (Motor Driver)Document13 pagesSla7024m (Motor Driver)Franklin Miranda RoblesNo ratings yet

- Xyce Users GuideDocument236 pagesXyce Users GuideasmedmirandaNo ratings yet

- 853D - V1Document1 page853D - V1asmedmirandaNo ratings yet

- NwsetupDocument1 pageNwsetupvermachandan95No ratings yet

- Vea Pasos InstalDocument2 pagesVea Pasos InstalasmedmirandaNo ratings yet

- Cable Configuracion DetalladaDocument1 pageCable Configuracion DetalladaciguaNo ratings yet

- Type Model File Jumper COM.3ds NAME Merged ANGLE 00 SCALE 1in X 1.4 Y - 2.70Document1 pageType Model File Jumper COM.3ds NAME Merged ANGLE 00 SCALE 1in X 1.4 Y - 2.70asmedmirandaNo ratings yet

- Notas Instalacion NcplotDocument30 pagesNotas Instalacion NcplotasmedmirandaNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Flash MemoryDocument15 pagesFlash MemoryCRT07No ratings yet

- The Electric Vehicle: A Review: International Journal of Electric and Hybrid Vehicles January 2017Document19 pagesThe Electric Vehicle: A Review: International Journal of Electric and Hybrid Vehicles January 2017TUSHAR BANGERANo ratings yet

- D Link DES 1024D ManualDocument17 pagesD Link DES 1024D Manualmile.bezvezeNo ratings yet

- Homework v.1Document5 pagesHomework v.1RasedulIslam50% (2)

- 1953 3 AudioDocument76 pages1953 3 Audiokimbalsummers801100% (1)

- SHIN-NIPPON User Manual PDFDocument34 pagesSHIN-NIPPON User Manual PDFJose Moreno0% (1)

- EC5 Ampleo/R: QES000089F - REV. E - 11/2007Document8 pagesEC5 Ampleo/R: QES000089F - REV. E - 11/2007AmiroucheBenlakehalNo ratings yet

- 10 Atomic StructureDocument9 pages10 Atomic StructurearcNo ratings yet

- R999000216 09 2015 Automation Media PDFDocument124 pagesR999000216 09 2015 Automation Media PDFJose Manuel Barroso PantojaNo ratings yet

- QG - Acer - 1.0 - Es - AS E1-431 - 471 Series PDFDocument14 pagesQG - Acer - 1.0 - Es - AS E1-431 - 471 Series PDFdanny diazNo ratings yet

- Immo BypassDocument1 pageImmo BypassPaul LuczonNo ratings yet

- EMTP-RV TRV-SWTDocument31 pagesEMTP-RV TRV-SWTboopathivpNo ratings yet

- PowerCube 1000 - V300R008C00 - PowerCube 1000 V300R008C00 User Manual (Full Scenarios) PDFDocument188 pagesPowerCube 1000 - V300R008C00 - PowerCube 1000 V300R008C00 User Manual (Full Scenarios) PDFChristopher Aiyapi100% (1)

- Napolcom Exam ReviewerDocument15 pagesNapolcom Exam ReviewerIrene FriasNo ratings yet

- IBM Power 570 Replacement ProcedureDocument346 pagesIBM Power 570 Replacement Procedure26cristinaNo ratings yet

- Smaw 1Document3 pagesSmaw 1OFFSHORE-ONSHORE INSTITUTE OF TECHNOLOGY INCNo ratings yet

- Onkyo Tx-Sr602-E 8260 SMDocument124 pagesOnkyo Tx-Sr602-E 8260 SMafraniobatista100% (1)

- 327 DatatakomDocument2 pages327 DatatakomNorman RuizNo ratings yet

- Hspice UseDocument28 pagesHspice Useprasanna810243No ratings yet

- Instruction Code Instruction Code Instruction Code Instruction Code Instruction CodeDocument4 pagesInstruction Code Instruction Code Instruction Code Instruction Code Instruction Codesm_nictNo ratings yet

- Musical Curiosities in The Temples of South IndiaDocument159 pagesMusical Curiosities in The Temples of South IndiaMiguel CoponNo ratings yet

- Lumel Current TransformersDocument32 pagesLumel Current TransformersMihai BuzzNo ratings yet

- Littelfuse Suppression ProductsDocument403 pagesLittelfuse Suppression ProductsJorge MontanoNo ratings yet

- Self Dehydrating Manual Type SDBDocument39 pagesSelf Dehydrating Manual Type SDBneoph138No ratings yet

- P3-No.10.9 TBEA Power Transformer BrochureDocument28 pagesP3-No.10.9 TBEA Power Transformer Brochurehamza shahzadNo ratings yet

- Improving Power System Stability Through Integrated Power System Stabilizers - 100520Document25 pagesImproving Power System Stability Through Integrated Power System Stabilizers - 100520soumyanitcNo ratings yet

- Data Sheet - T 754 A-V Surround Sound ReceiverDocument4 pagesData Sheet - T 754 A-V Surround Sound ReceiverLokiLongbowNo ratings yet

- Development of Power Factor Meter Using ArduinoDocument4 pagesDevelopment of Power Factor Meter Using ArduinoSam SureshNo ratings yet

- PDFDocument2 pagesPDFgordomanotas100% (1)

- 111 - 33KV Capacitor Bank .Document16 pages111 - 33KV Capacitor Bank .Aseem TandonNo ratings yet