Professional Documents

Culture Documents

UD Syllabus ADMIC 20141

Uploaded by

Hugo GonzalezCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UD Syllabus ADMIC 20141

Uploaded by

Hugo GonzalezCopyright:

Available Formats

ANLISIS Y DISEO DE MICROPROCESADORES.

Universidad Distrital Francisco Jos de Caldas Facultad de Ingeniera Proyecto curricular de Ingeniera Electrnica Horario: Mircoles 8:00 10:00 am, SAB 405. Jueves 4:00 - 6:00 pm, SAB 404. Viernes 12:00 2:00 pm, SAB 500 ( Grupo 03, Lab) Martes 2:00-4:00 pm , SAB 504 (Grupo 04, Lab) Profesor: Miguel A. Melgarejo R. Correo electrnico: mmelgarejo@udistrital.edu.co Horario de atencin a estudiantes: Viernes 10:00 am-12:00 pm, Sala LAMIC, 7 piso, SAB. Viernes 3:00 pm 5:00 pm, Sala LAMIC, 7 piso, SAB. SYLLABUS. Objetivos 1. Introducir al estudiante al uso de lenguaje de descripcin de hardware para la especificacin de microprocesadores. 2. Presentar al estudiante un mtodo formal para el diseo y sntesis de microprocesadores de aplicacin especfica. 3. Introducir al estudiante en el anlisis de microprocesadores de propsito general. Programa sinttico 1. 2. 3. 4. 5. 6. 7. Seales digitales y su representacin. Lenguajes de descripcin de hardware y sntesis de circuitos digitales Dispositivos lgicos programables Microprocesadores de aplicacin especfica Sntesis de microprocesadores de aplicacin especfica. Arquitectura y programacin del procesador CISC Arquitectura y programacin del procesador RISC

Competencias. Este espacio acadmico contribuye al desarrollo de las siguientes competencias: Generales: Disear y construir herramientas para la solucin de problemas. Emplear mtodos formales de diseo. Formular, desarrollar y documentar proyectos de ingeniera

Especificas: Entender el paradigma de especificacin de sistemas digitales empleando lenguajes de descripcin de hardware. Aplicar un lenguaje de descripcin de hardware de uso comn. Emplear un mtodo formal de diseo para procesadores digitales de propsito especifico. Analizar en detalle la arquitectura de un procesador de propsito general. Programar un procesador de propsito general para resolver un problema particular.

Metodologa. En una semana : 1. Leccin magistral: presentacin de conceptos (2 horas). 2. Sesin de laboratorio: aplicacin en la realidad de los conceptos (2 horas). 3. Sesin de ejercicios: trabajo conjunto alumno profesor para reforzar los conceptos ( 2 horas). 4. Trabajo autnomo: prcticas de laboratorio, tareas y lectura autnoma de textos ( 4 horas). Evaluacin. Componente terico: 1. Examen parcial 1 (HDLs) 2. Examen parcial 2 (ASMs) 3. Examen parcial 3 (Microprocesadores) Componente prctico: 4. Proyecto 1 (HDL) 5. Proyecto 2 (ASM) 6. Proyecto 3 (Microprocesadores)

10% 10% 20%

15% 15% 30% (Examen final)

Observaciones: La ausencia en un examen o entrega de proyecto deber estar justificada por una excusa que tenga el visto bueno de oficina de bienestar institucional. Se desarrollarn tareas a lo largo del semestre. Se entregarn voluntariamente y no se calificarn, sin embargo podrn ayudar en la nota final del curso. Se espera la participacin activa de los estudiantes en las sesiones de ejercicios. La participacin no se evaluar pero podr ayudar en la nota final del curso. Se llevar listado de asistencia. Referencias bibliogrficas. Textos Gua. Principios de diseo Digital, Daniel Gajski, Prentice Hall, 2000. Fundamentos de lgica digital con diseo VHDL, Stephen Brown, McGraw Gill, 2000. Computer Architecture : a quantitative approach, John Henessey , Morgan Kauffman, 2006 Textos complementarios Computer Architecture : a quantitative approach, John Henessey , Morgan Kauffman, 2006.

The design warriors guide to FPGAs ( Devices, tools and flows), Clive Maxfield, Elsevier,2000. Synthesis and optimization of digital circuits, Giovanni de Micheli, Prentice-hall, 1992. Digital Arithmetic, Milos Ercegovac, Morgan Kaufmann, 2004.

Cronograma del curso.

Semana 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Mayo 26-30 Abril 21-25 Arquitectura de procesadores. Camino de datos general Arquitectura de procesadores: Memoria Arquitectura de procesadores: Saltos Arquitectura de procesadores: RISC vs CISC Examen parcial 3 Proyecto 3 Mar 10-14 Maquinas de estado Maquinas de estado algortmicas (ASM) Sntesis de maquinas de estado algortmicas Reduccin de rea Examen parcial 2 Proyecto 2 Tema Seales digitales y aritmtica digital Lenguajes de descripcin de hardware e introduccin al VHDL Modelado y sntesis de circuitos combinacionales en VHDL Modelado y sntesis de circuitos sincrnicos en VHDL Introduccin a la lgica programable Examen parcial 1 Proyecto 1 Gajski, Captulo 6 Gajski , Captulo 8 Gajski , Captulo 8 Gajski , Captulo 8 Gajski, Captulo 8 Gajski , Captulo 9 Henessey Gajski , Captulo 9 Henessey Gajski, Captulo 9 Henessey Gajski , Captulo 9 Henessey Evaluacin Libro gua Brown , Captulo 5 Gajski, Captulo 2 Brown , Captulo 6 Maxfield captulo Brown , Captulo 6 Brown, Captulo 7 Maxfield, Capitulos 3y4

You might also like

- Oscilador A CristalDocument10 pagesOscilador A CristalHugo GonzalezNo ratings yet

- UD Syllabus ADMIC 20141Document3 pagesUD Syllabus ADMIC 20141Hugo GonzalezNo ratings yet

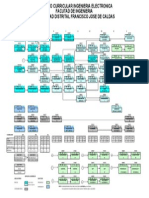

- Pensum 2007-III Horas ElectrónicaDocument1 pagePensum 2007-III Horas ElectrónicaHugo GonzalezNo ratings yet

- Proyecto1 AdmicDocument10 pagesProyecto1 AdmicHugo GonzalezNo ratings yet

- UD Syllabus ADMIC 20141Document3 pagesUD Syllabus ADMIC 20141Hugo GonzalezNo ratings yet

- Zona de Alimentacion Eldorado 0Document1 pageZona de Alimentacion Eldorado 0Hugo GonzalezNo ratings yet

- Curso Fpga Programacion Arreglos CompuertasDocument142 pagesCurso Fpga Programacion Arreglos CompuertasPaulo SalazarNo ratings yet

- Proyecto 2Document7 pagesProyecto 2Hugo GonzalezNo ratings yet

- Syllabus Electronica IIDocument8 pagesSyllabus Electronica IIHugo GonzalezNo ratings yet

- Proyecto Final Lab 2013 - 2 PDFDocument3 pagesProyecto Final Lab 2013 - 2 PDFHugo GonzalezNo ratings yet

- RenunciaDocument1 pageRenunciaHugo GonzalezNo ratings yet

- GramsciDocument3 pagesGramsciHugo GonzalezNo ratings yet

- Rub EnsDocument12 pagesRub EnsHugo GonzalezNo ratings yet