Professional Documents

Culture Documents

VHDL - Wikipedia, The Free Encyclopedia

Uploaded by

Suneelkrishna RallabhandiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VHDL - Wikipedia, The Free Encyclopedia

Uploaded by

Suneelkrishna RallabhandiCopyright:

Available Formats

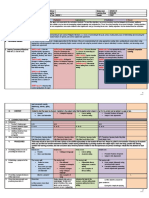

Paradigm(s) concurrent, reactive

Appeared in 1980s

Typing

discipline

strong

Influenced by Ada, Pascal

Website IEEE VASG (http://www.eda.org

/twiki/bin/view.cgi/P1076

/WebHome)

VHDL

VHDL source for a signed adder.

VHDL

From Wikipedia, the free encyclopedia

(Redirected fromVHSIC Hardware Description Language)

For Verilog HDL, see Verilog.

VHDL (VHSIC Hardware Description Language) is a

hardware description language used in electronic design

automation to describe digital and mixed-signal systems such

as field-programmable gate arrays and integrated circuits.

VHDL can also be used as a general purpose parallel

programming language.

Contents

1 History

1.1 Standardization

1.1.1 Revisions

1.1.2 Related standards

2 Design

3 Advantages

4 Design examples

4.1 Synthesizable constructs and VHDL

templates

4.2 MUX template

4.3 Latch template

4.4 D-type flip-flops

4.5 Example: a counter

4.6 Simulation-only constructs

5 VHDL simulators

6 See also

7 References

8 Further reading

9 External links

History

VHDL was originally developed at the behest of the U.S Department of Defense in order to document the

behavior of the ASICs that supplier companies were including in equipment.

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

1 of 10 5/16/2014 10:42 PM

The idea of being able to simulate the ASICs from the information in this documentation was so obviously

attractive that logic simulators were developed that could read the VHDL files. The next step was the

development of logic synthesis tools that read the VHDL, and output a definition of the physical implementation

of the circuit.

Due to the Department of Defense requiring as much of the syntax as possible to be based on Ada, in order to

avoid re-inventing concepts that had already been thoroughly tested in the development of Ada, VHDL borrows

heavily from the Ada programming language in both concepts and syntax.

The initial version of VHDL, designed to IEEE standard 1076-1987, included a wide range of data types,

including numerical (integer and real), logical (bit and boolean), character and time, plus arrays of bit called

bit_vector and of character called string.

A problem not solved by this edition, however, was "multi-valued logic", where a signals drive strength (none,

weak or strong) and unknown values are also considered. This required IEEE standard 1164, which defined the

9-value logic types: scalar std_logic and its vector version std_logic_vector.

The updated IEEE 1076, in 1993, made the syntax more consistent, allowed more flexibility in naming,

extended the character type to allow ISO-8859-1 printable characters, added the xnor operator, etc.

Minor changes in the standard (2000 and 2002) added the idea of protected types (similar to the concept of class

in C++) and removed some restrictions from port mapping rules.

In addition to IEEE standard 1164, several child standards were introduced to extend functionality of the

language. IEEE standard 1076.2 added better handling of real and complex data types. IEEE standard 1076.3

introduced signed and unsigned types to facilitate arithmetical operations on vectors. IEEE standard 1076.1

(known as VHDL-AMS) provided analog and mixed-signal circuit design extensions.

Some other standards support wider use of VHDL, notably VITAL (VHDL Initiative Towards ASIC Libraries)

and microwave circuit design extensions.

In June 2006, the VHDL Technical Committee of Accellera (delegated by IEEE to work on the next update of

the standard) approved so called Draft 3.0 of VHDL-2006. While maintaining full compatibility with older

versions, this proposed standard provides numerous extensions that make writing and managing VHDL code

easier. Key changes include incorporation of child standards (1164, 1076.2, 1076.3) into the main 1076

standard, an extended set of operators, more flexible syntax of case and generate statements, incorporation of

VHPI (interface to C/C++ languages) and a subset of PSL (Property Specification Language). These changes

should improve quality of synthesizable VHDL code, make testbenches more flexible, and allow wider use of

VHDL for system-level descriptions.

In February 2008, Accellera approved VHDL 4.0 also informally known as VHDL 2008, which addressed more

than 90 issues discovered during the trial period for version 3.0 and includes enhanced generic types. In 2008,

Accellera released VHDL 4.0 to the IEEE for balloting for inclusion in IEEE 1076-2008. The VHDL standard

IEEE 1076-2008 was published in January 2009.

Standardization

The IEEE Standard 1076 defines the VHSIC Hardware Description Language or VHDL. It was originally

developed under contract F33615-83-C-1003 from the United States Air Force awarded in 1983 to a team with

Intermetrics, Inc. as language experts and prime contractor, with Texas Instruments as chip design experts and

IBM as computer system design experts. The language has undergone numerous revisions and has a variety of

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

2 of 10 5/16/2014 10:42 PM

sub-standards associated with it that augment or extend it in important ways.

1076 was and continues to be a milestone in the design of electronic systems.

Revisions

1076-1987 First standardized revision of ver 7.2 of the language from the United States Air Force.

1076-1993 (ISBN 1-55937-376-8) Significant improvements resulting from several years of feedback.

Probably the most widely used version with the greatest vendor tool support.

1076-2000 Minor revision. Introduces the use of protected types.

1076-2002 Minor revision of 1076-2000. Rules with regard to buffer ports are relaxed.

1076-2008 (previously referred to as 1076-200x) Major revision released on 2009-01-26. Among other

changes, this standard introduces the use of external signals.

Related standards

IEEE 1076.1 VHDL Analog and Mixed-Signal (VHDL-AMS)

IEEE 1076.1.1 VHDL-AMS Standard Packages (stdpkgs)

IEEE 1076.2 VHDL Math Package (math)

IEEE 1076.3 VHDL Synthesis Package (vhdlsynth)

IEEE 1076.3 VHDL Synthesis Package - Floating Point (fphdl)

IEEE 1076.4 Timing (VHDL Initiative Towards ASIC Libraries: vital)

IEEE 1076.6 VHDL Synthesis Interoperability

IEEE 1164 VHDL Multivalue Logic (std_logic_1164) Packages

Design

VHDL is commonly used to write text models that describe a logic circuit. Such a model is processed by a

synthesis program, only if it is part of the logic design. A simulation program is used to test the logic design using

simulation models to represent the logic circuits that interface to the design. This collection of simulation models

is commonly called a testbench.

VHDL has constructs to handle the parallelism inherent in hardware designs, but these constructs (processes)

differ in syntax from the parallel constructs in Ada (tasks). Like Ada, VHDL is strongly typed and is not case

sensitive. In order to directly represent operations which are common in hardware, there are many features of

VHDL which are not found in Ada, such as an extended set of Boolean operators including nand and nor.

VHDL also allows arrays to be indexed in either ascending or descending direction; both conventions are used

in hardware, whereas in Ada and most programming languages only ascending indexing is available.

VHDL has file input and output capabilities, and can be used as a general-purpose language for text processing,

but files are more commonly used by a simulation testbench for stimulus or verification data. There are some

VHDL compilers which build executable binaries. In this case, it might be possible to use VHDL to write a

testbench to verify the functionality of the design using files on the host computer to define stimuli, to interact

with the user, and to compare results with those expected. However, most designers leave this job to the

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

3 of 10 5/16/2014 10:42 PM

simulator.

It is relatively easy for an inexperienced developer to produce code that simulates successfully but that cannot

be synthesized into a real device, or is too large to be practical. One particular pitfall is the accidental production

of transparent latches rather than D-type flip-flops as storage elements.

[1]

One can design hardware in a VHDL IDE (for FPGA implementation such as Xilinx ISE, Altera Quartus,

Synopsys Synplify or Mentor Graphics HDL Designer) to produce the RTL schematic of the desired circuit.

After that, the generated schematic can be verified using simulation software which shows the waveforms of

inputs and outputs of the circuit after generating the appropriate testbench. To generate an appropriate testbench

for a particular circuit or VHDL code, the inputs have to be defined correctly. For example, for clock input, a

loop process or an iterative statement is required.

[2]

A final point is that when a VHDL model is translated into the "gates and wires" that are mapped onto a

programmable logic device such as a CPLD or FPGA, then it is the actual hardware being configured, rather

than the VHDL code being "executed" as if on some form of a processor chip.

Advantages

The key advantage of VHDL, when used for systems design, is that it allows the behavior of the required system

to be described (modeled) and verified (simulated) before synthesis tools translate the design into real hardware

(gates and wires).

Another benefit is that VHDL allows the description of a concurrent system. VHDL is a dataflow language,

unlike procedural computing languages such as BASIC, C, and assembly code, which all run sequentially, one

instruction at a time.

A VHDL project is multipurpose. Being created once, a calculation block can be used in many other projects.

However, many formational and functional block parameters can be tuned (capacity parameters, memory size,

element base, block composition and interconnection structure).

A VHDL project is portable. Being created for one element base, a computing device project can be ported on

another element base, for example VLSI with various technologies.

Design examples

In VHDL, a design consists at a minimum of an entity which describes the interface and an architecture which

contains the actual implementation. In addition, most designs import library modules. Some designs also contain

multiple architectures and configurations.

A simple AND gate in VHDL would look something like

-- (this is a VHDL comment)

-- import std_logic from the IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- this is the entity

entity ANDGATE is

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

4 of 10 5/16/2014 10:42 PM

port (

I1 : in std_logic;

I2 : in std_logic;

O : out std_logic);

end entity ANDGATE;

-- this is the architecture

architecture RTL of ANDGATE is

begin

O <= I1 and I2;

end architecture RTL;

(Notice that RTL stands for Register transfer level design.) While the example above may seem verbose to HDL

beginners, many parts are either optional or need to be written only once. Generally simple functions like this

are part of a larger behavioral module, instead of having a separate module for something so simple. In addition,

use of elements such as the std_logic type might at first seem to be an overkill. One could easily use the

built-in bit type and avoid the library import in the beginning. However, using this 9-valued logic

(U,X,0,1,Z,W,H,L,-) instead of simple bits (0,1) offers a very powerful simulation and debugging tool to the

designer which currently does not exist in any other HDL.

In the examples that follow, you will see that VHDL code can be written in a very compact form. However, the

experienced designers usually avoid these compact forms and use a more verbose coding style for the sake of

readability and maintainability. Another advantage to the verbose coding style is the smaller amount of

resources used when programming to a Programmable Logic Device such as a CPLD.

Synthesizable constructs and VHDL templates

VHDL is frequently used for two different goals: simulation of electronic designs and synthesis of such designs.

Synthesis is a process where a VHDL is compiled and mapped into an implementation technology such as an

FPGA or an ASIC. Many FPGA vendors have free (or inexpensive) tools to synthesize VHDL for use with their

chips, where ASIC tools are often very expensive.

Not all constructs in VHDL are suitable for synthesis. For example, most constructs that explicitly deal with

timing such as wait for 10 ns; are not synthesizable despite being valid for simulation. While different

synthesis tools have different capabilities, there exists a common synthesizable subset of VHDL that defines

what language constructs and idioms map into common hardware for many synthesis tools. IEEE 1076.6 defines

a subset of the language that is considered the official synthesis subset. It is generally considered a "best

practice" to write very idiomatic code for synthesis as results can be incorrect or suboptimal for non-standard

constructs.

MUX template

The multiplexer, or MUX as it is usually called, is a simple construct very common in hardware design. The

example below demonstrates a simple two to one MUX, with inputs A and B, selector S and output X. Note that

there are many other ways to express the same MUX in VHDL.

X <= A when S = '1' else B;

Latch template

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

5 of 10 5/16/2014 10:42 PM

A transparent latch is basically one bit of memory which is updated when an enable signal is raised. Again, there

are many other ways this can be expressed in VHDL.

-- latch template 1:

Q <= D when Enable = '1' else Q;

-- latch template 2:

process(D,Enable)

begin

if Enable = '1' then

Q <= D;

end if;

end process;

D-type flip-flops

The D-type flip-flop samples an incoming signal at the rising (or falling) edge of a clock. This example has an

asynchronous, active-high reset, and samples at the rising clock edge.

DFF : process(RST, CLK)

begin

if RST = '1' then

Q <= '0';

elsif rising_edge(CLK) then

Q <= D;

end if;

end process DFF;

Another common way to write edge-triggered behavior in VHDL is with the eventsignal attribute. A single

apostrophe has to be written between the signal name and the name of the attribute.

DFF : process(RST, CLK)

begin

if RST = '1' then

Q <= '0';

elsif CLK'event and CLK = '1' then

Q <= D;

end if;

end process DFF;

Example: a counter

The following example is an up-counter with asynchronous reset, parallel load and configurable width. It

demonstrates the use of the unsignedtype, type conversions between unsignedand std_logic_vector and

VHDL generics. The generics are very close to arguments or templates in other traditional programming

languages like C++.

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

6 of 10 5/16/2014 10:42 PM

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all; -- for the unsigned type

entity COUNTER is

generic (

WIDTH : in natural := 32);

port (

RST : in std_logic;

CLK : in std_logic;

LOAD : in std_logic;

DATA : in std_logic_vector(WIDTH-1 downto 0);

Q : out std_logic_vector(WIDTH-1 downto 0));

end entity COUNTER;

architecture RTL of COUNTER is

signal CNT : unsigned(WIDTH-1 downto 0);

begin

process(RST, CLK) is

begin

if RST = '1' then

CNT <= (others => '0');

elsif rising_edge(CLK) then

if LOAD = '1' then

CNT <= unsigned(DATA); -- type is converted to unsigned

else

CNT <= CNT + 1;

end if;

end if;

end process;

Q <= std_logic_vector(CNT); -- type is converted back to std_logic_vector

end architecture RTL;

More complex counters may add if/then/else statements within the rising_edge(CLK) elsif to add other

functions, such as count enables, stopping or rolling over at some count value, generating output signals like

terminal count signals, etc. Care must be taken with the ordering and nesting of such controls if used together, in

order to produce the desired priorities and minimize the number of logic levels needed.

Simulation-only constructs

A large subset of VHDL cannot be translated into hardware. This subset is known as the non-synthesizable or

the simulation-only subset of VHDL and can only be used for prototyping, simulation and debugging. For

example, the following code will generate a clock with the frequency of 50 MHz. It can, for example, be used to

drive a clock input in a design during simulation. It is, however, a simulation-only construct and cannot be

implemented in hardware. In actual hardware, the clock is generated externally; it can be scaled down internally

by user logic or dedicated hardware.

process

begin

CLK <= '1'; wait for 10 NS;

CLK <= '0'; wait for 10 NS;

end process;

The simulation-only constructs can be used to build complex waveforms in very short time. Such waveform can

be used, for example, as test vectors for a complex design or as a prototype of some synthesizer logic that will

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

7 of 10 5/16/2014 10:42 PM

be implemented in the future.

process

begin

wait until START = '1'; -- wait until START is high

for i in 1 to 10 loop -- then wait for a few clock periods...

wait until rising_edge(CLK);

end loop;

for i in 1 to 10 loop -- write numbers 1 to 10 to DATA, 1 every cycle

DATA <= to_unsigned(i, 8);

wait until rising_edge(CLK);

end loop;

-- wait until the output changes

wait on RESULT;

-- now raise ACK for clock period

ACK <= '1';

wait until rising_edge(CLK);

ACK <= '0';

-- and so on...

end process;

VHDL simulators

Commercial:

Aldec Active-HDL

Cadence Incisive (Past products: NC-VHDL)

Mentor Graphics ModelSim. Special versions of this product used by various FPGA vendors e.g. Altera,

Lattice

Synopsys VCS-MX

Xilinx Vivado (a.k.a. xsim). Based on iSim from the previous ISE tool-chain. Xilinx Inc.

(http://www.xilinx.com)

Other:

boot. fromFree Range VHDL (http://www.freerangefactory.org/boot.html) based on GHDL and

GTKWave

GHDL. fromghdl.free.fr/ (http://ghdl.free.fr/)

Simili

Misc EDA Utilities (http://www.edautils.com) Free VHDL Parser, vhdl2verilog, vhdl2ipxact and many

other utilities

EDA Playground (http://www.edaplayground.com) - Free web browser-based VHDL IDE (uses ModelSim

for VHDL simulation)

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

8 of 10 5/16/2014 10:42 PM

See also

Hardware description language (HDL)

Altera Hardware Description Language (AHDL)

Verilog

SystemC

Register-transfer level (RTL) design

Electronic design automation (EDA)

Complex programmable logic device (CPLD)

Field-programmable gate array (FPGA)

Application-specific integrated circuit (ASIC)

References

^ "Why should I care about Transparent Latches?" (http://www.doulos.com/knowhow/fpga/latches/). Doulos.

Retrieved 22 December 2012.

1.

^ "Clock Generation" (http://www.doulos.com/knowhow/vhdl_designers_guide/tips/clock_generation/). Doulos.

Retrieved 22 December 2012.

2.

1076-1987 IEEE Standard VHDL Language Reference Manual. 1988.

doi:10.1109/IEEESTD.1988.122645 (http://dx.doi.org/10.1109%2FIEEESTD.1988.122645).

ISBN 0-7381-4324-3.

1076/INT-1991 IEEE Standards Interpretations: IEEE Std 1076-1987, IEEE Standard VHDL

Language Reference Manual. 1992. doi:10.1109/IEEESTD.1992.101084 (http://dx.doi.org

/10.1109%2FIEEESTD.1992.101084). ISBN 0-7381-0987-8.

1076-1993 IEEE Standard VHDL Language Reference Manual. 1994.

doi:10.1109/IEEESTD.1994.121433 (http://dx.doi.org/10.1109%2FIEEESTD.1994.121433).

ISBN 0-7381-0986-X.

1076-2000 IEEE Standard VHDL Language Reference Manual. 2000.

doi:10.1109/IEEESTD.2000.92297 (http://dx.doi.org/10.1109%2FIEEESTD.2000.92297).

ISBN 0-7381-1948-2.

1076-2002 IEEE Standard VHDL Language Reference Manual. 2002.

doi:10.1109/IEEESTD.2002.93614 (http://dx.doi.org/10.1109%2FIEEESTD.2002.93614).

ISBN 0-7381-3247-0.

1076c-2007 IEEE Standard VHDL Language Reference Manual Amendment 1: Procedural

Language Application Interface. 2007. doi:10.1109/IEEESTD.2007.4299594 (http://dx.doi.org

/10.1109%2FIEEESTD.2007.4299594). ISBN 0-7381-5523-3.

1076-2008 IEEE Standard VHDL Language Reference Manual. 2009.

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

9 of 10 5/16/2014 10:42 PM

doi:10.1109/IEEESTD.2009.4772740 (http://dx.doi.org/10.1109%2FIEEESTD.2009.4772740).

ISBN 978-0-7381-6854-8.

Further reading

Peter J. Ashenden, "The Designers Guide to VHDL, Third Edition (Systems on Silicon)", 2008, ISBN

0-1208-8785-1. (The VHDL reference book written by one of the lead developers of the language)

Bryan Mealy, Fabrizio Tappero (February 2012). Free Range VHDL (http://www.freerangefactory.org

/dl/free_range_vhdl.pdf). The no-frills guide to writing powerful VHDL code for your digital

implementations. freerangefactory.org (http://www.freerangefactory.org).

Johan Sandstrom (October 1995). "Comparing Verilog to VHDL Syntactically and Semantically"

(http://www.sandstrom.org/systemde.htm). Integrated System Design (EE Times). Sandstrom presents

a table relating VHDL constructs to Verilog constructs.

Qualis Design Corporation (2000-07-20). VHDL quick reference card (http://www.eda.org/rassp

/vhdl/guidelines/vhdlqrc.pdf) (PDF). 1.1. Qualis Design Corporation.

Qualis Design Corporation (2000-07-20). 1164 packages quick reference card (http://www.eda.org/rassp

/vhdl/guidelines/1164qrc.pdf) (PDF). 1.0. Qualis Design Corporation.

Janick Bergeron, "Writing Testbenches: Functional Verification of HDL Models", 2000, ISBN

0-7923-7766-4. (The HDL Testbench Bible)

External links

IEEE VASG (VHDL Analysis and Standardization Group) (http://www.eda.org/twiki/bin/view.cgi/P1076

/WebHome), the official VHDL working group

The VHDL newsgroup comp.lang.vhdl on Usenet (news://comp.lang.vhdl) and the web

(http://groups.google.com/group/comp.lang.vhdl/topics) and their Frequently Asked Questions And

Answers (http://www.vhdl.org/comp.lang.vhdl/)

Retrieved from "http://en.wikipedia.org/w/index.php?title=VHDL&oldid=606056772"

Categories: Ada programming language family Hardware description languages

This page was last modified on 27 April 2014 at 17:04.

Text is available under the Creative Commons Attribution-ShareAlike License; additional terms may

apply. By using this site, you agree to the Terms of Use and Privacy Policy. Wikipedia is a registered

trademark of the Wikimedia Foundation, Inc., a non-profit organization.

VHDL - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/VHSIC_Hardware_Description_Language

10 of 10 5/16/2014 10:42 PM

You might also like

- How Does A Smith Chart Work?Document12 pagesHow Does A Smith Chart Work?ani18100% (5)

- Antennas and Wave PropagationDocument3 pagesAntennas and Wave PropagationArockia RajaNo ratings yet

- Lump Pot 76 OhmDocument3 pagesLump Pot 76 OhmSuneelkrishna RallabhandiNo ratings yet

- Analysis and Design Principles of Microwave Antennas: Instructor Name: Amitabha Bhattacharya Institute: IIT KharagpurDocument2 pagesAnalysis and Design Principles of Microwave Antennas: Instructor Name: Amitabha Bhattacharya Institute: IIT KharagpurSuneelkrishna RallabhandiNo ratings yet

- Smith Chart From Black Magic DesignDocument1 pageSmith Chart From Black Magic DesignkgrhoadsNo ratings yet

- Geethanjali College of Engineering and TechnologyDocument2 pagesGeethanjali College of Engineering and TechnologySuneelkrishna RallabhandiNo ratings yet

- The Study of A New Circularly Polarized Microstrip Antenna PDFDocument4 pagesThe Study of A New Circularly Polarized Microstrip Antenna PDFSuneelkrishna RallabhandiNo ratings yet

- Plane Waves Part I - 2 PDFDocument13 pagesPlane Waves Part I - 2 PDFAnkur SinghNo ratings yet

- Wharton1972 PDFDocument4 pagesWharton1972 PDFSuneelkrishna RallabhandiNo ratings yet

- Design and Performance Analysis of 41 Corporate Feed Circular Polarized Rectangular Micro Strip Patch Antenna Using Hfss IJERTV3IS090767 PDFDocument6 pagesDesign and Performance Analysis of 41 Corporate Feed Circular Polarized Rectangular Micro Strip Patch Antenna Using Hfss IJERTV3IS090767 PDFSuneelkrishna RallabhandiNo ratings yet

- Impedance Matching Techniques.: Module 2: Transmission Lines Lecture 15: Impedance Matching Using Transmission LineDocument6 pagesImpedance Matching Techniques.: Module 2: Transmission Lines Lecture 15: Impedance Matching Using Transmission LineAnonymous yz5MQGtNo ratings yet

- Newman1985 PDFDocument7 pagesNewman1985 PDFSuneelkrishna RallabhandiNo ratings yet

- Electromagnetics Field Theory 69 Important MCQDocument12 pagesElectromagnetics Field Theory 69 Important MCQANIL SinghNo ratings yet

- Transmit Measured Data XXX Receive Measured Data Receive No. IDocument3 pagesTransmit Measured Data XXX Receive Measured Data Receive No. ISuneelkrishna RallabhandiNo ratings yet

- An Ultra-Broadband 3-dB Power Divider: Fanghai Xu Gaofeng Guo en Li Ju WuDocument4 pagesAn Ultra-Broadband 3-dB Power Divider: Fanghai Xu Gaofeng Guo en Li Ju WuSuneelkrishna RallabhandiNo ratings yet

- An Ultra-Broadband 3-dB Power Divider: Fanghai Xu Gaofeng Guo en Li Ju WuDocument4 pagesAn Ultra-Broadband 3-dB Power Divider: Fanghai Xu Gaofeng Guo en Li Ju WuSuneelkrishna RallabhandiNo ratings yet

- Wharton1972 PDFDocument4 pagesWharton1972 PDFSuneelkrishna RallabhandiNo ratings yet

- Novel Low Cost 1-To-4 Microstrip Wilkinson Power DividerDocument4 pagesNovel Low Cost 1-To-4 Microstrip Wilkinson Power DividerSuneelkrishna RallabhandiNo ratings yet

- Snpview: Free S-Parameter Web ViewerDocument14 pagesSnpview: Free S-Parameter Web ViewerSuneelkrishna RallabhandiNo ratings yet

- The Study of A New Circularly Polarized Microstrip Antenna PDFDocument4 pagesThe Study of A New Circularly Polarized Microstrip Antenna PDFSuneelkrishna RallabhandiNo ratings yet

- Wave Propagation GateDocument12 pagesWave Propagation GateSuneelkrishna RallabhandiNo ratings yet

- FM Transmission and Reception Rider 1949 PDFDocument402 pagesFM Transmission and Reception Rider 1949 PDFSuneelkrishna RallabhandiNo ratings yet

- Design of Yagi Uda Antenna Using HFSS Software.Document10 pagesDesign of Yagi Uda Antenna Using HFSS Software.Suneelkrishna RallabhandiNo ratings yet

- Yagi Antenna AnujDocument25 pagesYagi Antenna AnujclearhaiNo ratings yet

- Wharton1972 PDFDocument4 pagesWharton1972 PDFSuneelkrishna RallabhandiNo ratings yet

- Learn Sanskrit - Lesson 5Document16 pagesLearn Sanskrit - Lesson 5Swanand Raikar100% (1)

- Lump Pot 76 OhmDocument3 pagesLump Pot 76 OhmSuneelkrishna RallabhandiNo ratings yet

- Hfss ProjectsDocument7 pagesHfss ProjectsSuneelkrishna RallabhandiNo ratings yet

- Basics of Vedic AstrologyDocument18 pagesBasics of Vedic Astrologyclaudiota100% (1)

- Basics of Vedic AstrologyDocument18 pagesBasics of Vedic Astrologyclaudiota100% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sunrise Is Beautiful Isn't ItDocument1 pageThe Sunrise Is Beautiful Isn't ItlyaNo ratings yet

- Table of SpecificationsDocument2 pagesTable of SpecificationsJoje Sadili CostañosNo ratings yet

- LAW 521 LEGAL DRAFTING and CONVEYANCING Post Editorial Correction For UploadDocument170 pagesLAW 521 LEGAL DRAFTING and CONVEYANCING Post Editorial Correction For UploadVobogure SohagNo ratings yet

- Paliography, Epigraphy and NumismaticsDocument34 pagesPaliography, Epigraphy and NumismaticsAISWARYA K JAYANNo ratings yet

- Lesson Plan K13Document8 pagesLesson Plan K13Muhammad Hafiz Hafiz Ilham AkbarNo ratings yet

- Goethe Poems - by David HickmanDocument67 pagesGoethe Poems - by David HickmanNeo Şi-AtâtNo ratings yet

- Topic 9 PDFDocument15 pagesTopic 9 PDFDave MoonNo ratings yet

- Efficient Regular Language Search For Secure Cloud StorageDocument14 pagesEfficient Regular Language Search For Secure Cloud StorageShruthi CathrineNo ratings yet

- RobinhoodDocument13 pagesRobinhoodFrancoisNo ratings yet

- Usa & British in ProphecyDocument125 pagesUsa & British in ProphecyPeter Salemi100% (1)

- English 7Document4 pagesEnglish 7Vince Rayos CailingNo ratings yet

- Materials DevelopmentDocument23 pagesMaterials DevelopmentMbagnick DiopNo ratings yet

- Grammar 101: English For Medical School Student Muhammadiyah University Titus EmiliusDocument23 pagesGrammar 101: English For Medical School Student Muhammadiyah University Titus EmiliusAnomali RebornNo ratings yet

- RiddlesDocument6 pagesRiddlesJim BlizzardNo ratings yet

- Week 8: Getting Around: Pre-Beginner 1Document18 pagesWeek 8: Getting Around: Pre-Beginner 1Ernesto CazorlaNo ratings yet

- Unit 1Document17 pagesUnit 1trofinstephaneNo ratings yet

- 19-CPS Student Induction Presentation-RAZAK FinalDocument18 pages19-CPS Student Induction Presentation-RAZAK FinalbaderNo ratings yet

- Lesson Plan in Reflexive Pronoun Grade 10Document89 pagesLesson Plan in Reflexive Pronoun Grade 10Elmer Pineda Guevarra0% (1)

- RSpec TutorialDocument22 pagesRSpec TutorialsatyarthgaurNo ratings yet

- Marco Teorico para La Caracterizacion Patologica Del Control Sensoriomotor Del HablaDocument19 pagesMarco Teorico para La Caracterizacion Patologica Del Control Sensoriomotor Del HablaHeriberto RangelNo ratings yet

- B1 Preliminary and Preliminary For Schools 2020Document1 pageB1 Preliminary and Preliminary For Schools 2020Paula M. CánovasNo ratings yet

- Level 6 Mock Paper 12 33365876Document9 pagesLevel 6 Mock Paper 12 33365876elephantn63No ratings yet

- Movies NameDocument75 pagesMovies Namejigar8773No ratings yet

- Diction HandbookDocument69 pagesDiction HandbookTerrence A BrittNo ratings yet

- BMLS1E Rizal Chapter 2 Reporting FinalDocument39 pagesBMLS1E Rizal Chapter 2 Reporting FinalAlyssa Mae Paña RamigosoNo ratings yet

- TensesDocument18 pagesTensesMaheesha AmjaddNo ratings yet

- Contemporary Activity No 8Document3 pagesContemporary Activity No 8John Mark Ranilo100% (1)

- Oral Communication in Context: Quarter 1 - Module 6: Types of Speeches and Speech StyleDocument34 pagesOral Communication in Context: Quarter 1 - Module 6: Types of Speeches and Speech StyleDaniel Magno92% (39)

- Simple Past Vs Present Perfect Revisi N Del Intento PDFDocument1 pageSimple Past Vs Present Perfect Revisi N Del Intento PDFHector GuerraNo ratings yet

- Burroughs' Encyclopaedia of Astounding Facts and Useful Information, 1889 by Burroughs, BarkhamDocument275 pagesBurroughs' Encyclopaedia of Astounding Facts and Useful Information, 1889 by Burroughs, BarkhamGutenberg.org100% (1)