Professional Documents

Culture Documents

A New Dimmable 70W Electronic Ballast For HPS Lamps - Cavalcante - IAS02

Uploaded by

lbk50Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A New Dimmable 70W Electronic Ballast For HPS Lamps - Cavalcante - IAS02

Uploaded by

lbk50Copyright:

Available Formats

A New Dimmable 70W Electronic Ballast for High Pressure Sodium Lamps

Fabiana da Silveira Cavalcante

Power Electronic Systems Laboratory

Swiss Federal Institute of Technology Zurich

Physikstrasse 3 - ETH Zentrum

CH-8092 Zurich Switzerland

cavalcante@lem.ee.ethz.ch

http://www.pes.ee.ethz.ch

Ivo Barbi

Power Electronics Institute (INEP)

Federal University of Santa Catarina (UFSC)

P.O. Box 5119 88040-970

Florianpolis SC Brazil

ivobarbi@inep.ufsc.br

http://www.inep.ufsc.br

AbstractThis paper introduces a dimmable electronic

ballast for HPS lamps which uses a new strategy to implement

the variation of the lamps power, based on the variation of the

switches duty cycle. The complete operating principle,

theoretical analysis and relevant equations are presented in this

paper. The experimental results of a 70W electronic ballast

operating at 33 kHz switching frequency are also presented.

Keywordshigh-pressure sodium lamps; electronic ballast;

duty-cycle variation.

I. INTRODUCTION

This work presents a new 70W dimmable electronic

ballast, which uses a new strategy to improve the power

variation of a high-pressure sodium lamp. This electronic

ballast must be robust and must have a high power factor. The

ballast is commanded by a microcontroller, which has the

function of implementing the duty-cycle variation that is

responsible for the reduction of the lamps power during

certain daily periods pre-defined by the designer. A very

positive point of this innovative proposed strategy is that the

soft-switching is preserved throughout the entire range of the

duty-cycles variation.

II. THE CIRCUIT AND OPERATION PRINCIPLE

A. Circuit Description

The topology of the new 70W dimmable ballast is shown

in Fig. 1. The ballast consists of two power switches (S1, S2)

in a half-bridge inverter configuration, a DC component block

capacitor (Cc), an output filter inductor (Lo), an auxiliary

inductor (Laux) to implement the soft-switching, and a signal

and drive circuit composed basically of a microcontroller and

a gate driver integrated circuit. Diodes D1 and D2 are the

intrinsical diodes of the power switches.

B. Principle of Duty-Cycle Variation

Defining D as the duty-cycle for switch S1, switch S2 will

be driven complementary, meaning that its duty-cycle will be

equal to (1-D). This asymmetrical drive of the switches results

in a voltage waveform across the auxiliary inductor as shown

in Fig. 2, when D is smaller than or equal to 0.5. This

waveform will supply the output inductor and the lamp. Since

the ballast is operated at a high frequency, 33kHz, the lamp

can be modeled as a pure resistance.

S2

S1

Lo

Cc

Laux

D1

D2

HPS lamp

Vcc

+ -

Vaux

+

-

DVcc

+

-

Signal

drive

circuit

and

Fig. 1 Half-bridge inverter topology applied as a HPS-lamp ballast.

The rms value of the voltage, Vaux, shown in Fig. 2 is

given by (1).

( ) Vcc D 1 D Vaux

rms

= (1)

(1-D)Vcc

-DVcc

DT T

(1-D)T

Vaux

Fig. 2 Voltage waveform across the auxiliary inductor.

Equation (1) shows that the rms value of voltage Vaux

depends on the duty-cycle D. This voltage supplies the output

filter inductor and the lamp, which is considered as a

resistance. So, using electrical circuit analysis and performing

a couple of calculations, it can be proven that the lamp voltage

also depends on the duty-cycle. The next section will show an

extensive analysis of this dependence.

III. THEORETICAL ANALYSIS

A. Topological Stages

In order to simplify the analysis the following assumptions

are made: the circuit operates in steady state; all components

are considered ideal; the voltage Vcc supplied by the input

pre-regulator is constant and has no ripple; the capacitor, Cc,

is always charged with the voltage, DVcc. This voltage has the

polarity indicated in the Fig.1, and no ripple; the lamp can be

modeled as a pure resistance; the commutation times are equal

to zero therefore, the inductor, Laux, will not be considered

for this analysis. According to these considerations, the circuit

of the Fig.3 represents the simplified model of the inverter.

D1

S2

S1

D2

R

Cc

+

-

Vcc

Lo

Vaux

+

-

DVcc - +

Fig. 3 Simplified inverter topology for analysis.

First Stage (t

0

t

1

)

: This stage begins at t

0

when diode, D1,

starts conducting with an initial current equal to I

min

. This

current can be aproximated by (2),

( )

|

|

.

|

\

|

T

min

e 1

R

Vcc D

D I (2)

where:

T: switching period;

R

Lo

= : time constant of the circuit;

R: lamps resistance;

Lo: output inductor.

At this stage, the lamps current is negative and it

decreases exponentially until time t

1

, when it reaches zero,

finishing the stage. This stage is represented by Fig. 4(a). The

voltage Vaux is positive and equal to (1-D)Vcc. The lamps

current for this stage is given by (3).

( )

( )

( )

|

|

.

|

\

|

=

t

min

t

1

e D I e 1

R

Vcc D 1

t , D i (3)

Second Stage (t

1

t

2

): At t = t1, S

1

is gated on and it starts

conducting the lamps current as presented in the Fig. 4(b).

This current increases exponentially in positive direction

until reaching I

max

at t

2

, that corresponds to time D.T. The

current Imax is defined by (4).

( )

( )

|

|

.

|

\

|

=

+

1 2

t t

max

e 1

R

Vcc D 1

D I (4)

This stage ends at t

2

when S

1

is gated off. The lamps

current for the second stage is given by (5).

( )

( )

|

|

.

|

\

|

=

+

1

t t

2

e 1

R

Vcc D 1

t , D i (5)

D1

S2

S1

D2

R

Cc

+

-

Vcc

Lo

Vaux

+

-

DVcc - +

D1

S2

S1

D2

R

Cc

+

-

Vcc

Lo

Vaux

+

-

DVcc - +

(a)First Stage (b) Second Stage

D1

S2

S1

D2

R

Cc

+

-

Vcc

Lo

Vaux

+

-

DVcc - +

D1

S2

S1

D2

R

Cc

+

-

Vcc

Lo

Vaux

+

-

DVcc - +

(c) Third Stage (d) Fourth Stage

Fig. 4 - Topological Stages.

Third Stage (t

2

t

3

): This stage starts at t

2

when S

1

is gated

off and D

2

starts conducting. The lamps current is positive

and it decreases exponentially until reaching zero ending the

stage. The output current for this stage is given by (6).

( )

+

+

+

|

|

.

|

\

|

=

2 2

t t

max

t t

3

e I e 1

R 2

Vcc

t i (6)

Fourth Stage (t

3

t

4

): At t = t

3

, S2 is gated on starting the

last topological stage. The lamps current is negative and it

increases exponentially until I

min

completing one switching

period.

This stage is represented in Fig. 4(d) and (7) represents the

lamps current.

( ) ( )

+

=

3

t t

4

e 1

R

Vcc D

t , D i (7)

B. Power Variation

Considering that the lamp can be modeled as a pure

resistance, the lamps voltage for each of the topological

stages v

1

, v

2

, v

3

and v

4

can be obtained multiplying (3), (5),

(6), (7) by R, respectively. So, these voltages are also a

function of the duty-cycle and of the time. Figure 5 shows the

lamps voltage waveforms for five different duty-cycle values

for one switching period.

D= 0.1

D= 0.2

D= 0.3

D= 0.4

Lamp's Voltage(V)

D= 0.5

time(s)

0 5. 10

-6

1. 10

-5

1.5. 10

-5

2. 10

-5

2.5. 10

-5

3. 10

-5

-150

-100

50

0

50

100

150

Fig. 5 Lamps voltage as a function of duty-cycle and time.

The rms value of the lamps voltage is defined by (8).

( ) ( ) ( ) ( ) ( )

|

|

|

.

|

\

|

+ + + =

4

3

3

2

2

1

1

0

t

t

2

4

t

t

2

3

t

t

2

2

t

t

2

1

dt t , D v dt t , D v dt t , D v dt t , D v

T

1

D Vef

(8)

The rms value of the lamps voltage as a function of the

duty-cycle is shown in Fig. 6.

Therefore, the power of the lamp is also a function of the

duty-cycle.

Vrms(V)

D

0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5

30

40

50

60

70

80

90

Fig. 6 Lamps rms voltage as a function of the duty-cycle.

Figure 7 illustrates how the lamps power decreases with

the duty-cycles decrement.

Power(W)

D

0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5

10

20

30

40

50

60

70

80

Fig. 7 Lamps power as a function of the duty-cycle.

It is important to remember that this innovative strategy

preserves the soft-switching throughout the entire range of the

duty-cycles variation.

Another important fact to be considered is that lamps must

be operated in the full-power mode for at least fifteen minutes

prior to operation in the reduced- power mode. Furthermore,

in changing from the full-power mode to the reduced power-

mode, the time between full power and reduced power must

be no less than ninety seconds, and the rate of change of

power at any power level between full power and reduced

power must be no greater than that corresponding to a linear

reduction between those extremes in a ninety second time

interval [4]. If these conditions are not respected, the

extinction of the arc of the lamp can occur.

IV. DESIGN PROCEDURE AND EXAMPLE

A. Input data

DC bus voltage: 280V;

Rated output power: 70W;

Operation frequency: 33kHz;

Lamps equivalent resistance: R = 110;

Maximum duty cycle: D

max

= 0.5;

Minimum duty cycle: D

min

= 0.2.

B. Output Inductance

The output inductance and the other components of the

power stage must be designed for the full-power condition.

The output inductance must be related with the DC bus

voltage. This occurs because when the lamp becomes older its

resistance increases, therefore the inductance must be

designed so that when the lamps resistance increases, its

power decreases. Following this principle, the output

inductance is equal to 560H. Figure 8 shows the lamps

power as a function of the lamps resistance. It can be

observed that at the rated value, 110 ohms, the power is equal

to 70 W and it is maintained constant until 130 ohms before it

starts decreasing.

P (W)

70 80 90 100 110 120 130 140 150 160

60

65

70

75

80

Ro()

Fig. 8 Lamps power as a function of the lamps resistance.

C. DC block capacitor

The DC block capacitor can be determined based on a

maximum ripple value,

Cc

v , defined by the designer. Its

capacitance is given by (9).

(

(

|

|

.

|

\

|

+

|

|

|

.

|

\

|

|

|

.

|

\

|

|

|

.

|

\

|

+

1 e I 1 e 1 e t

R 2

Vcc

v 2

1

Cc

1 1 1 2

t

min

t t t

2

Cc

(9)

For a maximum output ripple of 42 V the chosen

capacitance is equal to 330 nF.

D. Auxiliary inductor

The auxiliary inductor is necessary in order to discharge

the gate- capacitances of the MOSFETs . Before the addition

of this inductor the gate voltages had some spikes that gated

on the switches inappropriately, causing a short circuit for

each commutation. The auxiliary inductor was chosen to be

equal to 2mH.

E. Power switches

Theoretically, the maximum voltage across the switches

would be equal to 280V, that it is the value of Vcc.

However, when the system operates as an open circuit, that

is, before the lamp starts, the voltage Vcc reaches 350V.

Therefore the maximum drain-to-source voltage across the

switches is V

DSmax

= 350V.

Figure 9 shows the current of the switch S1 for one

switching period for five different values of duty cycle. The

MOSFETs selection must be done considering the average

drain current and rms drain current for the rated conditions.

They are given by (10) and (11), respectively.

( ) A 344 . 0 I dt t , D i

T

1

I

avg 1 S

t

t

2 avg 1 S

2

1

=

|

|

|

.

|

\

|

=

(10)

( ) A 578 . 0 I dt t , D i

T

1

I

rms 1 S

t

t

2

2 rms 1 S

2

1

=

|

|

|

.

|

\

|

=

(11)

The IRF740 MOSFET was chosen as it features the

mentioned requirements.

D= 0.1

D= 0.2

D= 0.3 D= 0.4

i (A)

D= 0.5

time(s)

0 5 10

6

1 10

5

1.5 10

5

2 10

5

2.5 10

5

3 10

5

1.5

1

0.5

0

0.5

1

1.5

S1

Fig. 9 Drain current of the switch S1 for different values of duty cycle.

F. Signal and drive circuit

The signal and drive circuit is based on a PIC

microcontroller and on an integrated circuit IR2111.

The IR2111 is a high voltage, high-speed power MOSFET

and IGBT driver with dependent high and low side referenced

output channels designed for half-bridge applications. The

main connections for the IR2111 are shown in Fig. 10.

The PIC (Peripheral Interface Controller) microcontrollers

are RISC-based microcontrollers designed for applications

requiring high performance and low cost. The PIC can be

reprogrammed many times with a cheap programmer and it is

easy to program. For this application, it was chosen the

PIC16C62B microcontroller.

The PIC supplies a 5V pulse in the switching frequency

and with duty cycle determined by the programmer. This pulse

is adapted to 15V and is injected in the input channel of the

IR2111 that drives the two switches complementarily.

Cbs

Dbs

Rg1

Cvcc

S1

Rg2

S2

IN

Vdc

1

7

6

5

3

4

8

2

IR2111

Fig. 10 Drive circuit IR2111.

An example for the ballast operation sequence is illustrated

in Fig. 11.

The circuit is powered on when the daylight decreases

activating the photocell of the street lighting. The

microcontroller waits 10 minutes before it starts to produce

the voltage pulses for the drive circuit. After this time a soft-

start is provided and the duty cycle increases from zero to 0.5

in a specified time interval.

The duty cycle is maintained at 0.5, for example, for 6

hours until 00:10 when it is supposed that there are not so

many people in the streets anymore so, the luminosity can be

reduced. The lamps power is slowly reduced through the

duty-cycle reduction and the lamp will operate at the reduced

power until the circuit will be powered off when the morning

comes.

This operation sequence can be adjusted for different

regions and to implement these adjustments, no hardware

changes are necessary: all can be made with a software

alteration of the microcontroller.

V. EXPERIMENTAL RESULTS

Based on the theoretical analysis given in Section III, a

70W prototype has been implemented. The power stage of the

ballast was implemented using the following components:

18:00

00:10

00:20

18:10

06:00

Time

Lamp's power

70W

38W

Fig. 11 Example of time diagram for the ballast operation.

Inverter switches (S

1

, S

2

): MOSFETs IRF740;

Inverter diodes (D

1

, D

2

): MOSFETs body diodes;

Auxiliary inductor (Laux): 2mH -Ferrite core E20/6IP12

(Thornton) - 130 turns /26AWG ;

DC component block capacitor (Cc): 330nF/ 250 V

polypropylene (Epcos);

Output filter inductor (Lo): 560H -Ferrite core E30/14

IP12 (Thornton) - 76 turns / 6 turns -23AWG.

At rated power, when D is equal 0.5, the gate signal of

switch S2 (upper) and the lamps current (lower) can be

viewed in Fig. 12.

Fig. 12 Gate voltage and lamps current for D =0.5.

Voltage scale: 5V/div. Current scale: 1A/div

The lamps voltage (upper) and current (lower) for rated

conditions are shown in Fig. 13.

Fig. 13 Lamps voltage and lamps current for D =0.5.

Voltage scale: 100V/div. Current scale: 1A/div

The symmetry between the voltage and current waveforms

proves that when the lamp is operated at a high-frequency, it

can be modeled as a pure resistance.

At the chosen reduced power, 38W, when D is equal 0.2,

the gate signal of switch S2 (upper) and the lamps current

(lower) can be viewed in Fig. 14.

Fig. 14 Gate voltage and lamps current for D =0.2.

Voltage scale: 5V/div. Current scale: 1A/div

The lamps voltage (upper) and current (lower), at 38W of

power, are shown in Fig. 15.

Some relevant experimental results for the implemented

prototype are presented in Table I.

Fig. 15 Lamps voltage and lamps current for D =0.2.

Voltage scale: 100V/div. Current scale: 1A/div

TABLE I. RELEVANT EXPERIMENTAL RESULTS

Duty Cycle

Parameter D= 0.5 D=0.2

Lamps rms voltage 79,3 V 62,5 V

Lamps rms current 887 mA 626 mA

Lamps power 70,2 W 38,1 W

Power factor 0,973 0,805

Efficiency 88,41% 87,58%

It can be observed that the ballast efficiency is very high

for this power range. It could be observed later with the

construction of prototypes for higher power that the converter

losses will not increase linearly with the power increase so it

will be expected that for higher power the converter efficiency

will be significantly better.

VI. CONCLUSIONS

This work presented a new electronic ballast for HPS

lamps that uses an innovative strategy to control the lamps

power, throughout the variation of the power switches duty

cycle. The electronic ballast is completely controlled by a PIC

microcontroller, which takes care of the duty-cycles variation.

The new ballast is robust, it has high efficiency and soft-

switching is preserved throughout the entire range of the duty-

cycles variation. So, the experimental results showed that the

new power variation strategy is appropriate for this

application.

REFERENCES

[1] BARBI, I. Design of Switched-Mode Power Supplies (in Portuguese).

Power Electronics Institute UFSC. Florianpolis SC, 1990.

[2] CAVALCANTE, F. S. Electronic Ballasts for 70W HPS Lamps.

Masters Degree thesis (in Portuguese), INEP/UFSC. Florianpolis - SC,

2001.

[3] GROOT, J.J. and VLIET, J.A. J.M.. The High-Pressure Sodium Lamp.

Philips technical Library,1986.

[4] High Intensity Discharge Lamp Dimming. GE Lighting Institute,

http://www.gelighting.com, 2001.

[5] PIC16C62B/72A - 28-Pin 8 Bit CMOS Microcontrollers. Datasheet.

Microchip Technology Inc.. http://www.microchip.com, 1999.

[6] REDL, Richard. PAUL, Jon D.. A New High-Frequency and High-

Efficiency Electronic Ballast for HID Lamps: Topology, Analysis,

Design and Experimental Results. In: IEEE APEC 99( March 1999:

Dallas). APEC99 Proceedings. Dallas, 1999, pp. 486-492.

[7] The IESNA Lighting Handbook: Reference and Application. Illuminating

Engineering Society of North America. 9

th

Edition, 2000.

[8] VAN TICHELEN, P. ,WEYEN, D., GEENS, R. et al. A Novel

Dimmable Electronic Ballast for Street Lighting with HPS Lamps. In

IEEE IAS 00 (October 2000: Rom, Italy). Conference Record of the

2000 IEEE Industry Applications Society Conference. Rom, 2000, pp.

3419-3422.

You might also like

- New Definitive Tests For Corrosive SulfurDocument2 pagesNew Definitive Tests For Corrosive Sulfurlbk50No ratings yet

- 2008SimonelliPresentation - Water in TransformersDocument25 pages2008SimonelliPresentation - Water in Transformerslbk50No ratings yet

- The Benefits of On-Line DGA Tap Changer MonitoringDocument9 pagesThe Benefits of On-Line DGA Tap Changer Monitoringlbk50No ratings yet

- The Case of Failed TransformerDocument84 pagesThe Case of Failed Transformerlbk50100% (1)

- 2008BroszPresentation - Forensic Aspects of Transformer FailuresDocument22 pages2008BroszPresentation - Forensic Aspects of Transformer Failureslbk50No ratings yet

- The Case of Failed TransformerDocument84 pagesThe Case of Failed Transformerlbk50100% (1)

- Spatial Resolution Impacts Temperature ReadingsDocument9 pagesSpatial Resolution Impacts Temperature Readingslbk50No ratings yet

- 2008CoxPaper - The Benefits of Online DGA Tap Changer MonitoringDocument6 pages2008CoxPaper - The Benefits of Online DGA Tap Changer Monitoringlbk50No ratings yet

- Spatial Resolution Impacts Temperature ReadingsDocument9 pagesSpatial Resolution Impacts Temperature Readingslbk50No ratings yet

- 2008SimonelliPresentation - Water in TransformersDocument25 pages2008SimonelliPresentation - Water in Transformerslbk50No ratings yet

- Design Improvement by Diagnostics of Transformers Still in Operation and of Apparatus Taken Out of ServiceDocument50 pagesDesign Improvement by Diagnostics of Transformers Still in Operation and of Apparatus Taken Out of Servicelbk50No ratings yet

- 2008CoxPaper - The Benefits of Online DGA Tap Changer MonitoringDocument6 pages2008CoxPaper - The Benefits of Online DGA Tap Changer Monitoringlbk50No ratings yet

- The Aging of America TransformersDocument49 pagesThe Aging of America Transformerslbk500% (1)

- Condition Health Indices and Probabiltiy of FailureDocument30 pagesCondition Health Indices and Probabiltiy of Failurelbk50No ratings yet

- Transformer Winding Hot Spot Temperature DeterminationDocument35 pagesTransformer Winding Hot Spot Temperature Determinationlbk50No ratings yet

- Loss Prevention of A Global ScaleDocument13 pagesLoss Prevention of A Global Scalelbk50No ratings yet

- Field Processing Methods Fo Transformer Dry OutDocument42 pagesField Processing Methods Fo Transformer Dry Outlbk50100% (1)

- Transformer Life Extention Methodlogy Thru LTC ReplacementDocument28 pagesTransformer Life Extention Methodlogy Thru LTC Replacementlbk50No ratings yet

- Investigating Transformer Failures and Case StudiesDocument54 pagesInvestigating Transformer Failures and Case Studieslbk50100% (1)

- The Benefits of On-Line DGA Tap Changer MonitoringDocument9 pagesThe Benefits of On-Line DGA Tap Changer Monitoringlbk50No ratings yet

- Maintaining Short Circuit Strength in TransformersDocument26 pagesMaintaining Short Circuit Strength in Transformerslbk50No ratings yet

- Improving MV Underground Cable Performance - Experience of TNB MalaysiaDocument4 pagesImproving MV Underground Cable Performance - Experience of TNB Malaysialbk50No ratings yet

- Breaker Oil Analysis - A Non-Invaisve Approach To Maintenance Scheduling - PresentationDocument36 pagesBreaker Oil Analysis - A Non-Invaisve Approach To Maintenance Scheduling - Presentationlbk50No ratings yet

- Square Ageing Effects and Equipmet Fleet RequirementsDocument30 pagesSquare Ageing Effects and Equipmet Fleet Requirementslbk50No ratings yet

- From Transformer Incident To CourtDocument55 pagesFrom Transformer Incident To Courtlbk50No ratings yet

- Asset Management Applied at UtilitiesDocument22 pagesAsset Management Applied at Utilitieslbk50No ratings yet

- SF6 Handling Safety & Transportation GuideDocument13 pagesSF6 Handling Safety & Transportation Guidelbk50No ratings yet

- The Impact of Data Management On Hartford Steam Boiler's TOGA ProgramDocument21 pagesThe Impact of Data Management On Hartford Steam Boiler's TOGA Programlbk50No ratings yet

- New Diagnostic Concepts For Better Asset ManagementDocument44 pagesNew Diagnostic Concepts For Better Asset Managementlbk50No ratings yet

- DGA AnalysisDocument53 pagesDGA Analysislbk50No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Thermal BurnsDocument50 pagesThermal BurnsPooya WindyNo ratings yet

- Analysis and Calculations of The Ground Plane Inductance Associated With A Printed Circuit BoardDocument46 pagesAnalysis and Calculations of The Ground Plane Inductance Associated With A Printed Circuit BoardAbdel-Rahman SaifedinNo ratings yet

- Quaternary Protoberberine Alkaloids (Must Read)Document26 pagesQuaternary Protoberberine Alkaloids (Must Read)Akshay AgnihotriNo ratings yet

- Proposal Anguria Pasta NewDocument24 pagesProposal Anguria Pasta NewNOOR IRDINA HAFIZAH BT TAUPISNo ratings yet

- Current Relays Under Current CSG140Document2 pagesCurrent Relays Under Current CSG140Abdul BasitNo ratings yet

- Application of Fertility Capability Classification System in Rice Growing Soils of Damodar Command Area, West Bengal, IndiaDocument9 pagesApplication of Fertility Capability Classification System in Rice Growing Soils of Damodar Command Area, West Bengal, IndiaDr. Ranjan BeraNo ratings yet

- Rapid Prep Easy To Read HandoutDocument473 pagesRapid Prep Easy To Read HandoutTina Moore93% (15)

- Virchow TriadDocument6 pagesVirchow Triadarif 2006No ratings yet

- Swatchh Bharat AbhiyanDocument13 pagesSwatchh Bharat AbhiyanHRISHI SHARMANo ratings yet

- Fraktur Dentoalevolar (Yayun)Document22 pagesFraktur Dentoalevolar (Yayun)Gea RahmatNo ratings yet

- Feline DermatologyDocument55 pagesFeline DermatologySilviuNo ratings yet

- TutorialDocument324 pagesTutorialLuisAguilarNo ratings yet

- A6 2018 D Validation Qualification Appendix6 QAS16 673rev1 22022018Document12 pagesA6 2018 D Validation Qualification Appendix6 QAS16 673rev1 22022018Oula HatahetNo ratings yet

- Soil LiquefactionDocument12 pagesSoil LiquefactionKikin Kikin PelukaNo ratings yet

- Aircraft Design Project 2Document80 pagesAircraft Design Project 2Technology Informer90% (21)

- Phenomenological of in Church and TV WorshipDocument18 pagesPhenomenological of in Church and TV WorshipCindy TirtaNo ratings yet

- Nickel-Metal Hydride Battery Safety Data SheetDocument8 pagesNickel-Metal Hydride Battery Safety Data SheetYeong WheeNo ratings yet

- Pitch Manual SpecializedDocument20 pagesPitch Manual SpecializedRoberto Gomez100% (1)

- Internship ReportDocument18 pagesInternship ReportRathan Kumar SMNo ratings yet

- 07 Raction KineticsDocument43 pages07 Raction KineticsestefanoveiraNo ratings yet

- Direct From: 1St Quarter 2020Document23 pagesDirect From: 1St Quarter 2020JeanNo ratings yet

- Essentials For Professionals: Road Surveys Using SmartphonesDocument25 pagesEssentials For Professionals: Road Surveys Using SmartphonesDoly ManurungNo ratings yet

- Datasheet PDFDocument6 pagesDatasheet PDFAhmed ElShoraNo ratings yet

- PDFViewer - JSP 3Document46 pagesPDFViewer - JSP 3Kartik ChaudharyNo ratings yet

- DENSO COMMON RAIL INJECTOR REPAIR GUIDEDocument22 pagesDENSO COMMON RAIL INJECTOR REPAIR GUIDEMarcoNo ratings yet

- 中美两国药典药品分析方法和方法验证Document72 pages中美两国药典药品分析方法和方法验证JasonNo ratings yet

- A Compilation of Thread Size InformationDocument9 pagesA Compilation of Thread Size Informationdim059100% (2)

- Acuity Assessment in Obstetrical TriageDocument9 pagesAcuity Assessment in Obstetrical TriageFikriNo ratings yet

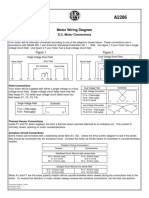

- Motor Wiring Diagram: D.C. Motor ConnectionsDocument1 pageMotor Wiring Diagram: D.C. Motor Connectionsczds6594No ratings yet

- Design of Fixed Column Base JointsDocument23 pagesDesign of Fixed Column Base JointsLanfranco CorniaNo ratings yet