Professional Documents

Culture Documents

DDR3 ReportNEW Bala (1) F

Uploaded by

Kirti Dutt0 ratings0% found this document useful (0 votes)

28 views76 pagessdfsdfssdfsdfsdfsdfsdfsdfsdfsdfsdf

Original Title

DDR3 ReportNEW Bala (1)f

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentsdfsdfssdfsdfsdfsdfsdfsdfsdfsdfsdf

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

28 views76 pagesDDR3 ReportNEW Bala (1) F

Uploaded by

Kirti Duttsdfsdfssdfsdfsdfsdfsdfsdfsdfsdfsdf

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 76

A Project Report on

DDR3 MEMORY CONTROLLER FOR HIGH

PERFORMANCE NETWORKING PROCESS

Submitted in partial fulfillment for the award of degree of

BACHELOR OF TECHNOLOGY

IN

ELECTRONICS AND COMMUNICATION ENGINEERING

Submitted by

CH.BALASARASWATHI(106F1A041!

G.SUNITHA(106F1A04""!

K.RO#A(106F1A043$!

SUNITHASHARMA(106F1A043!

Under the guidance of:

Mr.M.Ramesh, M.Tech

Asst. Professor

DEPARTMENT

OF

ELECTRONICS AND COMMUNICATION ENGINEERING

SAI GANAPATHI ENGINEERING COLLEGE

(Affiliated to Jawaharlal Nehru technological universit. !a"inada#

$idi%ala village.Ananda&uram,'isa"ha&atnam()*++,*

-.+.(-.+/

0A1 $ANAPAT21 3N$1N33R1N$ 45663$3,$171JA6A(

)*++,*

73PARTM3NT 58 3634TR5N140 AN7 45MMUN14AT15N

CERTIFICATE

This is to certif that the &ro%ect wor" entitled DDR3 MEMORY

CONTROLLER FOR HIGH PERFORMANCE

NETWORKING PERFORMANCE is a 9onafide wor" carried out

at 0A1 $ANAPAT21 3N$1N33R1N$ 45663$3, $171JA6A, 9

CH.BALASARASWATHI%P1NN5.(106F1A041#:G.SUNITHA,P1NN5.

(106F1A04""#:K.RO#A%P1NN5.(106F1A043$#;SUNITHA

SHARMA%P1NN5.(106F1A043#. <e the students of fourth ear second

0emester =.Tech, in the 7e&artment of ELECTRONICS AND

COMMUNICATION ENGINEERING, 0$34, in &artial fulfillment of

the re>uirements for the award of degree in BACHELOR OF

TECHNOLOGY affiliated to #AWAHARLAL NEHRU

TECHNOLOGICAL UNI&ERSITY% KAKINADA during the academic

ear -.+.(-.+/.

INTERNAL GUIDE HEAD OF THE

DEPARTMENT

Mr.M.Ramesh,M.Tech Mr.!.RAM302,M.Tech

Asst.Professor, Asst.Professor,

7e&t of 343 7e&t of 343

E'TERNAL E'AMINER

DECLARATION

<e here9 declare that the &ro%ect wor" entitled DDR3 MEMORY

CONTROLLER FOR HIGH PERFORMANCE OF NETWORKING

PROCESS is the 9onafied wor" done 9 us and su9mitted in &artial fulfillment for

the award of degree in B()*+,-. -/ T+)*0-,-12 in ELECTRONICS AND

COMMUNICATION, in S(3 G(0(4(5*3 E0130++.301 C-,,+1+ $idi%ala , and this

&ro%ect wor" has not 9een su9mitted in an other college or universit for the award of

an "ind of degree.

0u9mitted 9,

CH.BALASARAS

WATHI(106F1A041!

G.SUNITHA(106F1A04""!

K.RO#A(106F1A043$!

SUNITHA SHARMA(106F1A043!

ACKNOWLEDGEMENT

<e wish to e?&ress our dee&est sense of gratitude to M..M.RAMESH%

M.T+)* assistant &rofessor 3.4.3 7e&artment for his whole hearted co(o&eration,

unfailing ins&iration and valua9le guidance. Throughout the wor", his useful suggestions,

constant encouragement has given direction and sha&e to our learning. we are inde9ted

to him for his e?cellent and enlightened guidance.

<e consider it our &revilege to e?&ress our dee&est gratitude to

M..M.RAMESH% M.T+)* assistant &rofessor and 2ead of the 7e&artment for his

valua9le suggestions and constant motivation that greatl hel&ed the &ro%ect wor" to get

successfull com&leted.

<e also than" P.-/. &. RANGA RAO% Princi&al, for e?tending his utmost

su&&ort and coo&eration in &roviding all the &rovisions for successful com&letion of the

&ro%ect.

<ith great solemnit and sincerit, we offer our &rofuse than"s to our

management, SAI GANAPATHI ENGINEERING COLLEGE for successful

com&letion of the &ro%ect.

<e sincerel than" all the mem9ers of all the teaching and technical staff of the

7e&artment of 3lectronics and 4ommunication 3ngineering for their invalua9le hel& in

all our &ursuits.

<e than" all those who contri9uted directl or indirectl in successfull carring

out this wor".

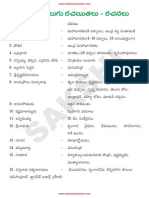

CONTENTS

1. DECLARATION 66666666666666666666666666666666666..1

". ACKNOWLEDGEMENT66666666666666666666666666666666."

3. ABSTRACT6666666666666666666666666666666666666....3

4. CONTENTS6666666666666666666666666666666666666....4

). LIST OF FIGURES6666666666666666666666666666666666....)

CHAPTER 16666666666666666666666.($713!

1.INTRODUCTION

1 INTRODUCTION6666666666666666666666666666

1.1 DDR3 SDRAM666666666666666666666666666

1." DDR3BASED LOOKUP CIRCUIT666666666666666666.1"

1.3 DDR3 AD&ANTAGES66666666666666666666666..13

CHAPTER "66666666666666666666(147"8!

TYPES OF MEMORY CONTROLLER

-.1TYPESOFMEMORYCONTROLLER666666666666666666.18

".1.1 DDR DIGITAPULSE66666666666666666666666616

"." DDR" SDRAM6666666666666666666666666666..16

".3 DDR3 SDRAM6666666666666666666666666666..1$

".4 COMPONENTS OF DDR9S666666666666666666666661:

".8 OTHER MEMORY TYPES6666666666666666666666.."0

".8.1 &IDEO RANDOM ACCESS MEMORY6666666666666666"0

".8." FLASH MEMORY6666666666666666666666666."0

".8.3 SHADOW RAM66666666666666666666666666.."1

".8.4 STATIC RAM66666666666666666666666666.."1

".8.8 DYNAMICRAM66666666666666666666666666"1

".8.6 CACHEMEMORY6666666666666666666666666"3

".8.$ CONTENT ADDRESSABLEMEMORY666666666666666."4

".8. HARDWARE ASSOCIATI&EMEMORY666666666666666"8

CHAPTER 3666666666666666666666.("6740!

DESIGN OF DDR3 SDRAM CONTROLLER

3.1 INTRODUCTION66666666666666666666666666"6

3." FUNCTIONAL BLOCK DIAGRAM66666666666666666."$

3.".1 ADDRESS FIFO666666666666666666666666"

3."." WRITE DATA FIFO66666666666666666666666...30

3.".3 CONTROLFIFO666666666666666666666666.31

3.".4 READ DATAREGISTER666666666666666666666631

3.3 DIFFERENT STATES OF INITIALFSM6666666666666666.31

3.3.IDLE6666666666666666666666666666666.34

3.3." NOOPERATION666666666666666666666666634

3.3.3PRECHARGE6666666666666666666666666666..38

3.3.4AUTOREFRESH666666666666666666666666666.38

3.3.8 LOAD MOD REGISTER666666666666666666666.38

3.3.6 READ;WRITECYCLE6666666666666666666666.38

CHAPTER466666666666666666666..(41780!

DIFFERENT STATES OF COMMAND FSM

4.1 DIFFERENT STATES OF COMMANFSM6666666666666664"

4.1.1 REFRESH CYCLE666666666666666666666664"

4.1. ACTI&E66666666666666666666666666664"

4.1. READ66666666666666666666666666666.43

4.1.4WRITE66666666666666666666666666666.44

4.1.8REFRESHCYCLE66666666666666666666666666646

4.1.6 DATPATHCONTROL66666666666666666666664$

4.1.$BANKCONTROL66666666666666666666666666....4$

4.1. TIMING DIAGRAM66666666666666666666666...4$

4."AD&ANTAGES66666666666666666666666666666..4:

4.3DISAD&ANTAGES6666666666666666666666666666.80

CHAPTER 866666666666666666666(8176"!

RESULTS

8.1 SIMULATION RESULT66666666666666666666668"

8.1.1 ADDRESSFIFO66666666666666666683

8.1." CONTROLFIFO66666666666666666.83

8.1.3 WRITEDATAFIFO666666666666666684

8.1.4 INITIALFSM666666666666666666..88

8.1.8 COMMANDFSM66666666666666666..86

8.1.8.1 NORMALWRITE666666666666

86

8.1.8." NORMALREAD666666666666.8$

8.1.8.3 FASTREAD666666666666668

8.1.6 DATA PATHCONTROL666666666666668:

8.1.$ TOP MODULE666666666666666666..60

8.1.$.1 NORMAL WRITE

OPERATION66666...60

8.1.$." NORMAL READ OPERATION666666

61

8.1.$.3 FAST READ666666666666666"

CHAPTER 6666666666666666666666(6"768!

CONCLUSION AND FUTURESCOPE6666666666666663

6.1 CONCLUSION6666666666666666666666666664

6." FUTURE SCOPE666666666666666666666666668

CHAPTER $666666666666666666666.(6676!

REFRENCES6666666666666666666666666.6$

CHAPTER 6666666666666666666666(6:7$:!

APPENDI'

.1 O&ER&IEW66666666666666666666666666..$0

." HISTORY BEGINNING666666666666666666666.$"

.3 DESIGN STYLES666666666666666666666666$4

.4 &ERILOG ABSTRACTION LE&ELS666666666666666$6

.8 ABOUT &ERILOG HDL666666666666666666666$$

.6 SALIENT FUTURES OF &ERILOG666666666666666..$

610T 58 81$U3R0:

81$ +.+ 77R* 07RAM

81$ +.- 30T1MAT15N $RAP2

81$ +.* 2A02 4AM 655!UP 41R4U1T

81$ -.+ $RAP214A6 R3PR303NTAT15N

81$ -.- 45MPAR105N 58 77R@0

81$ *.+ 8UN4T15NA6 =654! 71A$RAM

81$ *.- 1N1T1A6 80M 0TAT3 71A$RAM

81$ *.* PR3 42AR$3 45MMAN7

81$ *./ 45MMAN7 80M 0TAT3 71A$RAM

85R N5RMA6 R3A7A<R1T3

81$ *.) 45MMAN7 80M 8A0T R3A7

81$ /.+ A4T1'AT1N$ A 0P341814 R5<

1N A 0P341814 =AN!

81$ /.- R3A7 45MMAN7

81$ /.* <R1T3 45MMAN7

81$ /./ R3A7 4B463 T1M1N$ 71A$RAM

81$ /.) <R1T3 4B463 T1M1N$ 71A$RAM

81$ C.+ T5P(75<N 7301$N APPR5A42

ABSTRACT

1n com&uting, 77R* 07RAM or dou9le(data(rate three snchronous

dnamic random access memories is a random access memor interface

technolog used for high 9andwidth storage of the wor"ing data of a com&uter or

other digital electronic devices. 77R* is &art of the 07RAM famil of

technologies and is one of the man 7RAM (dnamic random access memor#

im&lementations. 77R* 07RAM is the *rd generation of 77R memories,

featuring higher &erformance and lower &ower consum&tion. 1n com&arison

with earlier generations, 77R+A- 07RAM, 77R* 07RAM is a higher densit

device and achieves higher 9andwidth due to the further increase of the

cloc" rate and reduction in &ower consum&tion.

1n this wor", the 77R*07RAM controller is designed and it can interface

with 6oo" u& ta9le 9ased 2ash 4AM circuit. C-05+057(<<.+==(>,+ ?+?-.2

(CAM# is a s&ecial t&e of com&uter memor used in certain ver high s&eed

searching a&&lications. =ecause a 4AM is designed to search its entire memor in

a single o&eration, it is much faster than RAM in virtuall all search

a&&lications.The architecture of 77R*07RAM controller consists of

1nitialiDation fsm 4ommand fsm, data &ath , 9an" control ,cloc" counter, refresh

counter, Address 8185, command 8185 ,<data 8185 and REdata reg .

1n this &a&er, an advanced 77R*07RAM controller architecture was

designed and which can interface with a high &erformance 2ash(4AM 9ased

loc"u& circuit. The 77R*07RAM controller normal write, read and fast read

o&erations are verified 9 simulation and 77R*07RAM controller is

snthesiDed.

058T<AR3 T556:F161NF G.-

01MU6AT5R :M573601M H./

CHAPTER 1

INTRODUCTION

CHAPTER 1

INTRODUCTION

1. INTRODUCTION

1.1 DDR3 SDRAM@

1n electronic engineering, 77R* 07RAM or dou9le(data(rate three snchronous

dnamic random access memories is a random access memor technolog used for high

9andwidth storage of the wor"ing data of a com&uter or other digital electronic

devices.77R* is &art of the 07RAM famil of technologies and is one of the man

7RAM (dnamic random access memor# im&lementations. 77R* 07RAM is an

im&rovement over its &redecessor, 77R- 07RAM.

The &rimar 9enefit of 77R* is the a9ilit to transfer 1A5 data at eight times the

data rate of the memor cells it contains, thus ena9ling higher 9us rates and higher &ea"

rates than earlier memor technologies. 2owever, there is no corres&onding reduction in

latenc, which is therefore &ro&ortionall higher. 1n addition, the 77R* standard allows

for chi& ca&acities of )+- mega9its to C giga9its, effectivel ena9ling a ma?imum

memor module siDe of +H giga9tes.

The 77R* 07RAM is not ver much different from the &revious generation

77R memor in terms of its design and wor"ing &rinci&les. 1n fact, it is true: 77R*

07RAM is a sort of third reincarnation of 77R 07RAM &rinci&les. Therefore, we have

ever right to com&are 77R* and 77R- 07RAM side 9 side here. Moreover, this

com&arison will hardl ta"e a lot of time.

FIG 1.1:DDR3 SDRAM

The fre>uencies of 77R* memor could 9e raised 9eond those of 77R- due to

dou9ling of the data &refetch that was moved from the info storage device to the

in&utAout&ut 9uffer. <hile 77R- 07RAM uses /(9it sam&les, 77R* 07RAM uses C(9it

&refetch also "nown as Cn(&refetch. 1n other words, 77R* 07RAM technolog im&lies

dou9ling of the internal 9us width 9etween the actual 7RAM core and the in&utAout&ut

9uffer. As a result, the increase in the efficient data transfer rate &rovided 9 77R*

07RAM doesn@t re>uire faster o&eration of the memor core. 5nl e?ternal 9uffers start

wor"ing faster. As for the core fre>uenc of the memor chi&s, it a&&ears C times lower

than that of the e?ternal memor 9us and 77R* 9uffers (this fre>uenc was / times

lower than that of the e?ternal 9us 9 77R-# 0o, 77R* memor can almost immediatel

hit higher actual fre>uencies than 77R- 07RAM, without an modifications or

im&rovements of the semiconductor manufacturing &rocess. 2owever, the a9ove

descri9ed techni>ue also has another side to it: unfortunatel, it increases not onl

memor 9andwidth, 9ut also memor latencies. As a result, we shouldn@t alwas e?&ect

77R* 07RAM to wor" faster than 77R- 07RAM, even if it o&erates at higher

fre>uencies than 77R-.

The final 77R* 07RAM s&ecification released 9 J3734 recentl descri9es a

few modifications of this memor with fre>uencies from C.. to +H..M2D. The ta9le

9elow shows the ma%or s&ecifications of the memor modifications listed in the s&ec:

TABLE 1.1:DDR3 SDRAM SPECIFICATIONS

4onsidering that the latenc of widel s&read 77R-(C.. 07RAM with /(/(/

timings e>uals +.ns, we can reall >uestion the efficienc of 77R* 07RAM at this time.

1t turns out that the new 77R* can onl win due to higher 9andwidth that should ma"e

u& for worse latenc values. Unfortunatel, the transition to 77R* 07RAM is a forced

measure to some e?tent. 77R- has alread e?hausted its fre>uenc &otential com&letel.

Although we can still &ush it to +.HHM2D with some allowances, further fre>uenc

increase lowers the &roduction ields dramaticall thus increasing the &rice of the 77R-

07RAM modules. That is wh J3734 didn@t standardiDe 77R- 07RAM with wor"ing

fre>uencies e?ceeding C..M2D, su&&orting the transition to 77R* technolog.

2owever, 77R* 07RAM offers a few other useful im&rovements that will

encourage not onl the manufacturers 9ut also the end users to ma"e u& their minds in

favor of the new technolog. Among these advantages 1 would li"e to first of all mention

lower voltage of the 77R* 07RAM modules that dro&&ed down to +.)'. 1t is -.I lower

than the voltage of 77R- 07RAM modules, which eventuall results into almost *.I

reduction in &ower consum&tion com&ared with 77R- memor wor"ing at the same

cloc" s&eeds. More advanced memor chi&s manufacturing technologies also contri9ute

to this &ositive effect.

FIG 1.2:ESTIMATION GRAPH

The =$A chi& &ac"aging also underwent a few modifications, and now it features more

&ins. This sim&lifies the chi& mounting &rocedure and increases mechanical contact.

1." DDR3 B(=+< L--AB4 C3.)B35 /-. H31*7P+./-.?(0)+ N+5C-.A

P.-)+==301

<ith the develo&ment of networ" sstems, &ac"et &rocessing techni>ues are

9ecoming more im&ortant to deal with the massive high(through&ut &ac"ets of the

internet. Accordingl, advances in memor architectures are re>uired to meet the

emerging 9andwidth demands. 4ontent Addressa9le Memor (4AM# 9ased techni>ues

are widel used in networ" e>ui&ment for fast ta9le loo" u&. 2owever, in com&arison to

Random Access Memor (RAM# technolog, 4AM technolog is restricted in terms of

memor densit, hardware cost and &ower dissi&ation. Recentl, a 2ash(4AM circuit ,

which com9ines the merits of the hash algorithm and the 4AM function, was &ro&osed to

re&lace &ure 4AM 9ased loo"u& circuits with com&ara9le &erformance, higher memor

densit and lower cost. Most im&ortantl, off(chi& high densit low(cost 77R memor

technolog has now 9ecome an attractive alternative for the &ro&osed 2ash(4AM 9ased

loo"u& circuit. 2owever, 77R technolog is o&timiDed for 9urst access for cached

&rocessor &latforms. As such, efficient 77R =andwidth utiliDation is a ma%or challenge

for loo"u& functions that e?hi9it short and random memor access &atterns. The e?treme

low(cost and high memor densit features of the 77R technolog allow a trade(off

9etween memor utiliDation and memor(9andwidth utiliDation 9 customiDing the

memor access. This, however, re>uires a custom &ur&ose 77R memor controller that

is o&timiDed to achieve the 9est read efficienc and highest memor 9andwidth. The

o9%ective of this wor" was to investigate advanced 77R* 07RAM controller

architectures and derive a customiDed architecture for the a9ovementioned &ro9lem.

77R* 07RAM is the *rd gener memories, featuring higher &erformance and lower

&ower consum&tion . 1n com&arison with earlier generations, 77R+A- 07RAM, 77R*

07RAM is a higher densit device and achieves higher 9andwidth due to the further

increase of the cloc" rate and reduction in &ower consum&tion 9enefiting from 1.5V

&ower su&&l at 90 nm fa9rication technolog. <ith 8 individual 9an"s, 77R* memor

is more fle?i9le to 9e accessed with fewer 9an" conflicts.

The &ro&osed 2ash(4AM 9ased loo" u& circuit is shown in 8igure +.

FIG1.3@HASH CAM LOOK UP CIRCUIT

The original data and reference address information are stored in the 77R* 07RAM

loo"u& re>uest (data in&ut# for a given content is &i&elined and &rocessed 9 the 2ash

circuit to generate an address. This address value is forwarded to 77R* 07RAM

1nterface where it is translated into instructions and addresses that are recogniDed 9 the

77R* memor as an access.

The stored data ; addresses in the memor are read 9ac" to the 2ash(4AM circuit in

order to validate the match. 1n the case of corres&onding reference address is reference

address is returned.

1.3 DDR3 A<D(05(1+=

6ower &ower

2igher s&eed

Master reset

More &erformance

6arger densities

CHAPTER "

TYPES OF MEMORY CONTROLLERS

CHAPTER7"

".1 TYPES OF MEMORY CONTROLLERS

".1.1 D-B>,+ D(5( R(5+7S20)*.-0-B= <20(?3) .(0<-? ())+==

M+?-.2 (DDR1 SDRAM! )-05.-,,+.

7ou9le 7ata Rate(07RAM, or sim&l 77R+, was designed to re&lace

07RAM. 77R+ was originall referred to as 77R(07RAM or sim&le 77R.

<hen 77R- was introduced, 77R 9ecame referred to as 77R+. Names of

com&onents constantl change as newer technologies are introduced, es&eciall

when the newer technolog is 9ased on a &revious e one. The &rinci&le a&&lied in

77R is e?actl as the name im&lies Jdou9le data rateK. The 77R actuall

dou9les the rate data is transferred 9 using 9oth the rising and falling edges of a

t&ical digital &ulse. 3arlier memor technolog such as 07RAM transferred data

after one com&lete digital &ulse. 77R transfers data twice as fast 9 transferring

data on 9oth the rising and falling edges of the digital &ulse. 6oo" at figure 9elow.

FIG ".1@GRAPHICAL REPRESANTATION

".1.1DDR D3135(, PB,=+

As shown in the a9ove figure, 77R can transfer twice the amount of data &er

single digital &ulse 9 using 9oth the rising edge, and the falling edge of the

digital signal. 77R can transfer twice the data as 07RAM.

"." D-B>,+ D(5( R(5+7S20)*.-0-B= <20(?3) .(0<-? ())+==

M+?-.2 (DDR" SDRAM! )-05.-,,+.

77R- is the ne?t generation of memor develo&ed after 77R. 77R-

increased the data transfer rate referred to as 9andwidth 9 increasing the

o&erational fre>uenc to match the high 80= fre>uencies and 9 dou9ling the

&refetch 9uffer data rate. There will 9e more a9out the memor &refetch 9uffer

data rate later in this section.

77R- is a -/. &in 71MM design that o&erates at +.C volts. The lower

voltage counters the heat effect of the higher fre>uenc data transfer. 7RR

o&erates at -.) volts and is a +CC &in 71MM design. 77R- uses a different

mother9oard soc"et than 77R, and is not com&ati9le with mother9oards designed

for 77R. The 77R- 71MM "e will not align with 77R 71MM "e. 1f the

77R- is forced into the 77R soc"et, it will damage the soc"et and the memor

will 9e e?&osed to a high voltage level. Also 9e aware the 77R is +CC &in 71MM

design and 77R- is a -/. &in 71MM design.

".3 D-B>,+ D(5( R(5+7S20)*.-0-B= <20(?3) .(0<-? ())+==

M+?-.2 (DDR3 SDRAM! )-05.-,,+.

77R* was the ne?t generation memor introduced in the summer of -..,

as the natural successor to 77R-. 77R* increased the &re(fetch 9uffer siDe to C(

9its an increased the o&erating fre>uenc once again resulting in high data transfer

rates than its &redecessor 77R-. 1n addition, to the increased data transfer rate

memor chi& voltage level was lowered to +.) ' to counter the heating effects of

the high fre>uenc.

= now ou can see the trend of memor to increase &re(fetch 9uffer siDe

and chi& o&erating fre>uenc, and lowering the o&erational voltage level to

counter heat. The &hsical 77R* is also designed with -/. &ins, 9ut the notched

"e is in a different &osition to &revent the insertion into a mother9oard RAM

soc"et designed for 77R-.

77R* is 9oth electrical and &hsicall incom&ati9le with &revious

versions of RAM. 1n addition to high fre>uenc and lower a&&lied voltage level,

the 77R* has a memor reset o&tion which 77R- and 77R+ do not. The

memor reset allows the memor to 9e cleared 9 a software reset action. 5ther

memor t&es do not have this feature which means the memor state is uncertain

after a sstem re9oot. The memor reset feature insures that the memor will 9e

clean or em&t after a sstem re9oot. This feature will result in a more sta9le

memor sstem. 77R* uses the same -/.(&in design as 77R-, 9ut the memor

module "e notch is at a different location.

".4 COMPARISION OF DDR1% DDR" AND DDR3

FIG "."@COMPARISION OF DDR9S

-.) O5*+. M+?-.2 T24+= :

".8.1 &3<+- R(0<-? A))+== M+?-.2

'RAM is a video version of 8PM and is most often used in video

accelerator cards. =ecause it has two &orts, it &rovides the e?tra 9enefit over

7RAM of 9eing a9le to e?ecute simultaneous readAwrite o&erations at the same

time.

5ne channel is used to refresh the screen and the other manages image changes.

'RAM tends to 9e more e?&ensive. 'ideo RAM, also "nown as multi &ort

dnamic random access memor (MP7RAM#, is a t&e of RAM used s&ecificall

for video ada&ters or *(7 accelerators. The Lmulti &ortL &art comes from the fact

that 'RAM normall has two inde&endent access &orts instead of one, allowing

the 4PU and gra&hics &rocessor to access the RAM simultaneousl. 'RAM is

located on the gra&hics card and comes in a variet of formats, man of which are

&ro&rietar.

The amount of 'RAM is a determining factor in the resolution and color

de&th of the dis&la. 'RAM is also used to hold gra&hics(s&ecific information

such as *(7 geometr data and te?ture ma&s. True multi &ort 'RAM tends to 9e

e?&ensive, so toda, man gra&hics cards use 0$RAM (snchronous gra&hics

RAM# instead. Performance is nearl the same, 9ut 0$RAM is chea&er.

".8." F,(=* M+?-.2

This is a solid(state, nonvolatile, re(writa9le memor that functions li"e RAM and

a hard dis" com9ined. 1f &ower is lost, all data remains in memor. =ecause of its

high s&eed, dura9ilit, and low voltage re>uirements, it is ideal for digital

cameras, cell &hones, &rinters, handheld com&uters, &agers and audio recorders.

".8.3 S*(<-C R(0<-? A))+== M+?-.2

<hen our com&uter starts u& (9oots#, minimal instructions for &erforming the

startu& &rocedures and video controls are stored in R5M (Read 5nl Memor# in

the ca&a9ilit of m the ca&a9ilit of moving selected &arts of the =150 code from

R5M to the faster RAM memor.what is commonl called =150.

".8.4 S5(53) R(0<-? A))+== M+?-.2

0tatic RAM uses a com&letel different technolog. 1n static RAM, a form of fli&(

flo& holds each 9it of memor. A fli&(flo& for a memor cell ta"es four or si?

transistors along with some wiring, 9ut never has to 9e refreshed. This ma"es

static RAM significantl faster than dnamic RAM. 2owever, 9ecause it has

more &arts, a static memor cell ta"es u& a lot more s&ace on a chi& than a

dnamic memor cell. Therefore, ou get less memor &er chi&.

0tatic random access memor uses multi&le transistors, t&icall four to si?, for

each memor cell 9ut doesnMt have a ca&acitor in each cell. 1t is used &rimaril for

cache. 0o static RAM is fast and e?&ensive, and dnamic RAM is less e?&ensive

and slower. 0o static RAM is used to create the 4PUMs s&eed(sensitive cache,

while dnamic RAM forms the larger sstem RAM s&ace.

".8.8 D20(?3) R(0<-? A))+== M+?-.2

7namic random access memor has memor cells with a &aired

transistor and ca&acitor re>uiring constant refreshing. 7RAM wor"s 9 sending a

charge through the a&&ro&riate column (4A0# to activate the transistor at each 9it

in the column. <hen writing, the row lines contain the state the ca&acitor should

ta"e on. <hen reading, the sense(am&lifier determines the level of charge in

the ca&acitor. 1f it is more than ). &ercent, it reads it as a +: otherwise it reads

it as a .. The counter trac"s the refresh se>uence 9ased on which rows have 9een

accessed in what order. The length of time necessar to do all this is so short that

it is e?&ressed in nanoseconds.

A memor chi& rating of ,.ns means that it ta"es ,. nanoseconds to

com&letel read and recharge each cell. 5ne of the most common t&es of

com&uter memor (RAM#. 1t can onl hold data for a short &eriod of time and

must 9e refreshed &eriodicall. 7RAMs are measured 9 storage ca&a9ilit and

access time. 0torage is rated in mega9tes (C M=, +H M=, etc#. Access time is

rated in nanoseconds (H.ns, ,.ns, C.ns, etc# and re&resents the amount of time to

save or return information. <ith a H.ns 7RAM, it would re>uire H. 9illionths of a

second to save or return information. The lower the nano s&eed, the faster the

memor o&erates. 7RAM chi&s re>uire two 4PU wait states for each e?ecution.

4an onl e?ecute either a read or write o&eration at one time. The ca&acitor in a

dnamic RAM memor cell is li"e a lea" 9uc"et. 1t needs to 9e refreshed

&eriodicall or it will discharge to .. This refresh o&eration is where dnamic

RAM gets its name. 7namic RAM has to 9e dnamicall refreshed all of the

time or it forgets what it is holding. The downside of all of this refreshing is that it

ta"es time and slows down the memor.

Memor cells are etched onto a silicon wafer in an arra of columns (9it

lines# and rows (word lines#. The intersection of a 9it line and word line

constitutes the address of the memor cell. Memor cells alone would 9e

worthless without some wa to get information in and out of them. 0o the

memor cells have a whole su&&ort infrastructure of other s&ecialiDed circuits.

These circuits &erform functions such as:Memor is made u& of 9its arranged in a

two(dimensional grid. 1n this figure, red cells re&resent +s and white cells

re&resent .s. 1n the animation, a column is selected and then rows are charged to

write data into the s&ecific column.

1dentifing each row and column (row address select and column address

select# !ee&ing trac" of the refresh se>uence (counter# Reading and restoring the

signal from a cell (sense am&lifier# Telling a cell whether it should ta"e a charge

or not (write ena9le# 5ther functions of the memor controller include a series of

tas"s that include identifing the t&e, s&eed and amount of memor and chec"ing

for errors. The traditional RAM t&e is 7RAM (dnamic RAM#. The other t&e is

0RAM (static RAM#. 0RAM continues to remem9er its content, while 7RAM

must 9e refreshed ever few milli seconds.

7RAM consists of micro ca&acitors, while 0RAM consists of offAon

switches. Therefore, 0RAM can res&ond much faster than 7RAM. 0RAM can 9e

made with a rise time as short as / ns. 7RAM is 9 far the chea&est to 9uild.

Newer and faster 7RAM t&es are develo&ed continuousl. 4urrentl, there are at

least four t&es:

FPM (Fast Page Mode

344 (3rror 4orrecting 4ode#

375 (3?tended 7ata 5ut&ut#

07RAM (0nchronous 7namic RAM#

".8.6 C()*+ M+?-.2

4ache Memor is fast memor that serves as a 9uffer 9etween the

&rocessor and main memor. The cache holds data that was recentl used 9 the

&rocessor and saves a tri& all the wa 9ac" to slower main memor. The memor

structure of P4s is often thought of as %ust main memor, 9ut itMs reall a five or

si? level structure: The first two levels of memor are contained in the &rocessor

itself, consisting of the &rocessorMs small internal memor, or registers, and 6+

cache, which is the first level of cache, usuall contained in the &rocessor. The

third level of memor is the 6- cache, usuall contained on the mother9oard.

2owever, the 4eleron chi& from 1ntel actuall contains +-C! of 6- cache within

the form factor of the chi&. More and more chi& ma"ers are &lanning to &ut this

cache on 9oard the &rocessor itself. The 9enefit is that it will then run at the same

s&eed as the &rocessor, and cost less to &ut on the chi& than to set u& a 9us and

logic e?ternall from the &rocessor.The fourth level is 9eing referred to as 6*

cache. This cache used to 9e the 6- cache on the mother9oard, 9ut now that some

&rocessors include 6+ and 6- cache on the chi&, it 9ecomes 6* cache. Usuall, it

runs slower than the &rocessor, 9ut faster than main memor. The fifth level (or

fourth if ou have no L6* cacheL# of memor is the main memor itself. The si?th

level is a &iece of the hard dis" used 9 the 5&erating 0stem, usuall called

virtual memor. Most o&erating sstems use this when the run out of main

memor, 9ut some use it in other was as well.

This si?(tiered structure is designed to efficientl s&eed data to the

&rocessor when it needs it, and also to allow the o&erating sstem to function

when levels of main memor are low. 1f there were one t&e of su&er(fast, su&er(

chea& memor, it could theoreticall satisf the needs of this entire memor

architecture. This will &ro9a9l never ha&&en since ou donMt need ver much

cache memor to drasticall im&rove &erformance, and there will alwas 9e a

faster, more e?&ensive alternative to the current form of main memor.

".8.$ C-05+057A<<.+==(>,+ M+?-.2 (CAM!

4ontent(addressa9le memor (4AM# is a s&ecial t&e of com&uter

memor used in certain ver high s&eed searching a&&lications. 1t is also "nown

as associative memor, associative storage, or associative arra, although the last

term is more often used for a &rogramming data structure.

".8. H(.<C(.+ A==-)3(53D+ A..(2@

Unli"e standard com&uter memor (random access memor or RAM# in

which the user su&&lies a memor address and the RAM returns the data word

stored at that address, a 4AM is designed such that the user su&&lies a data word

and the 4AM searches its entire memor to see if that data word is stored

anwhere in it. 1f the data word is found, the 4AM returns a list of one or more

storage addresses where the word was found (and in some architecture, it also

returns the data word, or other associated &ieces of data#.

CHAPTER 3

D+=310 -/ DDR3SDRAM

COTROLLER

CHAPTER 3 CHAPTER 3

DESIGN OF DDR3SDRAM COTROLLER

3.1 I05.-<B)53-0@

The 77R* 07RAM uses dou9le data rate architecture to achieve high(

s&eed o&eration. The dou9le data rate architecture is Cn(&refetch architecture with

an interface designed to transfer two data words &er cloc" ccle at the 1A5 &ins. A

single read or write access for the 77R* 07RAM consists of a single Cn(9it(

wide, one(cloc"(ccle data transfer at the internal 7RAM core and eight

corres&onding n(9it(wide, one(half(cloc"ccle data transfers at the 1A5 &ins. The

differential data stro9e (7N0, 7N0O# is transmitted e?ternall, along with data,

for use in data ca&ture at the 77R* 07RAM in&ut receiver. 7N0 is center(

aligned with data for <R1T3s. The read data is transmitted 9 the 77R*

07RAM and edge(aligned to the data stro9es.

The 77R* 07RAM o&erates from a differential cloc" (4! and 4!O#. The

crossing of 4! going 21$2 and 4!O going 65< is referred to as the &ositive

edge of 4!. 4ontrol, command, and address signals are registered at ever

&ositive edge of 4!. 1n&ut data is registered on the first rising edge of 7N0 after

the <R1T3 &ream9le, and out&ut data is referenced on the first rising edge of

7N0 after the R3A7 &ream9le. Read and write accesses to the 77R* 07RAM

are 9urst(oriented. Accesses start at a selected location and continue for a

&rogrammed num9er of locations in a &rogrammed se>uence. Accesses 9egin

with the registration of an A4T1'AT3 command, which is then followed 9 a

R3A7 or <R1T3 command. The address 9its registered coincident with the

A4T1'AT3 command are used to select the 9an" and row to 9e accessed. The

address

9its registered coincident with the R3A7 or <R1T3 commands are used to select

the 9an" and the starting column location for the 9urst access. 77R* 07RAM use

R3A7 and <R1T3 =6C and =4/. An auto &recharge function ma 9e ena9led to

&rovide a self(timed row &recharge that is initiated at the end of the 9urst access.

As with standard 77R 07RAM, the &i&elined, multi9an" architecture of

77R* 07RAM allows for concurrent o&eration, there9 &roviding high

9andwidth 9 hiding row &recharge and activation time. A self refresh mode is

&rovided, along with a &ower(saving, &ower(down mode.

3." FB0)53-0(, B,-)A D3(1.(?

F31. 3.1FUNCTIONAL BLOCK DIAGRAM

The functional 9loc" diagram of the 77R* controller is shown in 8igure

*.+. The architecture of 77R*07RAM controller consists of 1nitialiDation fsm

4ommand fsm, data &ath , 9an" control ,cloc" counter, refresh counter, Address

8185, command 8185 ,<data 8185 and REdata reg .

1nitialiDation fsm generates &ro&er i(0tate to initialiDe the modules in the

design. 4ommand fsm generates c(0tate to &erform the normal write, read and

fast write, read o&erations. The data &ath module &erforms the data latching and

dis&atching of the data 9etween 2ash 4AM unit and 77R*07RAM 9an"s. The

Address 8185 gives the address to the 4ommand fsm so the 9an" control unit can

o&en &articular 9an" and address location in that 9an". The <data 8185 &rovides

the data to the data &ath module in normal and fast write o&eration. The REdata

reg gets the data from the data &ath module normal and fast read o&eration.

1n this &ro%ect the designed 77R* controller &rovides interface to the

2A02 4AM circuit and the 77R Memor =an"s. 1f the data word is found, the

4AM returns a list of one or more storage addresses where the word was found

(and in some architecture, it also returns the data word, or other associated &ieces

of data#. =ecause a 4AM is designed to search its entire memor in a single

o&eration, it is much faster than RAM in virtuall all search a&&lications.

The 77R* controller gets the address, data and control from the 2A02

4AM circuit in to the Address fifo. <rite data fifo and control fifo res&ectivel.

3.".1 A<<.+== /3/-

77R* 07RAM controller gets the address from the Address fifo so that

controller can &erform the read from the memor or write in to the memor

address location s&ecified 9 the Address fifo. 2ere the Address fifo width is +*

9it and stac" de&th is C

3."." W.35+ <(5( /3/-

77R* 07RAM controller gets the data from the <rite data fifo in write

o&eration in to the memor address location s&ecified 9 the Address fifo. 2ere

the Address fifo width is H/ 9it and stac" de&th is C.

3.".3 C-05.-, /3/-

77R* 07RAM controller gets the command from the 4ontrol fifo

controller can &erform the read from the memor or write in to the memor

address location s&ecified 9 the Address fifo. 2ere the 4ontrol fifo width is - 9it

and stac" de&th is C. 1f the control fifo gives the J.+K 77R* controller &erforms

the Normal read o&eration. 1f the control is

J+.K 77R* controller &erforms the Normal read o&eration and if control is J++K

77R* controller &erforms the 8ast read o&eration.

3.".4 R+(< D(5( R+13=5+.

<hen 77R* controller &erforms Normal read or 8ast read o&eration Read

data register gets the data send to the 2ash 4am circuit.

INITIAL FSM STATE DIAGRAM@

F31. 3."@ INITIAL FSM STATE DIAGRAM

=efore normal memor accesses can 9e &erformed, 77R* needs to 9e

initialiDed 9 a se>uence of commands. The 1N1TE80M state machine handles

this initialiDation. 8igure *.- shows the state diagram of the 1N1TE80M state

machine. 7uring reset, the 1N1TE80M is forced to the iE1763 state. After reset,

the ssEdlE-..U0 signal will 9e sam&led to determine if the -..Ps &owerAcloc"

sta9iliDation dela is com&leted. After the &owerAcloc" sta9iliDation is com&lete,

the 77R initialiDation se>uence will 9egin and the 1N1TE80M will switch from

iE1763 to iEN5P state and in the ne?t cloc" to 1EPR3.

The initialiDation starts with the PR342AR$3 A66 command. Ne?t a

65A7 M573 R3$10T3R command will 9e a&&lied for the 3?tended mode

register to ena9le the 766 inside 77R, followed 9 another 65A7 M573

R3$10T3R command to the mode register to reset the 766. Then a PR342A$3

command will 9e a&&lied to ma"e all 9an"s in the device to idle state. Then two,

AUT5 R38R302 commands, and then the 65A7 M573 R3$10T3R command

to configure 77R to a s&ecific mode of o&eration. After issuing the 65A7

M573 R3$10T3R command and the tMR7 timing dela is satisfied, 1N1TE80M

goes to iEread state and remains there for the normal memor access ccles

unless reset is asserted. Also, signal ssEinitEdone is set to high to indicate the

77R initialiDation is com&leted. The iEPR3, iEAR+, iEAR-, iE3MR0 and iEMR0

states are used for issuing 77R commands. The 65A7 M573 R3$10T3R

command configures the 77R 9 loading data into the mode register through the

address 9us. The data &resent on the address 9us (ddrEadd# during the 65A7

M573 R3$10T3R command is loaded to the mode register. The mode register

contents s&ecif the 9urst length, 9urst t&e, 4A0 latenc, etc. A

PR342AR$3AAUT5 PR342AR$3 command moves all 9an"s to idle state. As

long as all 9an"s of the 77R are in idle state, mode register can 9e reloaded with

different value there9 changing the mode of o&eration. 2owever, in most

a&&lications the mode register value will not 9e changed after initialiDation. This

design assumes the mode register stas the same after initialiDation.

As mentioned a9ove, certain timing delas (tRP, tR84, tMR7# need to 9e

satisfied 9efore another non(N5P command can 9e issued. These 07RAM delas

var from s&eed grade to s&eed grade and sometimes from vendor to vendor. To

accommodate this without sacrificing &erformance, the designer needs to modif

the 276 code for the s&ecific delas and cloc" &eriod (t4!#. According to these

timing values, the num9er of cloc"s the state machine will sta at iEtRP, iEtR84+,

iEtR84-, iEtMR7 states will 9e determined after the code is snthesiDed. 1n cases

where t4! is larger than the timing dela, the state machine doesn@t need to

switch to the timing dela states and can go directl to the command states. The

dashed lines in 8igure *.* show the &ossi9le state switching &aths.

3.3 D3//+.+05 =5(5+= -/ I0353(, FSM@

3.3.1 I<,+@

<hen reset is a&&lied the initial fsm is forced to 1763 state irres&ective of

which state it is actuall in when sstem is in idle it remains idle without

&erforming an o&erations.

3.3." N- O4+.(53-0 (NOP!@

The N5 5P3RAT15N (N5P# command is used to instruct the selected

77R 07RAM to &erform a N5P (40O is 65< with RA0O, 4A0O, and <3O are

21$2#. This &revents unwanted commands from 9eing registered during idle or

wait states. 5&erations alread in &rogress are not affected.

3.3.3 P.+)*(.1+ (PRE!@

The PR342AR$3 command is used to deactivate the o&en row in a

&articular 9an" or the o&en row in all 9an"s as shown in 8igure *.*. The value on

the =A., =A+ in&uts selects the 9an", and the A+. in&ut selects whether a single

9an" is &recharged or whether all 9an"s are &recharged.

F31. 3.3@ P.+ )*(.1+ C-??(0<

3.3.4 AB5- R+/.+=* (AR!@

AUT5 R38R302 is used during normal o&eration of the 77R 07RAM

and is analogous to 4A0O(9efore(RA0O (4=R# refresh in 7RAMs. This

command is non&ersistent, so it must 9e issued each time a refresh is re>uired. All

9an"s must 9e idle 9efore an AUT5 R38R302 command is issued.

3.3.8 L-(< M-<+ R+13=5+. (LMR!@

The mode registers are loaded via in&uts A.QAn. The 65A7 M573

R3$10T3R command can onl 9e issued when all 9an"s are idle, and a

su9se>uent e?ecuta9le command cannot 9e issued until tMR7 is met.

3.3.6 R+(<;W.35+ C2),+@

The 8igure /.+ shows the state diagram of 4M7E80M which handles the

read, write and refresh of the 07RAM. The 4M7E80M state machine is

initialiDed to cEidle during reset. After reset, 4M7E80M stas in cEidle as long as

ssE1N1TE75N3 is low which indicates the 07RAM initialiDation se>uence is

not et com&leted.5nce the initialiDation is done, ssEA70n and ssER38ER3N

will 9e sam&led at the rising edge of ever cloc" ccle. A logic high sam&led on

ssER38ER3N will start a 07RAM refresh ccle. This is descri9ed in the

following section. 1f logic low is sam&led on 9oth ssER38ER3N and ssEA70n,

a sstem read ccle or sstem write ccle will 9egin. These sstem ccles are

made u& of a se>uence of 07RAM commands

3.3.$ COMMAND FSM STATE DIAGRAM@

F31. 3.4@ COMMAND FSM STATE DIAGRAM FOR NORMAL WRITE

AND READ

The figure /.+ shows the state diagram of 4M7E80M, which handles

read, write and refresh of the 77R. The 4M7E80M state machine is initialiDed to

cEidle during reset. After reset, 4M7E80M stas in cEidle as long as

ssEinitEdone is low which indicates the 77R initialiDation se>uence is not et

com&leted. 8rom this state, a R3A7AA<R1T3AAR38R302 ccle starts

de&ending u&on ssEadsnArdEwrEre>EduringErefEre> signals as shown in the state

diagram.

All rows are in the JclosedK status after the 77R initialiDation. The rows

need to 9e Jo&enedK 9efore the can 9e accessed. 2owever, onl one row in the

same 9an" can 9e o&ened at a time. 0ince there are four 9an"s, there can 9e at

most four rows o&ened at the same time. 1f a row in one 9an" is currentl o&ened,

it needs to 9e closed 9efore another row in the same 9an" can 9e o&ened.

A4T1'3 command is used to o&en the rows and PR342AR$3 (or the AUT5

PR342AR$3 hidden in the <R1T3 and R3A7 commands as used in this

design# is used to close the rows. <hen issuing the commands for o&ening or

closing the rows, 9oth row address and 9an" address need to 9e &rovided.

1n this design, the A4T1'3 command will 9e issued for each read or write

access to o&en the row. After a tR47 dela is satisfied, R3A7A or <R1T3A

commands will 9e issued with a high ddrEaddR+.S to ena9le the AUT5

R38R302 for closing the row after access. Therefore, the cloc"s re>uired for

readAwrite ccle are fi?ed and the access can 9e random over the full address

range. Read or write is determined 9 the ssErEwn status sam&led at the rising

edge of the cloc" 9efore the tR47 dela is satisfied. 1f logic high is sam&led, the

state machine switches to cER3A7A. 1f a logic low is sam&led, the state machine

switches to cE<R1T3A.

8or read ccles, the state machine switches from, cER3A7A to cEcl for

4A0 latenc, then switches to crate for transferring data from 77R to &rocessor.

The 9urst length determines the num9er of cloc"s the state machine stas in

cErdata state. After the data is transferred, it switches 9ac" to cEidle.

8or write ccles, the state machine switches from cE<R1T3A to cEwdata

for transferring data from 9us master to 77R, then switches to cEt7A6. 0imilar

to read, the num9er of cloc"s the state machine stas in cEwdata state is

determined 9 the 9urst length. The time dela t7A6 is the sum of <R1T3

recover time t<R and the AUT5 PR342AR$3 timing dela tRP. After the

cloc" rising edge of the last data in the 9urst se>uence, no commands other than

N5P can 9e issued to 77R 9efore t7A6 is satisfied.

The dashed lines indicate &ossi9le state switching &aths when the t4!

&eriod is larger than the timing dela s&ecification.

C-??(0< FSM C35* /(=5 .+(< -4+.(53-0@

8ast read can 9e achieved 9 switching 9an"s. =an" control logic is used

to issue desired 9an" addresses at each ccle when a 9an" active command or

read command is issued. The state machine for this method is given in 8igure

/(9#. The &ro&osed controller &rovides the control interface for switching 9etween

normal writeAread mode and fast read mode. Unli"e other data &rocessing

techni>ues, the distinct characteristic of the random data loo"u& is the uncertaint

of the incoming data. 1n this wor", address 8185s are a&&lied to 9uffer the

rowAcolumn addresses se&aratel for each read re>uest. The Jem&tK flag of the

row address 8185 (addr!fifo!empt"# is chec"ed in order to evaluate whether the

ne?t command is active (#$%# or read (&'##

COMMAND FSM

FIG 3.8 COMMAND FSM FAST READ WITH AUTO PRECHARGE

CHAPTER 4

DIFFERENT STATES OF

COMMAND FSM

CHAPTER74

4.1 DIFFERENT STATES OF COMMAND FSM

4.1.1 R+/.+=* C2),+@

77R memor needs a &eriodic refresh to hold the data. This &eriodic

refresh is done using AUT5 R38R302 command. All 9an"s must 9e idle 9efore

an AUT5 R38R302 command is issued. 1n this design all 9an"s will 9e in idle

state, as ever readAwrite o&eration uses auto &re charge.

4.1." A)53D+ (ACT!@

The A4T1'3 command is used to o&en (or activate# a row in a &articular

9an" for a su9se>uent access, li"e a read or a write, as shown in 8igure /.-. The

value on the =A., =A+ in&uts selects the 9an", and the address &rovided on

in&uts A.QAn selects the row.

F31. 4.1@ A)53D(5301 ( S4+)3/3) R-C 30 ( S4+)3/3) B(0A.

4.1.3 R+(<@

The R3A7 command is used to initiate a 9urst read access to an active

row, as shown in 8igure /.*. The value on the =A., =A+ in&uts selects the 9an",

and the address &rovided on in&uts A.QAi (where Ai is the most significant

column address 9it for a given densit and configuration# selects the starting

column location.

F31. 4."@ R+(< C-??(0<

4.1.4 W.35+@

The <R1T3 command is used to initiate a 9urst write access to an active

row as shown in 8igure /./. The value on the =A., =A+ in&uts selects the 9an",

and the address &rovided on in&uts A.QAi (where Ai is the most significant

column address 9it for a given densit and configuration# selects the starting

column location.

F31. 4.3@ W.35+ C-??(0<

0imilar to the 8P and 375 7RAM, row address and column address are

re>uired to &in&oint the memor cell location of the 07RAM access. 0ince

07RAM is com&osed of four 9an"s, 9an" address needs to 9e &rovided as well.

The 07RAM can 9e considered as a four 9 N arra of rows. All rows are

in the JclosedK status after the 07RAM initialiDation. The rows need to 9e

Jo&enedK 9efore the can 9e accessed. 2owever, onl one row in the same 9an"

can 9e o&ened at a time. 0ince there are four 9an"s, there can 9e at most four rows

o&ened at the same time. 1f a row in one 9an" is currentl o&ened, it must 9e

closed 9efore another row in the same 9an" can 9e o&ened.A4T1'3 command is

used to o&en the rows and PR342AR$3 (or the AUT5 PR342AR$3 hidden in

the <R1T3 and R3A7 commands, as used in this design# is used to close the

rows. <hen issuing the commands for o&ening or closing the rows, 9oth row

address and 9an" address need to 9e &rovided.

8or se>uential access a&&lications and those with &age memor

management, the &ro&er address assignments and the use of the 07RAM &i&eline

feature deliver the highest &erformance 07RAM controller. 2owever, this t&e of

controller design is highl associated with the 9us master ccle s&ecification and

will not fit the general a&&lications.Therefore, this 07RAM controller design does

not im&lement these custom features to achieve the highest &erformance through

these techni>ues.

1n this design, the A4T1'3 command will 9e issued for each read or write

access to o&en the row. After a tR47 dela is satisfied, R3A7 or <R1T3

commands will 9e issued with a high sdrEAR+.S to ena9le the AUT5 R38R302

for closing the row after access. 0o, the cloc"s re>uired for readAwrite ccle are

fi?ed and the access can 9e random over the full address range.

Read or write is determined 9 the ssERE<n status sam&led at the rising

edge of the cloc" 9efore tR47 dela is satisfied. 1f a logic high is sam&led, the

state machine switches to cER3A7A. 1f a logic low is sam&led, the state

machine switches to cE<R1T3A.

8or read ccles, the state machine switches from cER3A7A to cEcl for

4A0 latenc, then switches to cErdata for transferring data from 07RAM to 9us

master. The num9er of cloc"s the state machine stas in cErdata state is

determined 9 the 9urst length. After the data is transferred, it switches 9ac" to

cEidle.

8or write ccles, the state machine switches from cE<R1T3A to cEwdata

for transferring data from 9us master to 07RAM, then switches to cEt7A6.

0imilar to read, the num9er of cloc"s the state machine stas in cEwdata state is

determined 9 the 9urst length. The time dela t7A6 is the sum of <R1T3

recover time t<R and the AUT5 PR342AR$3 timing dela tRP. After the

cloc" rising edge of the last data in the 9urst se>uence, no commands otherthan

N5P can 9e issued to 07RAM 9efore t7A6 is satisfied.

As mentioned in the 1N1TE80M section a9ove, the dash lines indicates

&ossi9le state switching &aths when t4! &eriod is larger than timing dela s&ec.

4.1.8 R+/.+=* C2),+@

0imilar to the other 7RAMs, memor refresh is re>uired. A 07RAM

refresh re>uest is generated 9 activating sdrER38ER3N signal of the controller.

The sdrER38EA4! signal will ac"nowledge the recognition of sdrER38ER3N

and will 9e active throughout the whole refresh ccle. The sdrER38ER3N signal

must 9e maintained until the sdrER38EA4! goes active in order to 9e recogniDed

as a refresh ccle. Note that no sstem readAwrite access ccles are allowed when

sdrER38EA4! is active. All sstem interface ccles will 9e ignored during this

&eriod. The sdrER38ER3N signal assertion needs to 9e removed u&on recei&t of

sdrER38EA4! ac"nowledge,otherwise another refresh ccle will again 9e

&erformed.U&on recei&t of sdrER38ER3N assertion, the state machine

4M7E80M enters the cEAR state to issue an AUT5 R38R302 command to the

07RAM. After tR84 time dela is satisfied, 4M7E80M returns to idle.

4.1.6. D(5( P(5* C-05.-,

7ata &ath module &erforms the data latching and dis&atching 9ased on the

command fsm states. 1t &rovides interface 9etween the Read data register and the

memor 9an"s

4.1.$. B(0A )-05.-,

The 9an" control controls the all the eight 9an"s effectivel de&ending

u&on the istate and cstate 9 sending the re>uired control signals.

4.1. T3?301 D3(1.(?=@

The figures /.) and /.H are the read ccle and write ccle timing diagrams

of the reference design with the two 4A0 latenc ccles and the 9urst length of

four. The timing diagrams ma 9e different due to the values of the timing delas

tMR7AtRPAtR84AtR47AtR47At<R, the cloc" &eriod t4!, the 4A0 latenc and

the 9urst length. The total num9er of cloc"s for read and write ccles are decided

9 these factors. 1n the e?am&le shown in the figures, the read ccle ta"es +.

cloc"s and the write ccle ta"es G cloc"s.

The state varia9le cE0tate of 4M7E80M is also shown in these figures.

Note that the A4T1'3, R3A7, <R1T3 commands are asserted one cloc" after

the cEA4T1'3, cER3A7A, cE<R1T3A states res&ectivel.

The values of the region filed with slashes in the sstem interface in&ut

signals of these figures are Jdon@t care.K 8or e?am&le, signal ssERE<n needs to

9e valid onl at the cloc" 9efore 4M7E80M switches to the cER3A7A or

cE<R1T3A states. 7e&ending on the values of tR47 and t4!, this means tsignal

ssERE<n needs to 9e valid at state cEA4T1'3 or the last cloc" of state cEtR47.

/G

F31. 4.4@ R+(< C2),+ T3?301 D3(1.(?.

F31. 4.8@ W.35+ C2),+ T3?301 D3(1.(?.

).

4." AD&ANTAGES

+. 2igher 9andwidth &erformance increase, effectivel u& to -/..M2D.

-. Performance increase at low &ower (longer 9atter life in la&to&s#.

*. 3nhanced low &ower features with im&roved thermal design (cooler#.

/. 4om&ared w+th 77R07RAM the voltage of 77R* 07RAM was

lowered from -.)' to +.)'. This im&roves &ower consum&tion and heat

generation, as well as ena9ling more dense memor configurations for higher

ca&acities

). 77R* 07RAM achieves nearl twice the 9andwidth of the &receding

single data rate 77R- 07RAM 9 dou9le &um&ing (transferring data on the

rising and falling edges of the cloc" signal# without increasing the cloc"

fre>uenc.

H. 77R 07RAM is a &articularl e?&ensive alternative to 77R* 07RAM,

and most manufacturers have dro&&ed its su&&ort from their chi&sets.

,. 4A0 latenc is less com&ared to 77R07RAM.

C. 07RAM can acce&t one command and transfer one word of data &er cloc"

ccle. T&ical cloc" fre>uencies are ). and +** M2D.Tddr two commands n

su&&orts u&to-..MhDU.

G. 6ow &ower consum&tion.

+.. 6ow manufacturing cost.

++. 6ow(voltage, +.)' 77R* reduced chi& count &rovides significant &ower

savings.

)+

4.3 DISAD&ANTAGES@

4ommonl higher 4A0 6atenc 9ut com&ensated 9 higher 9andwidth,

there9 increasing overall &erformance under s&ecific a&&lications generall costs

much more than e>uivalent 77R- memor.

)-

CHAPTER 8

RESULTS

)*

CHAPTER 8 CHAPTER 8

RESULTS

8.1SIMULATION RESULTS@

TOP MODULE OUTPUT

)/

8.1.1 A<<.+== /3/-

))

8.1." C-05.-, /3/-

8.1.3 W.35+ <(5( /3/-@

)H

8.1.4 I0353(,3E(53-0 FSM

8.1.8 C-??(0< FSM

8.1.8.1 N-.?(, W.35+ -4+.(53-0

),

8.1.8." N-.?(, R+(< -4+.(53-0

8.1.8.3 F(=5 R+(< -4+.(53-0

)C

8.1.6 D(5( 4(5* )-05.-,

8.1.$ T-4 ?-<B,+

8.1.$.1 N-.?(, W.35+ -4+.(53-0 ((!

)G

8.1.$." N-.?(, R+(< -4+.(53-0 ((!

8.1.$.3 F(=5 R+(< -4+.(53-0 ((!

H.

CHAPTER 6

CONCLUSION AND FUTURE

SCOPE

H+

CHAPTER 6 CHAPTER 6

CONCLUSION AND FUTURESCOPE

6.1 CONCLUSION@

1n this &ro%ect we have designed a 2igh s&eed 77R* 07RAM 4ontroller

with H/(9it data transfer which snchroniDes the transfer of data 9etween 77R

RAM and 3?ternal &eri&heral devices li"e host com&uter, la&to&s and so on. The

advantages of this controller com&ared to 07R 07RAM , 77R+ 07RAM and

77R- 07RAM is that it snchroniDes the data transfer, and the data transfer is

twice as fast as &revious, the &roduction cost is also ver low.

H-

6." FUTURE SCOPE

+. 77R/ 07RAM is the /th generation of 77R 07RAM.

-. 77R* 07RAM im&roves on 77R 07RAM 9 using differential

signaling and lower voltages to su&&ort significant &erformance advantages over

77R 07RAM.

*. 77R* 07RAM standards are still 9eing develo&ed and im&roved.

77R 07RAM 0tandard 8re>uenc (M2D# 'oltage

77R /..()** -.)

77R- HH,(C.. +.C

77R* +.HH to ... +.)

/. 2igher fre>uencies ena9le higher rates of data transfer.

). 77R* 07RAM (7ou9le 7ata Rate Three 0nchronous 7namic Random

Access Memor# is the third generation of 77R 07RAM.

H. Reduced &ower consum&tion due to G.mm fa9rication technolog.

,. Pre(fetch 9uffer is dou9led to C 9its to further increase &erformance.

.

H*

CHAPTER $

REFRENCES

CHAPTER $ CHAPTER $

REFERENCES

H/

+. A. J. McAule, et al, J8ast Routing Ta9le 6oo"u& Using 4AMsK, Pro(eedings

on 1)th #nnual *oint $onferen(e of the +,,, $omputer and $ommuni(ations

So(ieties (+-F.$.M, 'ol.*, March +GG*, &&.+*C- Q +*G+.

-. F. Bang, et al, J2igh Performance 1P 6oo"u& 4ircuit Using 77R 07RAMK,

+,,, +nternational S.$ $onferen(e (S.$$/ 0e&t. -..C, &&. *,+(*,/.

*. $. Allan, JThe 6oveA2ate Relationshi& with 77R 07RAM 4ontrollersK,

M.S#+' %e(hnologies 0hitepaper, -..H.

/. 2. !im, et al, J2igh(Performance and 6ow(Power Memor( 1nterface

Architecture for 'ideo Processing A&&licationK, +,,, %ransa(tions on $ir(uit

and S"stems for Video %e(hnolog", 'ol. ++, Nov. -..+, &&. ++H.(++,..

). 3. $. T. Jas&ers, et al, J=andwidth Reduction for 'ideo Processing in

4onsumer 0stemsK, 1333 Transactions on 4onsumer 3lectronics, 'ol. /,, No. /,

Nov. -..+, &&. CC)( CG/.

H. N. Vhang, et al, J2igh Performance and 2igh 3fficienc Memor Management

0stem for 2.-H/AA'4 A&&lication in the 7ual(4ore PlatformK, +$#S,, 5ct.

-..H, &&. ),+G(),--.

,. J. Vhu, et al, JK2igh Performance 0nchronous 7RAMs 4ontroller in 2. -H/

27T' 7ecoderK, Proceedings of 1nternational 4onference on 0olid(0tate and

1ntegrated 4ircuts Technolog, 'ol. *, 5ct. -../, &&. +H-+(+H-/.

C. J2igh(Performance 77R* 07RAM 1nterface in 'irte?() 7evicesK, 1ilin2/

1#PP834 (51.0, 0e&t -/, -..,.

G. T. Mladenov, J=andwidth, Area 3fficient and Target 7evice 1nde&endent 77R

07RAM 4ontrollerK, Proceedings of <orld Academ of 0cience, 3ngineering

and Technolog, 'ol. +C, 7e. -..H, &&. +.-(+.H.

+.. 77R* 07RAM 0&ecification (J307,G(*A#, *,',$ Standard, *,',$ Solid

State %e(hnolog" #sso(iation, 0e&t. -..,.

H)

++. www.altera.comAliteratureAugAugEaltmem&h.&df, 3?ternal 77R Memor

P2B 1nterface Megafunction User $uide (A6TM3MP2B# accessed on -* 8e9.

-..G.

HH

CHAPTER

APPENDI'

CHAPTER

H,

APPENDI'

&ERILOG HDL

8.1 Overview

2ardware descri&tion languages, such as 'erilog , differ from software

&rogramming languages 9ecause the include was of descri9ing the &ro&agation

of time and signal de&endencies (sensitivit#. There are two assignment o&erators,

a 9loc"ing assignment (W#, and a non(9loc"ing (XW# assignment. The non(

9loc"ing assignment allows designers to descri9e a state(machine u&date without

needing to declare and use tem&orar storage varia9les. 0ince these conce&ts are

&art of the 'erilog language semantics, designers could >uic"l write descri&tions

of large circuits, in a relativel com&act and concise form. At the time of 'erilog

introduction (+GC/#, 'erilog re&resented a tremendous &roductivit im&rovement

for circuit designers who were alread using gra&hical schematic(ca&ture, and

s&eciall(written software &rograms to document and simulate electronic circuits.

The designers of 'erilog wanted a language with snta? similar to the 4

&rogramming language, which was alread widel used in engineering software

develo&ment. 'erilog is case(sensitive, has a 9asic &re&rocessor (though less

so&histicated than AN01 4A4YY#, and e>uivalent control flow "ewords (ifAelse,

for, while, case, etc.#, and com&ati9le language o&erators &recedence. 0ntactic

differences include varia9le declaration ('erilog re>uires 9it(widths on netAreg

t&es#, demarcation of &rocedural(9loc"s (9eginAend instead of curl 9races TU#,

and man other minor differences.

HC

A 'erilog design consists of a hierarch of modules. Modules enca&sulate

design hierarch, and communicate with other modules through a set of declared

in&ut, out&ut, and 9idirectional &orts. 1nternall, a module can contain an

com9ination of the following: netAvaria9le declarations concurrent and se>uential

statement 9loc"s and instances of other modules. 0e>uential statements are &laced

inside a 9eginAend and e?ecuted in se>uential order within the 9loc". =ut the

9loc"s themselves are e?ecuted concurrentl, >ualifing 'erilog as a 7ataflow

language.

'erilog conce&t of MwireM consists of 9oth signal values (/(state: L+, .,

floating, undefinedL#, and strengths (strong, wea", etc.# This sstem allows

a9stract modeling of shared signal(lines, where multi&le sources drive a common

net. <hen a wire has multi&le drivers, the wireMs (reada9le# value is resolved 9 a

function of the source drivers and their strengths.

A su9set of statements in the 'erilog language is snthesiDa9le. 'erilog

modules that conform to a snthesiDa9le coding(stle, "nown as RT6 (register

transfer level#, can 9e &hsicall realiDed 9 snthesis software. 0nthesis(

software algorithmicall transforms the (a9stract# 'erilog source into a net list, a

logicall(e>uivalent descri&tion consisting onl of elementar logic &rimitives

(AN7, 5R, N5T, fli&(flo&s, etc.# that are availa9le in a s&ecific '601 technolog.

8urther mani&ulations to the net list ultimatel lead to a circuit fa9rication

9lue&rint (such as a &hoto mas"(set for an A014, or a 9it stream(file for an

8P$A#.

8.2History Beginning

'erilog was invented 9 Phil Moor9 and Pra9hu $oel during the winter

of +GC*A+GC/ at Automated 1ntegrated 7esign 0stems (later renamed to $atewa

HG

7esign Automation in +GC)# as a hardware modeling language. $atewa 7esign

Automation was later &urchased 9 4adence 7esign 0stems in +GG.. 4adence

now has full &ro&rietar rights to $atewaMs 'erilog and the 'erilog(F6

simulator logic simulators.

&+.3,-17:8

<ith the increasing success of '276 at the time, 4adence decided to

ma"e the language availa9le for o&en standardiDation. 4adence transferred

'erilog into the &u9lic domain under the 5&en 'erilog 1nternational (5'1# (now

"nown as Accellera# organiDation. 'erilog was later su9mitted to 1333 and

9ecame 1333 0tandard +*H/(+GG), commonl referred to as 'erilog(G).

1n the same time frame 4adence initiated the creation of 'erilog(A to &ut

standards su&&ort 9ehind its analog simulator 0&ectre. 'erilog(A was never

intended to 9e a standalone language and is a su9set of 'erilog(AM0 which

encom&assed 'erilog(G).

&+.3,-1 "001

3?tensions to 'erilog(G) were su9mitted 9ac" to 1333 to cover the

deficiencies that users had found in the original 'erilog standard. These

e?tensions 9ecame 1333 0tandard +*H/(-..+ "nown as 'erilog(-..+.

'erilog(-..+ is a significant u&grade from 'erilog(G). 8irst, it adds

e?&licit su&&ort for (-Ms com&lement# signed nets and varia9les. Previousl, code

authors had to &erform signed(o&erations using aw"ward 9it(level mani&ulations

(for e?am&le, the carr(out 9it of a sim&le C(9it addition re>uired an e?&licit

descri&tion of the 9oolean(alge9ra to determine its correct value.# The same

function under 'erilog(-..+ can 9e more succinctl descri9ed 9 one of the 9uilt(

in o&erators: Y, (, A, Z, [[[. A generateAend generate construct (similar to '276Ms

,.

generateAend generate# allows 'erilog(-..+ to control instance and statement

instantiation through normal decision(o&erators (caseAifAelse#. Using generateAend

generate, 'erilog(-..+ can instantiate an arra of instances, with control over the

connectivit of the individual instances. 8ile 1A5 has 9een im&roved 9 several

new sstem(tas"s. And finall, a few snta? additions were introduced to im&rove

code(reada9ilit (eg. alwas \Z, named(&arameter override, 4(stle

functionAtas"Amodule header declaration.# 'erilog(-..+ is the dominant flavor of

'erilog su&&orted 9 the ma%orit of commercial 37A software &ac"ages.

&+.3,-1 "008

Not to 9e confused with 0stem'erilog, 'erilog -..) (1333 0tandard

+*H/(-..)# consists of minor corrections, s&ec clarifications, and a few new

language features (such as the uwire "eword.# A se&arate &art of the

'erilog standard, 'erilog(AM0, attem&ts to integrate analog and mi?ed signal

modelling with traditional 'erilog.

.3 D+=310 S52,+=

'erilog, li"e an other hardware descri&tion language, &ermits a design in

either =ottom(u& or To&(down methodolog.

B-55-?7U4 D+=310

The traditional method of electronic design is 9ottom(u&. 3ach design is

&erformed at the gate(level using the standard gates (refer to the 7igital 0ection

for more details#. <ith the increasing com&le?it of new designs this a&&roach is

nearl im&ossi9le to maintain. New sstems consist of A014 or micro&rocessors

with a com&le?it of thousands of transistors.

,+

These traditional 9ottom(u& designs have to give wa to new structural,

hierarchical design methods. <ithout these new &ractices it would 9e im&ossi9le

to handle the new com&le?it.

T-47D-C0 D+=310

The desired design(stle of all designers is the to&(down one. A real to&(

down design allows earl testing, eas change of different technologies, a

structured sstem design and offers man other advantages. =ut it is ver difficult

to follow a &ure to&(down design. 7ue to this fact most designs are a mi? of 9oth

methods, im&lementing some "e elements of 9oth design stles.

F31B.+ =*-C= ( T-47D-C0 <+=310

.4 &+.3,-1 A>=5.()53-0 L+D+,=

,-

'erilog su&&orts designing at man different levels of a9straction. Three of

them are ver im&ortant:

=ehavioral level

Register(Transfer 6evel

$ate 6evel

B+*(D3-.(, ,+D+,

This level descri9es a sstem 9 concurrent algorithms (=ehavioral#. 3ach

algorithm itself is se>uential, that means it consists of a set of instructions that are

e?ecuted one after the other. 8unctions, Tas"s and Alwas 9loc"s are the main

elements. There is no regard to the structural realiDation of the design.

R+13=5+.7T.(0=/+. L+D+,

7esigns using the Register(Transfer 6evel s&ecif the characteristics of a

circuit 9 o&erations and the transfer of data 9etween the registers. An e?&licit

cloc" is used. RT6 design contains e?act timing 9ounds: o&erations are scheduled

to occur at certain times. Modern RT6 code definition is LAn code that is

snthesiDa9le is called RT6 codeL.

G(5+ L+D+,

<ithin the logic level the characteristics of a sstem are descri9ed 9

logical lin"s and their timing &ro&erties. All signals are discrete signals. The can

onl have definite logical values (].M, ]+M, ]FM, ]V]#. The usa9le o&erations are

&redefined logic &rimitives (AN7, 5R, N5T etc gates#. Using gate level

modeling might not 9e a good idea for an level of logic design. $ate level code

,*

is generated 9 tools li"e snthesis tools and this net list is used for gate level

simulation and for 9ac"end.

.8 A>-B5 &+.3,-1 HDL

7igital sstems are highl com&le?. At their most detail level, the ma

consist of millions of elements li"e transistors or logic gates. Therefore, for large

digital sstems, gate level design is dead. To avoid that, 'erilog 276 was

introduced.

'erilog 276 is a 2ardware 7escri&tion 6anguage (276#. 1t is a

language used to descri9e a digital sstem, which ma 9e a com&uter or a

com&onent of a com&uter. 5ne ma descri9e a digital sstem at several levels.

8or e?am&le, an 276 might descri9e the laout of the wires, resistors and

transistors on an 1ntegrated 4ircuit (14# chi&, i.e. the switch level. 5r, it might

descri9e the logical gates and fli&(flo&s in a digital sstem, i.e. the gate level.

An even higher level descri9es the registers and the transfers of vectors of

information 9etween registers. This is called the Register Transfer 6evel

(RT6#. 'erilog su&&orts all of these levels. 1t is ver much li"e the 4

language.

.6S(,3+05 F+(5B.+= -/ &+.3,-1@

Primitive logic gates such as AN7, 5R and NAN7 gates are 9uilt(in

into this language.

8le?i9ilit of creating a user(defined &rimitive (U7P#. 0uch a

&rimitive could either 9e a com9inational logic &rimitive or a

se>uential logic &rimitive.

,/

0witch(level modeling &rimitive gates, such as PM50 and NM50 are

also 9uilt(in into this language.

3?&licit language constructs are &rovided for s&ecifing &in(to(&in

delas, &ath delas and timing chec"s of a dela.

A design can 9e modeled in three different stles or in a mi?ed stle.

These stles are 9ehavioral stle modeled using continuous

assignments, stle(modeled using gate and module instantiations.

There are two data t&es in verilog 276, the net data t&e and register

data t&e. The net t&e re&resents a &hsical connection 9etween

structural elements while a register t&e re&resents an a9stract data

storage element.

A design can 9e of ar9itrar siDe: the language does not im&ose a limit.

+. 'erilog 276 is non(&ro&rietar and is an 1333 standard.

1t is 9oth human and machine reada9le. Thus it can 9e used as an

e?change

anguage 9etween tools and designers.

The ca&a9ilit of the 'erilog 276 language can 9e further e?tended

9 using the &rogramming language interface (P61# mechanism. P61 is

a collection of routines that allow foreign functions to access

information within a verilog module and allows for designer

interaction with the simulator.

At the 9ehavioral(level, 'erilog 276 can 9e used to descri9e a design

not onl at the RT6(level, 9ut also at the architectural(level and its

algorithmic(level 9ehavior.

At the structural(level, gate and module instantiations can 9e used.

'erilog 276 also has 9uilt(in logic functions such as ; (9it wise

AN7# ^ (9it wise 5R#.

,)

Notion of concurrenc and time can 9e e?&licitl modeled.

Powerful file read and write ca&a9ilities are &rovided

'erilog 276 can 9e used to &erform res&onse monitoring of the design

under test, that is, the values of a design under test can 9e monitored and

dis&laed. These values can also 9e com&ared with e?&ected values, and

in case of a mismatch, a re&ort message can 9e &rinted.

The language is non(deterministic under certain situations, that is, a model

ma &roduce different results on different simulators: for e?am&le, the

ordering of events on an event >ueue is not defined 9 the standard.

,H

You might also like

- Structural Drafting Structural Symbols and Conventions GeneralDocument10 pagesStructural Drafting Structural Symbols and Conventions GeneralKirti DuttNo ratings yet

- Telugu PoetsDocument4 pagesTelugu PoetsKirti DuttNo ratings yet

- Career ObjectiveDocument2 pagesCareer ObjectiveKirti DuttNo ratings yet

- Qty Sell Price Total Validity Scrip Qty Buy Price Total Qty Buyprice Total Validity Stocks Purchased VTD Sell Order VTD Buy OrderDocument1 pageQty Sell Price Total Validity Scrip Qty Buy Price Total Qty Buyprice Total Validity Stocks Purchased VTD Sell Order VTD Buy OrderKirti DuttNo ratings yet

- 1st Year 1nd Sem Timetables - DDocument5 pages1st Year 1nd Sem Timetables - DKirti DuttNo ratings yet

- VisakhapatnamDocument28 pagesVisakhapatnamKirti DuttNo ratings yet

- Common Expressions: Arc WeldingDocument3 pagesCommon Expressions: Arc WeldingKirti DuttNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Final ME Paper I IES 2010Document18 pagesFinal ME Paper I IES 2010pajadhavNo ratings yet

- Instruction Manual Series 880 CIU Plus: July 2009 Part No.: 4416.526 Rev. 6Document44 pagesInstruction Manual Series 880 CIU Plus: July 2009 Part No.: 4416.526 Rev. 6nknico100% (1)

- E2 Lab 2 8 2 InstructorDocument10 pagesE2 Lab 2 8 2 InstructorOkta WijayaNo ratings yet

- LeasesDocument9 pagesLeasesCris Joy BiabasNo ratings yet

- Ibps Po Mains Model Question Paper PDF Set 2Document92 pagesIbps Po Mains Model Question Paper PDF Set 2DHIRAJNo ratings yet

- Openness and The Market Friendly ApproachDocument27 pagesOpenness and The Market Friendly Approachmirzatouseefahmed100% (2)

- Web Bearing and Buck1ling To BS en 1993Document3 pagesWeb Bearing and Buck1ling To BS en 1993antoninoNo ratings yet

- PosdmDocument29 pagesPosdmChandraBhushan67% (3)

- 1ST Term S1 Physics-1Document33 pages1ST Term S1 Physics-1onos arereNo ratings yet

- PRANIR ProfileDocument14 pagesPRANIR ProfileManish VadanereNo ratings yet

- IDS701Document26 pagesIDS701Juan Hidalgo100% (2)

- 13 DocumentsDocument38 pages13 DocumentsPoorClaresBostonNo ratings yet

- Advances in Automobiles With Nanomaterials: A ReviewDocument7 pagesAdvances in Automobiles With Nanomaterials: A Reviewpsmonu54No ratings yet

- Aircraft Materials and Hardware: (Nuts, Studs, Screws)Document25 pagesAircraft Materials and Hardware: (Nuts, Studs, Screws)PakistaniTalent cover songsNo ratings yet