Professional Documents

Culture Documents

Sail Pratice

Uploaded by

Kulmit SahOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sail Pratice

Uploaded by

Kulmit SahCopyright:

Available Formats

moumita@marcomworld.

in

Here is the paper pattern of the SAIL MT Computer Science:

The SAIL CS paper has follows subjects:

1. Reasoning- 45marks

2. Quantitative aptitude- 35 marks

3. General awareness- 35 marks

4. English language- 35 marks

5. Technical paper- 100 marks

The duration of the exam paper is 145 Minutes.

Here are the questions:

1. Tn a packet switching network, packets are routed from source to destination along a

single path having two intermediate nodes. If the message size is 24 bytes and each packet

contains a header of 3 bytes, then the optimum packet size is

(a)4

(b)6

(c)7

(d)9

2. Suppose the round trip propagation delay for a 10 Mbps Ethernet having 48-bit jamming

signal is 46.4 micro seconds The minimum frame size is?

(a) 94

(b) 416

(c) 464

(d) 512

3. For which one of the following reasons does Internet Protocol (IP) use the time-to-live

(TTL) field in the IP datagram header?

(a) Ensure packets reach destination m4in.com.ebozavr.com within that time

(b) Discard packets that reach later than that time

(c) Prevent packets from looping indefinitely

(d) Limit the time for which a packet gets queued in intermediate routers

4. Station A uses 32 byte packets to transmit messages to Station B using a sliding window

protocol. The round trip delay between A and B is 80 milliseconds and the bottleneck

bandwidth on the path between Aand B is 128 kbps. What is the optimal window size that A

should use?

(a) 20

(b) 40

(c) 160

(d) 320

5. Two computers C1and C2 are configured as follows.

C1has IP address 203. 197.2.53 and netmask 255.255. 128.0.

C2 has IP address 203.197.75.201 and netmask 255.255.192.0.

Which one of the following statements is true?

(a) C1 and C2 both assume they are on the same network

(b) C2 assumes Cl is on same network, but C1 assumes C2 is on a different network

(c) C1 assumes C2 is on same network, but C2 assumes C1 is on a different network

(d) C1 and C2 both assume they are on different networks

6. Station A needs to send a message consisting of 9 packets to Station B using a siding

window (window size 3) and go-back-n error control strategy. All packets are ready and

immediately available for

transmission. If every 5th packet that A transmits gets lost (but no acks from B ever get lost),

then what is the number of packets that A will transmit for sending the message to B?

(a)12

(b)14

(c)16

(d)18

7. For the given connection of LANs by bridges, which one of the following choices

represents the depth first traversal of the spanning tree of bridges?

(a) B1,B5,B3,B4,B2

(b) B1,B3,B5,B2,B4

(c) B1, B5, B2, B3, B4

(d) B1,B3,B4,B5,B2

8.The micro instructions stored in the control memory of a processor have a width of 26 bits.

Each micro-instruction is divided into three fields: a micro-operation field of 13 bits, a next

address field (X), and a MUX select field (Y). There are 8 status bits in the inputs of the

MUX.

How many bits are there in the X and Y fields, and what is the size

of the control memory in number of words?

(a)10,3,1024

(b) 8, 5, 256

(c) 5, 8 , 2048

(d) 10, 3, 512

9. A hard disk with a transfer rate of 10 M bytes/second is constantly transferring data to

memory using DMA. The processor runs at 600 MHz, and takes 300 and 900 clock cycles to

initiate and complete DMA transfer respectively. If the size of the transfer is 20 Kbytes, what

is the percentage of processor time consumed for the transfer operation?

(a)5.0%

(b)1.0%

(c)0.5%

(d) 0.1%

10. A 4-stage pipeline has the stage delays as 150, 120, 160 and 140 nanoseconds

respectively. Registers that are used between the stages have a delay of 5 nanoseconds each.

Assuming constant clocking rate, the total time taken to process 1000 data items on this

pipeline will be

(a) 120.4 microseconds

(b) 160.5 microseconds

(c) 165.5 microseconds

(d) 590.0 microseconds

11. Which one of the following is true for a CPU having a single interrupt request line and a

single interrupt grant line?

(a) Neither vectored interrupt nor multiple interrupting devices are possible

(b) Vectored interrupts are not possible but multiple interrupting devices are possible

(c) Vectored interrupts and multiple interrupting devices are both possible

(d) Vectored interrupt is possible but multiple interrupting devices are not possible

12. Normally user programs are prevented from handling 110 directly by I/O instructions in

them. For CPUs having explicit I/O instructions, such I/O protection is ensured by having the

I/O instructions privileged. In a CPU with memory mapped I/O, there is no explicit I/O

instruction. Which one of the following is true for a CPU with memory mapped I/O?

(a) I/O protection is ensured by operating system routine(s)

(b)I/O protection is ensured by a hardware trap

(c) I/O protection is ensured during system configuration

(d) I/O protection is not possible

13. What is the swap space in the disk used for?

(a) Saving temporarily html pages

(b) Saving process data

(c) Storing the super-block

(d) Storing device drivers

14. Increasing the RAM of a computer typically improves performance because

(a) Virtual memory increases

(b) Larger RAMs are faster

(c) Fewer page faults occur

(d) Fewer segmentation faults occur

Solutions:

1 d

2 d

3 b

4 b

5 c

6 c

7 a

8 a

9 d

10 c

11 b

12 a

13 b

14 c

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Commodore Magazine Vol-10-N08 1989 AugDocument100 pagesCommodore Magazine Vol-10-N08 1989 AugSteven DNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- ABES IT Group of Institutions Mba-024: Operations Research MBA Semester II Model Paper Ii 2012 Max. Marks: 100 Max. Time: 3 Hours Section-ADocument4 pagesABES IT Group of Institutions Mba-024: Operations Research MBA Semester II Model Paper Ii 2012 Max. Marks: 100 Max. Time: 3 Hours Section-AKulmit SahNo ratings yet

- Paint ChemicalDocument1 pagePaint ChemicalKulmit SahNo ratings yet

- Berger Paint DescriptionDocument3 pagesBerger Paint DescriptionKulmit SahNo ratings yet

- Origin and Evolution of Nerolac PaintsDocument1 pageOrigin and Evolution of Nerolac PaintsKulmit SahNo ratings yet

- Origin and Evolution of Nerolac PaintsDocument1 pageOrigin and Evolution of Nerolac PaintsKulmit SahNo ratings yet

- Acess Remote ComputerDocument1 pageAcess Remote ComputerKulmit SahNo ratings yet

- TMT Price WB KolkataDocument1 pageTMT Price WB KolkataKulmit SahNo ratings yet

- MY PresentationDocument1 pageMY PresentationKulmit SahNo ratings yet

- Polytechnic CollegeDocument4 pagesPolytechnic CollegeKulmit SahNo ratings yet

- CollegeDocument6 pagesCollegeKulmit SahNo ratings yet

- Polytechnic CollegeDocument4 pagesPolytechnic CollegeKulmit SahNo ratings yet

- Amendments: Chapter/Section DescriptionDocument28 pagesAmendments: Chapter/Section DescriptionNarcis PatrascuNo ratings yet

- LogDocument2 pagesLogpusu2566No ratings yet

- How To Install Ubuntu On HP Envy-4 UltrabookDocument6 pagesHow To Install Ubuntu On HP Envy-4 UltrabookHarry SolorzanoNo ratings yet

- Westermo An Rockwell Remote AccessDocument20 pagesWestermo An Rockwell Remote AccessHenry RodriguezNo ratings yet

- 8251 and 8255 USARTDocument86 pages8251 and 8255 USARTmoazzam hussainNo ratings yet

- Intrucciones Flasheo nwz-b183fDocument8 pagesIntrucciones Flasheo nwz-b183fHarnold Job Romero Milla0% (1)

- Computer Science 9608Document6 pagesComputer Science 9608Krishna Seewooruttun100% (2)

- Gigabyte GA-X79-UD7 MotherboardDocument42 pagesGigabyte GA-X79-UD7 MotherboardGIGABYTE UKNo ratings yet

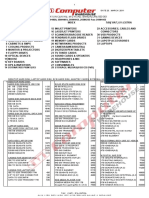

- 710, Barton Centre, M G Road, Bangalore 560 001: A.O: Against Order Tax (Vat) 5% ExtraDocument11 pages710, Barton Centre, M G Road, Bangalore 560 001: A.O: Against Order Tax (Vat) 5% ExtraAshly PaulNo ratings yet

- Lecture 1 2 Introduction To Vlsi and Embedded System PDFDocument28 pagesLecture 1 2 Introduction To Vlsi and Embedded System PDFBhaskar KNo ratings yet

- Disable Windows Driver SignatureDocument7 pagesDisable Windows Driver SignatureSatgas TarjaNo ratings yet

- 4 TUF GAMING B560M-PLUS WIFI Motherboards ASUS GlobalDocument4 pages4 TUF GAMING B560M-PLUS WIFI Motherboards ASUS GlobalPopa RafaelNo ratings yet

- Underlying Principles of Parallel and Distributed ComputingDocument118 pagesUnderlying Principles of Parallel and Distributed ComputingASWINI BNo ratings yet

- Microprocessors and Applications GuideDocument6 pagesMicroprocessors and Applications GuideRaja Dë ÇrúzèNo ratings yet

- 2nd QTR-Quiz 2 TLE 8&9Document4 pages2nd QTR-Quiz 2 TLE 8&9Ma-An FloraNo ratings yet

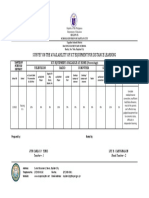

- Survey On The Availability of Ict Equipment For Distance LearningDocument1 pageSurvey On The Availability of Ict Equipment For Distance LearningRica PrologoNo ratings yet

- Familiarization With AVR Trainer Kit and Related Software: United International UniversityDocument18 pagesFamiliarization With AVR Trainer Kit and Related Software: United International UniversityNura Alam ProtikNo ratings yet

- Basic Computer Hardware NotesDocument7 pagesBasic Computer Hardware Notesk_rskNo ratings yet

- CA&ODocument12 pagesCA&OMohammad AhmedNo ratings yet

- Programmable Interval Timer Initialization and OperationDocument19 pagesProgrammable Interval Timer Initialization and OperationNaganarasaiah GoudNo ratings yet

- Phoenix BIOS Post Codes - BIOS CentralDocument9 pagesPhoenix BIOS Post Codes - BIOS CentralLito HulipasNo ratings yet

- Introduction To Freertos: What Is An Rtos?Document15 pagesIntroduction To Freertos: What Is An Rtos?عبدالله بحراويNo ratings yet

- Operating System Part 3-TestbookDocument9 pagesOperating System Part 3-TestbooksadafmirzaNo ratings yet

- Pos Terminal Pt262Document2 pagesPos Terminal Pt262sunny48137No ratings yet

- Cacheyoga Slim 7 Pro 14IAP7 82SV0053IN 230304 203744Document3 pagesCacheyoga Slim 7 Pro 14IAP7 82SV0053IN 230304 203744PruthvirajNo ratings yet

- General RTOS Concepts-PresentationDocument17 pagesGeneral RTOS Concepts-PresentationJhonnyVillarroelMendietaNo ratings yet

- OS Assignment 1Document3 pagesOS Assignment 1taz araishNo ratings yet

- CST232 Operating Systems Exam QuestionsDocument14 pagesCST232 Operating Systems Exam QuestionsjeelalalaNo ratings yet

- Computer MCQ Part 2 Student Success ChannelDocument9 pagesComputer MCQ Part 2 Student Success ChannelJarmanjit SinghNo ratings yet