Professional Documents

Culture Documents

Midterm Exam Statistics: - ADC Converters

Uploaded by

am1liOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Midterm Exam Statistics: - ADC Converters

Uploaded by

am1liCopyright:

Available Formats

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K.

Page 1

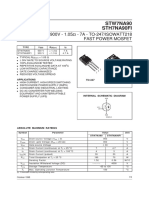

Midterm Exam Statistics

0

1

2

3

4

5

6

10 15 16 17 17.5 18

Grade

Max.=20

Number of

Occurrence

Mean=16

Standard Deviation: 2

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 2

EE247

Lecture 18

ADC Converters

Sampling (continued)

Sampling switch considerations

Switch induced distortion

Sampling switch conductance dependence on input

voltage

Clock voltage boosters

Sampling switch charge injection & clock feedthrough

Complementary switch

Use of dummy device

Bottom-plate switching

Track & hold circuits

T/H circuit incorporating gain & offset cancellation

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 3

Summary of Last Lecture

DAC Converters (continued)

Dynamic element matching

DAC reconstruction filter

ADC Converters

Sampling (continued)

Sampling switch considerations

Thermal noise due to switch resistance

Sampling switch bandwidth limitations

Switch induced distortion

Sampling switch conductance dependence on input

voltage

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 4

Practical Sampling

Summary So Far!

2

2

2

12

B

B

FS

C k T

V

( ) 1 for

in

ON o o ox DD th

DD th

W V

g g g C V V

V V

L

= =

0.72

s

R

B f C

<<

kT/C noise

Finite R

sw

limited bandwidth

g

sw

= f (V

in

) distortion

v

IN

v

OUT

C

M1

1

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 5

Switch On-Resistance

SwitchMOS operating in triode mode:

V

in

C

M1

1

V

DD

( ) ( )

( )

( )

0

1

,

2

1 1

is a function of results in distortion

What if instead of connecting G to a fixed voltage,

DS

D triode

DS

D triode ox GS TH DS

ON DS

V

ON

ox GS th ox DD th in

ON in

dI

W V

I C V V V

L R dV

R

W W

C V V C V V V

L L

R V

=

= =

a floating and fixed voltage source is connected to G & S?

Desirable to maximize on voltage of GS Minimize

ON

R

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 6

Boosted & Constant V

GS

Sampling

V

GS

=const.

OFF

ON

Increase gate overdrive voltage as

much as possible + keep V

GS

constant

Switch overdrive voltage

independent of signal level

Error due to finite R

ON

linear (to

1st order)

Lower R

on

lower time constant

Higher frequency of operation

Gate voltage V

GS

=low

Device off

Beware of signal

feedthrough due to parasitic

capacitors

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 7

Constant V

GS

Sampling

(= voltage @ the switch input terminal)

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 8

Constant V

GS

Sampling Circuit

VP1

100ns

M12

M8

M9

M6

M11

Vin

1.5V

1MHz

Chold

P

C1 C2

M1

M2

VDD=3V

M3

C3

M5

M4

P

This Example: All device sizes:10/0.35

All capacitor size: 1pF (except for Chold)

Note: Each critical switch requires a separate clock booster

Vg

Va Vb

Sampling switch & C

PB

Ref: A. Abo et al, A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter, JSSC

May 1999, pp. 599.

PB

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 9

Clock Voltage Doubler Operation

C1 C2

M1

0ff

M2

Saturation

mode

VP1

=clock

PB

VDD=03V

P

a) Startup

03V

03V 00

03V 0(3V-V

th

M2

)

Acquire

charge C1 C2

M1

Triode

M2

off

VP1

PB

VDD=3V

P

3V0

3V0

3V03V (3V-V

th

M2

)(6V-V

th

M2

)

b) Next clock transition

03V

VP1

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 10

Clock Voltage Doubler Operation

C1 C2

M1

0ff

M2

VP1

PB

VDD=3V

P

03V

03V

3V~6V

3V0

c) Next clock phase

(6V-V

th

M2

)(3V-V

th

M2

)~ 3V

M2

Triode

Acquires

charge

Both C1 & C2

charged to

VDD after one

clock cycle

Note that

bottom plate

of C1 & C2 is

either 0 or

VDD while top

plates are at

VDD or 2VDD

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 11

Clock Voltage Doubler

Simulation

C1 C2

M1

M2

VP1

Clock period: 100ns

PB

P_Boost

VDD

2VDD

0

VDD=3V

R1 R2

*R1 & R2=1GOhm

dummy resistors added for simulation only

P

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 12

Constant V

GS

Sampler: Low

Sampling switch M11

is OFF

C3 charged to ~VDD

Input voltage

source

M3

Triode

C3

M12

Triode

M4

OFF

VS1

1.5V

1MHz

Chold

1pF

~ 2 VDD

(boosted clock)

VDD

VDD

OFF M11

OFF

Device

OFF

VDD=3V

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 13

Constant V

GS

Sampler: High

C3 previously

charged to VDD

M8 & M9 are on:

C3 across G-S of M11

M11 on with constant

VGS = VDD

C3

1pF

M8

M9

M11

VS1

1.5V

1MHz

Chold

1pF

VDD

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 14

Constant V

GS

Sampling

Simulation

Input Switch V

Gate

Input Signal

Chold Signal

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 15

Boosted Clock Sampling

Complete Circuit

Ref: A. Abo et al, A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter, JSSC

May 1999, pp. 599.

Clock Multiplier

Switch

M7 & M13 for

reliability

Remaining issues:

-V

GS

constant only

for V

in

<V

out

-Nonlinearity due to

Vth dependence of

M11on body-

source voltage

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 16

Advanced Clock Boosting Technique

Ref: M. Waltari et al., "A

self-calibrated pipeline

ADC with 200MHz IF-

sampling frontend,"

ISSCC 2002, Dig.

Tech. Papers, pp. 314

Sampling

Switch

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 17

Advanced Clock Boosting Technique

clklow

Capacitors C1a & C1b charged to VDD

MS off

Hold mode

Sampling

Switch

clklow

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 18

Advanced Clock Boosting Technique

Sampling

Switch

clkhigh

Top plate of C1a & C1b connected to gate of sampling switch

Bottom plate of C1a connected to V

IN

Bottom plate of C1b connected to V

OUT

VGS & VGD of MS both @ VDD & ac signal on G of MS average of V

IN

&

V

OUT

clkhigh

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 19

Advanced Clock Boosting Technique

Gate tracks average of input and output, reduces effect of IR drop at

high frequencies

Bulk also tracks signal reduced body effect (technology used allows

connecting bulk to S)

Reported measured SFDR = 76.5dB at f

in

=200MHz

Ref: M. Waltari et al., "A

self-calibrated pipeline

ADC with 200MHz IF-

sampling frontend,"

ISSCC 2002, Dig.

Tech. Papers, pp. 314

Sampling

Switch

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 20

Constant Conductance Switch

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB

SFDR," IEEE J. Solid-State Circuits, pp. 1769-1780, Dec. 2000

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 21

Constant Conductance Switch

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB

SFDR," IEEE J. Solid-State Circuits, pp. 1769-1780, Dec. 2000

OFF

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 22

Constant Conductance Switch

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB

SFDR," IEEE J. Solid-State Circuits, pp. 1769-1780, Dec. 2000

ON

M2Constant current

constant g

ds

M1replica of M2

& same VGS

as M2

M1 also

constant g

ds

Note: Authors report requirement

of 280MHz GBW for the opamp for

12bit 50Ms/s ADC

Also, opamp common-mode

compliance for full input range

required

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 23

Switch Off-Mode Feedthrough Cancellation

Ref: M. Waltari et al., "A self-calibrated pipeline ADC with 200MHz IF-sampling frontend,"

ISSCC 2002, Dig. Techn. Papers, pp. 314

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 24

Practical Sampling

V

o

C

M1

1

R

sw

= f(V

i

) distortion

Switch charge injection & clock feedthrough

V

i

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 25

Sampling Switch Charge Injection

Switching from Track to Hold

V

i

V

O

C

s

M1

V

G

First assume V

i

is a DC voltage

When switch turns off offset voltage (V) induced on C

s

Why?

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

V

t

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 26

Sampling

Switch Charge Injection

Channel distributed RC network formed between G,S, and D

Channel to substrate junction capacitance distributed & voltage dependant

Drain/Source junction capacitors to substrate or well voltage dependant

Over-lap capacitance C

ov

= L

D

xWx C

ox

associated with G-S & G-D overlap

MOS xtor operating in triode region

Cross section view

Distributed channel resistance &

gate & junction capacitances

S

G

D

B

L

D

L

C

ov

C

ov

C

j

db

C

j

sb

C

HOLD

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 27

Switch Charge Injection

Slow Clock

Slow clockclock fall time >> device speed

During the period (t- to t

off

) current in channel discharges channel

charge acquired during the previous clock cycle into low

impedance signal source

Only source of error Clock feedthrough from C

ov

to C

s

V

G

t

V

H

V

i

V

L

V

i

+V

th

t

off

t-

Device still

conducting

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 28

Switch Clock Feedthrough

Slow Clock

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

V

t

D

C

ov

V

G

( )

( )

( ) ( )

( )

( )

ov

i t h L

ov s

ov

i t h L

s

o i

ov ov ov

o i i t h L i t h L

s s s

o i os

ov ov

os t h L

s s

C

V V V V

C C

C

V V V

C

V V V

C C C

V V V V V V 1 V V

C C C

V V 1 V

C C

where ; V V V

C C

= +

+

+

= +

= + =

= + +

= =

t-

C

s

V

O

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 29

Switch Charge Injection & Clock Feedthrough

Slow Clock- Example

( )

' 2

ov ox t h L

ov

s

ov

os t h L

s

C 0. 1f F / C 9 f F / V 0. 4V V 0

C 10 x0. 1f F /

. 1%

C 1pF

Al l owi ng 1/ 2LSB ADC resol ut i on ~ 9bi t

C

V V V 0. 4mV

C

= = = =

= = =

= <

= =

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

V

t

V

i

V

O

C

s

=1pF

M1

V

G

10/0.18

t-

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 30

Switch Charge Injection

Fast Clock

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

V

t

V

i

V

O

C

s

=1pF

M1

V

G

Fast gate voltage drop no gate voltage to establish current in channel

channel charge has no choice but to escape out towards S & D

Q

ch

mQ

ch

nQ

ch

n+m=1

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 31

For simplicity it is assumed channel charge divided equally between S & D

Source of error channel charge transfer + clock feedthrough via C

ov

to C

s

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

V

t

Switch Charge Injection & Clock Feedthrough

Fast Clock

Clock Fall-Time << Device Speed:

( )

( )

( ) ( )

( )

( )

( )

ov ch

o H L

ov s s

ox H i t h ov

H L

ov s s

o i os

ox

s

ov ox H t h

os H L

s s

C 1 Q

V V V

C C 2 C

WC L V V V C 1

V V

C C 2 C

V V 1 V

1 WC L

where

2 C

C 1 WC L V V

V V V

C 2 C

=

+

+

= + +

=

=

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 32

Switch Charge Injection & Clock Feedthrough

Fast Clock- Example

V

i

V

O

C

s

=1pF

M1

V

G

10/0.18

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

V

t

( )

( )

2

ov ox t h DD L

2

ox

s

ov ox H t h

os H L

s s

C 0. 1f F / , C 9 f F / V 0. 4V,V 1. 8V, V 0

WLC 10 x0. 18 x9 f F /

1/ 2 1. 6% ~ 5 bi t

C 1pF

C 1 WC L V V

V V V 1. 8mV 14. 6mV 16. 4mV

C 2 C

,

= = = = =

= = =

= = =

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 33

V

o

V

V

i

Switch Charge Injection & Clock Feedthrough

Slow Clock versus Fast Clock

Slow Clock

V

o

V

V

i

Fast Clock

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 34

Switch Charge Injection & Clock Feedthrough

Example-Summary

Error function of:

Clock fall time

Input voltage level

Source impedance

Sampling capacitance

Switch size

Clock fall/rise should be well-controlled & not to be faster

(sharper) than necessary

Clock fall time

V

OS

Clock fall time

1.6%

-.1%

16mV

0.4mV

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 35

Switch Charge Injection

Error Reduction

( )

( )

( ) ( )

ch

o

s

s s

ON s

ox GS t h

ox GS t h

s

o s ox H i t h

2

1Q

V

2 C

C T

R C ( not e : k

W

2

C V V

L

Consi der t he f i gure of meri t ( FOM) :

W

C V V

1 C

L

FOM 2

V C WC L V V V

FOM

L

)

=

= = =

How do we reduce the error?

Reduce switch size?

Reducing switch size increases increased distortion not a viable solution

Small and small V use minimum chanel length (mandated by technology)

For a given technology x V ~ constant

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 36

Sampling Switch Charge Injection & Clock Feedthrough

Summary

Extra charge injected onto sampling capacitor @

switch device turn-off

Channel charge injection

Clock feedthrough to C

s

via C

ov

Issues due to charge injection & clock feedthrough:

DC offset induced on hold C

Input dependant error voltage distortion

Solutions:

Complementary switch?

Addition of dummy switches?

Bottom-plate sampling?

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 37

Switch Charge Injection & Clock Feedthrough

Complementary Switch

In slow clock case if area of n & p devices widths are equal (W

n

=W

p

)

effect of overlap capacitor for n & p devices to first order cancel

(cancellation accuracy depends on matching of n & p width and overlap

length L

D

)

Since in CMOS technologies

n

~2.5

p

choice of W

n

=W

p

not optimal

from linearity perspective (W

p

>W

n

preferable)

1B

1B

V

G

t

V

H

V

i

V

L

1

1B

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 38

Switch Charge Injection

Complementary Switch

Fast Clock

In fast clock case

To 1

st

order, offset due to overlap caps

cancelled for equal device width

Input voltage dependant error worse!

1B

V

G

t

V

H

V

i

V

L

( )

( )

( )

ch n n ox n H i t h n

t h p ch p p ox p i L

ch p ch n

o

s s

o i os

n ox n p ox p

s

Q W C L V V V

V Q W C L V V

Q 1 Q

V

2 C C

V V 1 V

1 W C L W C L

2 C

=

=

= + +

+

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 39

Switch Charge Injection

Dummy Switch

V

i

V

O

C

s

t

V

H

V

i

V

L

V

G

V

GB

W

M2

=1/2W

M1

V

G

V

GB

M1

M2

M1 M1

1 ch ov

M2 M2

2 ch ov

M2 M1 2 1

1

Q Q Q

2

Q Q 2Q

1

For W W Q Q

2

+

+

= =

Q

1 Q

2

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 40

Switch Charge Injection

Dummy Switch

V

i

V

O

C

s

t

V

H

V

i

V

L

V

G

V

GB

Dummy switch same L as main switch but half W

Main device clock goes low, dummy device gate goes high dummy

switch acquires same amount of channel charge main switch needs to

lose

Effective only if exactly half of the charge stored in M1 is transferred to M2

(depends on input/output node impedance) and requires good matching

between clock fall/rise

W

M2

=1/2W

M1

V

G

V

GB

M1

M2

Q

1 Q

2

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 41

Switch Charge Injection

Dummy Switch

V

i

V

O

M1

V

G

M2

V

GB

To guarantee half of charge goes to each sidecreate the same

environment on both sides

Add capacitor equal to sampling capacitor to the other side of the switch

+ add fixed resistor to emulate input resistance of following circuit

Issues: Degrades sampling bandwidth

C

s C

s

R

W

M2

=1/2W

M1

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 42

Dummy Switch Effectiveness Test

Ref: L. A. Bienstman et al, An Eight-Channel 8 13it Microprocessor Compatible NMOS D/A

Converter with Programmable Scaling, IEEE JSSC, VOL. SC-15, NO. 6, DECEMBER 1980

Dummy switch

W=1/2W

main

As Vin is

increased Vc1-Vin

is decreased

channel charge

decreasedless

charge injection

Note large Ls

good device

area matching

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 43

Switch Charge Injection

Differential Sampling

V

i+

V

O+

V

i-

V

O-

To 1

st

order, offset terms cancel

Note gain error still about the same

Has the advantage of better immunity to

noise coupling and cancellation of even

order harmonics

Cs

Cs

( )

( )

( )

( )

o o od i i i d

o o i i

oc i c

o i 1 os1

o i 2 os2

1 2

od i d i d 1 2 i c os1 os2

V V V V V V

V V V V

V V

2 2

V V 1 V

V V 1 V

V V V V V V

2

+ +

+ +

+ +

= =

+ +

= =

= + +

= + +

+

= + + +

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 44

Avoiding Switch Charge Injection

Bottom Plate Sampling

Switches M2 opened slightly earlier compared to M1

Injected charge by the opening of M2 is constant since its DS voltage

is zero & eliminated when used differentially

Since C

s

bottom plate is already open when M1 is opened

No charge injected on C

s

1a

V

H

V

L

t

1b

V

i

V

O

M1

1b

1a

M2

Cs

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 45

Flip-Around Track & Hold

v

IN

v

OUT

C

S1A

1D

S2

2

S2A

2

S3

1D

1 S1

v

CM

Concept based on bottom-

plate sampling

1D

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 46

Flip-Around T/H-Basic Operation

1

high

v

IN

v

OUT

C

S1A

1D

S2

2

S2A

2

S3

1D

1 S1

v

CM

Charging C

1D

2

Note: Opamp has to be

stable in unity-gain

configuration

Q

1

=V

IN

xC

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 47

Flip-Around T/H-Basic Operation

2

high

v

IN

v

OUT

C

S1A

1D

S2

2

S2A

2

S3

1D

1 S1

v

CM

Holding

1D

Q

2

=V

OUT

xC

V

OUT

=V

IN

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 48

Flip-Around T/H - Timing

S1 opens earlier than S1A

No resistive path from C

bottom plate to Gnd charge

can not change

"Bottom Plate Sampling"

v

IN

v

OUT

C

S1A

1D

S2

2

S2A

2

S3

1D

1 S1

v

CM

1D

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 49

Charge Injection

At the instant of transitioning from track to hold

mode, some of the charge stored in sampling

switch S1 is dumped onto C

With "Bottom Plate Sampling", only charge

injection component due to opening of S1 and

is to first-order independent of v

IN

Only a dc offset is added. This dc offset can be

removed with a differential architecture

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 50

Flip-Around T/H

v

IN

v

OUT

C

S1A

1D

S2

2

S2A

2

S3

1D

1 S1

v

CM

Constant switch V

GS

to minimize distortion

Note: Among all switches

only S1A & S2A

experience full

input voltage swing

1D

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 51

Flip-Around T/H

S1 is chosen to be an n-channel MOSFET

Since it always switches the same voltage, its on-

resistance, R

S1

, is signal-independent (to first order)

Choosing R

S1

>> R

S1A

minimizes the non-linear

component of R = R

S1A

+ R

S1

Typically, S1A is a wide (much lower resistance than S1) &

constant V

GS

switch

In practice size of S1A is limited by the (nonlinear) S/D

capacitance that also adds distortion

If S1As resistance is negligible delay depends only on S1

resistance

S1 resistance is independent of V

IN

error due to finite

time-constant independent of V

IN

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 52

Differential Flip-Around T/H

Ref: W. Yang, et al. A 3-V 340-mW 14-b 75-Msample/s CMOS ADC With 85-dB SFDR at Nyquist Input, IEEE

JOURNAL OF SOLID-STATE CIRCUITS, VOL. 36, NO. 12, DECEMBER 2001 1931

Offset voltage associated with charge injection of S11 & S12 cancelled by differential

nature of the circuit

During input sampling phaseamp outputs shorted together

S11

S12

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 53

Differential Flip-Around T/H

Gain=1

Feedback factor=1

2

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 54

Differential Flip-Around T/H

Issues: Input Common-Mode Range

V

in-cm

=V

out_com

-V

sig_com

Amplifier needs to have large input common-mode compliance

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 55

Differential Flip-Around T/H

Issues: Input Common-Mode Range

V

in-cm

=V

out_com

-V

sig_com

Amplifier needs to have large input common-mode compliance

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 56

Input Common-Mode

Cancellation

Ref: R. Yen, et al. A MOS Switched-Capacitor Instrumentation Amplifier, IEEE JOURNAL OF

SOLID-STATE CIRCUITS, VOL. SC-17, NO. 6,, DECEMBER 1982 1008

Note: Shorting switch M3 added

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 57

Input Common-Mode Cancellation

Track mode ( high)

V

C1

=V

I1

, V

C2

=V

I2

V

o1

=V

o2

=0

Hold mode ( low)

V

o1

+V

o2

=0

V

o1

-V

o2

= -(V

I1

-V

I2

)(C

1

/(C

1

+C

3

))

Input common-mode level removed

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 58

T/H + Charge Redistribution Amplifier

Track mode: (S1, S3 on S2off)

V

C1

=V

os

V

IN

, V

C2

=0

V

o

=V

os

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 59

T/H + Charge Redistribution Amplifier

Hold Mode

Hold/amplify mode (S1, S3 off S2on)

Offset NOT cancelled, but not amplified

Input-referred offset =(C

2

/C

1

) x V

OS

, & often C

2

<C

1

2

1

2

EECS 247- Lecture 18 Nyquist Rate ADCs-Sampling 2007 H.K. Page 60

T/H & Input Difference Amplifier

Sample mode (S1, S3 on S2off)

V

C1

=V

os

V

I1

, V

C2

=0

V

o

=V

os

You might also like

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- The Art & Science of Protective Relaying - C. Russell Mason - GEDocument357 pagesThe Art & Science of Protective Relaying - C. Russell Mason - GEAasim MallickNo ratings yet

- EMC Design Guide For PCBDocument78 pagesEMC Design Guide For PCBFaruq AhmedNo ratings yet

- Analog Circuit Design Volume 2: Immersion in the Black Art of Analog DesignFrom EverandAnalog Circuit Design Volume 2: Immersion in the Black Art of Analog DesignNo ratings yet

- Desinging Analog ChipsDocument242 pagesDesinging Analog ChipsRyan Sullenberger100% (12)

- PCB DesignerDocument70 pagesPCB Designeram1liNo ratings yet

- Calculations of MV CablesDocument3 pagesCalculations of MV CablesAnonymous kdFzbQ4jfNo ratings yet

- Bandgap 2009Document27 pagesBandgap 2009jjloksNo ratings yet

- DiDocument5 pagesDiTao Quang BinhNo ratings yet

- Lecture On Basic Concept Operation and Control of HVDCDocument74 pagesLecture On Basic Concept Operation and Control of HVDCpongpum0% (1)

- NMOS FundamentalsDocument71 pagesNMOS FundamentalsManjit KaurNo ratings yet

- Irf 6775 MPBFDocument10 pagesIrf 6775 MPBFBragal GabriellNo ratings yet

- EE247 Lecture 20Document30 pagesEE247 Lecture 20maqadarNo ratings yet

- Week4 UDocument81 pagesWeek4 UUllas SinghNo ratings yet

- Small Signal Model MOSFETDocument8 pagesSmall Signal Model MOSFETRAHUL100% (1)

- CMOS Subcircuit Design and AnalysisDocument80 pagesCMOS Subcircuit Design and AnalysisashishmanyanNo ratings yet

- All About Small Signal Analysis PDFDocument12 pagesAll About Small Signal Analysis PDFSaiKanthGNo ratings yet

- Datasheet IRFZ34NDocument9 pagesDatasheet IRFZ34NcandabiNo ratings yet

- Irf 460Document7 pagesIrf 460Arif SusantoNo ratings yet

- Datasheet FDB44N25Document8 pagesDatasheet FDB44N25jalvarez_385073No ratings yet

- Irfh 5215 PBFDocument8 pagesIrfh 5215 PBFKathryn ColemanNo ratings yet

- Lecture 8 - Multistage AmplifiersDocument43 pagesLecture 8 - Multistage AmplifiersRanjan KarkiNo ratings yet

- Irf 4905 PBFDocument9 pagesIrf 4905 PBFEverton RamiresNo ratings yet

- Data Sheet IRFB42N20DDocument8 pagesData Sheet IRFB42N20DvalubaNo ratings yet

- 7N65 PDFDocument8 pages7N65 PDFboedagbageurNo ratings yet

- P 55 NF 06 FPDocument6 pagesP 55 NF 06 FPviki_gpNo ratings yet

- 55NF06 MOSFET DatasheetDocument6 pages55NF06 MOSFET DatasheetMunish KaundalNo ratings yet

- Uni-Kl Adc-Review Jan03 5782 PDFDocument33 pagesUni-Kl Adc-Review Jan03 5782 PDFMiguel BrunoNo ratings yet

- 1NK60Z PDFDocument14 pages1NK60Z PDFkimxoNo ratings yet

- Analog Fault DerivationDocument89 pagesAnalog Fault DerivationSachidananda SwarNo ratings yet

- Low Power CMOS AD ConvertersDocument53 pagesLow Power CMOS AD ConvertersguitarfridoNo ratings yet

- AN102 FETbiasingDocument10 pagesAN102 FETbiasingGaetanoCirilloNo ratings yet

- Cmos BasicDocument21 pagesCmos BasicAnkesh JaiswalNo ratings yet

- An102 - Jfet Biasing TechniquesDocument10 pagesAn102 - Jfet Biasing TechniquesDewdeAlmighty100% (1)

- 900V 7A N-Channel Power MOSFET TO-247/ISOWATT218 DatasheetDocument9 pages900V 7A N-Channel Power MOSFET TO-247/ISOWATT218 DatasheetAngel Simo MoralesNo ratings yet

- Ad 7821Document16 pagesAd 7821compilixNo ratings yet

- MOS Transistor Theory: OutlineDocument24 pagesMOS Transistor Theory: OutlineCarlos AzevedoNo ratings yet

- N-Channel MOSFET for SMPS and UPSDocument7 pagesN-Channel MOSFET for SMPS and UPSlyorhitmaNo ratings yet

- IRL540, SiHL540 Power MOSFET Product SummaryDocument9 pagesIRL540, SiHL540 Power MOSFET Product SummaryAziz AşçıNo ratings yet

- BRY39Document17 pagesBRY39tarpinoNo ratings yet

- Irf 3205 ZPBFDocument13 pagesIrf 3205 ZPBFOsman KoçakNo ratings yet

- Mosfet Irlb 8743Document9 pagesMosfet Irlb 8743Karan ArjunNo ratings yet

- 689 Track HoldDocument35 pages689 Track HoldShiva KumarNo ratings yet

- Lecture12-Small Signal Model-BJT PDFDocument12 pagesLecture12-Small Signal Model-BJT PDFKahina ZitouniNo ratings yet

- FDP 2614Document8 pagesFDP 2614HadeedAhmedSherNo ratings yet

- FQD2N60C / FQU2N60C: N-Channel Qfet MosfetDocument9 pagesFQD2N60C / FQU2N60C: N-Channel Qfet MosfetTomescu MarianNo ratings yet

- Power Mosfet THRU-HOLE (TO-254AA) IRFM460 500V, N-CHANNELDocument7 pagesPower Mosfet THRU-HOLE (TO-254AA) IRFM460 500V, N-CHANNELSim AbdeeNo ratings yet

- Unisonic Technologies Co., LTD: 8A, 650V N-Channel Power MosfetDocument8 pagesUnisonic Technologies Co., LTD: 8A, 650V N-Channel Power MosfetMarcos RangelNo ratings yet

- Al-Nahrain University College of Engineering Department of Biomedical EngineeringDocument8 pagesAl-Nahrain University College of Engineering Department of Biomedical EngineeringMêly CrêâzyGîrlNo ratings yet

- SSF 7510Document5 pagesSSF 7510luis_h_t_79No ratings yet

- Irlr2908 SMD Datasheet 1Document11 pagesIrlr2908 SMD Datasheet 1BalbalaManiukNo ratings yet

- Irf9540, Sihf9540: Vishay SiliconixDocument9 pagesIrf9540, Sihf9540: Vishay SiliconixraminakhanNo ratings yet

- Irf 730 ADocument9 pagesIrf 730 Ajose_mamani_51No ratings yet

- Microdevices: Mosfets - Metal Oxide Field Effect Transistors N MosfetDocument11 pagesMicrodevices: Mosfets - Metal Oxide Field Effect Transistors N Mosfetblue7nicoNo ratings yet

- MTP52N06V Datasheet - 2 PDFDocument7 pagesMTP52N06V Datasheet - 2 PDFLeonel ValençaNo ratings yet

- IRF830A: Smps MosfetDocument8 pagesIRF830A: Smps MosfetRICHIHOTS2No ratings yet

- Chapter 13 Small-Signal Modeling and Linear AmplificationDocument30 pagesChapter 13 Small-Signal Modeling and Linear AmplificationAbraham JyothimonNo ratings yet

- LC Mos Dual, Complete, 12-Bit/14-Bit Serial Dacs Ad7242/Ad7244Document12 pagesLC Mos Dual, Complete, 12-Bit/14-Bit Serial Dacs Ad7242/Ad7244Mohamed NabilNo ratings yet

- Vishay Siliconix SPICE Device Model Si4362BDY N-Channel 30-V (D-S) Reduced Q, Fast Switching WFETDocument3 pagesVishay Siliconix SPICE Device Model Si4362BDY N-Channel 30-V (D-S) Reduced Q, Fast Switching WFETdreyes3773No ratings yet

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument8 pagesN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datameroka2000No ratings yet

- MTP2955V Power MOSFET 12 Amps, 60 Volts: P-Channel TO-220Document8 pagesMTP2955V Power MOSFET 12 Amps, 60 Volts: P-Channel TO-220Rodrigo AlemánNo ratings yet

- Datasheet - HK 9d5n20p 421835Document7 pagesDatasheet - HK 9d5n20p 421835BoKi PoKiNo ratings yet

- Pcbdesigner PDFDocument70 pagesPcbdesigner PDFam1liNo ratings yet

- bq27520 g4Document34 pagesbq27520 g4am1liNo ratings yet

- Continuous-Time Fourier Series ProblemsDocument7 pagesContinuous-Time Fourier Series Problemsam1liNo ratings yet

- Butterworth Filter Design Solutions ExplainedDocument11 pagesButterworth Filter Design Solutions Explainedam1liNo ratings yet

- 82801eb 82801er Serial Ata ManualDocument59 pages82801eb 82801er Serial Ata Manualam1liNo ratings yet

- Feedback Example: The Inverted Pendulum: Recommended ProblemsDocument10 pagesFeedback Example: The Inverted Pendulum: Recommended Problemsam1liNo ratings yet

- HP Simple SaveDocument14 pagesHP Simple SaveWe Wan WangNo ratings yet

- Theory and Implementation of Impedance Track™ Battery Fuel-Gauging Algorithm in bq2750x FamilyDocument11 pagesTheory and Implementation of Impedance Track™ Battery Fuel-Gauging Algorithm in bq2750x Familyanon_643612655No ratings yet

- Agarwal A., Lang J. - Foundations of Analog and Digital Electronic Circuits - Supplemental Sections and Examples - 2005Document136 pagesAgarwal A., Lang J. - Foundations of Analog and Digital Electronic Circuits - Supplemental Sections and Examples - 2005შაქრო ტრუბეცკოიNo ratings yet

- SedraSmith6e Appendix GDocument4 pagesSedraSmith6e Appendix Gam1liNo ratings yet

- FSW Dat-Sw en 5214-5984-22 v0700pdfDocument32 pagesFSW Dat-Sw en 5214-5984-22 v0700pdfam1liNo ratings yet

- Features Description: LT3085 Adjustable 500ma Single Resistor Low Dropout RegulatorDocument28 pagesFeatures Description: LT3085 Adjustable 500ma Single Resistor Low Dropout Regulatoram1liNo ratings yet

- AN2799 Application Note: Measuring Mains Power Consumption With The STM32x and STPM01Document14 pagesAN2799 Application Note: Measuring Mains Power Consumption With The STM32x and STPM01am1liNo ratings yet

- Ua709 TiDocument6 pagesUa709 TiMauro Ferreira De LimaNo ratings yet

- U17518EJ1V0IF00Document3 pagesU17518EJ1V0IF00am1liNo ratings yet

- 14Document23 pages14am1liNo ratings yet

- 18 038 RSGHBHC1 S01 2TDocument12 pages18 038 RSGHBHC1 S01 2Tam1liNo ratings yet

- Yergin 1991Document4 pagesYergin 1991am1liNo ratings yet

- L21 f07Document30 pagesL21 f07am1liNo ratings yet

- HW7 f10Document2 pagesHW7 f10am1liNo ratings yet

- 2003 AllochrtDocument1 page2003 Allochrtam1liNo ratings yet

- Er100/200 & Pubpol 184/284 Energy and SocietyDocument47 pagesEr100/200 & Pubpol 184/284 Energy and Societyam1liNo ratings yet

- Fourier Transform RefDocument3 pagesFourier Transform RefcustomerxNo ratings yet

- Midterm Exam Statistics: - ADC ConvertersDocument30 pagesMidterm Exam Statistics: - ADC Convertersam1liNo ratings yet

- Filters (Continued)Document36 pagesFilters (Continued)am1liNo ratings yet