Professional Documents

Culture Documents

Features Product Summary: Led Buck Regulator Control Ic

Uploaded by

Jess AJOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Features Product Summary: Led Buck Regulator Control Ic

Uploaded by

Jess AJCopyright:

Available Formats

www.irf.

com 2010 International Rectifier

September 8, 2010

Datasheet No PD97524

IRS254(01,11)

LED BUCK REGULATOR CONTROL IC

Features

200 V (IRS25401) and 600 V (IRS25411) half

bridge driver

Micropower startup (<500 A)

2% voltage reference

140 ns deadtime

15.6 V zener clamp on V

CC

Frequency up to 500 kHz

Auto restart, non-latched shutdown

PWM dimmable

Small 8-Lead DIP/8-Lead SOIC packages

Typical Applications

LED drivers for lamp replacement

LED driver back end current regulator

Product Summary

Topology Buck

V

OFFSET

200V,600V

V

OUT

VCC

I

o+

& I

o-

(typical) 0.5A/0.7A

t

ON

& t

OFF

(typical)

50/30nS

Deadtime (typical) 140nS

Packages

8-Lead PDIP 8-LeadSOIC

IRS254(01,11)PbF IRS254(01,11)SPbF

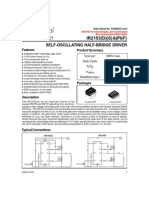

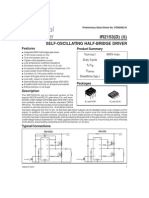

Typical Connection Diagram

1

2

3

4

8

7

6

5

I

R

S

2

5

4

0

1

VCC

IFB

LO

VS

HO

VB

COM

M1

M2

CBOOT

DBOOT

RCS

RF

CF

RS1

CVCC1

CVCC2

ROV1

ROV2

CEN

DOV

DEN1

L1

EN

COM

VBUS

COUT

RG1

RG2

VOUT+

VOUT-

IC1

CBUS2

RS2

DCLAMP

CBUS1

L2

ENN

ROUT

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

2

Table of Contents Page

Description 3

Qualification Information 5

Absolute Maximum Ratings 6

Recommended Operating Conditions 6

lectrical Characteristics 7

Functional Block Diagram 8

Input/Output Pin Equivalent Circuit Diagram 9

Lead Definitions 10

Lead Assignments 10

Application Information and Additional Details 12

Package Details 17

Tape and Reel Details 18

Part Marking Information 19

Ordering Information 20

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

3

Description

The IRS254(01,11) are high voltage, high frequency buck control ICs for constant LED current regulation. They

incorporate a continuous mode time-delayed hysteretic buck regulator to directly control the average load current,

using an accurate on-chip bandgap voltage reference. These parts directly replace the IRS2540 and IRS2541

with improved latch up immunity.

The application is inherently protected against short circuit conditions, with the ability to easily add open-circuit

protection. An external high-side bootstrap circuit drives the buck switching element at high frequencies. A low-

side driver is also provided for synchronous rectifier designs. All functions are realized within a simple 8 pin DIP

or SOIC package.

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

4

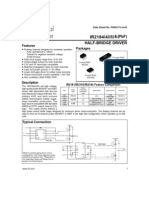

Alternate application circuit using a single MOSFET

I

R

S

2

5

4

0

1

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

5

Qualification Information

Industrial

Qualification Level

Comments: This family of ICs has passed JEDECs Industrial

qualification. IRs Consumer qualification level is granted by

extension of the higher Industrial level.

SOIC8

MSL2

260C

(per IPC/JEDEC J-STD-020)

Moisture Sensitivity Level

PDIP8

Not applicable

(non-surface mount package style))

Machine Model

Class B

(per JEDEC standard JESD22-A115)

ESD

Human Body Model

Class 1C

(per EIA/JEDEC standard EIA/JESD22-A114)

IC Latch-Up Test

Class I, Level A

(per JESD78)

RoHS Compliant

Yes

Qualification standards can be found at International Rectifiers web site http://www.irf.com/

Higher qualification ratings may be available should the user have such requirements. Please

contact your International Rectifier sales representative for further information.

Higher MSL ratings may be available for the specific package types listed here. Please contact your

International Rectifier sales representative for further information.

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

6

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage

parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The

thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

Symbol Definition Min Max Units

IRS25401 -0.3 225

V

B

High-side floating well supply voltage

IRS25411 -0.3 625

V

S

High-side floating well supply return voltage V

B

+ 0.3 V

B

+ 0.3

V

HO

Floating gate drive output voltage V

S

0.3 V

B

+ 0.3

V

LO

Low-side output voltage -0.3 V

CC

+ 0.3

V

IFB

Feedback voltage -0.3 V

CC

+ 0.3

V

ENN

Enable voltage -0.3 V

CC

+ 0.3

V

I

CC

Supply current (

) -20 20 mA

dV/dt Allowable offset voltage slew rate -50 50 V/ns

(8-Pin DIP) --- 1

P

D

Package power dissipation @ T

A +25 C

P

D

= (

T

JMAX

-T

A

)/R

THJA

(8-Pin SOIC) --- 0.625

W

(8-Pin DIP) ---

125

R

JA

Thermal resistance, junction to ambient

(8-Pin SOIC) --- 200

C/W

T

J

Junction temperature -55 150

T

S

Storage temperature -55 150

T

L

Lead temperature (soldering, 10 seconds) --- 300

C

: This IC contains a zener clamp structure between the chip V

CC

and COM, with a nominal breakdown voltage

of 15.6 V. Please note that this supply pin should not be driven by a low impedance DC power source greater

than V

CLAMP

specified in the electrical characteristics section.

Recommended Operating Conditions

For proper operation the device should be used within recommended conditions.

Symbol Definition Min Max Units

V

BS

High-side floating supply voltage V

CC

-0.7 V

CLAMPHS

IRS25401 -1 200

V

S

Steady state high-side floating supply offset

voltage IRS25411 -1 600

V

V

CC

Supply voltage V

CCUV+

V

CLAMP

I

CC

Supply current -Note 2 10

T

J

Junction temperature -25 125

: Sufficient current should be supplied to

VCC

to keep the internal 15.6 V zener regulating at V

CLAMP

.

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

7

Electrical Characteristics

V

CC

= V

BS

= V

BIAS

= 14 V +/- 0.25 V, C

LO

=C

HO

=1000 pF, C

VCC

=C

VBS

=0.1 F, T

A

=25 C unless otherwise

specified.

Symbol Definition Min Typ Max Units Test Conditions

Supply Characteristics

V

CCUV+

V

CC

supply undervoltage positive going

threshold

8.0 9.0 10.0 V

CC

rising from 0 V

V

CCUV-

V

CC

supply undervoltage negative going

threshold

6.5 7.5 8.5 V

CC

falling from 14 V

V

UVHYS

V

CC

supply undervoltage lockout

hysteresis

1.0 1.2 2.0

V

I

QCCUV

UVLO mode quiescent current --- 50 150 A V

CC

=6 V

I

QCCENN

Diesabled mode quiescent current --- 1.0 2.0 EN>V

ENTH+

I

QCC

Quiescent V

CC

supply current --- 1.0 2.0 I

FB

= 1 V

I

CC50k

V

CC

supply current, f = 50 kHz --- 2.0 3.0

mA

Duty Cycle = 50%

f = 50 kHz

V

CLAMP

V

CC

zener clamp voltage 14.6 15.6 16.6 V I

CC

= 10 mA

Floating Supply Characteristics

I

QBS0

Quiescent V

BS

supply current --- 0.05 1.0 V

HO

= V

S

I

QBS1

Quiescent V

BS

supply current --- 1.0 2.0

mA

I

FB

= 0 V

V

BSUV+

V

BS

supply undervoltage positive going

threshold

6.5 7.5 8.5

V

BSUV-

V

BS

supply undervoltage negative going

threshold

6.0 7.0 8.0

V

I

LK

Offset supply leakage current --- 1 50 A

IRS25401:V

B

=V

S

=200 V

IRS25411:V

B

=V

S

=600 V

V

CLAMPHS

V

BS

high side zener clamp voltage 24.4 26.0 27.6 V I

CC

= 10 mA

Current Control Operation

V

ENNTH+

ENN pin positive threshold 2.5 2.7 3.0

V

ENNTH-

ENN pin negative threshold 1.7 2.0 2.3

V

V

0.5

0.5 V voltage reference (die level test) 490 500 510

V

IFBTH

IFB pin threshold 455 500 540

mV

f Maximum frequency --- 500 --- kHz

Gate Driver Output Characteristics

V

OL

Low level output voltage (HO or LO) --- COM ---

V

OH

High level output voltage (HO or LO) --- V

CC

---

V

t

r

Turn-on rise time --- 50 120

t

f

Turn-off fall time --- 30 50

ns

I

O+/-

Output source/sink short circuit pulsed

current

--- 0.5/0.7 --- A

DT Deadtime --- 140 ---

t

LO,ON

Delay between V

IFB

>V

IFBTH

and LO turn-on --- 320 ---

t

LO,OFF

Delay between V

IFB

<V

IFBTH

and LO turn-off --- 180 ---

t

HO,ON

Delay between V

IFB

<V

IFBTH

and HO turn-

on

--- 320 ---

t

HO,OFF

Delay between V

IFB

>V

IFBTH

and HO turn-

off

--- 180 ---

ns

I

FB

= 50 kHz square

wave, 200 mV pk-pk

DC offset = 400 mV

Duty Cycle = 50%

Watchdog timer

t

WD

Watchdog timer period --- 20 ---

P

WWD

LO pulse width --- 1.0 ---

s I

FB

=1 V

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

8

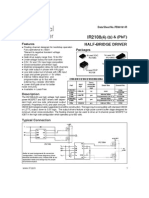

Functional Block Diagram

Values in block diagram are typical values

LEVEL

SHIFT

PULSE

FILTER &

LATCH

7

8

6 VS

HO

VB

1

5

2 COM

LO

VCC

15.6V

4

ENN

2V

3

IFB

DELAY

DELAY UVLO

UVN

0. 5V

Watchdog

Timer 20?S

1?SPulse

Generator

BANDGAP

REFERENCE 100 K

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

9

Input/Output Pin Equivalent Circuit Diagrams: IRS25401/IRS25411

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

10

Lead Definitions

PIN # Symbol Description

1 VCC Supply voltage

2 COM IC power & signal ground

3 IFB Current feedback

4 ENN Disable outputs (LO=High, HO=Low)

5 LO Lowside gate driver output

6 VS Highside floating return

7 HO Highside gate driver output

8 VB Highside gate driver floating supply

Lead Assignments

IRS254(01,11)(S)

www.irf.com 2010 International Rectifier

11

State Diagram

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

12

Application Information and Additional

Details

Operating Mode

The IRS254(01,11) operates as a time-delayed

hysteritic buck controller. During normal operating

conditions the output current is regulated via the IFB

pin voltage (nominal value of 500 mV). This feedback

is compared to an internal high precision bandgap

voltage reference. An on-board dV/dt filter has also

been used to ignore erroneous transitioning.

Once the supply to the IC reaches V

CCUV+

, the LO

output is held high and the HO output low for a

predetermined period of time. This initiates charging of

the bootstrap capacitor, establishing the V

BS

floating

supply for the high-side output. The IC then begins

toggling HO and LO outputs as needed to regulate the

current.

Fig.1 IRS254(01,11) Control Signals, Iavg=1.2 A

As long as V

IFB

is below V

IFBTH

, HO is on, modulated by

the watchdog timer described below, which maintains

charge for the floating high side on the bootstrap

capacitor. The load is receiving current from V

BUS

,

which simultaneously stores energy in the inductor, as

V

IFB

increases, unless the load is open circuit. Once

V

IFB

crosses V

IFBTH

, the control loop switches HO off

after the delay t

HO,OFF

. When HO switches off, LO will

turn on after the deadtime (DT), the inductor then

releases its stored energy into the load and V

IFB

starts

decreasing. When V

IFB

drops below V

IFBTH

again, the

control loop switches HO on after the delay t

HO,ON

and

LO off after the delay t

HO,ON

+ DT. The switching

continues to regulate the current at an average value

determined as follows. When the inductance value

is large enough to maintain a low ripple on I

FB

, I

out,avg

can be calculated:

RCS

VIFBTH

avg Iout = ) (

(A) (B)

Fig.2 (A) Storing Energy in Inductor

(B) Releasing Inductor Stored Energy

t_LO_on

t_HO_off

DT1

IFBTH

50%

50%

50%

50%

t_LO_off

DT2

t_HO_on

HO

LO

IFB

50%

Fig.3 IRS254(0,1) Time Delayed Hysterisis

The control method is hysteretic with a free running

frequency, which enables average current regulation

in constrast to a fixed frequency scheme providing

peak current regulation only. This reduces the part

count since there is no need for frequency setting

components and also provides an inherently stable

system, which acts as a dynamic current source.

A deadtime of approximately 140 ns between the two

gate drive signals is incoporated to prevent shoot-

through. The deadtime has been adjusted to maintain

precise current regulation, while still preventing

shoot-through.

HO

LO

Iout

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

13

Watchdog Timer

During an open circuit condition, without the watchdog

timer, the HO output would remain high at all times and

the charge stored in the bootstrap capacitor C

BOOT

would gradually discharge the floating power supply for

the high-side driver, which would then be unable to fully

switch on the upper MOSFET causing high losses. To

maintain sufficient charge on the bootstrap capacitor, a

watchdog timer has been implemented. In the

condition where V

IFB

remains below V

IFBTH

, the HO

output is driven low after 20 s and the LO output

forced high. This toggling of the outputs will last for

approximately 1 s to maintain and replenish sufficient

charge on C

BOOT

.

Fig.4 Illustration of Watchdog Timer

Bootstrap Capacitor and Diode

The bootstrap capacitor value needs to be selected so

that it maintains sufficient charge for at least the

approximately 20 s interval until the watchdog timer

allows the capacitor to recharge. If the capacitor value

is too small, it will discharge in less than 20 s. The

typical bootstrap capacitor is approximately 100 nF.

The bootstrap diode must be a fast recovery or ultrafast

recovery component to maintain good efficiency. Since

the cathode of the bootstrap diode will be switching

between zero and to the high voltage bus, the reverse

recovery time of this diode is critical. For additional

information concerning the bootstrap components, refer

to the Design Tip (DT 98-2), Bootstrap Component

Selection For Control ICs at www.irf.com under Design

Support

Disable (ENN) Pin

The disable pin can be used for PWM dimming and

open-circuit protection. When the ENN pin is held

low, the chip remains in a fully functional state with no

alterations to the operating environment. To disable

the control feedback and regulation, a voltage greater

than V

ENTH

(approximately 2.5 V) needs to be applied

to the ENN pin. With the chip in a disabled state, HO

output will remain low, whereas the LO output will

remain high to prevent V

S

from floating, in addition to

maintaining charge on the bootstrap capacitor. The

threshold for disabling the IRS254(01,11) has been

set to 2.5 V to enhance noise immunity. This 2.5 V

threshold also provides compatibility for a drive signal

from a microcontroller.

Dimming Mode

To achieve dimming, a signal with constant frequency

and adjustable duty cycle can be fed into the ENN

pin. There is a direct linear relationship between the

average load current and duty cycle. If the ratio is

50%, 50% of the maximum set light output will be

realized. Likewise if the ratio is 30%, 70% of the

maximum set light output will be realized. A

sufficiently high frequency of the dimming signal must

be chosen to avoid noticeable flashing or strobe

light effect. A signal above 120Hz up to 5kHz is

sufficient.

The ENN pin logic is inverted to provide enable low

so that the default state is with the IC running.

The minimum amount of dimming achievable (light

output approaches 0%) will be determined by the on

time of the HO output, when in a fully functional

regulating state. To maintain reliable dimming, it is

recommended to keep the off time of the enable

signal at least 10 times that of the HO on time. For

example, if the application is running at 75 kHz with

an input voltage of 100 V and an output voltage of 20

V, the HO on time will be approximately 2.7 s

according to standard buck topology theory. This will

set the minimum off time of the enable signal to 27

s.

s

kHz

HO

V

V

V

V

Cycle Duty

on

in

out

7 . 2

75

1

* % 20

% 20 100 *

100

20

100

time

=

= = =

HO

LO

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

14

Enable Duty Cycle Relationship to Light Output

0

10

20

30

40

50

60

70

80

90

100

0 10 20 30 40 50 60 70 80 90 100

Percentage of Light Output

E

n

a

b

l

e

P

i

n

D

u

t

y

C

y

c

l

e

Fig.5 Light Output vs Enable Pin Duty Cycle

Fig.6 IRS254(01,11) Dimming Signals

Open Circuit Protection Mode

There are several

methods of providing

over voltage protection

at the output if needed.

The following very

simple method uses a

voltage divider,

capacitor, and zener

diode, the output

voltage can be clamped

at any desired value. In open-

circuit condition without any

output clamp, the positive output terminal may reach a

high DC voltage. Switching will still occur between the

HO and LO outputs, whether due to the output voltage

clamp or the watchdog timer. Transients and switching

will be observed at the positive output terminal as seen

in Fig. 8. The difference in signal shape, between the

output voltage and the I

FB

, is due to the capacitor used

to form the voltage clamp. The repetition of the

spikes can be reduced by simply increasing the

capacitor size.

The two resistors form a voltage divider for the

output, which is then fed into the cathode of the zener

diode. The diode will only conduct, flooding the

enable pin, when its nominal voltage is exceeded.

The chip will enter a disabled state once the divider

network produces a voltage at least 2.5 V greater

than the zener rating. The capacitor serves only to

filter and slow the transients/switching at the positive

output terminal. The clamped output voltage can be

determined by the following analysis. The choice of

capacitor is at the designers discretion.

This scheme will not be adequate in all applications.

An improved method is described in IRPLLED1 Rev

D reference design documentation.

( )( )

Voltage Rated Nominal Diode Zener

5 . 2

2

2 1

=

+ +

=

DZ

R

R R DZ V

V

out

Fig.8 Open Circuit Fault Signals, with Clamp

Under-voltage Lock-out Mode

The under-voltage lock-out mode (UVLO) is defined

as the state IRS254(01,11) is in when

VCC

is below

the turn-on threshold of the IC. During startup

conditions, if the IC supply remains below

VCCUV+

, the

IRS254(01,11) will enter the UVLO mode. This state

is very similar to when the IC has been disabled via

control signals, except that LO is also held low.

When the supply is increased to V

CCUV+

, the IC enters

Fig.7 Open Circuit

Protection Scheme

3

4

I

R

S

2

5

4

0

/

1

EN

IFB

Vout

R1

R2

HO

LO

EN

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

15

the normal operation mode. If already in normal

operation, the IC does not enter UVLO unless the

supply voltage falls below V

CCUV--

.

Inductance Selection

To maintain tight hysteretic current regulation the

inductor and output capacitor C

OUT

(in parallel with the

LEDs) need to be large enough to maintain the supply to

the load during t

HO,ON

and avoid significant

undershooting of the load current, which in turn causes

the average current to fall below the desired value.

First, consider the effect of the inductor when there is no

output capacitor to clearly demonstrate the impact of the

inductor. In this case, the load current is identical to the

inductor current. Fig. 9 shows how the inductor value

impacts the frequency over a range of input voltages. As

can be seen, the input voltage has a great impact on the

frequency and the inductor value has the greatest impact

at reducing the frequency for smaller input voltages.

175

225

275

325

375

425

30 80 130 180

Vin (V)

F

r

e

q

u

e

n

c

y

(

k

H

z

)

470uH

680uH

1mH

1.5mH

Fig.9 Frequency Response for Chosen Inductances

I

out

= 350 mA, V

out

= 16.8 V

Fig. 10 shows how the variation in load current increases

over a span of input voltages, as the inductance is

decreased. Fig. 11 shows the variation of frequency over

different output voltages and different inductance values.

Finally Fig. 12 shows how the load current variation

increases with lower inductance over a range of output

voltages.

The output capacitor can be used simultaneously to

achieve the target frequency and current control

accuracy. Fig. 11 shows how the capacitance reduces

the frequency over a range of input voltage. A small

capacitance of 4.7 F has a large effect on reducing the

frequency. Fig. 12 shows how the current regulation is

also improved with the output capacitance. There is a

point at which continuing to add capacitance no longer

has a significant effect on the operating frequency or

current regulation, as can be seen in Figs. 13 and 14.

330

340

350

360

370

380

390

400

30 80 130 180

Vin (V)

I

o

u

t

(

m

A

)

470uH

680uH

1mH

1.5mH

Fig.10 Current Regulation for Chosen Inductances

I

out

= 350 mA, V

out

= 16.8 V

200

220

240

260

280

300

320

340

360

380

400

13 18 23 28 33

Vout (V)

F

r

e

q

u

e

n

c

y

(

k

H

z

)

470uH

680uH

1mH

1.5mH

Fig.11 Frequency Response for Chosen Inductances

I

out

= 350 mA, V

in

= 50 V

325

327

329

331

333

335

337

339

341

343

345

13 18 23 28 33

Vout (V)

I

o

u

t

(

m

A

)

470uH

680uH

1mH

1.5mH

Fig.12 Current Regulation for Chosen Inductances

I

out

= 350 mA, V

in

= 50 V

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

16

10

100

1000

30 50 70 90 110 130 150 170

Vin (V)

F

r

e

q

u

e

n

c

y

(

k

H

z

)

0uF

4.7uF

10uF

22uF

33uF

47uF

Fig. 13 I

out

= 350 mA, V

out

= 16.8 V, L = 470 H

0

50

100

150

200

250

300

350

400

0 10 20 30 40 50

Capacitance (uF)

F

r

e

q

u

e

n

c

y

(

k

H

z

)

40V

100V

160V

Fig. 14 I

out

= 350 mA, V

out

= 16.8 V, L = 470 H

The addition of the C

OUT

increases the amount of

energy that can be stored in the output stage, which

also means it can supply current for an increased

period of time. Therefore by slowing down the di/dt

transients in the load, the frequency is effectively

decreased.

With the C

OUT

capacitor, the inductor current is no

longer identical to that seen in the load. The inductor

current will still have a perfectly triangular shape, where

as the load will see the same basic trend in the current,

but all sharp corners will be rounded with all peaks

significantly reduced, as can be seen in Fig. 15

VCC

Supply

Since the IRS254(01,11) is rated for 200 V (or 600 V),

V

BUS

can reach values of this magnitude. If a supply

resistor to V

BUS

is used, it can experience high power

losses. For higher voltage applications if the output

voltage is above VCCUV+ plus one diode drop an

alternate V

CC

supply scheme utilizing the micro-power

start-up and a resistor feed-back from the output can to

be implemented, as seen in Fig. 16.

Fig. 15 I

out

= 350 mA, V

in

= 100 V, V

out

= 16.85 V, L = 470 H,

C

out

= 33 F

The resistance between V

BUS

and V

CC

supply should

be large enough to minimize the current sourced

directly from the input voltage line; value should be on

the order of hundreds of k. Through the supply

resistor, a current will flow to charge the

VCC

capacitor. Once the capacitor is charged up to the

VCCUV+

threshold, the IRS254(01,11) enters the micro

start-up regime and begins to operate, activating the

LO and HO outputs. After the first few cycles of

switching, the resistor connected between the output

and

V

CC

will take over and source all necessary

current for the IC. The resistor connecting the output

to the supply should be carefully designed according

to its power rating.

mA Icc

P

RS mA P

mA

V V

RS

Rated RS

RS

out

10

2

2 ) 10 (

10

6 . 15

2

_ 2 2

2

=

Fig. 16 Alternate Supply Diagram

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

17

Package Details

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

18

Tape and Reel Details

E

F

A

C

D

G

A

B H

NOTE : CONTROLLING

DIMENSION IN MM

LOADED TAPE FEED DIRECTION

A

H

F

E

G

D

B

C

CARRIER TAPE DIMENSION FOR 8SOICN

Code Min Max Min Max

A 7.90 8.10 0.311 0.318

B 3.90 4.10 0.153 0.161

C 11.70 12.30 0.46 0.484

D 5.45 5.55 0.214 0.218

E 6.30 6.50 0.248 0.255

F 5.10 5.30 0.200 0.208

G 1.50 n/a 0.059 n/a

H 1.50 1.60 0.059 0.062

Metric Imperial

REEL DIMENSIONS FOR 8SOICN

Code Min Max Min Max

A 329.60 330.25 12.976 13.001

B 20.95 21.45 0.824 0.844

C 12.80 13.20 0.503 0.519

D 1.95 2.45 0.767 0.096

E 98.00 102.00 3.858 4.015

F n/a 18.40 n/a 0.724

G 14.50 17.10 0.570 0.673

H 12.40 14.40 0.488 0.566

Metric Imperial

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

19

Part Marking Information

SOIC

PDIP

IRS254(0,1)(S)PbF

www.irf.com 2010 International Rectifier

20

Ordering Information

Standard Pack

Base Part Number Package Type

Form Quantity

Complete Part Number

PDIP8 Tube/Bulk 50 IRS25401PBF

Tube/Bulk 95 IRS25401SPBF IRS25401

SOIC8

Tape and Reel 2500

IRS25401STRPBF

PDIP8 Tube/Bulk 50 IRS25411PBF

Tube/Bulk 95 IRS25411SPBF IRS25411

SOIC8

Tape and Reel 2500

IRS25411STRPBF

The information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility

for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of

other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any

patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This

document supersedes and replaces all information previously supplied.

For technical support, please contact IRs Technical Assistance Center

http://www.irf.com/technical-info/

WORLD HEADQUARTERS:

233 Kansas St., El Segundo, California 90245

Tel: (310) 252-7105

You might also like

- Irs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICDocument29 pagesIrs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICAnonymous R0s4q9X8No ratings yet

- Self-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Document9 pagesSelf-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Zoltán HalászNo ratings yet

- Ir 2153Document9 pagesIr 2153SteveAbonyiNo ratings yet

- FAN7382 High-And Low-Side Gate Driver: Features DescriptionDocument15 pagesFAN7382 High-And Low-Side Gate Driver: Features DescriptionRiza BaduaNo ratings yet

- Irs 2453 DDocument18 pagesIrs 2453 DMallickarjunaNo ratings yet

- Driving Half-Bridges up to 600 VDocument30 pagesDriving Half-Bridges up to 600 VphieuxuatkhoNo ratings yet

- Ir 2111Document15 pagesIr 2111Miltongrimi GrimilNo ratings yet

- Ir 2184Document24 pagesIr 2184buiphuoclaiNo ratings yet

- 74LVT2244, 74LVTH2244 Low Voltage Octal Buffer/Line Driver With 3-STATE Outputs and 25 Series Resistors in The OutputsDocument9 pages74LVT2244, 74LVTH2244 Low Voltage Octal Buffer/Line Driver With 3-STATE Outputs and 25 Series Resistors in The Outputsjovares2099No ratings yet

- Ir 2108Document23 pagesIr 2108robertofurlancriNo ratings yet

- Voltage-Controlled Oscillator: ... The Analog Plus CompanyDocument24 pagesVoltage-Controlled Oscillator: ... The Analog Plus CompanyMoltrevNo ratings yet

- Ir2181 Igbt Driver PDFDocument21 pagesIr2181 Igbt Driver PDFismifaizulNo ratings yet

- Ap5002 - PWM Control 2a Step-Down ConverterDocument10 pagesAp5002 - PWM Control 2a Step-Down ConverterAmador Garcia IIINo ratings yet

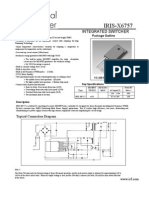

- IRIS-X6757: FeaturesDocument10 pagesIRIS-X6757: Featuresmiguel angel jaramilloNo ratings yet

- Ir 2105Document12 pagesIr 2105Manuel Villegas AcostaNo ratings yet

- Datasheet PDFDocument7 pagesDatasheet PDFpurwadiNo ratings yet

- Datasheet 42Document18 pagesDatasheet 42Roozbeh Bahmanyar100% (1)

- Fan 7361Document9 pagesFan 7361Odalis CabaNo ratings yet

- LM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BDocument24 pagesLM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BPravin MevadaNo ratings yet

- FAN73832 (Half-Bridge Dead Time Control)Document16 pagesFAN73832 (Half-Bridge Dead Time Control)Ismael StarkNo ratings yet

- Ir 2153Document9 pagesIr 2153Carlos Marinho SilvaNo ratings yet

- 4-Channel Secondary Monitoring IC DatasheetDocument11 pages4-Channel Secondary Monitoring IC DatasheetIdelbrando RochaNo ratings yet

- Hcnw3120 Opto CouplerDocument26 pagesHcnw3120 Opto CouplercknitterNo ratings yet

- IR2175(S) & (PbF) Linear Current Sensing IC Data Sheet SummaryDocument7 pagesIR2175(S) & (PbF) Linear Current Sensing IC Data Sheet SummaryLullaby summerNo ratings yet

- Data Sheet Summary for Half-Bridge Driver IRS2103(S)PbFDocument14 pagesData Sheet Summary for Half-Bridge Driver IRS2103(S)PbFViệt LêNo ratings yet

- HP 450 OptocouplerDocument16 pagesHP 450 Optocoupler1cvbnmNo ratings yet

- Universal DC/DC Converter: (Top View)Document11 pagesUniversal DC/DC Converter: (Top View)Engine Tuning UpNo ratings yet

- High and low side driver data sheet summaryDocument16 pagesHigh and low side driver data sheet summaryguiknopNo ratings yet

- Ir 2101Document14 pagesIr 2101Willard DmpseyNo ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- LM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesDocument17 pagesLM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesbhushanchittaragiNo ratings yet

- Isolated Flyback Switching Regulator W - 9V OutputDocument16 pagesIsolated Flyback Switching Regulator W - 9V OutputCasey DialNo ratings yet

- AZ324Document10 pagesAZ324Franklim Miranda Dos SantosNo ratings yet

- Low Power Dual Operational Amplifiers Az358/358CDocument13 pagesLow Power Dual Operational Amplifiers Az358/358CMarissa ValdezNo ratings yet

- Fan 7530Document20 pagesFan 7530aldo_suviNo ratings yet

- 2.0 Amp Output Current IGBT Gate Drive Optocoupler: Technical DataDocument24 pages2.0 Amp Output Current IGBT Gate Drive Optocoupler: Technical DatajhucorpNo ratings yet

- 7Z08Document7 pages7Z08André Frota PaivaNo ratings yet

- Ir 2109Document25 pagesIr 2109Chavi AlmeidaNo ratings yet

- 8 Pin Ic - FSQ510Document15 pages8 Pin Ic - FSQ510Raja Pathamuthu.GNo ratings yet

- Fan 7316Document21 pagesFan 7316sontuyet82No ratings yet

- S2127Document21 pagesS2127RICHIHOTS2No ratings yet

- MJL21193 21194Document6 pagesMJL21193 21194DiosmeHenrnadezNo ratings yet

- Self-Oscillating Half-Bridge Driver Preliminary Data SheetDocument9 pagesSelf-Oscillating Half-Bridge Driver Preliminary Data Sheetamijoski6051No ratings yet

- Datasheet (LT1074)Document16 pagesDatasheet (LT1074)HermesSanchezNo ratings yet

- 2SA2040/2SC5707: Bipolar TransistorDocument10 pages2SA2040/2SC5707: Bipolar Transistorblueword66No ratings yet

- Fs 276 LFV 02Document12 pagesFs 276 LFV 02Pablo MgNo ratings yet

- Ir 2110Document17 pagesIr 2110Nguyen KhangNo ratings yet

- Ir 2304Document8 pagesIr 2304Rajo AmehNo ratings yet

- MC100EL1648 5 V ECL Voltage Controlled Oscillator Amplifier: DescriptionDocument16 pagesMC100EL1648 5 V ECL Voltage Controlled Oscillator Amplifier: DescriptionHudionoHoodNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- AMD-V Hyper-V EULA - FinalDocument4 pagesAMD-V Hyper-V EULA - FinalsumodiningratNo ratings yet

- Hamilton Beach 22810 ToasterDocument24 pagesHamilton Beach 22810 ToasterJess AJNo ratings yet

- Dpa-300s - 600S - 900S - 1200S - Service - 1401 2Document86 pagesDpa-300s - 600S - 900S - 1200S - Service - 1401 2ЕвгенийNo ratings yet

- Symetrix Solutions: Tech Tip: Transient Suppressor DSP ModuleDocument1 pageSymetrix Solutions: Tech Tip: Transient Suppressor DSP ModuleJess AJNo ratings yet

- Et Series Solid State Toasters: Standard Features ModelsDocument2 pagesEt Series Solid State Toasters: Standard Features ModelsJess AJNo ratings yet

- 70VMultizoneSingleAmpAudioSystem 251Document1 page70VMultizoneSingleAmpAudioSystem 251Jess AJNo ratings yet

- 511.79 Nvidia Control Panel Quick Start GuideDocument28 pages511.79 Nvidia Control Panel Quick Start GuideMusik BaratNo ratings yet

- Shopjimmy T Con Board Samsung Bn96 42319aDocument1 pageShopjimmy T Con Board Samsung Bn96 42319aJess AJNo ratings yet

- Bottom Freezer Refrigerator: Refrigerador Con Congelador InferiorDocument92 pagesBottom Freezer Refrigerator: Refrigerador Con Congelador InferiorJess AJNo ratings yet

- T3 PINBALL sb142 PDFDocument1 pageT3 PINBALL sb142 PDFJess AJNo ratings yet

- TSPP Manual PDFDocument216 pagesTSPP Manual PDFJess AJNo ratings yet

- Terminator3 Manual PDFDocument218 pagesTerminator3 Manual PDFJess AJNo ratings yet

- VP 100 Users Manual PDFDocument8 pagesVP 100 Users Manual PDFJess AJNo ratings yet

- TT2000 Ticket Eater MANUAL WITH BJ 100 LOGIC PCB PDFDocument31 pagesTT2000 Ticket Eater MANUAL WITH BJ 100 LOGIC PCB PDFJess AJNo ratings yet

- T3 PINBALL sb140 PDFDocument1 pageT3 PINBALL sb140 PDFJess AJNo ratings yet

- TS PP PINBALL sb138 PDFDocument1 pageTS PP PINBALL sb138 PDFJess AJNo ratings yet

- T3 PINBALL sb145 PDFDocument1 pageT3 PINBALL sb145 PDFJess AJNo ratings yet

- Drift Upgrade BrochureDocument1 pageDrift Upgrade BrochureJess AJNo ratings yet

- T3 PINBALL sb143 PDFDocument1 pageT3 PINBALL sb143 PDFJess AJNo ratings yet

- LG LCD TV 42lp1d Service ManualDocument52 pagesLG LCD TV 42lp1d Service ManualDamiaoNo ratings yet

- 32LP1D Service ManualDocument1 page32LP1D Service ManualJess AJNo ratings yet

- Datasheet 2SD2627Document4 pagesDatasheet 2SD2627Jess AJNo ratings yet

- Max 17105Document26 pagesMax 17105Jess AJNo ratings yet

- P6NA60FP DatasheetDocument5 pagesP6NA60FP DatasheetJess AJNo ratings yet

- Drift Conversion ManualDocument32 pagesDrift Conversion ManualJess AJNo ratings yet

- Irfib7N50A: Smps MosfetDocument8 pagesIrfib7N50A: Smps MosfetJess AJNo ratings yet

- Drift Conversion ManualDocument32 pagesDrift Conversion ManualJess AJNo ratings yet

- Drift Conversion BrochureDocument1 pageDrift Conversion BrochureJess AJNo ratings yet

- Drift Conversion ManualDocument32 pagesDrift Conversion ManualJess AJNo ratings yet

- DILET70ADocument28 pagesDILET70AObrian MahurureNo ratings yet

- Unit-1.1.1 Fundamentals of Electrical CircuitDocument23 pagesUnit-1.1.1 Fundamentals of Electrical Circuitbadrinarayan2210298No ratings yet

- Panasonic TC-L32XM6H TV Service Manual Parts ListDocument34 pagesPanasonic TC-L32XM6H TV Service Manual Parts ListHector Fabio PelaezNo ratings yet

- Twin Loop Treasure Seeker: Robert and David CroneDocument5 pagesTwin Loop Treasure Seeker: Robert and David CronesafdsfdNo ratings yet

- CT5601 (SOT23-6) EN Rev1.0Document12 pagesCT5601 (SOT23-6) EN Rev1.0Angel Luciano Ramon GomezNo ratings yet

- Eet 203 Measurements and Instrumentation Module IDocument42 pagesEet 203 Measurements and Instrumentation Module Idevil jattNo ratings yet

- 12 PhysicsDocument8 pages12 PhysicsHem Narayan AcharjaNo ratings yet

- Nr131s Ds enDocument13 pagesNr131s Ds enlalgalleNo ratings yet

- Sample PBLDocument10 pagesSample PBLMABINI Hanna SchaneNo ratings yet

- Wireless Charging of Electric VehiclesDocument11 pagesWireless Charging of Electric Vehiclesomkar chitnisNo ratings yet

- TU Physics Syllabus 2016Document26 pagesTU Physics Syllabus 2016S.M. Ashikur RahmanNo ratings yet

- Split Air Conditioner Wiring Diagram ContactorsDocument8 pagesSplit Air Conditioner Wiring Diagram ContactorsVicente Rossi80% (5)

- B767 ATA 24 Student BookDocument73 pagesB767 ATA 24 Student BookElijah Paul Merto100% (6)

- Aircraft Systems - Booster CoilDocument2 pagesAircraft Systems - Booster CoilzcrackNo ratings yet

- Question Paper Physics PB I 2023-24Document6 pagesQuestion Paper Physics PB I 2023-24rishirajkaran2006No ratings yet

- 1433481891893-Question Bank TechIII-TL LDCEDocument42 pages1433481891893-Question Bank TechIII-TL LDCEkrishgkkd333991% (32)

- Igcse Physics c9 Prac QuesDocument6 pagesIgcse Physics c9 Prac QueshuxxiNo ratings yet

- JEE Main-Sample Papers-By FIITJEE PDFDocument40 pagesJEE Main-Sample Papers-By FIITJEE PDFMihir Jain100% (1)

- RHS Brochure 2013Document48 pagesRHS Brochure 2013Mohamed Diaa MortadaNo ratings yet

- HLQ INDUCTION COILS BASIC DESIGNDocument12 pagesHLQ INDUCTION COILS BASIC DESIGNTuan PhamNo ratings yet

- Ultrasound Blind Stick Using GPS+GSM+VoiceDocument58 pagesUltrasound Blind Stick Using GPS+GSM+VoiceSanowar Hossin100% (1)

- Hemant SirDocument5 pagesHemant SirkamalNo ratings yet

- TLE 10 - Electronics - SLAS 1 - Tracing The History of ElectronicsDocument13 pagesTLE 10 - Electronics - SLAS 1 - Tracing The History of ElectronicsGerrylie GallardoNo ratings yet

- Simple DC To DC Converter CircuitsDocument10 pagesSimple DC To DC Converter Circuitscarlken_07100% (1)

- CWIEME Chicago 2010 - Exhibitor List - Products and ServicesDocument12 pagesCWIEME Chicago 2010 - Exhibitor List - Products and Servicesrehansadiq1No ratings yet

- GRADES 1 To 12 Daily Lesson Log: School: Grade Level: Teacher: Learning Area: Teaching Dates and Time: QuarterDocument8 pagesGRADES 1 To 12 Daily Lesson Log: School: Grade Level: Teacher: Learning Area: Teaching Dates and Time: QuarterKeiC Dela CruzNo ratings yet

- MODELLING of Explosively Driven Magnetic Flux Compression GeneratorsDocument113 pagesMODELLING of Explosively Driven Magnetic Flux Compression Generatorsazeraqw22No ratings yet

- Power Line CarrierDocument27 pagesPower Line CarrierAmeer Ullah Khan100% (1)

- Power and Distribution Transformer Markets: ColumnDocument8 pagesPower and Distribution Transformer Markets: ColumnGAURAV GUPTANo ratings yet

- Colpitts Oscillator Using Op Amp - BJT Colpitts OscillatorDocument3 pagesColpitts Oscillator Using Op Amp - BJT Colpitts Oscillatorliton_kabirNo ratings yet