Professional Documents

Culture Documents

Csecs 42

Uploaded by

Ganesan SOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Csecs 42

Uploaded by

Ganesan SCopyright:

Available Formats

PCB Thermal Design Improvement Through Thermal Vias

NADEZHDA KAFADAROVA, ANNA ANDONOVA

Department of Microelectronics

Technical University of Sofia

1797 Sofia, 8, Kl. Ohridski str.

BULGARIA

n_kafadarova@yahoo.com; ava@ecad.tu-sofia.bg

Abstract: - An approach based on design of different experiments for improvement the thermal paths in PCB through

thermal vias is offered. An efficient thermal via placed on the PCB decreases the junction temperature of the package.

In this paper elaborate study has been done in analyzing the effect of thermal vias and the ways to decrease the junction

temperature by given number of computations. Thermal enhancement has been achieved by running the thermal

simulations with and without thermal vias. Temperature profiles have been plotted in FLOTHERM. The thermal

enhancement study focuses on the importance of thermal vias to a great extent. The simulation models are validated

with experiments.

Key-Words: - Thermal simulation, CFD, PCB, Thermal vias, Thermal resistance, Thermography

1 Introduction

As thermal problems become more evident, new

physical design paradigms and tools are needed to

manage them. Such problems as increased interconnect

delays, power consumption and temperature, all of

which can have serious implications on reliability,

performance, and design effort. The thermal resistance

between junction-to-ambient (

JA

) is highly dependent

on the PCB (Printed Circuit Board) design factors. This

becomes more critical for packages having very low

thermal resistance between junction-to-case.

JA

is used

to characterize the heat dissipation ability of a

package/board system from the die through the PCB

board to the ambient environment. As the thermal

resistance from PCB board to ambient is much larger

than that from die to board, it is more significant to study

the effect of the PCB board design on the thermal

resistance

JA

in detail.

The idea of using thermal vias to solve thermal problems

is not new [1]. The use of thermal vias in packaging is

implemented by two different methods. The first one is

that the one end of via is attached to the bottom

substrate, and the other is attached to the top substrate

with a hole through to the substrate. The other is that the

one end of via is attached to the top die, and the other is

attached to the bottom die with a hole to the die. The

thermal solution of vias depends on the thermal

resistance. The various via configurations based on the

first method of packaging will be analyzed.

The relationships between design parameters and the

thermal resistance of thermal via clusters in PCBs were

determined by simplifying the via cluster into parallel

networks.

It has become of particular interest to design efficient

heat conduction paths right into a PCB/MCM/chip to

eliminate localized hot spots directly. Despite all the

work that has been done in evaluating thermal vias,

thermal via placement algorithms are lacking even

with 2D PCB. As circuits and temperature profiles

increase in complexity, efficient algorithms are needed

to accurately determine the location and number of

thermal vias [2].

An approach based on design of different experiments

for improvement the thermal paths in PCB through

thermal vias is offered.

2 CFD Simulations of Conduction Paths

for Thermal Vias Impovement

It is well known that the thermal resistance of the

package, especially,

JA

, is highly dependent on the PCB

in which the parts are mounted for thermal testing. The

effect of the PCB is more critical when the package has

extremely low

JC

(or thermal resistance between

junction-to-case) because the thermal resistance between

case to PCB, and PCB to ambient air, becomes more

dominant than that between die to package case [3].

The remaining conduction paths extend from the device

into the rest of the layers (both copper and dielectric)

through the thermal vias underneath the device. These

conduction paths, if optimized through proper design of

the thermal via array, are the most efficient paths in the

structure for removing heat from the device.

When considering the design of the thermal via array, it

is helpful to first identify an ideal structure for the

purpose of heat conduction. After the theoretical ideal is

established, the system designer can attempt to design in

a more practical structure that will closely replicate the

ideal structure.

All of the vias arrays are arranged to be on a regular

pitch on a matrix pattern. The vias matrices vary from no

RECENT ADVANCES in CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL and SIGNAL PROCESSING

ISSN: 1790-5117 241 ISBN: 978-960-474-139-7

vias (0 x 0) to a large 4 x 4 array and the vias numbers

vary from 0 to 16. Different location of thermal vias

and the vertical and horizontal distances between the

thermal vias are studied: once with the same distances

of 0,8 mm between the thermal vias and other with

different vertical of 2 mm and horizontal of 0,8 mm

distances between the thermal vias respectively.

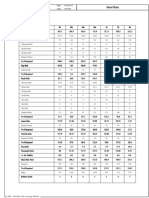

In Table1 are given different types of thermal via

structures.

Table.1. The thermal via structures for the purpose

of heat conduction investigations of PCB

Stucture Ideal type

copper slug

First type

solder slug

Second type

air slug

View with

two Cu

laers

In Table 2 the design of experiment parameters for CFD

simulation are shown.

Table.2. Parameters for CFD simulation

(K

Cu

=385W/mK; K

Ni

=59W/mK; K

FR4

=0,4 W/mK; K

Sn63

= 50,9W/mK)

PCB area 576 mm

2

(24 mm x 24 mm)

FR4 thickness 1,2 mm

Device dimensions 20mm x 20 mm x 1,5 mm

Diameter of the via, mm 0,8 1 2

Vias array, XxY 2x2 3x3 4x4

Copper thickness, mm 0,04 0,08 0,12

Power dissipated,W 1 2 3

Ambient temperature,

0

C 20 40 60

Number of Cu layers 2 3 4

The number and size of the vias are limited by the size

of the thermal pad and the capabilities of the PCB

manufacturer, making their design relatively

straightforward. For reliability in the manufacturing

process, the drill diameter of the vias should be no less

than 0,25 mm, and the center-line of the vias should

remain 0,9 mm away from the edge of the thermal pad

and from each other. It would seem that, since the

purpose of adding this via structure is to replicate a solid

copper slug, the designer should add as many vias as

possible.

The value of the thermal conductivity, K, in any

particular direction corresponds to the density of thermal

vias that are arranged in that direction. Increasing the

number of thermal vias in one direction increases the

thermal conductivity in the other directions but in the

direction of the smaller magnitude. For simplicity, the

interdependence can be considered to be negligible, and

the Ks in the x, y, and z directions can be considered to

be independent to a certain extent.

The percentage of thermal vias, m, (also called thermal

ensity) in a thermal via region is given by the

equation:

via d

following

m =

nA

ic

wh

(1)

where n is the number of individual thermal vias in the

region, A

via

is the cross sectional area of each thermal

via, w is the width of the region, and h is the height of

the region. The relationship between the percentage of

erma and the effective vertical thermal th l vias

conductivity is given by:

K

c]]

z

= mK

u

+ (1 -m)K

Iuc

z

(2)

where K

via

is the thermal conductivity of the via material

and K

layer

z

is the thermal conductivity of the region

without any thermal vias.

The effective lateral thermal conductivity can be found

c using the per entage of thermal vias:

K

c]]

x

= K

c]]

= (1 - m)K

Iuc

IutcuI

+

m

1-m

K

lcjcr

lctcrcl

+

m

K

ic

(3)

More often this lateral thermal conductivity is negligible

value and it may be ignored.

The number of layers in a PCB has a very large impact

on how well heat conducts away. While it is probable

that the layer count of a design will be chosen for

reasons other than thermal mass, this consideration

should not be overlooked by the system designer.

One way to decrease the resistance of each layer is by

increasing the copper weight of the layer. For cost-

sensitive designs, increasing the copper weight provides

an opportunity to get more thermal margin without

having to incur the costs of additional board layers. As is

the case with the number of thermal vias used, there is a

law of diminishing returns for increasing copper weight.

However, even a small change in copper weight has a

large impact on the thermal performance of the PCB.

The effect of adding layers of copper and the impact of

higher copper weight are examined by digital simulation

of 44 vias array in both 2- 4- layer design, as well as

for two copper weight of 0,07 and 0,035mm.

3 Results

When considering the design of the thermal via array, it

is helpful to first identify an ideal structure for the

purpose of heat conduction. After the theoretical ideal is

established, the system designer can attempt to design a

more practical structure that will closely replicate the

ideal structure.

Thermal via densities are increased from their minimum

to maximum values, and the change in the temperatures

and thermal gradients is observed. The thermal via

regions are given the same minimum, midrange, and

maximum thermal conductivity values. The minimum

values correspond to the case where no thermal vias are

RECENT ADVANCES in CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL and SIGNAL PROCESSING

ISSN: 1790-5117 242 ISBN: 978-960-474-139-7

used. The maximum values correspond to maximum

thermal via usage. In the midrange case, thermal via

regions are given thermal via densities that are the

average of the minimum and maximum values. The

temperatures and thermal gradients in the minimum and

maximum cases define the bounds on the thermal values

that can be obtained from adjusting the thermal via

densities. At the midrange with an average thermal via

density of 24% in the thermal via regions, the maximum

temperatures are 47% lower and the average

temperatures are 28% lower than in the case where no

thermal vias are used.

The number and size of the vias are limited by the size

of the thermal pad and the capabilities of the PCB

manufacturer, making their design relatively

straightforward. For reliability in the manufacturing

process, the drill diameter of the vias should be no less

than 0.25 mm, and the center-line of the vias should

remain 0.9 mm away from the edge of the thermal pad

and from each other. It would seem that, since the

purpose of adding this via structure is to replicate a solid

copper slug, the system designer should add as many

vias as possible. However, a law of diminishing returns

makes the addition of a large numbers of vias somewhat

unnecessary.

without vias 4 vias 16 vias

Fig.1. Effect of Number of Vias on PCB

Thermal Resistance (at dissipated power of 1 W)

The effect of adding additional layers of copper can be

seen in Fig. 2. This thermal model was created to predict

the performance of a 4 x 4 via array in a 1-, 2-layer and

3-layer design, given a power dissipated of 1W and 0,04

mm copper layer. The thermal contour indicates that the

heating in the 2-layer design is much more localized into

the device. However, in the 4-layer design, the heat

continues to progress towards the edges of the board.

This is due to the parallel combination of the spreading

resistance of the individual copper layers and the

temperature field is the most equable in the area.

a)one Cu-layer b) two Cu-layer c)3 Cu-layer

Fig.2.Effect of PCB layer count on heat dissipation

The effect of increasing the thickness of the copper

layers is shown in Fig.3. The impact the higher copper

weight has on the spreading resistance is readily seen

from the simulation. These plots show the effects of

higher spreading resistance on the designs with lower

copper weight. The heat flow between the source (the

outer regions of the PCB) and the ambient air is

minimal, and the PCBs capability as a heat sink is

restricted to the small region directly around the device.

thickness 0,04mm thickness 0,08mm thickness1,2mm

Fig. 3. Effect of PCB layer thickness on heat dissipation

Results of thermal simulation show that if thermally

conductive fill material is not a viable option for the

design, the vias can be optimized by specifying the

thickness of the copper covering the internal walls of the

via (Fig.4). If this specification is not directly described

in the specification drawing for the PCB, the thermal

conductivity of the via may be compromised by having a

thin internal wall. It is only necessary to specify a

minimum wall thickness, as any thickness over this

range will only improve the thermal conductivity of the

via. A good starting point is to specify a 0,035mm

copper wall thickness, which should result in no cost

increase to the design since this is a common practice.

Increasing the inner wall thickness beyond this minimum

requirement should be decided based upon the

manufacturing capabilities of the PCB manufacturer.

a) air b) Ni c) Solder Sn63

Fig. 4. Effect of PCB via fill material

On the lower layers of the PCB, it has be greater control

over the routing of the traces. In order to maximize the

thermal performance of the device and PCB structure, it

should keep the traces on the lower layers of the PCB as

far away from the vias array as possible. This ensures

that the solid area of copper under the device is as large

as possible for maximum heat conduction away from the

part. An illustration of this point is found in Fig.5.

The first trace, marked with number 1, runs parallel to

the vias array. As heat flows out of the vias, it

encounters a large thermal resistance created by the trace

cutting across the copper plane. The second trace

RECENT ADVANCES in CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL and SIGNAL PROCESSING

ISSN: 1790-5117 243 ISBN: 978-960-474-139-7

configuration is better than the first because it is as far

away from the thermal via array as possible.

4 Conclusion

Thermal vias are generically added to PCB to achieve

the desired thermal conductivities. The goal is to satisfy

given thermal requirements using as few thermal vias as

possible, i.e., keeping the thermal conductivities as low

as possible. Furthermore, with the thermal via regions

being oriented vertically, lateral thermal vias will have

little effect. The thermal gradients in the vertical (z)

direction are almost two orders of magnitude larger than

in the lateral directions.

Fig.5. Effect of trace location and directions on heat

conduction within the lower PCB layers

This ensures that heat conduction is only limited by the

inherent spreading resistance of the copper layer itself. If

it is not possible to avoid having traces close to the

device, the third routing method can be used to limit the

impact of the traces on heat conduction. Traces running

perpendicular to the center of the device present a

smaller crosssectional profile of thermal resistance to

heat conducting away from the device.

The important thing to remember concerning heat flow

through the PCB and into the ambient is that the thermal

resistance between the heat source and the cooler outer

regions of the PCB must be kept as low as possible.

Acknowledgements

The authors would like to thank for the support of

Bulgarian Ministry of Education SIF under which

contract 1-854/2007 Thermal Management of

Microelectronic Systems, the present work was

conducted

On the Fig. 6 the effect of ambient temperature is shown.

T

A

= 25

0

C T

A

= 60

0

C

Fig.6. Effect on ambient temperature at T

j

=100

0

C

References:

[1] Li R., Optimization of Thermal Via Design

Parameters Based on an Analytical Thermal

Resistance Model, Thermal and Thermomechanical

Phenomena in Electronic Systems, 1998, pp. 475-

480.

jT

is defined as

jT

= (T

j

T

top

)/P

diss

where T

j

and T

top

are

the junction temperature and the temperature at the top

center of the package, respectively.

jT

is often used to

predict the junction temperature at the end user

environment based on the temperature T

top

. The

temperature T

top

can be measured by a IR camera at the

top center of the package and is dependent on the PCB

conductivity [4, 5]. The PCB with higher effective

conductivity will give a lower value of

jT

. The resultant

of

jT

measurement is shown in Fig.7.

[2] Javier T., Density Factor Approach to Representing

Impact of Die Power Maps on Thermal

Management IEEE Transactions on advanced

packaging, vol. 28, No, 4, 2005, pp.28-31.

[3] Andonova A., N. Kafadarova, Application of the

CFD Method for Heat Transfer Simulation,

Proceedings of the ICEST, Macedonia, 2007, pp.87-

90

[4] Andonova A., N. Kafadarova, V. Videkov, S.

Andreev, Investigation of Thermal Conductivity of

PCB, Proceedings of the 32

nd

ISSE, Czeh Republic,

ISBN: 078-80-214-3874-3, 2009.

Sp1:temp 88.6

19.5

40.6 C

20

30

40

[5] Grau M., Al. Bekiarski, P. Venkov, I. Nacheva,

Robot Control with Camera Eye, International

Conference on Communications, Electromagnetics

and Medical Applications (CEMA07), Bulgaria,

2007, pp. 21-24.

Fig. 7. The image of IR FLIR P640 camera shows the

measured values at the top center of the package

(P

diss

= 3W, T

A

= 21,6

0

C, T

j

= 98,3

0

C and

jT

= 3,23

0

C/W)

RECENT ADVANCES in CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL and SIGNAL PROCESSING

ISSN: 1790-5117 244 ISBN: 978-960-474-139-7

You might also like

- PCB Trace Width Calculator - Trace Width vs. Current TableDocument5 pagesPCB Trace Width Calculator - Trace Width vs. Current TableGanesan SNo ratings yet

- Angelina Jolie Shad BalaDocument1 pageAngelina Jolie Shad BalaGanesan S100% (1)

- Predicting Fusing Time of Overloaded PCB Traces Can We Predict It at All - With Douglas Brooks, PHD and Dr. Johannes Adam - ARTECH HOUSE INSIDERDocument12 pagesPredicting Fusing Time of Overloaded PCB Traces Can We Predict It at All - With Douglas Brooks, PHD and Dr. Johannes Adam - ARTECH HOUSE INSIDERGanesan SNo ratings yet

- Final - Radio Technology WuDocument15 pagesFinal - Radio Technology WuGanesan SNo ratings yet

- Gap Analysis of GNSS Receivers and Technology: GSA-227890 GRAMMAR D1.4 Version 1.17Document72 pagesGap Analysis of GNSS Receivers and Technology: GSA-227890 GRAMMAR D1.4 Version 1.17Ganesan SNo ratings yet

- Prepared and Compiled by Govindon Gopalan (Harish)Document1 pagePrepared and Compiled by Govindon Gopalan (Harish)Ganesan SNo ratings yet

- Angelina Jolie VARSHAPHALADocument1 pageAngelina Jolie VARSHAPHALAGanesan SNo ratings yet

- MMIC/RFIC For Receivers Front-End: To Cite This VersionDocument7 pagesMMIC/RFIC For Receivers Front-End: To Cite This VersionGanesan SNo ratings yet

- Installation Guide of AstrotransitDocument3 pagesInstallation Guide of AstrotransitGanesan SNo ratings yet

- 25 Myths About PATENTS Demystified EbookDocument52 pages25 Myths About PATENTS Demystified EbookGanesan SNo ratings yet

- Thermal Management of Visible Leds: Application Bulletin 228Document4 pagesThermal Management of Visible Leds: Application Bulletin 228Ganesan SNo ratings yet

- Rarnasu: Sub: - Contactless Book Scanner RegDocument1 pageRarnasu: Sub: - Contactless Book Scanner RegGanesan SNo ratings yet

- Using PATENTS To Reduce R&D Efforts: First Edition 2016Document31 pagesUsing PATENTS To Reduce R&D Efforts: First Edition 2016Ganesan SNo ratings yet

- Intellectual Property Rights: Handbook OnDocument50 pagesIntellectual Property Rights: Handbook OnGanesan SNo ratings yet

- Unep Pops Nip Belgium 1.englishDocument115 pagesUnep Pops Nip Belgium 1.englishGanesan SNo ratings yet

- New Thermasim™ Online Mosfet Thermal Simulation ToolDocument4 pagesNew Thermasim™ Online Mosfet Thermal Simulation ToolGanesan SNo ratings yet

- A11 MBS (Analyst)Document15 pagesA11 MBS (Analyst)Ganesan SNo ratings yet

- A6 Direct Frequency Response (a-NFX2014)Document41 pagesA6 Direct Frequency Response (a-NFX2014)Ganesan SNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Steel Reinforcement For WallsDocument7 pagesSteel Reinforcement For WallsSurinderPalSinghGillNo ratings yet

- Azuma 2015 Metrologia 52 360Document17 pagesAzuma 2015 Metrologia 52 360Rudolf KiraljNo ratings yet

- Issues in Timing: Digital Integrated Circuits © Prentice Hall 1995 TimingDocument14 pagesIssues in Timing: Digital Integrated Circuits © Prentice Hall 1995 TimingAbhishek BhardwajNo ratings yet

- A Photovoltaic Panel Model in Matlab - FinalDocument7 pagesA Photovoltaic Panel Model in Matlab - FinalLeela KrishnaNo ratings yet

- Whirlpool Arc 6700Document7 pagesWhirlpool Arc 6700MiguelLoureiroNo ratings yet

- 820-3740 Technical OverviewDocument238 pages820-3740 Technical Overviewppjim100% (1)

- Police StationDocument18 pagesPolice StationRuchira SrivastavaNo ratings yet

- TMB 60Document2 pagesTMB 60oac08No ratings yet

- Binary and Decimal Number Systems: Addressing The Network - Ipv4Document3 pagesBinary and Decimal Number Systems: Addressing The Network - Ipv4Mase Astrid C. BarayugaNo ratings yet

- Rosemount 2120 Vibrating Fork Liquid Level SwitchDocument16 pagesRosemount 2120 Vibrating Fork Liquid Level SwitchTariqMalikNo ratings yet

- Authorization For Entering Manual ConditionsDocument15 pagesAuthorization For Entering Manual ConditionsSushil Sarkar100% (2)

- Preliminary Pages FinallyDocument9 pagesPreliminary Pages FinallyMark Kian ProfogoNo ratings yet

- Msamb Rules and Japan GuidelinesDocument3 pagesMsamb Rules and Japan GuidelineslawrgeoNo ratings yet

- Cop - CannyDocument3 pagesCop - CannyAlaa Layas0% (1)

- VarmaDocument86 pagesVarmanandy39No ratings yet

- AD Merkblatt 2000 CodeDocument4 pagesAD Merkblatt 2000 CodeoscartttNo ratings yet

- Information: Reading Images - The Grammar of Visual DesignDocument5 pagesInformation: Reading Images - The Grammar of Visual DesignAndang Prasetya Adiwibawa BernardusNo ratings yet

- WOWMini WW2 RulebookDocument36 pagesWOWMini WW2 RulebookBrett Michael ChinchenNo ratings yet

- AZ-Edit User ManualDocument288 pagesAZ-Edit User Manualdjjd40No ratings yet

- 21CS8133 Labassignment1Document7 pages21CS8133 Labassignment1Sai PraneethNo ratings yet

- All Code ListsDocument3,292 pagesAll Code ListsshanzNo ratings yet

- WS 4 Minutes - 2.9.2019Document3 pagesWS 4 Minutes - 2.9.2019Andrea KakuruNo ratings yet

- Accident Alert With Automatic DialerDocument39 pagesAccident Alert With Automatic Dialersenanath8100% (1)

- Airtag Wallet Keyword Search-2Document15 pagesAirtag Wallet Keyword Search-2Azhar ShakeelNo ratings yet

- Lit MotorsDocument11 pagesLit MotorsJohnson7893No ratings yet

- Punjab ULBRFPVolume IAttachmentdate 21 Nov 2016Document214 pagesPunjab ULBRFPVolume IAttachmentdate 21 Nov 2016NishantvermaNo ratings yet

- O I - LT3 - HP3 - User - 02Document14 pagesO I - LT3 - HP3 - User - 02Francisco AvilaNo ratings yet

- Comsol Acdc RF 42aDocument71 pagesComsol Acdc RF 42aneomindxNo ratings yet

- 378 and 378 HT SeriesDocument2 pages378 and 378 HT SeriesTim Stubbs100% (2)

- Settle 3 DDocument2 pagesSettle 3 DSheril ChandraboseNo ratings yet