Professional Documents

Culture Documents

1 s2.0 S0142061510001523 Main

Uploaded by

AnWar MustaFaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1 s2.0 S0142061510001523 Main

Uploaded by

AnWar MustaFaCopyright:

Available Formats

Solid-state tap-changer of transformers: Design, control and implementation

Jawad Faiz

, Behzad Siahkolah

Center of Excellence on Applied Electromagnetic Systems, School of Electrical and Computer Engineering, University of Tehran, Tehran 1439957131, Iran

a r t i c l e i n f o

Article history:

Received 28 April 2009

Received in revised form 5 July 2010

Accepted 13 August 2010

Keywords:

Transformer

Electronic tap-changer

Hardware

a b s t r a c t

This paper presents the implementation of a prototype electronic tap-changer of transformer. Mechanical

tap-changer has many problems such as low operating speed, short lifetime and heavy size. In order to

solve these problems a fully solid-state tap-changer with a new control strategy and optimal congura-

tion is proposed. The design of tap-changer is discussed and bi-directional solid-state power electronics

switches are implemented. Following the realization of the tap-changer controller, developed software

for such precise control is introduced. To verify the design procedure and optimal conguration and apply

the developed software, a prototype low-power tap-changer has been built and tested.

2010 Elsevier Ltd. All rights reserved.

1. Introduction

Normally the main objective of a tap-changer is to regulate and

adjust the output voltage of transformer [1]. The voltage uctua-

tion springs from the load changes. Sometimes tap-changer in

power transformer is used to shift the phase angle [2,3]. An on-load

tap-changer (OLTC) enables to change the taps under load and it is

utilized where a short period of time is required for such changes.

In an OLTC impedance is added to circuit in order to prevent the

short circuit during the tap-changing process while the load cur-

rent passes the load when tap-changer operates.

The main advantage of a reactive OLTC is that the reactor stands

continuous load current. However, this type of tap-changer has

some disadvantages including low operating speed, large arcs,

shorter lifetime and heavy size [4]. Therefore, it is obsolete now.

Due to the above-mentioned drawbacks, reactive tap-changers

are almost replaced by resistive tap-changers. In spite of progress

made in the structure of mechanical OLTC, they have some limita-

tions and considerable drawbacks, as such that major fault in

power transformers springs from the tap-changer fault [5]. Some

limitations and drawbacks of mechanical OLTC include arc in con-

tacts, high cost of maintenance, low speed of operation and high

losses [6]. The main function of the controller in the tap-changer

system is to minimize the uctuations (rising and falling) of the

voltage amplitude in comparison with the reference voltage at

the point called the regulation bus. The regulation bus may be

far from the secondary of transformer. In the other words, the main

objective of the controller is to keep the amplitude of the bus volt-

age within a dened range [7]. Of course, in addition to the main

function, the tap-changer controller may control the tap-changer

during critical cases such as over-loads, output short-circuits, tran-

sient over-voltages of input and tap-changer damage. In order to

preserve power system integrity in emergency conditions, the taps

of transformer can be moved and locked to predetermined position

or voltage set-point [8]. The controller may also make the neces-

sary decision to protect the tap-changer system and its loads. To

remove these limitations and drawbacks, new circuits and struc-

tures for OLTC have been so far suggested [16]. They are catego-

rized into two main groups:

1. Electronically assisted OLTC [912].

2. Solid-state OLTC [1322].

In the 1st group, solid-state power switches have been em-

ployed beside mechanical switches in order to reduce the arc. In

the 2nd group, there are no mechanical parts and they have been

totally built by solid-state power switches. The advantages of the

latter group of OLTC are very low maintenance cost, high operating

speed, and possibility of tap jumping and high performance.

Although several ideas have been so far introduced to realize the

totally solid-state tap-changer, there is no any versatility in these

ideas. It is not clear that which ideas is suitable for a dene applica-

tion. Basically which structures are optimal or what is an optimal

conguration. The above-mentioned functions for the tap-changer

controller are expected for any mechanical and electronic tap-chan-

ger. However, it is noted that there are fundamental differences be-

tween the capabilities and characteristics of mechanical and

electronics tap-changers [23,24]. So, if the same conventional con-

troller of a mechanical tap-changer is used for an electronic tap-

changer system, many capabilities and features of the electronic

tap-changer will not be realized.

0142-0615/$ - see front matter 2010 Elsevier Ltd. All rights reserved.

doi:10.1016/j.ijepes.2010.08.016

Corresponding author. Tel.: +98 21 88003330; fax: +98 21 88633029.

E-mail address: jfaiz@ut.ac.ir (J. Faiz).

Electrical Power and Energy Systems 33 (2011) 210218

Contents lists available at ScienceDirect

Electrical Power and Energy Systems

j our nal homepage: www. el sevi er . com/ l ocat e/ i j epes

The authors have reviewed the differences between the tap-

changing processes in both types of the tap-changers, and de-

scribed the differences. Some modications in the conventional

controllers used in the mechanical tap-changers structure have

then been applied and a general structure for electronic tap-chang-

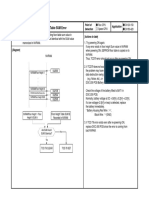

ers is suggested [2527]. Fig. 1 shows such a modied controller.

In a series of papers an attempt has been made to classify the

introduced ideas in OLTC in a logical manner. Then the cost of

tap-changer has been taken as an objective in order to introduce

an optimal structure. Following this selection, other requirements

such as switching technique for a proper commutation, controlling

and detecting fall and rise of voltage have been applied and nally

it has been built and tested [2834]. In [30] criteria for optimal

conguration of transformer windings as well as power electronic

switches are proposed for design and implementation of low-

power electronic tap-changer. The aims in this optimization in-

clude minimization of: (1) number of switches and their voltages

and currents, (2) number of taps in transformer, (3) number of

voltage steps and (4) deviation of amplitude of voltage compared

with the reference voltage in the regulation bus. Present paper de-

scribes the developed software for realization of the electronic tap-

changer. The hardware and software are then used to build a sin-

gle-phase low-power prototype 5 kVA electronic tap-changer.

The test results for this prototype are also presented and compared

with the simulated results and good agreements are achieved. This

shows the advantages of the proposed electronic tap-changer over

mechanical tap-changer.

Although a single-phase tap-changer is investigated in this pa-

per, it can be extended into three-phase version taking into ac-

count the structure of the transformer. If tap-changer is xed in

the star-connected side of the three-phase transformer, this exten-

sion can be easily implemented, because the phase voltage is easily

measured. However, this can be also implemented in the D-con-

nected case with some modications. However some design con-

siderations such as bi-directional switches conguration, current

commutation between them and control loop in any phase can

be exactly applied. Of course, algorithm of amplitude and phase

angle measurements must be largely changed compared with the

single-phase version

Section 2 points out the design of taps winding structure and

switches arrangements. Bi-directional solid-state switches used

in OLTC are described in this section. In Section 3, more explana-

tion of each block shown in Fig. 1 is given and their design proce-

dures are discussed. In Section 4, the developed software for

controlling an electronic tap-changer is introduced and a method

for converting the difference between the output voltage of the

transformer and the reference voltage (DV) into the tap-number

and switch commands. Section 5 presents the experimental re-

sults. Finally, Section 6 concludes the paper. It is noted that up to

now the required software in the microprocessor board has not

been proposed in the literature and this paper is mainly focused

on the detailed requirement of such software.

2. Designing taps winding structure and solid-state switches

arrangement

There are two following major parameters that determine the

cost of an OLTC: (1) number of solid-state power switches and

their voltages and currents and (2) number of taps because any

tap needs insulating and special insulator. The main objectives of

OLTC design consists of:

1. Minimizing number of solid-state switches and their currents

and voltages.

2. Minimizing the taps number.

3. Maximizing voltage steps over output voltage regulation range

for precise regulating.

Of course, there are some other objectives beside the above-

mentioned objects such as lower losses, higher reliability, lower

short circuit current and over-voltage. Design of taps winding

structure was proposed in [23]. Selecting voltage of any section

of windings in the taped-winding was given in [24]. The switches

arrangement leading to the maximum achievable number of volt-

ages was discussed in [27]. The optimal topology without and with

taking into account the voltage and current of the switches was

proposed in [23].

Solid-state switches are the most important element of an elec-

tronic OLTC which are bi-directional switches due to their ac volt-

age and current [34]. The bi-directional switches used are two

common emitter IGBTs in series with reversed diodes. Strategy of

switches control is based on the current direction [24,28]. A com-

bination of solid-state switches is employed in order to realize a bi-

directional switch. Switch-on losses in the bi-directional switches,

current commutation between these switches based on the voltage

and current direction, design of terminals snubber capacitor of

OLTC, different switches modulation in tap-changer and no-modu-

lation case are the major problems that are proposed in [2834]. To

realize the proposed electronic tap-changer a single-phase proto-

type low-power tap-changer was designed, built and tested as de-

scribed in [30].

3. Electronic tap-changer controller

The main blocks of Fig. 1 are described in this section.

3.1. Measurement and calculation block for rms value

In a mechanical tap-changer, the method shown in Fig. 2 is used

for measuring the rms voltage of the regulation bus, where the

Fig. 1. Schematic of the proposed electronic tap-changer based on a modied conventional controller used in a mechanical tap-changer.

J. Faiz, B. Siahkolah/ Electrical Power and Energy Systems 33 (2011) 210218 211

minimum delay of the low-pass lter is equivalent to 0.45 s or 20

cycles of the operating frequency. The process of tap-changing in a

mechanical tap-changer system is a slow process, but the delay

introduced does not produce a serious problem. However, an

electronic tap-changer operates fast and a real-time measurement

of the rms value of the regulation bus is expected. This is the rea-

son that the averaging concept of rms voltage cannot be used. One

of the best substitutions for the rms value of the voltage is the

instantaneous rms value of the voltage. Fig. 3 shows the block dia-

gram of this method.

Referring to Fig. 3, the rms value of instantaneous voltage can

be expressed as follows:

V

2mrms

t

1

T

Z

t

0

V

2

2m

t

0

V

2

2m

t

0

Tdt

0

s

1

T

Z

t

0

V

2

2m

t

0

dt

0

s

1

where T is the period of signal V

2m

(t), which is half of supply fre-

quency (10 ms). The response of the rms voltage detecting block

(for a = 10) and rms detecting with a low-pass lter (the conven-

tional method) for a step change of the sinusoidal function has been

shown in Fig. 4. The rms value of the instantaneous voltage is a very

useful value for the controller of the electronic tap-changer. This va-

lue contains the data of a half cycle of the waveform and measures

the variations of the output voltage amplitude over a maximum

period of 10 ms. For 50 Hz supply the full period is 20 ms and the

period of the rectied V

2m

(t) will be 10 ms (20 ms divided by 2). If

the supply frequency is slightly changed, by measuring the time be-

tween the voltages of zero-crossing in hardware system, this

change is measured and the measured time is used in the software.

Obviously transformer and tap-changer is designed for 50 Hz and

large change of the frequency not only affects the tap-changer but

also can seriously damage the transformer.

) (

1

10 ) ( ) (

1

2

2

X

ST

ms T X t V

m

=

Fig. 3. Block diagram of system for measuring rms value of instantaneous voltage of regulation bus in an electronic tap-changer.

Fig. 4. (a) Main signal, (b) response of rms detecting block (for a = 10) and (c) rms response of detecting with low-pass lter (conventional method) for step change of

sinusoidal function.

2 1 2

2

2

) (

/ 1

1

) ( ) ( X

a s

X t V

m

+

Fig. 2. Block diagram of system for measuring rms voltage of regulation bus in a mechanical tap-changer.

212 J. Faiz, B. Siahkolah/ Electrical Power and Energy Systems 33 (2011) 210218

3.2. Dead-band block

A dead-band (DB) is inserted after the DV calculation due to the

intrinsic limit of the tap-changer system and the discontinuity of

the system. This dead-band is always necessary. In the mechanical

tap-changer, DV reaches the saturation values of +1 and 1 after

passing from the dead-band block to the saturation block, because

it is only possible to change any tap to a higher or lower tap. How-

ever, in the electronic tap-changer, it is possible to jump from one

tap to another and there is no need for a saturation block.

It has been shown [7] that if the controller system is designed

such that DB is a xed parameter, then it must satisfy the following

condition:

2DB > V

2stepMax

2

where V

2StepMax

is obtained as follows:

V

2StepMax

V

2Max

a

0

Da

a

0

1 2n

max

1

Da

a

0

3

where n

max

is the maximum tap number, a

0

is the turn ratio of the

transformer and Da is the step variations of a with varying one

number in the tap. V

2Max

is the maximum voltage of the secondary.

It is noted that if condition (2) is not satised in determining DB,

oscillations will occur in the control loop.

3.3. Compensating block

On the contrary to a mechanical tap-changer, an electronic tap-

changer is a rapid system. Therefore, the compensator used in the

electronic tap-changer must be designed more carefully such that

it satises the control loop requirements and at the same time does

not slow down the system. So, a general compensating block is

used instead of a delay block, which is a special type of

compensator.

In [7], it has been shown that the use of an integrator in the

compensating block of an electronic tap-changer seems interesting

from a quality point of view. The integrator produces typically the

delay proportional with DV and it also has memory. Meanwhile,

the integrator extends the steady-state error to the minimum pos-

sible value. The integrator gain inuences the stability and also the

speed of the system. If the gain factor of this block is large, it causes

the oscillation of the control loop, and if the gain is too small, it

slows down the loop operation.

3.4. Quantizer, sampler, keeper and detector of zero-crossing and look-

up table

Since the row number of tap is an integer, a quantizer block

must be included. The range of the quantizer block output is be-

tween the maximum (+n

max

) and the minimum (n

max

) row num-

ber of tap. The reason for using the sample and hold block and also

the zero-crossing detector is that the tap position is allowed to be

changed only during the instants of the zero-crossing of current.

The reason for adding the look-up table is that any row of the num-

ber corresponds to a particular position of the switches, and the

position of the switches has already been stored in the memory

of the look-up table for later use.

The inputoutput characteristic block is shown in Fig. 5. The

output of the quantizer block is the row number of the tap. It is

clear from Fig. 5 that the system is non-continuous.

4. Software development

This section presents the developed software used in the micro-

processor briey.

4.1. General strategy for software design

Fig. 6 shows the block diagram of the electronic tap-changer

from a control point of view. The designed software in the micro-

processor is fully realized in the control part of the block diagram.

Output

1 2 3 -1

n

Max

-2 -3

1

2

1-

2-

n

Max

input

-n

Max

-n

Max

Fig. 5. Inputoutput characteristic of quantizer block.

Tapped transformer

and

switches connected

to taps

Detecting zero

crossing load

current

Converting

V

to tap number

Switches positions

considering V

Tap-changer

switches

command

Input

voltage

l

o

a

d

v

o

l

t

a

g

e

l

o

a

d

c

u

r

r

e

n

t

Output

voltage

V

Vrem

+

V

ref

=220 V

Sampling load

voltage and

computation of

rms value

c

o

n

t

r

o

l

s

e

c

t

i

o

n

Fig. 6. Block diagram of the electronic tap-changer from control point of view.

J. Faiz, B. Siahkolah/ Electrical Power and Energy Systems 33 (2011) 210218 213

It is noted that the controller block in Fig. 6 is the block converting

DV to tap number.

In order to convert the voltage and load current signals into

desired signals for the control system, three rectied full-wave

voltages in-phase with the load voltage, three rectied full-waves

in-phase with the load current, a square wave voltage in-phase

with the load voltage and a square wave voltage in-phase with

the load current are produced using an analogue processor board

(Fig. 7). Relation of load voltage and load current with the afore-

mentioned signals are presented in Fig. 8.

The reason for generating the three rectied signals from volt-

age (or current) covers a wider range of voltage with suitable accu-

racy. In the present paper, a single-phase prototype 220 V/220 V

transformer equipped with an electronic tap-changer has been dis-

cussed. If a load voltage signal of peak amplitude up to 350

p

2 is

covered, the ratio 350

p

2/5 = 99 must be used, while the load volt-

age peak is frequently around a rated value of 220

p

2 V. So by the

above ratio, the input signal A/D has an amplitude equal to 220

p

2/

99 = 3.14, while the amplitude of the input voltage of the A/D con-

verter of up to 5 V is permissible. This is the reason for using three

ratios, where one converts peak amplitude of 250

p

2 V into 4.5 V,

another 300

p

2 V into 4.5 V and the last one 350

p

2 V into 4.5 V.

Therefore, if in reading a channel of the A/D, the amplitude of

the voltage of one channel exceeds 4.5 V, sampling will be carried

out from another channel in order to keep the accuracy and read

the larger voltage. This is also true for current. The reason to pro-

duce digital signals in-phase with voltage and current is that when

rectifying full-wave voltage and current, the zero-crossing infor-

mation of these signals is eliminated (crossing from negative val-

ues to positive or vice-versa). This information exists in the

digital voltage and current signals and they are entered into the

micro-controller. The major feature of voltage and current digital

signals is that the edges of two signals determine the location of

zero-crossing voltage and load current. This is useful information

and may be more important than the rst feature. In particular,

the zero-crossing of current is required for switching at zero cur-

rent. Thus, digital voltage and load current signals contain informa-

tion about the time of zero-crossing of the voltage and load

current.

The general strategy for designing the software is based on the

following:

(1) Using the edge of the digital voltage for:

(a) Calculating the length of half the period of the load voltage

and consequently evaluating load voltage frequency (f);

(b) Measuring the frequency;

Fig. 7. Inputs and outputs of analogue processor board.

Load

voltage

t

Load

current

t

rectified

voltages

t

+5 v

Digital

voltage

+5V

t

Rectified

currents

t

+6 V

Digital

Current

5V

t

+5V

2 220

Fig. 8. Typical waveforms of input and output of analogue processor board.

214 J. Faiz, B. Siahkolah/ Electrical Power and Energy Systems 33 (2011) 210218

(c) Starting regular sampling of the voltage and current dur-

ing a half-period over the following time intervals:

t

samp

T

2

nsamp

2

4

where T/2 is the interval between two successive crossings of zero

voltage, t

samp

is the time between two successive samples of the

analogue signals and n

samp

is the sample number during a complete

cycle of the input voltage.

(d) Calculating the load power factor.

(2) Use the edge of digital current for:

(a) Calculating the load power factor;

(b) Applying switch commands to achieve zero current

switching.

The control system is implemented by taking all the above-

mentioned points into account. Using every edge, the half-period

time, which is now ended, is computed. This block does the sam-

pling, calculates the rms value edge, the time of the half-period

that has just ended is evaluated and t

samp

is then obtained by (4).

Now the block responsible for regular sampling of voltage and cur-

rent, evaluates DV and then converts it into a tap number.

Having the current edge, the load power factor is calculated and

the switch commands are applied. The high speed input (HSI) block

detects the edges of digital voltage and current, while the high

speed output (HSO) block programs the sampling interval (starting

the A/D at regular time intervals). Calculation of the rms value and

the conversion of DV into the tap number is carried out at the in-

stant of every voltage sample and pause routine the A/D. The dig-

ital voltage signal synchronizes the operation of the system. Every

edge of this signal indicates the end of a half cycle of voltage and

the start of the next half cycle. The necessary calculations, sam-

pling and evaluating required over the new half cycle is carried

out and programmed. So, in practice the HIS routine undertakes

the control programming. The HSO starts the A/D over a half cycle

in suitable time intervals and does this in parallel with the pro-

gram. The A/D pauses at the end of a conversion, after any sample

is taken by the A/D. The pause routine of the A/D then calculates

the rms value and DV and converts DV into the tap number. The

HSI block applies the switch commands corresponding with the

calculated tap number in A/D routine to the switch drivers at the

instant of detecting the current edge.

Based on the above, it is clear that the system is controlled by

the HSI pause routine, HSO block and pause block A/D. Thus, all

jobs are carried out in parallel with the main software program.

4.2. Converting DV into a tap number and switch commands

A curve that converts the value of DV(=V

ref

V

rms

) into the tap

number is a step curve with the hysteresis shown in Fig. 8. In this

gure, the width of the steps is 2a and the value of each curve over

every range, (2k1)a, a, (2k + 1)a, is a constant value of the tap

number k. The range of variation for k is: 24, 23, . . . , 0, . . . , 24.

As shown in Fig. 9, the hysteresis width is 2DV

offset

. Therefore:

For rising DV : T k; DV 2 2k 1a DV

offset

; 2k 1a DV

offset

5

For falling DV : T k; DV 2 2k 1a DV

offset

; 2k 1a DV

offset

6

For values of DV in the range of |DV| > (2k

max

+ 1)a, the curve va-

lue saturates and remains equal to its value at |k| = 24. Based on the

above explanation, in order to introduce the curve, it sufces that

the width of the step (DVSW = 2a) be the hysteresis value

(DVOFF = DV

offset

) and the maximum tap number (KMAX = k

max

) is

introduced to the program.

To prevent the use of the negative numbers, the curve is shifted

to the right by (2k

max

+ 1) on the horizontal axis and to the upper

side by k

max

on the vertical axis, so Fig. 10 is obtained. Therefore,

x is computed instead of DV and the value of SWPN is obtained

from this curve. In such a case the actual value of T is equal to

SWPN k

max

. Fig. 11 shows the block diagram of the process of

converting DV to the tap number. The low-pass lter is introduced

to the system with a cut-off frequency of A3 dB. To realize the low-

-a -3a -5a

2

-1

-2

-23

-24

1

2

2

49 47 45 5a 3a a

2 Voffset

Fig. 9. Hysteresis curve converting DV into tap number.

2 V

offset

2

1

4

4

8a 6a 4a 2a

(

2

k

m

a

x

-

1

)

2

a

(

2

k

m

a

x

)

2

a

(

2

k

m

a

x

+

1

)

2

a

3

Fig. 10. Shifted curve of Fig. 8 for preventing the use of negative numbers.

J. Faiz, B. Siahkolah/ Electrical Power and Energy Systems 33 (2011) 210218 215

pass lter, a trapezoidal model is used, which leads to a higher

accuracy. In this model, in addition to the input value at instant

t, an input and output at t 1 is also required. The spaces DV

and DV1 are assigned for this purpose.

Applying hysteresis is carried out such that the new SWPN is

compared with the old value, then:

1. If SWPN was not changed, hysteresis is not applied.

2. If SWPN was reduced, its value is modied using DVOFF.

3. If SWPN was increased, its value is modied using DVOFF.

Every tap number is equivalent with a specic on and off pat-

tern of the switches of the system. Table 2 shows the pattern cor-

responding with each number. This table is introduced as look-up

table to the micro-controller by the name of SEPO.

5. Experimental results

A prototype electronic tap-changer for a low-power transformer

have been constructed and tested. Specications of this tap-chan-

ger are summarized in Table 1. The test results for open-loop and

closed-loop cases will be presented below.

5.1. Open-loop control

The power circuit of the device and also command signals gen-

erated in the controller are tested and their performances are stud-

ied. For the open-loop case, a test software was developed, which

applies the tap number from the minimum value (24) and then

one number is added in every cycle (at the incident edge of digital

voltage signal) until the tap number becomes zero. At the zero tap

number, three cycles are paused and then the trend of re-increas-

ing the tap number continues from zero to the maximum value

(+24). If the tap approaches +24, the tap number jumps to 24.

Fig. 12 shows the output voltage waveform of the tap-changer

for the on-load case of the above-mentioned test software and

the load current equal to 5 A. According to this gure, 49 different

states for the output voltage are visualized. The linear steps of the

output voltage are also clear in the gure. The capability of jump-

ing from the highest tap number to lowest tap number has been

presented. A voltage drop of 1% can be visualized.

x=V+(2k

max

+1) a

A Applying

H Hysteresis

Tap No. = SWPN-k

max

Intermediate

SWPN

x

V

F Final

S SW WP PN N

t= Tap No.

Fig. 11. Block diagram of the process of transforming DV to the tap number.

Table 1

Specications of proposed electronic tap-

changer.

Number of phase 1

Regulated rms output voltage 220 V

Input rms voltage 220 V

No. of voltage steps 48

Step voltage for rated input 2 V

Maximum output current 20 A

Output power 5 kVA

Table 2

Position of one-by-one switches corresponding with every tape number.

No. Switches positions V

out

210

(V)

S

1

S

1

S

2

S

2

S

3

S

3

S

4

S

4

S

5

S

5

S

6

S

6

1 0 1 0 0 1 0 0 1 0 0 1 0 48

2 0 0 0 1 1 0 0 1 0 0 1 0 46

3 0 1 1 0 0 0 0 1 0 0 1 0 44

4 1 1 0 0 0 0 0 1 0 0 1 0 42

5 1 0 0 1 0 0 0 1 0 0 1 0 40

6 0 0 1 0 0 1 0 1 0 0 1 0 38

7 1 0 0 0 0 1 0 1 0 0 1 0 36

8 0 1 0 0 1 0 0 0 0 1 1 0 34

9 0 0 0 1 1 0 0 0 0 1 1 0 32

10 0 1 1 0 0 0 0 0 0 1 1 0 30

11 1 1 0 0 0 0 0 0 0 1 1 0 28

12 1 0 0 1 0 0 0 0 0 1 1 0 26

13 0 0 1 0 0 1 0 0 0 1 1 0 24

14 1 0 0 0 0 1 0 0 0 1 1 0 22

15 0 1 0 0 1 0 0 1 1 0 0 0 20

16 0 0 0 1 1 0 0 1 1 0 0 0 18

17 0 1 1 0 0 0 0 1 1 0 0 0 16

18 1 1 0 0 0 0 0 1 1 0 0 0 14

19 1 0 0 1 0 0 0 1 1 0 0 0 12

20 0 0 1 0 0 1 0 1 1 0 0 0 10

21 1 0 0 0 0 1 0 1 1 0 0 0 8

22 0 1 0 0 1 0 1 1 0 0 0 0 6

23 0 0 0 1 1 0 1 1 0 0 0 0 4

24 0 1 1 0 0 0 1 1 0 0 0 0 2

25 1 1 0 0 0 0 1 1 0 0 0 0 0

26 1 0 0 1 0 0 1 1 0 0 0 0 2

27 0 0 1 0 0 1 1 1 0 0 0 0 4

28 1 0 0 0 0 1 1 1 0 0 0 0 6

29 0 1 0 0 1 0 1 0 0 1 0 0 8

30 0 0 0 1 1 0 1 0 0 1 0 0 10

31 0 1 1 0 0 0 1 0 0 1 0 0 12

32 1 1 0 0 0 0 1 0 0 1 0 0 14

33 1 0 0 1 0 0 1 0 0 1 0 0 16

34 0 0 1 0 0 1 1 0 0 1 0 0 18

35 1 0 0 0 0 1 1 0 0 1 0 0 20

36 0 1 0 0 1 0 0 0 1 0 0 1 22

37 0 0 0 1 1 0 0 0 1 0 0 1 24

38 0 1 1 0 0 0 0 0 1 0 0 1 26

39 1 1 0 0 0 0 0 0 1 0 0 1 28

40 1 0 0 1 0 0 0 0 1 0 0 1 30

41 0 0 1 0 0 1 0 0 1 0 0 1 32

42 1 0 0 0 0 1 0 0 1 0 0 1 34

43 0 1 0 0 1 0 1 0 0 0 0 1 36

44 0 0 0 1 1 0 1 0 0 0 0 1 38

45 0 1 1 0 0 0 1 0 0 0 0 1 40

46 1 1 0 0 0 0 1 0 0 0 0 1 42

47 1 0 0 1 0 0 1 0 0 0 0 1 44

48 0 0 1 0 0 1 1 0 0 0 0 1 46

49 1 0 0 0 0 1 1 0 0 0 0 1 48

216 J. Faiz, B. Siahkolah/ Electrical Power and Energy Systems 33 (2011) 210218

5.2. Closed-loop test

The performance of the power circuit, switch drivers and the

generation of the command signals of the controller are veried

by the open-loop test. The capabilities of the control system for

output regulation are studied by means of the closed-loop test.

The closed-loop performance will be presented for line and load

voltage regulation.

5.2.1. Line regulation

The purpose of line regulation is to stabilize the output voltage

against input voltage uctuations. In this case, the load current is

xed. Fig. 13 shows the output voltage waveform of the tap-chan-

ger for the input voltage equal to 241 V and the no-load case. The

tap number in the gure is 24. It is clear from this input voltage,

the output voltage remains constant. Fig. 14 shows the tap-changer

output voltage for on-load current equal to 5 A and input voltage

241 V. The tap numbers in these cases are evident from the gures.

Thus far, the static line regulation has been studied. To investi-

gate the dynamic line regulation and transient states, the input

voltage is quickly varied by means of an auto-transformer. In all la-

ter tests the integrator factor is set to 10, unless another value is

mentioned. The output voltage waveform for quick input voltage

variations with the lter inserted has been obtained and shown

in Fig. 15. It is clear that inserting this lter leads to a second-order

closed-loop system and there is a small oscillation. Fig. 16 shows

the tap-changer output voltage waveform for integrator factor

equal to 50, as seen at the output voltage uctuates.

As shown in [30], the output voltage can be easily regulated

against sudden changes of the load at a xed input voltage. It

means that the scheme is stable and reliable under transient load

uctuations.

6. Conclusions

The design stages of a fully electronic tap-changer were pre-

sented in this paper. This included the design of the power circuit,

aspects relating to its control and software design. The simulation

results of a prototype low-power (5 kVA) electronic tap-changer

were also presented and a prototype built and tested. The experi-

mental results veried the design procedure in both hardware

and software parts. The prediction and simulation results agreed

well with the test results. If the cost of high voltage and high cur-

rent power electronics devices decrease considerably and the prop-

er protection equipment employed, the tap-changer with a similar

structure can be fully used in distribution systems as described in

[8].

Fig. 12. Tap-changer output voltage waveform for 5 A load and the test software:

vertical axis scale: 175 V and horizontal axis scale: 0.1 s [30].

Fig. 13. Tap-changer output voltage waveform for input voltage 241 V and no-load

case: vertical axis scale: 220 V and horizontal axis scale: 0.05 s [30].

Fig. 14. Tap-changer output voltage waveform for input voltage 241 V and 5 A load:

vertical axis scale: 220 V and horizontal axis scale: 0.05 s [30].

Fig. 15. No-load output waveform for sudden increase of input voltage from 170 V

to 220 V with low-pass software lter: vertical axis scale: 220 V and horizontal axis

scale: 0.1 s [30].

Fig. 16. Output voltage waveform for integrator factor equal to 50: vertical axis

scale: 220 V and horizontal axis scale: 0.1 s [30].

J. Faiz, B. Siahkolah/ Electrical Power and Energy Systems 33 (2011) 210218 217

References

[1] IEEE Standard Dictionary of Electrical and Electronics Terms. 3rd ed.; 1894. p.

9189.

[2] Gebert KL, Edwards KR. Transformers 1974:20721.

[3] Central Station Engineers of the Westinghouse Electric Corporation. Electrical

transmission and distribution reference book. p. 1214.

[4] Austen Stigant S, Franklin AC. The J & P Transformer Book. 10th ed.

Butterworth; 1976. p. 22767.

[5] Kang P, Birtwhistle D. Condition assessment of power transformer on-load tap-

changers using. IEEE Trans Power Deliv; 2003.

[6] Gao D, Lu Q, Luo J. A new scheme for on-load tap-changer of transformers. In:

International conf on power system technology, 2002, Power Con; 2002. p.

101620.

[7] Shuttleworth R, Tian X, Fan C, Power A. New tap changing scheme. IEE Proc

Electr Power Appl 1996;143(1):10812.

[8] Capitanescu F et al. Decentralized tap-changer blocking and load shedding

against voltage instability: prospective tests on the RTE system. Int J Electr

Power Energy Syst 2009;31:5706.

[9] Robert ME, Ashman WG. A thyristor assisted mechanical on-load tap-changer.

In: IEE Proc power thyristors and their applications; 1969. p. 18592.

[10] Cooke GH, Williams KT. Thyristor assisted on-load tap-changers for

transformers. In: Fourth international conf on power electronics and

variable-speed drives; 1990. p. 12731.

[11] Cooke GH, Williams KT. New thyristor assisted diverter switch for on-load

transformer tap-changers. IEE Proc Electr Power Appl 1992;139(6):

50711.

[12] Shuttleworth R, Power A, Tian X, Jiang H, Alzahawi BA. A novel thyristor-

assisted tap-changer scheme. In: IEE 14th international conf on electricity

distribution, vol. 1; 1997. p. 28/15.

[13] Musgrave G, OKelly D. Improvement of power system transmission by solid-

state techniques. In: IEE conf pub, vol. 123; 1974. p. 22833.

[14] OKelly ] D, Musagrave G. Improvement of power system transient stability

limits. Proc IEE 1973 1997;120(2):24753.

[15] Y-Zai FQ, QKelly D. Solid-state on-load transformer tap-changer. IEE Proc

Electr Power Appl 1996;143(6):48191.

[16] Larsson T, Innanen R, Norstrom G. Static electronic tap-changer for electric

machines and voltage control. In: IEEE fast phase and drives conf; 1997. p. TC3/

4.14.3.

[17] Degeneff RC. A new concept for a solid-state on-load tap-changer. In: IEE conf

pub no. 438, vol. 1; 1997. p. 7/14.

[18] Dernirci O, Torrey DA, Degeneff RC, Schaeffer FK, Frazer R. A new approach to

solid-state on-load tap-changing transformers. IEEE Trans Power Deliv

1998;13(3):95261.

[19] Bauer P, deHaan SWH. Electronic tap changer for 500 kVA/10 kV distribution

transformers: design, experimental results and impact in distribution

network. IEEE IAS 1998;2:15307.

[20] Bauer P, deHaan SWH, Paap GC. Solid-state control for transformer tap

changing, PEMC 1996, Budapest; 1996. p. 3944.

[21] Bauer P, deHaan SWH. Electronic tap-changer for 10 kV distribution

transformers. EPE 1997;97:3/10105.

[22] Bauer P, de Haan SWH. Protective device for electronic tap-changer for

distribution transformers. EPE 1997;97:4/2827.

[23] Faiz J, Siahkolah A. Optimal congurations for taps of windings and power

electronics switches in electronic tap-changers of power transformers. Proc

IEE, Pt. C. 2002;149(5):51724.

[24] Faiz J, Siahkolah B. New solid-state on-load tap-changers topology for

distribution transformers. IEEE Trans Power Deliv 2003;18(1):13641.

[25] Faiz J, Siahkolah B. Effect of solid-state on-load distribution tap-changer on

power quality enhancement. Int J Eng, IR Iran 2004;17:14356.

[26] Faiz J, Siahkolah B. Sag mitigation by an electronic tap-changer: specications

and comparisons with other custom power tools. IEE, Pt. C

2005;152(5):697704.

[27] Faiz J, Siahkolah B. Differences between conventional and electronic tap-

changers and modications of controller. IEEE Trans Power Deliv

2006;21(3):13429.

[28] Faiz J, Siahkolah B. New controller for an electronic tap-changer part I: design

procedure and simulation results. IEEE Trans Power Deliv 2007;22(1):2239.

[29] Faiz J, Siahkolah B. New controller for an electronic tap-changer part II:

measurement algorithm and test results. IEEE Trans Power Deliv

2007;22(1):2307.

[30] Faiz J, Siahkolah B. Implementation of a low power electronic tap-changer in

transformers. IET J Electr Power Appl 2008;2(6):36273.

[31] Bassett DL. Control of tap change under load transformers through the use of

programmable logic controllers. IEEE Trans Power Deliv 1993;8(8):175965.

[32] Wheeler P, Clare J, Empringham L, Apap M, Bland M. Matrix converters. Power

Eng J 2002:27382.

[33] Siahkolah B. Design and optimization of a full-electronic tap-changer for a

distribution transformer. Ph.D. Thesis, Department of Electrical and Computer

Engineering, University of Tehran; 2004.

[34] Bauer P, deHaan SWH. Electronic tap-changer for 500 kVA/10 kV distribution

transformers: design, experimental results and impact in distribution

network. IEEE IAS 1998;2:15307.

218 J. Faiz, B. Siahkolah/ Electrical Power and Energy Systems 33 (2011) 210218

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Data Sheet: UHF Variable Capacitance DiodeDocument8 pagesData Sheet: UHF Variable Capacitance DiodeGerard PabloNo ratings yet

- MP-6 Sonixs 1000 X 800 Manual 2014 Rev A PDFDocument190 pagesMP-6 Sonixs 1000 X 800 Manual 2014 Rev A PDFCésar Tejaxún33% (3)

- Medical Electronics SyllabusDocument83 pagesMedical Electronics SyllabussitalekshmiNo ratings yet

- SM Chapter26 PDFDocument26 pagesSM Chapter26 PDFLuis CristhianNo ratings yet

- 3.20 Fire Alarm Notification WireDocument4 pages3.20 Fire Alarm Notification WireJamesNo ratings yet

- Astm e 426Document4 pagesAstm e 426김경은No ratings yet

- Types CR, CRC, CRP and CRD Directional Overcurrent Relays: CautionDocument32 pagesTypes CR, CRC, CRP and CRD Directional Overcurrent Relays: CautionRida JavidNo ratings yet

- IO Plus ManualDocument30 pagesIO Plus ManualMohamed AzzuzNo ratings yet

- Raycap CatalogueDocument26 pagesRaycap CatalogueMagesh VenuNo ratings yet

- CAVSP ChecklistDocument11 pagesCAVSP ChecklistJPNo ratings yet

- Impact of Excitation System On Power System StabilityDocument39 pagesImpact of Excitation System On Power System StabilityZafar Bajwa100% (4)

- 2019 Enel3ds - Exam - MainDocument15 pages2019 Enel3ds - Exam - MainNOMPUMELELO MTHETHWANo ratings yet

- Spill Control Valve InspectionDocument1 pageSpill Control Valve InspectionArdi AgusmanNo ratings yet

- Joy Warrior 24f8 Datasheet 01Document15 pagesJoy Warrior 24f8 Datasheet 01Bien MorfeNo ratings yet

- Frm220 HW Manv114Document34 pagesFrm220 HW Manv114German FloresNo ratings yet

- Quiz Questions For DLD LabDocument6 pagesQuiz Questions For DLD LabGerald Carson100% (1)

- PhysicsDocument13 pagesPhysics42,Vansh 8th DNo ratings yet

- RV4 65B R5 V2 Product SpecificationDocument5 pagesRV4 65B R5 V2 Product SpecificationMario Alvarez GarciaNo ratings yet

- Ch11 6628089Document54 pagesCh11 6628089khaled99No ratings yet

- Trigger ModuleDocument33 pagesTrigger ModuleMenna NagyNo ratings yet

- B.Tech 2019 SE Rev2020 FinalDocument135 pagesB.Tech 2019 SE Rev2020 FinalprismNo ratings yet

- NVRAM Floor Height Table SUM Error: Point of Detection ApplicationDocument1 pageNVRAM Floor Height Table SUM Error: Point of Detection ApplicationDaniel GatdulaNo ratings yet

- Decibels and LogarithmsDocument4 pagesDecibels and Logarithmsjnewman85No ratings yet

- Ex 6 MicrowaveDocument2 pagesEx 6 Microwavevuthiloan08No ratings yet

- Wika ProductPortfolio en Co 6434Document116 pagesWika ProductPortfolio en Co 6434VedranNo ratings yet

- Led T8 Value Glass: Tubular LampsDocument2 pagesLed T8 Value Glass: Tubular LampsRoudy J. MhawasNo ratings yet

- MIG/MAG Welding Machine SpecificationDocument3 pagesMIG/MAG Welding Machine Specificationnyaungzin100% (3)

- Rev SPRING SEPARATORDocument8 pagesRev SPRING SEPARATORAswin MNo ratings yet

- Plant Shutdown ProcedureDocument2 pagesPlant Shutdown ProceduretomiNo ratings yet

- Electrical EngineeringDocument11 pagesElectrical EngineeringEdson MilanoNo ratings yet