Professional Documents

Culture Documents

Bie Stables

Uploaded by

Jose Luis Tubon CondemaitaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bie Stables

Uploaded by

Jose Luis Tubon CondemaitaCopyright:

Available Formats

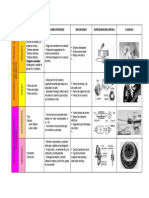

Biestables. Tipos.

Son los componentes bsicos para construir los circuitos secuenciales. Se caracterizan por poseer

memoria, es decir, recuerdan las entradas anteriores que se han producido en el circuito. Se

pueden construir cableando a partir de puertas lgicas o lo que es ms comn, formando parte de

circuitos integrados. Tambin son llamados bsculas o flip-flop.

Segn la lgica de disparo, se pueden dar los siguientes tipos:

Biestables R-S

Biestable D

Biestable J-K

Biestable T

1.1. Biestables R-S (Reset-Set)

Es un dispositivo con dos entradas R y S (Reset y Set) y una variable de estado o salida Q capaz de

almacenar un bit de informacin. Su funcionamiento es el siguiente:

Si su entrada Set se activa su estado Q se pone en Alto.

Si su entrada Reset se activa su estado Q se pone en Bajo.

Si no se activa ni Set ni Reset su estado no cambia.

Por supuesto, no se permite activar Set y Reset simultneamente.

Tabla de Funcionamiento

Los fabricantes de circuitos integrados, para describir la operacin que realiza el circuito, emplean

la llamada tabla de funcionamiento, que es lo que hasta ahora hemos venido llamando tabla de

verdad para los circuitos combinacionales, a la que se ha aadido el estado del tiempo, que resulta

esencial para los circuitos secuenciales.

La tabla de funcionamiento del biestable S-R, resulta ser:

Hemos empleado la siguiente notacin:

t

n

= instante de tiempo en el que se aplican las entradas.

t

n+1

= instante de tiempo inmediatamente posterior en el que el circuito responde.

Q

0

= salida Q en el instante t

n

Q+ = salida en el instante t

n+1

Aunque el flip-flop SR tiene dos entradas S y R, y una salida Q, es habitual que al implementarlo

aparezca con otra salida ms, la resultante de complementar la salida Q, y la entrada de reloj C.

Se suele representar simblicamente como un rectngulo como se indica en la figura.

Imagen 01. elaboracin propia

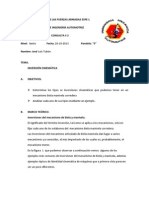

Diseo de un biestable S-R (Set- Reset)

Estos circuitos se pueden disear siguiendo las tcnicas que hemos venido empleando en el diseo

de los circuitos combinacionales, sin ms que tener en cuenta, que los circuitos secuenciales

presentan una realimentacin.

Vamos a aplicar el mtodo al diseo de un flip-flop S-R. En nuestro caso la salida Q+ depende tanto

de la salida anterior Q

0

, como de las entradas S y R, por lo que para implementarlo vamos a tratarlo

como a un circuito combinacional, pero considerando que Q

0

es tambin una entrada, por lo que

manejaremos la tabla de verdad que se adjunta, a partir de la tabla de estado que acabamos de

comentar.

Las entradas a cero no producen variacin del valor de salida.

Si la entrada S es 1, el valor de la salida pasa a 1.

Si la entrada R es 1, el valor de la salida pasa a 0.

Las dos entradas a uno (no se utilizan) dan una salida indeterminada.

La funcin cannica ser:

Que al simplificar quedar:

Aunque no es el procedimiento habitual, se consigue una funcin ms simplificada si despreciamos los

trminos indiferentes del mapa de Karnaugh. Por lo tanto se hacen dos bolsas de dos celdas y se

obtiene:

Si lo implementamos empleando nicamente puertas NOR:

Que una vez implementado quedar

Imagen 02. Elaboracin propia

Esta implementacin tiene la ventaja de que tambin produce la funcin en la salida de la primera

puerta NOR, de modo que se suele dibujar este circuito (en el circuito y en muchas ocasiones,

:

Imagen 03. Elaboracin propia

En el caso de un biestable R-S sncrono por nivel alto sera:

Imagen 04. elaboracin propia Imagen 05. elaboracin propia

Su cronograma y su tabla de estados sera:

Imagen 06. Elaboracin propia

1.2. Biestable D

Se conocen por el nombre de biestables de datos o seguidores. Tienen una nica entrada D, que es

copiada en el interior del biestable en los instantes de sincronismo.

Solamente tienen sentido como biestables sncronos por nivel o por flanco.

Su tabla de funcionamiento ser:

El nuevo estado Q

t+1

es 1. si D est activa 1 en el instante de sincronismo.

El nuevo estado Q

t+1

es 0, si D est inactiva 0 en el instante de sincronismo

Vamos a considerar que la entrada D es activa por nivel alto, con lo que su circuito ser

Imagen 07. Elaboracin propia

Su smbolo

Imagen 08. Elaboracin propia

y su tabla de estados sera;

Por tanto, su funcin lgica sera

Biestable J-K

Su funcionamiento es similar al flip-flop R-S, de modo que la entrada K acta para la puesta a 0

(reset) y la entrada J para la puesta a 1 (set). Cuando se activan las dos entradas simultneamente,

el biestable cambia de estado. Son biestables sncronos, lo que quiere decir que las transiciones de

los valores de salida se producen durante los flancos activos de las seales de reloj.

Su circuito es:

Imagen 09. Elaboracin propia

el smbolo es:

Imagen 10. Elaboracin propia

Su tabla de estados sera:

Y su funcin lgica:

Cronograma de un biestable J-K sncrono por flanco de subida.

Imagen 11. Elaboracin propia

1.4. Biestable T (Trigger=disparo)

Es igual que el biestable J-K, de modo que estas dos entradas estn puenteadas y forman la

entrada T de la bscula, de forma que cuando T toma el valor 0 la salida Q

t+1

=Q

t

, es decir no

cambia.

Cuando la entrada T toma el valor 1, la salida cambia de estado (bascula, de ah su nombre).

En el caso de que se mantenga la entrada T permanente igual a 1, la bscula T se comporta como

un divisor de frecuencia de la seal de reloj entre dos.

Su smbolo es como el de la figura adjunta.

Imagen 12. Elaboracin propia

Y su tabla de estado:

You might also like

- Empresa Eléctrica Ambato Regional Centro Norte S.A.: Versión SERCOP 1.1 (20 de Febrero 2014)Document266 pagesEmpresa Eléctrica Ambato Regional Centro Norte S.A.: Versión SERCOP 1.1 (20 de Febrero 2014)Jose Luis Tubon CondemaitaNo ratings yet

- Información PinesDocument2 pagesInformación PinesJose Luis Tubon CondemaitaNo ratings yet

- Modulo Como Ser HackerDocument20 pagesModulo Como Ser HackerJose Luis Tubon CondemaitaNo ratings yet

- Contador SincronoDocument12 pagesContador SincronoJose Luis Tubon Condemaita100% (1)

- MECANISMOS S4 Aplicaciones de TrinqueteDocument2 pagesMECANISMOS S4 Aplicaciones de TrinqueteJose Luis Tubon Condemaita100% (2)

- Características Del Biodiesel - CIQUIME ArgentinaDocument1 pageCaracterísticas Del Biodiesel - CIQUIME ArgentinaJose Luis Tubon CondemaitaNo ratings yet

- Consulta Mecanismo Inversion CinematicaDocument6 pagesConsulta Mecanismo Inversion CinematicaJose Luis Tubon Condemaita0% (1)

- Privilegio de AmarDocument1 pagePrivilegio de AmarJose Luis Tubon CondemaitaNo ratings yet

- Consulta Electronica - C I 741 - C I 358Document5 pagesConsulta Electronica - C I 741 - C I 358Jose Luis Tubon CondemaitaNo ratings yet

- 09 Tres Puertas-SanguanDocument2 pages09 Tres Puertas-SanguanElysenda ValNo ratings yet

- Plan de Mantenimiento Del Laboratorio de MetrologíaDocument16 pagesPlan de Mantenimiento Del Laboratorio de MetrologíaGladys PeredoNo ratings yet

- Alicia en El Pais de Las Maravillas Guión TeatralDocument4 pagesAlicia en El Pais de Las Maravillas Guión TeatralLixc Morales100% (1)

- Identificacion de Los Factores Que AfectanDocument18 pagesIdentificacion de Los Factores Que AfectanenersolicNo ratings yet

- Cuáles Son Los Cinco Grandes Rasgos de PersonalidadDocument5 pagesCuáles Son Los Cinco Grandes Rasgos de PersonalidadtaniaNo ratings yet

- N CSV Car 3 05 004 02 PDFDocument9 pagesN CSV Car 3 05 004 02 PDFArmando Huanca SolanoNo ratings yet

- Palabras en ItalianoDocument52 pagesPalabras en ItalianoDaniel Bolivar100% (1)

- Diagnostico Integral de ArchivoDocument36 pagesDiagnostico Integral de ArchivoUNIDAD DE ARCHIVO CENTRAL UNAMADNo ratings yet

- CitosolDocument12 pagesCitosolMarina OteizaNo ratings yet

- Tutoria 1º Aprendiendo A Manejar El EstresDocument4 pagesTutoria 1º Aprendiendo A Manejar El EstresNorma R VA Öf̲̲̅̅ı̲̲̅̅c̲̲̅̅ı̲̲̅̅a̲̲̅̅l̲̲̅̅'̲̲̅̅F̲̲̅̅bNo ratings yet

- Actividad 1 - Neuropsicología y El Desarrollo Del Sistema Nervioso CentralDocument5 pagesActividad 1 - Neuropsicología y El Desarrollo Del Sistema Nervioso CentralDelia Imbajoa CabreraNo ratings yet

- Exploracion de Las Computadoras y Sus UsosDocument6 pagesExploracion de Las Computadoras y Sus UsosLisbeth Garcia100% (1)

- PARACETAMOLDocument2 pagesPARACETAMOLCarolina LopezNo ratings yet

- Proyecto Corazon de JesusDocument25 pagesProyecto Corazon de JesusMelida Rafael QuispeNo ratings yet

- Catalogo General Aerotecnica 19-12-2005Document60 pagesCatalogo General Aerotecnica 19-12-2005YoNo ratings yet

- Piro MetroDocument8 pagesPiro MetroKaren VásconezNo ratings yet

- Quimico de HecesDocument19 pagesQuimico de HecesJesús Adrián Gómez OrtizNo ratings yet

- Instrumentos de IfáDocument7 pagesInstrumentos de IfáMao Cisneros100% (1)

- Traduccion Aproximada Fases y Proceso de Marisa PeerDocument51 pagesTraduccion Aproximada Fases y Proceso de Marisa Peerjoshua lancaster100% (1)

- Informe National Del Estado Del Ambiente - GEO Guatemala 2003 PDFDocument233 pagesInforme National Del Estado Del Ambiente - GEO Guatemala 2003 PDFJose Alberto Gramajo HerreraNo ratings yet

- Constancio de Castro A - Mapas MentalesDocument4 pagesConstancio de Castro A - Mapas MentalesJuan David Gallo GarcíaNo ratings yet

- Ebook PDFDocument234 pagesEbook PDFJoao SalazarNo ratings yet

- Fundamentos de Redes FTTHDocument27 pagesFundamentos de Redes FTTHcarlos valenzuelaNo ratings yet

- Sensor HegoDocument14 pagesSensor HegoJhonatan Sangovalin50% (2)

- SillaDocument4 pagesSillaJosé Gabriel PérezNo ratings yet

- Union Simple Acero InoxDocument1 pageUnion Simple Acero InoxJorge VillalbaNo ratings yet

- Sopa de LetrasDocument2 pagesSopa de LetrasDesther Josue Perez QuevedoNo ratings yet

- Que Es El Ser HumanoDocument2 pagesQue Es El Ser Humanocesar BurgosNo ratings yet

- Presentación 4: Colón Ante La Reina" (1843), de Emanuel Gottlieb (1816-1868)Document5 pagesPresentación 4: Colón Ante La Reina" (1843), de Emanuel Gottlieb (1816-1868)Lorena Valdes MoralesNo ratings yet

- Programa de PaltoDocument2 pagesPrograma de PaltoJoab CelsoNo ratings yet