Professional Documents

Culture Documents

Lesson 12: Introduction To 8051 Microcontroller Internal Architecture

Uploaded by

Saurabh SamirOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lesson 12: Introduction To 8051 Microcontroller Internal Architecture

Uploaded by

Saurabh SamirCopyright:

Available Formats

REAL TIME EMBEDDED SYSTEMS

LESSON 12:

INTRODUCTION TO 8051 MICROCONTROLLER INTERNAL ARCHITECTURE

A struggle has been going on between MCU manufacturers for Pins On The Case

quite a long time, each of them trying to best respond to the • 1–8: Port 1; Each of these pins can be used as either input

ever-increasing demands of the market. Every couple of days or output according to your needs. Also, pins 1 and 2 (P1.0

there is a brand new chip available, working at higher frequency, and P1.1) have special functions associated with Timer 2.

with more memory or with better A/D converters. And yet, a

• 9: Reset Signal; High logical state on this input halts the

closer look to their interior reveals the same or at least very

MCU and clears all the registers. Bringing this pin back to

similar structural design referred to as “8051 compatibility”.

logical state zero starts the program anew as if the power

What is it all about? The story began in the 80’s when Intel

had just been turned on. In another words, positive

introduced their microcontroller family MCS 8051 to the

voltage impulse on this pin resets the MCU. Depending on

market. Although this family had quite limited capabilities by

the device’s purpose and environs, this pin is usually

today’s notions, it quickly captivated the world and became the

connected to the push-button, reset-upon-start circuit or a

standard for what is today understood as ‘microcontroller’. The

brown out reset circuit (covered in the previous chapter).

most significant cause for such a success can be found in the

The image shows one simple circuit for safe reset upon

cleverly chosen configuration which can satisfy a diversity of

starting the controller. It is utilized in situations when

needs, yet allowing for continuous upgrades (in form of new

power fails to reach its optimal voltage.

controllers). In a brief period of time, a decent amount of

software has been developed for 8051, making further changes

of the hardware core simply uneconomical. Consequently, there

is a variety of MCUs available today, basically just the upgraded

8051 models. What exactly makes this microcontroller so special

and universal that it is still manufactured by all the major

companies, just under a different label?

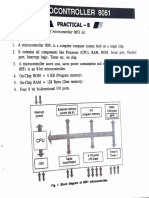

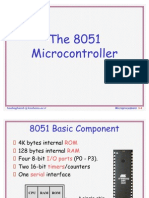

As can be seen on the image above, there is nothing particularly

remarkable about MCU 8051:

• 4 kilobytes of ROM is neither too little nor too much.

• 10-17: Port 3; As with Port 1, each of these pins can be

• 128 bytes of RAM (SFR registers included) can satisfy the

used as universal input or output. However, each pin of

basic needs, but is not really astounding.

Port 3 has an alternative function:

• 4 ports totaling 32 I/O lines, are usually sufficient for

• Pin 10: RXD - serial input for asynchronous

connecting to the environs and are by no means luxury.

communication.

Obviously, 8051 configuration is intended to satisfy the needs

of programmers developing the controlling devices and • Pin 11: TXD - serial output for asynchronous

instruments. This is one part of its key to success: there is communication or clock output for synchronous

nothing missing, yet there is no lavishness; it is meant for the communication

average user. The other clue can be found in the organization of • Pin 12: INT0 - input for interrupt 0

RAM, Central Processor Unit (CPU), and ports - all of which • Pin 13: INT1 - input for interrupt 1

maximally utilize the available resources and allow further

• Pin 14: T0 - clock input of counter 0

upgrades.

• Pin 15: T1 - clock input of counter 1

© Copy Right: Rai University

46 3.375/3A.375/3B.375

• Pin 16: WR - signal for writing to external (add-on) RAM ALE. External register (74HCT373 or 74HCT375 circuits

REAL TIME EMBEDDED SYSTEMS

memory synchronous communication. are common), memorizes the state of port P0 upon

• Pin 11: TXD - serial output for asynchronous receiving a signal from ALE pin, and uses it as part of the

communication or clock output for synchronous address for memory chip. During the second part of the

communication mechanical MCU cycle, signal on ALE is off, and port P0 is

used as Data Bus. In this way, by adding only one cheap

• Pin 12: INT0 - input for interrupt 0

integrated circuit, data from port can be multiplexed and

• Pin 13: INT1 - input for interrupt 1 the port simultaneously used for transferring both

• Pin 14: T0 - clock input of counter 0 addresses and data.

• Pin 15: T1 - clock input of counter 1 • 31: EA; Bringing this pin to the logical state zero (mass)

• Pin 16: WR - signal for writing to external (add-on) RAM designates the ports P2 and P3 for transferring addresses

memory regardless of the presence of the internal memory. This

means that even if there is a program loaded in the MCU it

• Pin 17: RD - signal for reading from external RAM

will not be executed, but the one from the external ROM

memory

will be used instead. Conversely, bringing the pin to the

• 18-19: X2 and X1; Input and output of internal oscillator. high logical state causes the controller to use both

Quartz crystal controlling the frequency commonly connects memories, first the internal, and then the external (if

to these pins. Capacitances within the oscillator mechanism present).

(see the image) are not critical and are normally about 30pF.

• 32-39: Port 0; Similar to Port 2, pins of Port 0 can be used

Instead of a quartz crystal, miniature ceramic resonators can

as universal input/output, if external memory is not used.

be used for dictating the pace. In that case, manufacturers

If external memory is used, P0 behaves as address output

recommend using somewhat higher capacitances (about 47

(A0 – A7) when ALE pin is at high logical level, or as data

pF). New MCUs work at frequencies from 0Hz to

output (Data Bus) when ALE pin is at low logical level.

50MHz+.

• 40: VCC; Power +5V

Input – Output (I/O) Ports

Every MCU from 8051 family has 4 I/O ports of 8 bits each.

This provides the user with 32 I/O lines for connecting MCU

to the environs. Unlike the case with other controllers, there is

no specific SFR register for designating pins as input or output.

Instead, the port itself is in charge: 0=output, 1=input. If

particular pin on the case is needed as output, the appropriate

bit of I/O port should be cleared. This will generate 0V on the

specified controller pin. Similarly, if particular pin on the case is

needed as input, the appropriate bit of I/O port should be set.

This will designate the pin as input, generating +5V as a side

effect (as with every TTL input

Port 0

Port 0 has two fold role: if external memory is used, it contains

the lower address byte (addresses A0-A7), otherwise all bits of

the port are either input or output. Another feature of this port

• 20: GND; Ground comes to play when it has been designated as output. Unlike

other ports, Port 0 lacks the “pull up” resistor (resistor with

• 21- 28: Port 2; If external memory is not present, pins of +5V on one end). This seemingly insignificant change has the

Port 2 act as universal input/output. If external memory is following consequences:

present, this is the location of the higher address byte, i.e.

addresses A8 – A15. It is important to note that in cases • When designated as input, pin of Port 0 acts as high

when not all the 8 bits are used for addressing the memory impedance offering the infinite input resistance with no

(i.e. memory is smaller than 64kB), the rest of the unused “inner” voltage.

bits are not available as input/output. • When designated as output, pin acts as “open drain”.

• 29: PSEN; MCU activates this bit (brings to low state) Clearing a port bit grounds the appropriate pin on the case

upon each reading of byte (instruction) from program (0V). Setting a port bit makes the pin act as high

memory. If external ROM is used for storing the program, impedance.

PSEN is directly connected to its control pins. Therefore, to get positive logic (5V) at output, external “pull

• 30: ALE; Before each reading of the external memory, up” resistor needs to be added for connecting the pin to the

MCU sends the lower byte of the address register positive pole.

(addresses A0 – A7) to port P0 and activates the output

© Copy Right: Rai University

3.375/3A.375/3B.375 47

Therefore, to get one (5V) on the output, external “pull up” MCU. Locations that are available to the user span addresses

REAL TIME EMBEDDED SYSTEMS

resistor needs to be added for connecting the pin to the positive from 0 to 7Fh, i.e. first 128 registers, and this part of RAM is

pole. split into several blocks as can be seen in the image below.

Port 1

This is “true” I/O port, devoid of dual function characteristic

for Port 0. Having the “pull up” resistor, Port 1 is fully

compatible with TTL circuits

Port 2

When using external memory, this port contains the higher

address byte (addresses A8–A15), similar to Port 0. Otherwise,

it can be used as universal I/O port

Port 3

Beside its role as universal I/O port, each pin of Port 3 has an

alternate function. In order to use one of these functions, the

pin in question has to be designated as input, i.e. the appropri-

ate bit of register P3 needs to be set. From a hardware

standpoint, Port 3 is similar to Port 0.

Memory

During the runtime, microcontroller uses two different types of

memory: one for holding the program being executed (ROM

memory), and the other for temporary storage of data and

auxiliary variables (RAM memory). Depending on the particular

model from 8051 family, this is usually few kilobytes of ROM

and 128/256 bytes of RAM. This amount is built-in and is

sufficient for common tasks performed “independently” by the

MCU. However, 8051 can address up to 64KB of external

memory. These can be separate memory blocks, (separate RAM

chip and ROM chip) totaling 128KB of memory on MCU

which is a real programming goody.

ROM Memory

First models from 8051 family lacked the internal program

memory, but it could be added externally in a form of a separate

chip. These MCUs can be recognized by their mark which begins

with 803 (e.g. 8031 or 8032). New models have built-in ROM,

although there are substantial variations. With some models

internal memory cannot be programmed directly by the user.

Instead, the user needs to proceed the program to the manufac-

turer, so that the MCU can be programmed (masked)

appropriately in the process of fabrication. Obviously, this • First block comprises 4 “banks” of 8 registers each, marked

option is cost-effective only for large series. Fortunately, there are as R0 - R7. To address these, the parent bank has to be

MCU models ideal for experimentation and small specialized selected.

series. Many manufacturers deliver controllers that can be • Second memory block (range 20h – 2Fh) is bit-addressable,

programmed directly by the user. These come in a ceramic case meaning that every belonging bit has its own address (0 to

with an opening (EPROM version) or in a plastic case without 7Fh). Since the block comprises 16 of these registers, there

an opening (EEPROM version). This book deals with one of is a total of 128 addressable bits. (Bit 0 of byte 20h has bit

the latter models that can be programmed via simple program- address 0, while bit 7 of byte 2Fh has bit address 7Fh).

mer, even if the chip has already been mounted to the • Third is the group of available registers at addresses 2Fh –

designated device. 7Fh (total of 80 locations) without special features or a

RAM Memory preset purpose

As previously stated, RAM is used for storing temporary data Extra Memory Block

and auxiliary results generated during the runtime. Apart from To satisfy the programmers’ ever-increasing demands for RAM,

that, RAM comprises a number of registers: hardware counters latest 8051 models were added an extra memory block of 128

and timers, I/O ports, buffer for serial connection, etc. With locations. But it is not all that simple... The problem lies in the

older versions, RAM spanned 256 locations, while new models fact that the electronics which addresses RAM employs 1 byte (8

feature additional 128 registers. First 256 memory locations bits), reaching only the first 256 locations. Therefore, a little trick

form the basis of RAM (addresses 0 – FFh) of every 8051

© Copy Right: Rai University

48 3.375/3A.375/3B.375

had to be applied in order to keep the existing 8-bit architecture serial connection, etc). Although there are 128 available memory

REAL TIME EMBEDDED SYSTEMS

for the sake of compatibility with older models. The idea is to slots for allocating SFR registers, the basic core shared by 8051

make the additional memory block share the addresses with the MCUs has but 22 registers. The rest has been left open inten-

existent locations intended for SFR registers (80h - FFh). For tionally to allow future upgrades while retaining the

distinguishing these two physically separate memory areas, compatibility with earlier models. This fact makes possible to

different methods of addressing are used: if SFR registers are in use programs developed for obsolete models long ago.

question, direct addressing is used; for extra RAM locations,

indirect addressing is used.

Memory Expanding

In case the built-in amount of memory (either RAM or ROM)

is not sufficient for your needs, there is always an option of

adding two external 64KB memory chips. When added, they are

addressed and accessed via I/O ports P2 and P3. From user’s

point of view it’s all very simple, because if properly connected

most of the job is carried out automatically by MCU.

8051 MCU has two separate read signals, RD# (P3.7) and

PSEN#. The first one is active when reading byte from the

external data memory (RAM), and the second one is active

when reading byte from the external program memory (ROM).

Both signals are active on low logical level. The following image

shows a typical scheme for such expansion using separate chips

for RAM and ROM, known as Harvard architecture

Notes

Memory can be also mapped as a single block, functioning as

both data memory and program memory simultaneously (only

one memory chip is used). This approach is known as Von

Neumann architecture. To be able to read the same block using

RD# or PSEN#, these two signals were combined via logical

AND. In this way, output of AND circuit is low if any of the

two inputs is low.

Using the Harvard architecture effectively doubles MCU

memory, but that’s not the only advantage offered by the

method. Keeping the program code separated from the data

makes the controller more reliable since there is no writing to

the program memory.

SFR Registers (Special Function Registers)

SFR registers can be seen as a sort of control panel for manag-

ing and monitoring the microcontroller. Every register and each

of the belonging bits has its name, specified address in RAM

and strictly defined role (e.g. controlling the timer, interrupt,

© Copy Right: Rai University

3.375/3A.375/3B.375 49

You might also like

- Internship Report - Embedded System.Document30 pagesInternship Report - Embedded System.kutty vicky71% (7)

- Department of Electronics & Communication Engineering Lab Manual B.Tech Year: 3rd Semester: VIDocument53 pagesDepartment of Electronics & Communication Engineering Lab Manual B.Tech Year: 3rd Semester: VImacfready100% (1)

- 8051pin CH 34Document23 pages8051pin CH 34Malgireddy RavireddyNo ratings yet

- Expt No-01Document6 pagesExpt No-01No NamNo ratings yet

- Microcontroller Exp To Write 6 To 8Document12 pagesMicrocontroller Exp To Write 6 To 8ee210150900103No ratings yet

- Messenger Development Without Internet Using Zigbee TechnologyDocument89 pagesMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyNo ratings yet

- Internet of Things Lab Manual Up DateDocument53 pagesInternet of Things Lab Manual Up DateASHU KNo ratings yet

- A Comparative Analysis of Conventional 8051 Micro Controller With Modern Ultra Low Power MSP430 1 PPRDocument6 pagesA Comparative Analysis of Conventional 8051 Micro Controller With Modern Ultra Low Power MSP430 1 PPRNishit ChittoraNo ratings yet

- Unit 3 Micro Controllers: Intel 8051: RV College of EngineeringDocument28 pagesUnit 3 Micro Controllers: Intel 8051: RV College of EngineeringRiya Shetty B HNo ratings yet

- 2 13v3i1 2Document5 pages2 13v3i1 2Hazal kayaNo ratings yet

- Tampering Detection of Transmission Line: AbstractDocument9 pagesTampering Detection of Transmission Line: AbstractJayant KumarNo ratings yet

- 15 01 06 16 14 27 3077 MkumarDocument94 pages15 01 06 16 14 27 3077 MkumarVasantha KumariNo ratings yet

- Lab1 FinalDocument6 pagesLab1 FinalsufyanNo ratings yet

- 8051 Micro Controller TrainerDocument2 pages8051 Micro Controller Trainerkira_yamato999999542No ratings yet

- Automatic Temperature ControllerDocument24 pagesAutomatic Temperature Controllerarunbera00792% (12)

- Two-Wire Peripheral Expansion For The AT89C2051 MicrocontrollerDocument9 pagesTwo-Wire Peripheral Expansion For The AT89C2051 MicrocontrollerVlaovic GoranNo ratings yet

- Digital Code Locking SystemDocument89 pagesDigital Code Locking SystemSrinivas Reddy100% (5)

- Moving Display Using 8051 Micro ControllerDocument45 pagesMoving Display Using 8051 Micro ControllerMuraliKrishnaNo ratings yet

- IOT FILE FinalDocument16 pagesIOT FILE FinalHardik UpasaniNo ratings yet

- Unit 1Document9 pagesUnit 1Suresh MeesalaNo ratings yet

- Microcontrollers Chapter 1 SlidesDocument11 pagesMicrocontrollers Chapter 1 SlidesDawod SalmanNo ratings yet

- MC Lab-Record Final - Watermark-1Document116 pagesMC Lab-Record Final - Watermark-1Mohamed SaleelNo ratings yet

- Lab 5Document8 pagesLab 5Zunair NazirNo ratings yet

- MC14500B HandbookDocument112 pagesMC14500B HandbookAnonymous aP1FSUPoNo ratings yet

- Code LockDocument94 pagesCode LockVaibhav AhujaNo ratings yet

- Data RFDocument63 pagesData RFmgitecetechNo ratings yet

- Power Saving Time Operated Electrical Appliance Using Microcontroller AT89S52Document19 pagesPower Saving Time Operated Electrical Appliance Using Microcontroller AT89S52zetamieNo ratings yet

- Compact DeviceDocument57 pagesCompact Devicesriram kantipudiNo ratings yet

- MIcrocontroller Based Embedded System E - ContentsDocument54 pagesMIcrocontroller Based Embedded System E - ContentsLokesh SharmaNo ratings yet

- RS 485Document51 pagesRS 485mgitecetech100% (1)

- Dasar-Dasar PLCDocument45 pagesDasar-Dasar PLCFarid MulyanaNo ratings yet

- Scanned Notes For MPMCDocument6 pagesScanned Notes For MPMCNischal KataraNo ratings yet

- AT89C2051 Traffic Light ControllerDocument39 pagesAT89C2051 Traffic Light ControllerNagesh RayNo ratings yet

- Project Report On Microcontroller Based Traffic Light ControllerDocument22 pagesProject Report On Microcontroller Based Traffic Light ControllerMohitpariharNo ratings yet

- Chapter 2 - 8051 Microcontroller ArchitectureDocument27 pagesChapter 2 - 8051 Microcontroller ArchitectureAgxin M J Xavier100% (1)

- A Presentation On Microcontroller 8051Document22 pagesA Presentation On Microcontroller 8051Praveen ShrivastavaNo ratings yet

- In-Depth Articles: Volume OneDocument21 pagesIn-Depth Articles: Volume OneakuisajaNo ratings yet

- 8051 Microcontroller Project ReportDocument27 pages8051 Microcontroller Project ReportSahib SinghNo ratings yet

- Micro ControllerDocument6 pagesMicro ControllerAwais AhmedNo ratings yet

- 7th Sem Project ReportDocument49 pages7th Sem Project ReportSamridhi GuptaNo ratings yet

- Android Controlled Home AppliancesDocument60 pagesAndroid Controlled Home AppliancesWaseem AshrafNo ratings yet

- Project Report On Microcontroller Based Traffic Light ControllerDocument23 pagesProject Report On Microcontroller Based Traffic Light Controllerالموعظة الحسنه chanelNo ratings yet

- Automatic College Bell Using RTC ECE ProjectDocument6 pagesAutomatic College Bell Using RTC ECE ProjectchandravmNo ratings yet

- 8051 MicrocontrollerDocument10 pages8051 MicrocontrollerAfsar ShaikhNo ratings yet

- PLC - Course Notes - 1Document72 pagesPLC - Course Notes - 1fatihts126No ratings yet

- Project ReportDocument20 pagesProject ReportPiyush GuptaNo ratings yet

- System Description: Microcontroller (AT89S52)Document19 pagesSystem Description: Microcontroller (AT89S52)Ayush SharmaNo ratings yet

- PLC Programming: Ladder Logic InputsDocument15 pagesPLC Programming: Ladder Logic InputsMuhamad ParwezNo ratings yet

- Submitted To: Submitted By:: (Department of Electronics and Instrumentation Engg.)Document19 pagesSubmitted To: Submitted By:: (Department of Electronics and Instrumentation Engg.)nikboy88No ratings yet

- Micro Controller 8051Document16 pagesMicro Controller 8051Gaurav Tripathi100% (1)

- Quiz BuzzerDocument18 pagesQuiz BuzzerSatyam Lala100% (1)

- Final Project File MeenalDocument50 pagesFinal Project File MeenalMeenal MishraNo ratings yet

- 89c420 UserguideDocument135 pages89c420 Userguideprakov_komesNo ratings yet

- MKT3811 Week4 03.11.2021 RDocument62 pagesMKT3811 Week4 03.11.2021 REmirhan AlmaNo ratings yet

- Mircroprocessor Systems and InterfacingDocument72 pagesMircroprocessor Systems and InterfacingMuaz ShahidNo ratings yet

- Chapter-3 Hardware ComponentsDocument23 pagesChapter-3 Hardware ComponentsKrishna PrasadNo ratings yet

- 2-Introduction To 8051 Microcontroller-10-01-2024Document49 pages2-Introduction To 8051 Microcontroller-10-01-2024someshwaranmNo ratings yet

- 8051 MicrocontrollerDocument8 pages8051 MicrocontrollerIan Neven TayuponNo ratings yet

- Traffic Light Controller SchematicDocument2 pagesTraffic Light Controller SchematicBeny Stephen0% (1)

- Microcontroller & GSM Based ProjectsDocument7 pagesMicrocontroller & GSM Based ProjectsBien MorfeNo ratings yet

- Assembler Language - 8051powerpoint PresentationDocument56 pagesAssembler Language - 8051powerpoint PresentationtauseeeeeeeeNo ratings yet

- Accident-Statistics,-Buzzer-During-Any-Accident DOCUMENTATIONDocument13 pagesAccident-Statistics,-Buzzer-During-Any-Accident DOCUMENTATIONsaikumar0% (1)

- The 8051 Microcontroller and Embedded Systems: Interrupts Programming in AssemblyDocument26 pagesThe 8051 Microcontroller and Embedded Systems: Interrupts Programming in AssemblyAnushkaSinhaNo ratings yet

- TP MicroprocessorDocument10 pagesTP MicroprocessorAnshuman Swaroop DasNo ratings yet

- ESEx 1Document3 pagesESEx 1PrayNo ratings yet

- Development BoardDocument20 pagesDevelopment BoardFaraz Ali100% (1)

- ASM51Document199 pagesASM51You Nix0% (1)

- 8051 - Micro ControllersDocument33 pages8051 - Micro ControllersRijo Jackson TomNo ratings yet

- Detection & Distinction of Colors Using Color Sorting Robotic Arm in A Pick & Place MechanismDocument42 pagesDetection & Distinction of Colors Using Color Sorting Robotic Arm in A Pick & Place MechanismTrinesh GowdaNo ratings yet

- 8051Document141 pages8051sudhinnnNo ratings yet

- Sensor Based Energy Conservation System For Corporate Computers and Lighting SystemDocument43 pagesSensor Based Energy Conservation System For Corporate Computers and Lighting SystemSaravanan ViswakarmaNo ratings yet

- MC Unit-3,4 QuestionsDocument3 pagesMC Unit-3,4 QuestionsPraneetha InumarthiNo ratings yet

- Unit-3 - (Generating Control Signals)Document19 pagesUnit-3 - (Generating Control Signals)Puneeth SuNo ratings yet

- Beginners Guide To Embedded C Programming EbookDocument3 pagesBeginners Guide To Embedded C Programming Ebooknalinagc0% (1)

- 5-Yr Idd Bme PDFDocument30 pages5-Yr Idd Bme PDFInventory gammaNo ratings yet

- Ch-1 1Document29 pagesCh-1 1A_b_qNo ratings yet

- Interfacing Stepper Motor With 8051Document9 pagesInterfacing Stepper Motor With 8051jannathNo ratings yet

- Electronic Circuits and Diagram-Electronics Projects and DesignDocument8 pagesElectronic Circuits and Diagram-Electronics Projects and DesignEric MelendezNo ratings yet

- 47.GSM Based Home AutomationDocument73 pages47.GSM Based Home AutomationMikroc Thupati SrinivsNo ratings yet

- ECE310 Introduction To Microcontrollers and Applications: Assume Missing Data SuitablyDocument2 pagesECE310 Introduction To Microcontrollers and Applications: Assume Missing Data SuitablyKRISHNAPRIYANo ratings yet

- Microcontrollers 8051 MSP430 Notes For IV Sem ECE StudentsDocument61 pagesMicrocontrollers 8051 MSP430 Notes For IV Sem ECE StudentsSaneesh Cleatus T100% (2)

- Smart Card Reader For Student IDDocument43 pagesSmart Card Reader For Student IDSheshu technocrat100% (3)

- Nuvoton 8051 ISP by COM Port: User ManualDocument18 pagesNuvoton 8051 ISP by COM Port: User ManualParth PatelNo ratings yet

- Interfacing A LCD Display With 8051Document7 pagesInterfacing A LCD Display With 8051bhaswati100% (1)

- 4th Sem EC 1257 MicroprocessorDocument7 pages4th Sem EC 1257 MicroprocessorHarleen BarmiNo ratings yet

- Power TheftDocument71 pagesPower TheftmanikandanNo ratings yet

- 8051 MicrocontrolllerDocument296 pages8051 MicrocontrolllerAniket BabutaNo ratings yet

- ME-303 Mechatronics: Dr. Fakhre Alam KhanDocument29 pagesME-303 Mechatronics: Dr. Fakhre Alam KhanSadia KhanNo ratings yet