Professional Documents

Culture Documents

Max 1672

Uploaded by

jnax101Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Max 1672

Uploaded by

jnax101Copyright:

Available Formats

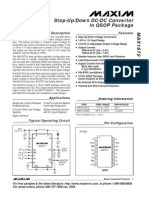

________________General Desc ription

The M A X1672 integrates a step-up D C -D C converter w ith a

linear regulator to provide step-up/dow n voltage conver-

sion. This device provides a constant output voltage for

inputs that vary above and below the output voltage. It has

a 1.8V to 11V input range and a preset 3.3V or 5V output.

The output can also be set from 1.25V to 5.5V using tw o

resistors. Typical efficiency is 85% .

The M A X1672s step-up/linear-regulator configuration per-

m its the use of a single, physically sm aller inductor than

can be used w ith com peting SEPIC and flyback configura-

tions. Sw itch current is also selectable, perm itting the use

of sm aller inductors in low -current applications. The linear

regulator also acts as a filter to reduce output ripple voltage.

The M A X1672 has a low 85A quiescent supply current, w hich

is further reduced to 0.1A in logic-controlled shutdow n. The

output voltage is disconnected from the input in shutdow n.

The M A X1672 also has a PG I/PGO low -battery detector.

The M A X1672 com es in a 16-pin Q SO P package (sam e size

as a standard 8-pin SO ). For a larger device that delivers m ore

output current, refer to the M A X710/M A X711. The preassem -

bled M A X1672 evaluation kit is available to speed designs.

________________________Applic ations

Single-C ell, Lithium -Pow ered 2-C ell to 4-C ell A A A lkaline

Portable D evices H and-H eld Equipm ent

3.3V and O ther Low -Voltage B attery-Pow ered D evices

System s w ith A C Input A dapters

D igital C am eras

____________________________Features

o Step-Up/Down Voltage Conversion

o 1.8V to 11V Input Range

o 3.3V/5V or Adjustable Output Voltage Range

o Output Current:

300mA at 5V (V

IN

2.5V)

150mA at 5V (V

IN

1.8V)

o Smaller Inductor than SEPIC and Flybacks

o Load Disconnects from Input in Shutdown

o Supply Current from Battery:

85A (No-Load)

0.1A (Shutdown)

o PGI/PGO Low-Battery Comparator

o 16-Pin QSOP Package

(same footprint as 8-pin SO)

o No External FETs Required

o Thermal and Short-Circuit Protection

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800.

For small orders, phone 408-737-7600 ext. 3468.

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

________________________________________________________________ Maxim Integrated Products 1

19-1307; R ev 0a; 11/97

EVALUATION KIT

AVAILABLE

______________Ordering Information

*D ice are tested at T

A

= +25C .

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

LX LX

PGND

GND

REF

IN

PS

FB

OUT

TOP VIEW

MAX1672

QSOP

PGND

ONA

ILIM

PGO

PGI

3/ 5

ONB

__________________Pin Configuration

MAX1672

IN

ONA

PGI

ONB

OFF ON

PGND GND

PS

3.3V/ 5V

OUTPUT

INPUT

1.8V TO 11V

LOW- BATTERY

DETECTOR

OUTPUT

OUT

PG0

FB REF

LX

OFF

3/ 5

ILIM

5V

0.8A

ON

3.3V

0.5A

__________Typic al Operating Circ uit

PART

M A X1672C /D

M A X1672EEE -40C to + 85C

0C to + 70C

TEMP. RANGE PIN-PACKAGE

D ice*

16 Q SO P

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(V

PS

= 6V, C

R EF

= 0.1F, C

O U T

= 4.7F, T

A

= -40C to + 85C , unless otherw ise noted. Typical values are at T

A

= + 25C .) (N ote 1)

Stresses beyond those listed under A bsolute M axim um R atingsm ay cause perm anent dam age to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not im plied. Exposure to

absolute m axim um rating conditions for extended periods m ay affect device reliability.

IN , PS, LX, O U T, PGO to G N D .........................-0.3V to + 11.5V

ILIM , O N A , ONB, FB , 3/5,

R EF, PG I to G N D ......................................-0.3V to (V

PS

+ 0.3V)

PG N D to G N D .......................................................-0.3V to + 0.3V

O U T Short C ircuit to G N D ..........................................C ontinuous

O utput C urrent..................................................................350m A

C ontinuous Pow er D issipation (T

A

= + 70C )

16-Pin Q SO P (derate above + 70C by 8.3m W /C ).......667m W

O perating Tem perature R ange .........................-40C to + 85C

Junction Tem perature ....................................................+ 150C

Storage Tem perature R ange ...........................-65C to + 160C

Lead Tem perature (soldering, 10sec)............................+ 300C

V

PS

= 5.5V

V

O U T

= 0V, O N A = G N D , ONB = PS

V

PS

= 2.7V, I

O U T

= 50m A

V

PS

= 5.5V, I

O U T

= 50m A

ILIM = G N D

V

LX

= 11V, O N A = G N D , ONB = PS

V

PS

= 2.7V, I

LX

= 50m A

I

R EF

= 0m A

V

PS

= 5.5V, I

LX

= 50m A

V

IN

= G N D to 11V

O N A = G N D , ONB = PS, current m easured into PS pin

O N A = PS or ONB = G N D , current m easured into PS pin,

I

O U T

= 0m A

V

IN

= 2V, 3/5 = G N D , FB = G N D , I

O U T

= 10m A to 150m A

V

FB

= 1.3V

V

IN

= 3V to 5V, 3/5 = G N D , I

O U T

= 100m A

H ysteresis = 15m V typical

CONDITIONS

A 0.35 0.7 1.4 O utput PFET C urrent Lim it

A 0.1 1 O utput PFET Leakage C urrent

2.3 4.6

1.2 2.4

O utput PFET R esistance

0.3 0.5 0.7

0.35 0.5 0.65

A 0.1 1 LX Leakage C urrent

0.9 2.0

LX O n-R esistance

0.6 1.3

A 3 6 IN Input C urrent

nA 1 50 FB Input C urrent

m V 70 FB D ual-M ode Trip Threshold

4.8 5.2

V 0.9

V 1.8 11.0 Input Voltage

Startup Voltage

1.21 1.25 1.29

V 1.21 1.25 1.29 R eference Voltage

A 0.1 1 Shutdow n Q uiescent C urrent

A 85 125 Q uiescent C urrent

4.75 5.00 5.25

V 1.25 5.5

O utput Voltage A djustm ent

R ange

% /m A 0.003 O utput Load R egulation

% /V 0.15 O utput Line R egulation

UNITS MIN TYP MAX PARAMETER

V

3.17 3.43

3.13 3.30 3.47

O utput Voltage

FB = G N D ,

I

O U T

= 0m A to

150m A

T

A

= 0C to + 85C

T

A

= -40C to + 85C

T

A

= 0C to + 85C

T

A

= -40C to + 85C

V

1.20 1.30

FB Voltage

T

A

= 0C to + 85C

T

A

= -40C to + 85C

ILIM = PS

A

0.5 0.8 1.1

LX C urrent Lim it

0.6 0.8 1.0

T

A

= 0C to + 85C

T

A

= -40C to + 85C

T

A

= 0C to + 85C

T

A

= -40C to + 85C

3/5 = PS

O U T = FB

3/5 = G N D

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

_______________________________________________________________________________________ 3

ELECTRICAL CHARACTERISTICS (continued)

(V

PS

= 6V, C

R EF

= 0.1F, C

O U T

= 4.7F, T

A

= -40C to + 85C , unless otherw ise noted. Typical values are at T

A

= + 25C .) (N ote 1)

Note 1: Specifications to -40C are guaranteed by design.

O N A , ONB, 3/5; ILIM

T

A

= 0C to + 85C

V

PG O

= 11V

I

PG O

= 2m A , V

PG I

= 1.2V

CONDITIONS

m V 30 H ysteresis

C 20

C 150 Therm al Shutdow n Threshold

Therm al Shutdow n H ysteresis

V 0.4 Input Low Voltage

1.21 1.29

A 0.1 1 PGO O utput Leakage

V 0.1 0.4 PGO O utput Low Voltage

UNITS MIN TYP MAX PARAMETER

O N A , ONB, 3/5; ILIM V 1.6 Input H igh Voltage

__________________________________________Typic al Operating Charac teristic s

(T

A

= + 25C , unless otherw ise noted.)

100

50

0.1 1 10 100 1000

EFFICIENCY vs. OUTPUT CURRENT

(V

OUT

= 5V)

60

M

A

X

1

6

7

2

-

0

1

OUTPUT CURRENT (mA)

E

F

F

I

C

I

E

N

C

Y

(

%

)

70

80

90

V

IN

= 5V

V

IN

= 3.6V

V

IN

= 1.8V

V

IN

= 0.9V

V

IN

= 2.7V

100

50

0.1 1 10 100 1000

EFFICIENCY vs. OUTPUT CURRENT

(V

OUT

= 3. 3V)

60

M

A

X

1

6

7

2

-

0

2

OUTPUT CURRENT (mA)

E

F

F

I

C

I

E

N

C

Y

(

%

)

70

80

90

V

IN

= 3.3V

V

IN

= 1.8V

V

IN

= 0.9V

V

IN

= 2.7V

50

60

70

80

90

100

0 4 5 2 3 1 6 7 8 9 10

EFFICIENCY vs. INPUT VOLTAGE

(I

OUT

= 10mA)

M

A

X

1

6

7

2

-

0

3

INPUT VOLTAGE (V)

E

F

F

I

C

I

E

N

C

Y

(

%

)

V

OUT

= 3.3V

V

OUT

= 5V

V

PG I

= 1.3V nA 1 50 PG I Input B ias C urrent

O N A , ONB, 3/5, ILIM nA 1 100 Input B ias C urrent

T

A

= -40C to + 85C

V

1.19 1.25 1.31

PG I Threshold Voltage

PGI/PGO COMPARATOR

LOGIC AND CONTROL INPUTS

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

4 _______________________________________________________________________________________

_____________________________Typic al Operating Charac teristic s (c ontinued)

(T

A

= + 25C , unless otherw ise noted.)

0

100

200

300

400

0 2 1 3 4

MAXIMUM OUTPUT CURRENT vs.

INPUT VOLTAGE (V

OUT

= 5V)

M

A

X

1

6

7

2

-

0

4

INPUT VOLTAGE (V)

M

A

X

I

M

U

M

O

U

T

P

U

T

C

U

R

R

E

N

T

(

m

A

)MAXIMUM RECOMMENDED

OUTPUT CURRENT

ILIM = GND (0.5A)

ILIM = PS (0.8A)

0

100

200

300

400

0 2 1 3 4

MAXIMUM OUTPUT CURRENT

vs. INPUT VOLTAGE (V

OUT

= 3. 3V)

M

A

X

1

6

7

2

-

0

5

INPUT VOLTAGE (V)

M

A

X

I

M

U

M

O

U

T

P

U

T

C

U

R

R

E

N

T

(

m

A

)MAXIMUM RECOMMENDED

OUTPUT CURRENT

ILIM = GND (0.5A)

ILIM = PS (0.8A)

0

100

200

300

400

4 5 7 8 9 11 6 10 12

MAXIMUM OUTPUT CURRENT

vs. INPUT VOLTAGE

(POWER DISSIPATION LIMIT)

M

A

X

1

6

7

2

-

0

6

INPUT VOLTAGE (V)

M

A

X

I

M

U

M

O

U

T

P

U

T

C

U

R

R

E

N

T

(

m

A

)

MAXIMUM RECOMMENDED

OUTPUT CURRENT

V

OUT

= 5V

V

OUT

= 3.3V

T

A

= +25C

T

A

= +85C

V

OUT

= 3.3V

V

OUT

= 5V

M

A

X

I

M

U

M

R

E

C

O

M

M

E

N

D

E

D

I

N

P

U

T

V

O

L

T

A

G

E

1000

10

0 1 2 3 4 5 6 7 8 9 10 11

NO-LOAD BATTERY CURRENT

vs. INPUT VOLTAGE

M

A

X

1

6

7

2

-

0

7

INPUT VOLTAGE (V)

S

U

P

P

L

Y

C

U

R

R

E

N

T

(

A

)

100

V

OUT

= 5V

V

OUT

= 3.3V

A

B

2ms/ di v

LINE-TRANSIENT RESPONSE

MAX1672- 10

A: V

OUT

= 5V (100mV/ di v, AC COUPLED)

B: V

IN

= 2V TO 4V (I

OUT

= 100mA)

1

0.01

0 1 2 3 4 5 6 7 8 9 10 11

SHUTDOWN CURRENT

vs. INPUT VOLTAGE

M

A

X

1

6

7

2

-

0

8

INPUT VOLTAGE (V)

S

U

P

P

L

Y

C

U

R

R

E

N

T

(

A

)

0.1

70

10

0.01 1 10 100 0.1 1000

LINEAR REGULATOR POWER-SUPPLY

REJECTION RATIO vs. FREQUENCY

20

M

A

X

1

6

7

2

-

0

9

FREQUENCY (kHz)

P

S

R

R

(

d

B

)

30

40

60

50

A

B

2ms/ di v

LOAD-TRANSIENT RESPONSE

MAX1672- 11

A: V

OUT

= 5V (50mV/ di v, AC COUPLED)

B: I

OUT

= 10mA TO 100mA (V

IN

= 2V)

A

B

10s/ di v

OUTPUT RIPPLE (MEDIUM LOAD)

MAX1672- 12

A: V

OUT

= 5V (20mV/ di v, AC COUPLED)

B: I

L1

(500mA / di v) (V

IN

= 2.7V, I

OUT

= 80mA)

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

_______________________________________________________________________________________ 5

______________________________________________________________Pin Desc ription

NAME FUNCTION

1 LX Inductor C onnection to the D rain of the Internal N -C hannel Pow er M O SFET

PIN

_____________________________Typic al Operating Charac teristic s (c ontinued)

(T

A

= + 25C , unless otherw ise noted.)

A

B

10s/ di v

OUTPUT RIPPLE (HEAVY LOAD)

MAX1672- 13

A: V

OUT

= 5V (20mV/ di v, AC COUPLED)

B: I

L1

(500mA / di v) (V

IN

= 2.7V, I

OUT

= 250mA)

A

B

50s/ di v

START-UP DELAY

MAX1672- 14

A: V

OUT

= (2V/ di v)

B: ONB (2V/ di v) (V

IN

= 2.7V, R

LOAD

= 50)

A

B

200s/ di v

TURN-OFF DELAY

MAX1672- 15

A: V

OUT

= (2V/ di v)

B: ONB (2V/ di v) (V

IN

= 2.7V, R

LOAD

= 50)

2 PG N D Pow er G round

3 ONB

O n C ontrol Input. W hen ONB = low or O N A = high, the IC is on. C onnect ONB to G N D for norm al operation

(Table 1).

4 O N A

O n C ontrol Input. W hen O N A = low and ONB = high, the IC is off. C onnect O N A to PS for norm al operation

(Table 1).

5 3/5

O utput Voltage Selection Input. C onnect to PS for 3.3V output and to G N D for 5V output. W ith V

FB

> 80m V,

the state of the 3/5 pin is ignored. (Table 2).

6 PG I Low -B attery D etector Input (1.25V threshold)

7 PGO Low -B attery D etector O utput (open drain). PGO pulls low w hen V

PG I

is greater than 1.25V.

8 ILIM Inductor-C urrent-Lim it Selection Input. C onnect to PS for 0.8A current lim it and to G N D for 0.5A current lim it.

9 O U T R egulator O utput. D rain of internal PFET linear regulator. B ypass w ith a 4.7F capacitor to G N D .

10 FB

Feedback Input. For 3.3V or 5V output, connect to G N D . For adjustable output, connect to feedback resistor-

divider netw ork. W ith V

FB

> 70m V, the state of the 3/5 pin is ignored.

11 PS

B ootstrapped Pow er Supply. O utput of step-up sw itch-m ode regulator and source of internal PFET linear

regulator. The IC is pow ered from this pin.

12 IN Input Voltage Sense Input. C onnect to input supply.

13 R EF R eference Voltage O utput. B ypass w ith a 0.1F capacitor to G N D .

14 G N D A nalog G round

15 PG N D Pow er G round

16 LX Inductor C onnection to the D rain of the Internal N -C hannel Pow er M O SFET

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

6 _______________________________________________________________________________________

N

LX

ILIM

PGND

PS

OUT

100mV

MAX1672

T

ON

FIXED T

OFF

GENERATOR

DRV

REF

ERROR

AMP 2

ERROR

AMP 1

INPUT

MONITOR

CURRENT- LIMIT

COMPARATOR

OFF

FB

REFERENCE

GENERATOR

P

FB

FB1

FB2

REF + OFFSET

REF

PS

N

REF

PGI

PGO

3/ 5

FB

REF

ONB

ONA

IN

OUT

70mV

N

GND

Figure 1. Functional D iagram

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

_______________________________________________________________________________________ 7

_______________Detailed Desc ription

The M A X1672 integrates a step-up, sw itch-m ode D C -

D C converter w ith a linear regulator to provide step-

up/dow n voltage conversion. The step-up converter

contains an N -channel pow er M O SFET sw itch, w hile

the linear regulator contains a P-channel M O SFET pass

elem ent (Figure 1). The step-up converter and the lin-

ear regulator share the sam e precision voltage refer-

ence. The M A X1672s input range is from + 1.8V to

+ 11V, and the regulated output is internally preset to

+ 3.3V or + 5V, or can be adjusted w ith tw o external

resistors. B oost efficiency typically exceeds 80% over a

2m A to 200m A load range. The device is bootstrapped

w ith chip pow er derived from the stepped-up voltage

output at PS. The M A X1672 typically starts up w ith a

0.9V input.

The M A X1672s step-up/linear-regulator configuration

perm its the use of a physically sm aller inductor than

com peting SEPIC and flyback configurations because

the

1

/

2

LI

2

requirem ents of a step-up converter are half

those of SEPIC and flyback converters. A lso, high-fre-

quency sw itching and selectable peak inductor current

lim it allow for low inductor value (10H ) and low current

saturation rating, respectively, further reducing the

inductors physical dim ensions.

The M A X1672 m axim izes efficiency in both step-up and

step-dow n operation. In step-up m ode, w hen V

IN

<

V

O U T

, only the step-up regulator is active, w hile the lin-

ear regulator behaves as a 1.2 (at 5V output) PFET

sw itch. This p rovid es op tim um efficiency (typ ically

85% ).

In low -dropout, step-dow n operation, w hen V

IN

is slight-

ly greater than V

O U T

, both the step-up regulator and

linear regulator are active. The step-up regulator is

autom atically enabled to m aintain headroom across the

linear regulator (typically 1V above the 5V output). In

this case, boost ripple is rejected by the linear regula-

tor, and O U T rem ains in regulation w ith no dropout.

In norm al step-dow n operation, w hen V

IN

is significantly

greater than V

O U T

, only the linear regulator is active.

The m ode of operation is autom atically controlled on-

chip throug h the IN p in, w hich com p ares V

IN

and

V

O U T

. Transitions betw een step-up, low -dropout step-

dow n, and norm al step-dow n operation are stable, but

can be seen as sm all variations in the output D C level

and output ripple.

Step-Up Switc h-Mode Converter

A pulse-frequency-m odulation (PFM ) control schem e,

w ith a constant 1s off-tim e and variable on-tim e, con-

trols the N -channel M O SFET sw itch. A pulse is initiated

w henever O U T falls out of regulation. The N -channel

sw itch then turns off w hen the inductor current reaches

the peak current lim it or after the 4s m axim um on-tim e,

w hichever occurs first. This control architecture pro-

vides high-efficiency, discontinuous inductor current

under light loads as w ell as continuous inductor current

under heavy loads. The sw itching frequency and output

ripple are a function of load current and input voltage.

Linear Regulator

The low -dropout linear regulator consists of a refer-

ence, an error am plifier, and a P-channel M O SFET. The

reference is connected to the error am plifier input. The

error am plifier com pares this reference w ith the select-

ed feedback voltage and am plifies the difference. The

difference is conditioned and applied to the P-channel

pass transistors gate.

ILIM

The current-lim it-select input, ILIM , selects betw een the

tw o peak inductor current lim its: 0.8A (ILIM = PS) and

0.5A (ILIM = G N D ). If the application requires low out-

put current (see Typical O perating C haracteristics),

select 0.5A . The low er peak current lim it allow s for a

sm aller, low er-cost inductor, and reduced output ripple.

On/Off Control

The M A X1672 is turned on or off by logic inputs O N A

and ONB (Table 1). W hen O N A = 1 or ONB = 0, the

device is on. W hen O N A = 0 and ONB = 1, the device

shuts dow n (see the A pplications Inform ation section).

For norm al (on) operation, connect O N A to PS and

ONB to G N D . Shutdow n m ode turns off the M A X1672

com pletely, disconnecting the input from the output

and actively pulling O U T to G N D .

ONB MAX1672

0 0 O n

0 1 O ff

ONA

1 0 O n

1 1 O n

Table 1. On/Off Logic Control

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

8 _______________________________________________________________________________________

__________________Design Proc edure

Output Voltage Selec tion

For fixed output voltages of 3.3V or 5V, connect 3/5 to

P S or G N D and connect FB to G N D (Tab le 2).

A lternatively, adjust the output voltage from 1.25V to

5.5V by connecting tw o resistors, R 1 and R 2 (Figure 2),

w hich form a voltage divider betw een O U T and FB .

C hoose resistor values as follow s:

R 1 = R 2[(V

O U T

/ V

R EF

) -1]

w here V

R EF

= 1.25V. Since the input bias current at FB

has a m axim um value of 50nA , R 1 and R 2 can be large

w ith no significant accuracy loss. C hoose R 2 in the

100k to 270k rang e and calculate R 1 using the

above form ula. For 1% error, the current through R 1

should be at least 100 tim es FB s bias current.

W henever the voltag e at FB exceed s 70m V ab ove

G N D , the state of the 3/5 pin is ignored. C onnect 3/5 to

G N D w hen adjusting V

O U T

w ith a resistor divider. N ever

leave 3/5 unconnected.

Low-Battery Detec tion

The M A X1672 contains a com parator for low -battery

detection. If the voltage at PG I falls below V

R EF

(typical-

ly 1.25V), the open-drain com parator output (PGO)

goes high. H ysteresis is typically 30m V. Set the low -

battery detectors threshold w ith resistors R 3 and R 4

(Figure 2) using the follow ing equation:

R 3 = R 4[(V

PG T

/ V

R EF

) -1]

w here V

PG T

is the desired threshold of the low -battery

detector and V

R EF

= 1.25V. Since the input bias current

at PG I has a m axim um value of 50nA , R 3 and R 4 can

be large to m inim ize input loading w ith no significant

accuracy loss. C hoose R 4 in the 100k to 270k range

and calculate R 3 using the ab ove form ula. For 1%

error, the current through R 3 should be at least 100

tim es PG Is bias current.

The PGO output is open-drain and should be pulled

high w ith external resistor R 5 for norm al operation. If the

low -battery com parator is not used, connect PG I and

PGO to G N D .

Induc tor Selec tion

A 10H inductor perform s w ell in m ost M A X1672 appli-

cations. Sm aller inductor values typically offer a sm aller

physical size for a given series resistance, but m ay

increase sw itching losses. Larg er ind uctor values

exhibit higher output current capability and larger phys-

ical dim ensions for a given series resistance. For opti-

m um p erform ance, choose an ind uctor value from

Table 3 or by using the follow ing equation:

w here I

LIM

is the peak sw itch-current lim it, w hich is

0.8A for I

LIM

= PS and 0.5A for I

LIM

= G N D .

The inductors increm ental saturation current rating

should also be greater than the peak sw itch-current

lim it. H ow ever, it is generally acceptable to bias m ost

inductors into saturation by as m uch as 20% w ith slight-

ly reduced efficiency. The inductors D C resistance sig-

nificantly affects efficiency. See Tables 4 and 5 for a list

of suggested inductors and suppliers.

V + V

I

V + V

I

O U T D IO D E

LIM

IN (m in) SW ITC H

LIM

( )

<

<

( )

t L

t

O FF

O N

2

(m ax)

MAX1672

IN

ONA

PGI

ONB

OFF ON

C3

0.1F

C1

100F

C2

100F

R2

R1 R5

1M

C4

4.7F

R3

R4

L1

10H

PGND GND

PS

1.25V TO

5.5V OUTPUT

INPUT

1.8V TO 11V

LOW- BATTERY-

DETECTOR

OUTPUT

OUT

PG0

FB REF

LX

OFF

3/ 5

ILIM 0.8A

ON

0.5A

Figure 2. A djustable O utput Voltage C onfiguration

Table 2. Output Voltage Control

FB V

OUT

(V)

0 G N D + 5

1 G N D + 3.3

3/5

X > 70m V + 1.25 to + 5.5

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

_______________________________________________________________________________________ 9

Capac itor Selec tion

The equivalent series resistance (ESR ) of both bypass

and filter capacitors affects efficiency and output rip-

ple. O utput voltage ripple is the product of peak induc-

tor current and filter cap acitor E S R . U se low -E S R

capacitors for best perform ance, or connect tw o or

m ore filter capacitors in parallel.

A 100F, 16V, input bypass capacitor (C 1) w ith low

ESR reduces peak battery currents and reflected noise

due to inductor current ripple. Sm aller ceram ic capaci-

tors m ay also be used for light loads or in applications

that can tolerate higher input ripple.

A 100F, 16V, surface-m ount (SM T) tantalum PS filter

capacitor (C 2) w ith 0.1 ESR typically exhibits 20m V

output ripple (at O U T) w hen stepping up from 2V to 5V

at 100m A load. Sm aller capacitors (dow n to 10F w ith

higher ESR ) are acceptable for light loads or in applica-

tions that can tolerate higher output ripple.

O nly 4.7F is needed at O U T (C 4) to m aintain linear

regulator stability. D uring boost operation, this capaci-

tor reduces output voltage spikes from the step-up con-

verter by form ing an R -C low pass filter along w ith the

P-channel M O SFET on-resistance. O utput ripple can be

further reduced by increasing C 4.

See Tables 4 and 5 for a list of suggested capacitors

and suppliers.

Diode Selec tion

The M A X1672s high sw itching frequency dem ands a

hig h-sp eed rectifier. S chottky d iod es, such as the

1N 5817 or M B R S130T3, are recom m ended. M ake sure

the diodes current rating exceeds the m axim um load

current. See Tables 4 and 5 for a list of suggested

diodes and suppliers.

Table 3. Suggested Inductor Values Table 4. Suggested Components

ILIM

INDUCTOR VALUE

(H)

0 (5V) 0 (0.5A ) 10 to 22

0 (5V) 1 (0.8A ) 10

3/5

1 (3.3V) 0 (0.5A ) 10

1 (3.3V) 1 (0.8A ) 4.7 to 10

INDUCTORS

Sum ida

C D 43-100 (1.04A , 0.182)

C D 54-100 (1.44A , 0.100)

C D R H 73-100 (1.68A , 0.072)

L1

10H

C oilcraft

D T1608C -103 (0.7A , 0.095)

CAPACITORS

A VX

TPSE Series

Sprague

593D or 595D Series

Tantalum

DIODES

M otorola

M B R S130LT3 (1.0A , 30V)

M B R 0520LT3 (0.5A , 20V)

Schottky

1N 5817 Equivalent

International R ectifier

10B Q 40 (1.0A , 40V)

Table 5. Component Suppliers

PHONE

A VX (803) 946-0690

C oilcraft (847) 639-6400

SUPPLIER

International

R ectifier

(310) 322-3331

M otorola (602) 303-5454

FAX

(803) 626-3123

(847) 639-1469

(310) 322-3332

(602) 994-6430

Sanyo (619) 661-6835 (619) 661-1055

Sprague (603) 224-1961 (603) 224-1430

Sum ida (847) 956-0666 (847) 956-0702

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

10 ______________________________________________________________________________________

__________Applic ations Information

Using a Single, Pushbutton On/Off Switc h

A single pushbutton sw itch can be used to turn the

M A X1672 on and off. A s show n in Figure 3, O N A is

pulled low and ONB is pulled high w hen the part is off.

W hen the m om entary sw itch is pressed, ONB is pulled

low and the regulator turns on. The sw itch should be on

long enough for the C to exit reset. The controller

issues a logic high to O N A , w hich guarantees the part

w ill stay on regardless of the sw itch state.

To turn off the regulator, press the sw itch again. The

controller reads the sw itch status and pulls O N A low .

W hen the sw itch is released, ONB goes high, turning

off the M A X1672.

Thermal Overload Protec tion

Therm al overload protection lim its total pow er dissipa-

tion in the M A X1672. W hen the junction tem perature

exceeds T

J

= + 150C , the pass transistor turns off,

allow ing the M A X1672 to cool. The pass transistor turns

on again after the IC s junction tem perature cools by

20C , resulting in a pulsed output during therm al over-

load conditions.

Therm al overload protection is designed to protect the

M A X1672 if fault conditions occur. It is not intended to

be used as an operating m ode. Prolonged operation in

therm al shutdow n m ode m ay reduce the IC s reliability.

For continual operation, do not exceed the absolute

m axim um junction tem perature rating T

J

= + 150C .

Power Dissipation and Operating Region

The M A X1672s m axim um pow er dissipation in step-

dow n m ode depends on the therm al resistance of the

case and circuit board, the tem perature difference

betw een the die junction and am bient air, and the air

flow rate. The p ow er d issip ated in the d evice is

P = I

O U T

(V

IN

- V

O U T

) during step-dow n operation. The

m axim um pow er dissipation is as follow s:

P

M A X

= (T

J

- T

A

)/(

JB

+

B A

)

w here (T

J

- T

A

) is the tem perature difference betw een

the M A X1672 die junction and the surrounding air,

JB

(or

JC

) is the therm al resistance of the package, and

B A

is the therm al resistance throughout the printed cir-

cuit board, copper traces, and other m aterials to the

surrounding air. The M A X1672s therm al resistance is

120C /W . See the Typical O perating C haracteristics for

M axim um O utput C urrent vs. Input Voltage.

Layout Considerations

Proper PC board layout is essential to m inim ize noise

due to high inductor current levels and fast sw itching

w aveform s. To m axim ize output pow er and efficiency

and m inim ize output ripple voltage and ground noise,

use the follow ing g uid elines w hen d esig ning your

board:

U se a ground plane.

K eep the IC s G N D pin and the ground leads of C 1

and C 2 (Figure 2) less than 0.2in. (5m m ) apart.

M ake all connections to the FB and LX pins as short

as possible.

S old er the IC s G N D p in d irectly to the g round

plane.

R efer to the M A X1672 EV kit for a suggested PC board

layout.

MAX1672

ONA

ONB

1M

1M

I/ O

I/ O

OUT

V

DD

C

Figure 3. M om entary Pushbutton O n/O ff C ontrol

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

______________________________________________________________________________________ 11

________________________________________________________Pac kage Information

Q

S

O

P

.

E

P

S

M

A

X

1

6

7

2

Step-Up/Down DC-DC Converter

in QSOP Pac kage

12 ______________________________________________________________________________________

NOTES

You might also like

- Artwork SpecificationDocument4 pagesArtwork Specificationjnax101No ratings yet

- MC 14093Document8 pagesMC 14093rrebollarNo ratings yet

- Box ExampleDocument6 pagesBox Examplejnax101No ratings yet

- Classd Digital Amplifier TutorialDocument54 pagesClassd Digital Amplifier TutorialemerychNo ratings yet

- SG 3524Document15 pagesSG 3524jnax101No ratings yet

- Electronics 1 Practical 6: Equipment RequiredDocument1 pageElectronics 1 Practical 6: Equipment Requiredjnax101No ratings yet

- Transistor NPN 2n222aDocument8 pagesTransistor NPN 2n222aRoberto Eduardo Tenorio RamosNo ratings yet

- Applications Using The SG3524: Integrated CircuitsDocument3 pagesApplications Using The SG3524: Integrated Circuitsjnax101No ratings yet

- 28701-En LZT14606 en A PDFV1R2Document3 pages28701-En LZT14606 en A PDFV1R2jnax101No ratings yet

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDocument1 pageElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101No ratings yet

- SG3524 Application NotesDocument6 pagesSG3524 Application NotesSANDEEP KUMAR RAHEJANo ratings yet

- SG 3524Document3 pagesSG 3524florianosNo ratings yet

- LM337Document12 pagesLM337jnax101No ratings yet

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDocument1 pageElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101No ratings yet

- Elt 1 Practical 1.WpdDocument1 pageElt 1 Practical 1.Wpdjnax101No ratings yet

- Data Sheet IC LM 723Document13 pagesData Sheet IC LM 723Wahyu Sulistyo NugrohoNo ratings yet

- Electronics 1 Practical 3 Circuit WaveformsDocument2 pagesElectronics 1 Practical 3 Circuit Waveformsjnax101No ratings yet

- LM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionDocument22 pagesLM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionrutayanpNo ratings yet

- ELT 1 Prac 4Document2 pagesELT 1 Prac 4jnax101No ratings yet

- LM78XX Series Voltage Regulators: General DescriptionDocument6 pagesLM78XX Series Voltage Regulators: General DescriptiondebabratalogonNo ratings yet

- LM317Document22 pagesLM317jnax101No ratings yet

- LM393Document15 pagesLM393Izabela AlcântaraNo ratings yet

- MAX606Document12 pagesMAX606jnax101No ratings yet

- MAX608Document12 pagesMAX608jnax101No ratings yet

- MAX619Document7 pagesMAX619jnax101No ratings yet

- Max 1672Document12 pagesMax 1672jnax101No ratings yet

- Max 1674Document12 pagesMax 1674jnax101No ratings yet

- Max 1642Document12 pagesMax 1642jnax101No ratings yet

- Max 1686Document4 pagesMax 1686jnax101No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5782)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)