Professional Documents

Culture Documents

Fan 7361

Uploaded by

Odalis CabaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fan 7361

Uploaded by

Odalis CabaCopyright:

Available Formats

2005 Fairchild Semiconductor Corporation www.fairchildsemi.

com

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

November 2009

FAN7361, FAN7362 Rev. 1.0.8

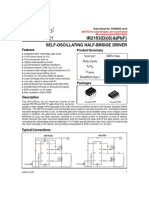

FAN7361, FAN7362

High-Side Gate Driver

Features

! Floating Channel Designed for Bootstrap

Operation to +600V

! Typically 250mA/500mA Sourcing/Sinking Current

Driving Capability

! Common-Mode dv/dt Noise Canceling Circuit

! V

CC

& V

BS

Supply Range from 10V to 20V

! UVLO Function for V

BS

! Output In-phase with Input Signal

! 8-SOP

Applications

! PDP Scan Driver

! Motor Control

! SMPS

! Electronic Ballast

Description

The FAN7361/FAN7362, a monolithic high-side gate

drive IC, can drive MOSFETs and IGBTs that operate up

to +600V. Fairchilds high-voltage process and common-

mode noise canceling techniques provide stable opera-

tion of the high-side driver under high dv/dt noise circum-

stances. An advanced level shift circuit offers high-side

gate driver operation up to V

S

=-9.8V(typ.) for V

BS

=15V.

The UVLO circuit prevents malfunction when V

BS

is

lower than the specified threshold voltage. Output drivers

typically source/sink 250mA/500mA, respectively, which

is suitable for fluorescent lamp ballast, PDP scan driver,

motor control, and so on.

8-SOP

Ordering Information

Note:

1. These devices passed wave soldering test by JESD22A-111.

For Fairchilds definition of Eco Status, please visit: http://www.fairchildsemi.com/company/green/rohs_green.html.

Part Number Package

Operating

Temperature Range

Eco Status Packing Method

FAN7361M

(1)

8-SOP -40C ~ 125C RoHS

Tube

FAN7361MX

(1)

Tape & Reel

FAN7362M

(1)

Tube

FAN7362MX

(1)

Tape & Reel

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7361, FAN7362 Rev. 1.0.8 2

Typical Application Circuit

DBOOT

IN2

CBOOT

15V

RBOOT

Q1

R1

R2

VB

IN

GND

HO

VS

NC

1

2

NC

VCC

5

6

8

3

4

7

R3

R4

600V

Q2

IN1

Load

FAN7361 Rev.04

Figure 1. Typical Application Circuit

Internal Block Diagram

UVLO

D

R

I

V

E

R

P

U

L

S

E

G

E

N

E

R

A

T

O

R

V

CC

GND

IN

V

B

HO

V

S

R

R

S Q

6

7

8 3

4

2

NOISE

CANCELLER

Pin 1 and 5 are not connection

FAN7361 Rev.04

Figure 2. Functional Block Diagram

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7361, FAN7362 Rev. 1.0.8 3

Pin Assignments

V

S

V

B

FAN7361

FAN7362 V

CC

NC

IN HO

NC 4 GND

3

2

1

5

6

7

8

FAN7361 Rev.04

Figure 3. Pin Configuration (Top View)

Pin Definitions

1 NC No Connection

2 IN Logic Input for High-Side Gate Driver Output

3 V

CC

Supply Voltage

4 GND Logic Ground

5 NC No Connection

6 V

S

High-Voltage Floating Supply Return

7 HO High-Side Driver Output

8 V

B

High-Side Floating Supply

Pin Name Function/ Description

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7361, FAN7362 Rev. 1.0.8 4

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be opera-

ble above the recommended operating conditions and stressing the parts to these levels is not recommended. In addi-

tion, extended exposure to stresses above the recommended operating conditions may affect device reliability. The

absolute maximum ratings are stress ratings only. T

A

=25C, unless otherwise specified.

V

S

High-Side Offset Voltage V

B

-25 V

B

+0.3

V

V

B

High-Side Floating Supply Voltage -0.3 625

V

HO

High-Side Floating Output Voltage V

S

-0.3 V

B

+0.3

V

CC

Logic Fixed Supply Voltage -0.3 25

V

IN

Logic Input Voltage -0.3 V

CC

+0.3

dV

S

/dt Allowable Offset Voltage Slew Rate 50 V/ns

P

D

(2)(3)(4)

Power Dissipation 0.625 W

"

JA

Thermal Resistance, Junction-to-Ambient 200 C/W

T

J

Junction Temperature +150 C

T

S

Storage Temperature +150 C

T

A

Ambient Temperature -40 +125 C

Notes:

2. Mounted on 76.2 x 114.3 x 1.6mm PCB (FR-4 glass epoxy material).

3. Refer to the following standards:

JESD51-2: Integral circuits thermal test method environmental conditions - Natural convection

JESD51-3: Low effective thermal conductivity test board for leaded surface mount packages

4. Do not exceed P

D

under any circumstances.

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

V

B

High-Side Floating Supply Voltage V

S

+10 V

S

+20

V

V

S

High-Side Floating Supply Offset Voltage 6-V

CC

600

V

HO

High-Side Output Voltage V

S

V

B

V

IN

Logic Input Voltage GND V

CC

V

CC

Logic Supply Voltage 10 20

Symbol Characteristics Min. Max. Unit

Symbol Parameter Min. Max. Unit

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7361, FAN7362 Rev. 1.0.8 5

Electrical Characteristics

V

BIAS

(V

CC

, V

BS

)=15.0V, T

A

= 25C, unless otherwise specified. The V

IN

and I

IN

parameters are referenced to GND.

The V

O

and I

O

parameters are referenced to V

S

and are applicable to the respective output HO.

V

BSUV

+

V

BS

Supply Under-Voltage Positive Going

Threshold

V

BS

=Sweep

FAN7361 8.2 9.2 10.2

V

FAN7362 7.6 8.6 9.6

V

BSUV

-

V

BS

Supply Under-Voltage Negative

Going Threshold

V

BS

=Sweep

FAN7361 7.4 8.6 9.2

FAN7362 7.2 8.2 9.2

V

BSHYS

V

BS

Supply Under-Current Lockout

Hysteresis

V

BS

=Sweep

FAN7361 0.5

FAN7362 0.4

I

LK

Offset Supply Leakage Current V

B

=V

S

=600V 10

A

I

QBS

Quiescent V

BS

Supply Current V

IN

=0V or 5V 50 80

I

QCC

Quiescent V

CC

Supply Current V

IN

=0V 30 75

I

PBS

Operating V

BS

Supply Current C

L

=1nF, f=10kHz 420 550

V

IH

Logic "1" Input Voltage

FAN7361 3.6

V

FAN7362 2.9

V

IL

Logic "0" Input Voltage

FAN7361 1.0

FAN7362 0.8

V

OH

High Level Output Voltage, V

B

-V

HO

No load 0.1

V

OL

Low Level Output Voltage, V

HO

No load 0.1

I

IN+

Logic "1" Input Bias Current V

IN

=5V 50 90

A

I

IN-

Logic "0" Input Bias Current V

IN

=0V 1.0 2.0

I

O+

Output High Short Circuit Pulse Current V

HO

=0V, V

IN

=5V, PW # 10s 200 250

mA

I

O-

Output Low Short Circuit Pulse Current V

HO

=15V, V

IN

=0V,PW # 10s 400 500

V

S

Allowable Negative V

S

Pin Voltage for IN

Signal Propagation to HO

-9.8 -7.0 V

Dynamic Electrical Characteristics

V

BIAS

(V

CC

, V

BS

)=15.0V, V

S

=GND, C

L

=1000pF and T

A

= 25C, unless otherwise specified.

t

on

Turn-on Propagation Delay V

S

=0V 120 200

ns

t

off

Turn-off Propagation Delay

(5)

V

S

=0V or 600V 90 180

t

r

Turn-on Rise Time 70 160

t

f

Turn-off Fall Time 30 100

Note:

5. This parameter guaranteed by design.

Symbol Characteristics Test Condition Min. Typ. Max. Unit

Symbol Characteristics Test Condition Min. Typ. Max. Unit

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7361, FAN7362 Rev. 1.0.8 6

Typical Characteristics

Figure 4. I

QCC

vs. Supply Voltage Figure 5. Input Bias Current vs. Input Voltage

Figure 6. V

BS

UVLO vs. Temp. Figure 7. Turn On/Off Propagation Time vs. Temp.

Figure 9. Output Sinking/Sourcing Current vs. Temp.

Figure 8. Rising/Falling Time vs. Temp.

0 5 10 15 20 25

0

10

20

30

40

50

60

70

80

V

CC

=15V

IN=COM=0V

I

Q

C

C

[

$

A

]

V

CC

[V]

-40C

25C

125C

0 2 4 6 8 10 12 14

0

50

100

150

200

-40C

25C

125C

I

I

N

[

$

A

]

V

IN

[V]

-20 0 20 40 60 80 100 120

7.5

8.0

8.5

9.0

9.5

10.0

10.5

V

B

S

[

V

]

AMBIENT TEMPERATURE [C]

VBSUVP1

VBSUVP2

VBSUVN1

VBSUVN2

0 20 40 60 80 100 120

0

20

40

60

80

100

120

140

160

180

200

AMBIENT TEMPERATURE [C]

P

R

O

P

A

G

A

T

I

O

N

D

E

L

A

Y

T

I

M

E

[

n

s

e

c

]

TON

TOFF

-20 0 20 40 60 80 100 120

10

20

30

40

50

60

70

80

90

t

r

/

t

f

[

n

s

e

c

]

AMBIENT TEMPERATURE [C]

TR

TF

-20 0 20 40 60 80 100 120

200

300

400

500

600

AMBIENT TEMPERATURE [C]

O

U

T

P

U

T

C

A

P

A

B

I

L

I

T

Y

[

m

A

]

IOH+

IOH-

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7361, FAN7362 Rev. 1.0.8 7

Switching Time Definition

Figure 10. Switching Time Test Circuit Figure 11. Input / Output Timing Diagram

HVIC

HO

V

S

V

B

V

CC

=15V

GND

IN

10$F

10$F

0.1$F

0.1$F

C

L

15V

FAN7361 Rev.03

IN

HO-V

S

50% 50%

10%

90% 90%

10%

5V

t

off

t

f

t

r

t

on

FAN7361 Rev.02

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7361, FAN7362 Rev. 1.0.8 8

Physical Dimensions

8

0

SEE DETAIL A

NOTES: UNLESS OTHERWISE SPECIFIED

A) THIS PACKAGE CONFORMS TO JEDEC

MS-012, VARIATION AA, ISSUE C,

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE MOLD

FLASH OR BURRS.

D) LANDPATTERN STANDARD: SOIC127P600X175-8M.

E) DRAWING FILENAME: M08AREV13

LAND PATTERN RECOMMENDATION

SEATING PLANE

0.10 C

C

GAGE PLANE

x 45

DETAIL A

SCALE: 2:1

PIN ONE

INDICATOR

4

8

1

C M B A 0.25

B

5

A

5.60

0.65

1.75

1.27

6.20

5.80

3.81

4.00

3.80

5.00

4.80

(0.33)

1.27

0.51

0.33

0.25

0.10

1.75 MAX

0.25

0.19

0.36

0.50

0.25

R0.10

R0.10

0.90

0.406

(1.04)

OPTION A - BEVEL EDGE

OPTION B - NO BEVEL EDGE

Figure 12. 8-Lead Small Outline Package (SOP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchilds worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

F

A

N

7

3

6

1

,

F

A

N

7

3

6

2

H

i

g

h

-

S

i

d

e

G

a

t

e

D

r

i

v

e

r

2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7361, FAN7362 Rev. 1.0.8 9

You might also like

- Air Brake SystemDocument81 pagesAir Brake SystemOdalis Caba100% (15)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- Hart Chapter 9 SolutionsDocument23 pagesHart Chapter 9 SolutionsCassio SchefferNo ratings yet

- Transformer Driver For Isolated Power Supplies: Features ApplicationsDocument29 pagesTransformer Driver For Isolated Power Supplies: Features Applicationsngongpro27No ratings yet

- 8 Pin Ic - FSQ510Document15 pages8 Pin Ic - FSQ510Raja Pathamuthu.GNo ratings yet

- Ir 2111Document15 pagesIr 2111Miltongrimi GrimilNo ratings yet

- Ca3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesDocument4 pagesCa3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesPaulo Cesar SimonettiNo ratings yet

- FAN73832 (Half-Bridge Dead Time Control)Document16 pagesFAN73832 (Half-Bridge Dead Time Control)Ismael StarkNo ratings yet

- FAN7535 PFC & Ballast Control IC: Features DescriptionDocument12 pagesFAN7535 PFC & Ballast Control IC: Features Descriptionashish_rewaNo ratings yet

- Fan 7316Document21 pagesFan 7316sontuyet82No ratings yet

- Driving Half-Bridges up to 600 VDocument30 pagesDriving Half-Bridges up to 600 VphieuxuatkhoNo ratings yet

- Multi Demul 4053Document7 pagesMulti Demul 4053Edward RinconNo ratings yet

- Features Product Summary: Led Buck Regulator Control IcDocument20 pagesFeatures Product Summary: Led Buck Regulator Control IcJess AJNo ratings yet

- Nc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description FeaturesDocument9 pagesNc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description Featuresgreentea601No ratings yet

- REVISIONSDocument7 pagesREVISIONSJose Antonio GBNo ratings yet

- Voltage-Controlled Oscillator: ... The Analog Plus CompanyDocument24 pagesVoltage-Controlled Oscillator: ... The Analog Plus CompanyMoltrevNo ratings yet

- Fan 7530Document20 pagesFan 7530aldo_suviNo ratings yet

- 74HC4051 74HCT4051: 1. General DescriptionDocument31 pages74HC4051 74HCT4051: 1. General DescriptiondonghungstbNo ratings yet

- 5-CH BTL DRIVER FOR DVD PLAYER WITH DISC BIDIRECTIONAL DRIVER AND TWO VARIABLE REGULATORSDocument8 pages5-CH BTL DRIVER FOR DVD PLAYER WITH DISC BIDIRECTIONAL DRIVER AND TWO VARIABLE REGULATORSalbinicue1No ratings yet

- 7Z08Document7 pages7Z08André Frota PaivaNo ratings yet

- Self-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Document9 pagesSelf-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Zoltán HalászNo ratings yet

- Irams10Up60A: Pd-94640 RevhDocument17 pagesIrams10Up60A: Pd-94640 RevhCleiton Da Gama GarciaNo ratings yet

- Tca 965 BDocument18 pagesTca 965 BMichael WickertNo ratings yet

- AZ3842 PWM Controller Data Sheet SummaryDocument13 pagesAZ3842 PWM Controller Data Sheet SummaryEngr Khalid IqbalNo ratings yet

- Elevador VoltajeDocument10 pagesElevador VoltajeFernando AugustoNo ratings yet

- FAN7382 High-And Low-Side Gate Driver: Features DescriptionDocument15 pagesFAN7382 High-And Low-Side Gate Driver: Features DescriptionRiza BaduaNo ratings yet

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601No ratings yet

- FSQ311Document24 pagesFSQ311zektorNo ratings yet

- 74LS573Document6 pages74LS573Negru P. PlantatieNo ratings yet

- Ir 2184Document24 pagesIr 2184buiphuoclaiNo ratings yet

- TEA5101B Ds PDFDocument6 pagesTEA5101B Ds PDFMingo YontoNo ratings yet

- Data Sheet Ic fr9886Document14 pagesData Sheet Ic fr9886Setya Budi S100% (1)

- Ir 2153Document9 pagesIr 2153SteveAbonyiNo ratings yet

- PTH12020 12 Vin: SpecificationsDocument6 pagesPTH12020 12 Vin: SpecificationsAlys AlysNo ratings yet

- Conversor Lucent 48-12VDocument16 pagesConversor Lucent 48-12VmauribravNo ratings yet

- XR-215 PLLDocument32 pagesXR-215 PLLJ Jesús Villanueva GarcíaNo ratings yet

- High and low side driver data sheet summaryDocument16 pagesHigh and low side driver data sheet summaryguiknopNo ratings yet

- Ir2181 Igbt Driver PDFDocument21 pagesIr2181 Igbt Driver PDFismifaizulNo ratings yet

- Analog Servo Drive: Description Power RangeDocument7 pagesAnalog Servo Drive: Description Power RangeElectromateNo ratings yet

- OpAmp 4580 M Data SheetDocument14 pagesOpAmp 4580 M Data SheetedzitroNo ratings yet

- 74LS109Document5 pages74LS109ЭРекиNo ratings yet

- Data Sheet TDA 7377Document8 pagesData Sheet TDA 7377Carlos MorenoNo ratings yet

- S2127Document21 pagesS2127RICHIHOTS2No ratings yet

- VO3120 2.5 A Output Current IGBT and MOSFET Driver: Vishay SemiconductorsDocument10 pagesVO3120 2.5 A Output Current IGBT and MOSFET Driver: Vishay Semiconductorsfadapow4uNo ratings yet

- FSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument12 pagesFSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionJohan BeckersNo ratings yet

- Ir 2109Document25 pagesIr 2109Chavi AlmeidaNo ratings yet

- 2A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesDocument13 pages2A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesCesar TemocheNo ratings yet

- VERTICAL DEFLECTION CIRCUIT DATA SHEETDocument12 pagesVERTICAL DEFLECTION CIRCUIT DATA SHEETd_richard_dNo ratings yet

- 1A H-Bridge Driver Delivers Up to 200kHzDocument2 pages1A H-Bridge Driver Delivers Up to 200kHzEjaz AhmadNo ratings yet

- Ir 2110Document17 pagesIr 2110Nguyen KhangNo ratings yet

- Analog Servo Drive: Description Power RangeDocument9 pagesAnalog Servo Drive: Description Power RangeElectromateNo ratings yet

- 4-Channel Secondary Monitoring IC DatasheetDocument11 pages4-Channel Secondary Monitoring IC DatasheetIdelbrando RochaNo ratings yet

- Tda 7250Document11 pagesTda 7250tica007No ratings yet

- The History of the Mysterious Voynich ManuscriptDocument88 pagesThe History of the Mysterious Voynich ManuscriptNadeem Ahmed ZafarNo ratings yet

- HPT5054 Service ManualDocument90 pagesHPT5054 Service ManualOdalis CabaNo ratings yet

- Res Plans Bldgpermit WebDocument8 pagesRes Plans Bldgpermit WebOdalis CabaNo ratings yet

- DSL InstallGuideDocument32 pagesDSL InstallGuideOdalis CabaNo ratings yet

- Pdp42v6 PlasmaDocument24 pagesPdp42v6 PlasmaMagla Cornel GabrielNo ratings yet

- Fujitsu Stylistic q584Document8 pagesFujitsu Stylistic q584conmar5mNo ratings yet

- Itpec Ip 2020 Q2Document35 pagesItpec Ip 2020 Q2gokuNo ratings yet

- Evo HTML To PDFDocument2 pagesEvo HTML To PDFumeshNo ratings yet

- IdeaPad 1 - 14IGL7Document7 pagesIdeaPad 1 - 14IGL7abdiel welmavenNo ratings yet

- Modbus Client DriverDocument9 pagesModbus Client DriverHéctor VelásquezNo ratings yet

- 5f2a ReferenceDocument1 page5f2a ReferenceJuhani KokkonenNo ratings yet

- Chapter 3 T2Document91 pagesChapter 3 T2raghu atluriNo ratings yet

- Managing A Cisco Internetwork: Sonia Hanif Roll NoDocument32 pagesManaging A Cisco Internetwork: Sonia Hanif Roll NoHassan KhanNo ratings yet

- Anr 6.42 (64200002) 0Document10 pagesAnr 6.42 (64200002) 0Moni SainjakitNo ratings yet

- Software For Automatic Potentiometric TitratorDocument8 pagesSoftware For Automatic Potentiometric Titratorstr_ilaNo ratings yet

- TL250 Quick InstallDocument4 pagesTL250 Quick InstallsiteromNo ratings yet

- Unit 5 SoftwareToolsDocument50 pagesUnit 5 SoftwareToolsconm shaligramNo ratings yet

- UTP CATEGORY 5e LAN CABLE SPECIFICATIONSDocument1 pageUTP CATEGORY 5e LAN CABLE SPECIFICATIONSbernardoNo ratings yet

- Text-To-Speech and Speech-To-Text: Licensed Under Creative Commons Attribution 2.5 License. All Rights ReservedDocument9 pagesText-To-Speech and Speech-To-Text: Licensed Under Creative Commons Attribution 2.5 License. All Rights Reserved08 itNo ratings yet

- Programming Quotes: "A good programmer is someone who always looks both ways before crossing a one-way streetDocument5 pagesProgramming Quotes: "A good programmer is someone who always looks both ways before crossing a one-way streetVidhya DharanNo ratings yet

- D72896GC30 Lesson01Document11 pagesD72896GC30 Lesson01linhniit123No ratings yet

- MODULE 2 Memoery Devices and Display SystemsDocument10 pagesMODULE 2 Memoery Devices and Display SystemsGangadhara CNo ratings yet

- Tanner Manual - HydDocument65 pagesTanner Manual - Hydkarthikp207No ratings yet

- CFC For M7 Continuous Function ChartDocument88 pagesCFC For M7 Continuous Function ChartPradeep TripathiNo ratings yet

- Docker Essentials TR 1669573518Document70 pagesDocker Essentials TR 1669573518Elvin YavuzNo ratings yet

- HP-UX 11.0 Installation and Update GuideDocument168 pagesHP-UX 11.0 Installation and Update GuideAgustin GonzalezNo ratings yet

- Delivery Release SIMATIC STEP 7 Professional / Basic V15Document7 pagesDelivery Release SIMATIC STEP 7 Professional / Basic V15disse_detiNo ratings yet

- Bose Panaray 502 A, 502 B, and 502 BEX Loudspeakers: Technical InformationDocument4 pagesBose Panaray 502 A, 502 B, and 502 BEX Loudspeakers: Technical Informationjesus barriosNo ratings yet

- Certificate: Gayatri Vidya Parishad College of Engineering Madhurawada, Visakhapatnam-530 041Document73 pagesCertificate: Gayatri Vidya Parishad College of Engineering Madhurawada, Visakhapatnam-530 041Rajat VijNo ratings yet

- Bypassing Anti Viruses by C#.NET Programming Chapter 3Document19 pagesBypassing Anti Viruses by C#.NET Programming Chapter 3Ralph LeoNo ratings yet

- Graillon User ManualDocument15 pagesGraillon User ManualHemera HadesNo ratings yet

- Dhamdhere OS2E Chapter 02 PowerPoint SlidesDocument73 pagesDhamdhere OS2E Chapter 02 PowerPoint SlidesManjunath MaddyNo ratings yet

- CGG PowerLogDocument2 pagesCGG PowerLogMuhNo ratings yet

- DesignDocument126 pagesDesignbelayNo ratings yet