Professional Documents

Culture Documents

Mos Capacitances: EEE C443 Analog and Digital VLSI Design

Uploaded by

Anurag LaddhaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Mos Capacitances: EEE C443 Analog and Digital VLSI Design

Uploaded by

Anurag LaddhaCopyright:

Available Formats

LECTURE

MOS CAPACITANCES

EEE C443 Analog and Digital VLSI Design

MOS CAPACITANCES

SCALING TECHNIQUES

SHORT CHANNEL EFFECTS

Dynamic Behavior of MOS Transistor

D

S

G

B

C

GD

C

GS

C

SB

C

DB

C

GB

The Gate Capacitance

Voltage dependent capacitances---

dynamic gate capacitance, junction

capacitances.

Voltage independent capacitances.

overlap capacitances C

GDOV

C

GSOV

MOSFET CAPACITANCES

Average Gate Capacitance

Most important regions in digital design: saturation and cut-off

Different distributions of gate capacitance for varying

operating conditions

JUNCTION Capacitances -> Cdb,

Csb

Junction Capacitance

Linearizing the Junction Capacitance

Replace non-linear capacitance by

large-signal equivalent linear capacitance

which displaces equal charge

over voltage swing of interest

EQUIVALENT LARGE SIGNAL

AREA CAPACTIANCE

Junction Capacitance

Scaling techniques

ROADMAP FOR ULSI TECHNOLOGY

*Taken as 70% of the technology parameter

++ NMOS/PMOS

Technology Generation 250 nm 180 nm 150 nm 130 nm 100 nm 70 nm 50 nm

Year (Production) 1997 1999 2001 2003 2006 2009 2012

DRAM/SRAM 256/64M 1G/256M 1G/256M 4G/1G 16G/4G 64G/16G 256/64G

DRAM chip (cm

2

) 2.8 4.0 4.45 5.6 7.9 11.2 15.8

DRAM cost (??bit) 120 60 30 15 5.3 1.9 0.66

Wafer Diameter (mm) 200 300 300 300 300 450 450

Logic gates/cm

2

3.7-8M 6.2-14M 10-16M 18-24M 39-40M 84-64M 180-100M

Logic chip (cm

2

) 3-4.8 3.4-8 3.85-8.5 4.3-9 5.2-10 6.2-11 7.5-13

Frequency (GH) 0.3-0.75 0.5-1.2 0.6-1.4 0.7-1.6 0.9-2.0 1.2-2.5 1.5-3.0

cost (m ?T) 3000 1735 1000 580 255 110 49

ASIC NRE cost (m ?T) 50 25 20 15 10 5 2.5

Power/chip (W) 70 90 110 130 160 170 175

Power Supply 2.5-1.8V 1.8-1.5V 1.5-1.2V 1.5-1.2 V 1.2-0.9V 0.9-0.6V 0.6-0.5

Levels of Metal 6 6-7 7 7 7-8 8-9 9

Oxide Thickness (nm) 4-5 3-4 2-3 2-3 1.5-2 <1.5 <1

Xj at Channel (nm) 50-100 36-72 30-60 26-52 20-40 15-30 10-20

Xj Contact (nm) 100-200 70-140 60-120 50-100 40-80 15-30 10-20

Nominal Leff (m)* 140-210 100-151 84-126 73-109 56-84 44-54 28-42

Leff Variation <20% <20% <20% <20% <20% <20% <20%

Id sat ( / m ) ++ 600/280 600/280 600/280 600/280 600/280 600/280 600/280

Ioff (nA/ m ) 1 1 3 3 3 10 10

Number of I/O pins 1450 2000 2400 3000 4000 5400 73002

RESULTS:

Density/Chip D

Delay/Ckt t

Power/Circuit P

SCALING THEORY

EEE C443 Analog and Digital VLSI Design

Why Scaling?

Technology shrinks by ~0.7/generation

With every generation can integrate 2x more

functions per chip; chip cost does not increase

significantly

Cost of a function decreases by 2x

But

How to design chips with more and more functions?

Design engineering population does not double every

two years

Hence, a need for more efficient design methods

Exploit different levels of abstraction

Technology scaling

Currently, technology scaling has a threefold

objective:

Reduce the gate delay by 30% (43% increase in

frequency)

Double the transistor density

Saving 50% of power (at 43% increase in frequency)

How is scaling achieved?

All the device dimensions (lateral and vertical) are

reduced by 1/s

Concentration densities are increased by s

Device voltages reduced by 1/s (not in all scaling

methods)

Typically 1/s = 0.7 (30% reduction in the dimensions)

EEE C443 Analog and Digital VLSI Design

Scaling Models

FULL SCALING---in accordance with poison equation

si

(d

2

V(x) /dx

2

) = (x) = q (N

D

+

- N

A

-

- n + p)

The scaling variables are:

Supply voltage: V

dd

V

dd

/ s

Gate length: L L / s

Gate width: W W / s

Gate-oxide thickness: t

ox

t

ox

/ s

Junction depth: X

j

X

j

/ s

Substrate doping: N

A

N

A

s

This is called constant field scaling because the

electric field across the gate-oxide does not change

when the technology is scaled

Some consequences of full scaling

si

(d

2

V(x) /dx

2

) = (x) = q N

D

30% scaling in the constant field regime (s =

1.43, 1/s = 0.7):

Device/die area:

W L (1/s)

2

= 0.49

In practice, microprocessor die size grows

about 25% per technology generation! This is

a result of added functionality.

Transistor density:

(unit area) /(W L) s

2

= 2.04

In practice, memory density has been scaling

as expected.

(not true for microprocessors)

Some consequences of full scaling

Gate capacitance:

W L / t

ox

1/s = 0.7

Drain current:

(W/L) (V

2

/t

ox

) 1/s = 0.7

Gate delay:

(C V) / I 1/s = 0.7

Frequency s = 1.43

In practice, microprocessor frequency has doubled

every technology generation (2 to 3 years)! This

faster increase rate is due to two factors:

the number of gate delays in a clock cycle decreases with

time (the designs become highly pipelined)

advanced circuit techniques reduce the average gate delay

beyond 30%per generation.

Some consequences of full scaling

Power dissipation:

C V

2

f (1/s)

2

= 0.49

Power density:

(1/t

ox

V

2

f ) / area 1

Active capacitance/unit-area:Power dissipation is a function of

the operation frequency, the power supply voltage and of the

circuit size (number of devices).

If we normalize the power density to V

2

f we obtain the active

capacitance per unit area for a given circuit. This parameter can

be compared with the oxide capacitance per unit area:

1/t

ox

s = 1.43

In practice, for microprocessors, the active capacitance/unit-

area only increases between 30% and 35%. Thus, the two

fold improvement in logic density between technologies is

not achieved.

Electromigration (1)

Limits dc-current to 1 mA/

m

If the power supply voltage is maintained

constant the scaling is called constant

voltage.

In this case, the electric field across the gate-

oxide increases as the technology is scaled

down.

Due to gate-oxide breakdown, below

0.8m only constant field scaling is

used.

Constant voltage scaling

The scaling variables are:

Supply voltage: V

dd

V

dd

Gate length: L L / s

Gate width: W W / s

Gate-oxide thickness: t

ox

t

ox

/ s

Junction depth: X

j

X

j

/ s

Substrate doping: N

A

N

A

s

2

Some consequences of CV scaling

si

(d

2

V(x) dx

2

) = (x) = q N

D

Device/die area:

W L (1/s)

2

= 0.49

Transistor density:

(unit area) /(W L) s

2

= 2.04

Some consequences of CV scaling

Gate capacitance:

C

GS

W L / t

ox

1/s = 0.7

Drain current:

(W/L) (V

2

/t

ox

) s = 1.43

Gate delay:

(C

GS

V

DS

) / I

D

1/ s

2

= 0.49

Frequency s

2

= 2.04

Some consequences of CV scaling

Power dissipation:

Vds*Ids = C

GS

V

2

f s = 1.43

Power density:

(P/AREA) 1/t

ox

V

2

f s

3

= 2.92

Active capacitance/unit-area:

power density/ (V

2

f ) s

EEE C443 Analog and Digital VLSI Design

Parameter Constant Field Constant Voltage

Supply voltage (V

dd

) 1/ 1

Length (L) 1/ 1/

Width (W) 1/ 1/

Gate-oxide thickness (t

ox

) 1/ 1/

Junction depth (X

j

) 1/ 1/

Substrate doping (N

A

)

Electric field across gate oxide (E) 1

Depletion layer thickness 1/ 1/

Gate area (Die area) 1/

2

1/

2

Gate capacitance (load) (C) 1/ 1/

Drain-current (I

dss

) 1/

Transconductance (g

m

) 1

Gate delay 1/ 1/

2

Current density

3

DC & Dynamic power dissipation 1/

2

Power density 1

3

Power-Delay product 1/

3

1/

Scaling

Variables

Device

Repercussion

Circuit

Repercussion

Summary =s

SCALING OF CONDUCTORS

CAPACITANCE C C/a

RESISTANCE R aR

TIME CONSTANT RC RC

CURRENT DENSITY J aJ

R=L/wt

C=

ox

A/t

EEE C443 Analog and Digital VLSI Design

Interconnects scaling:

Higher densities are only possible if the

interconnects also scale.

Reduced width increased resistance

Denser interconnects higher parasitic

capacitance

To account for increased parasitics and

integration complexity more interconnection

layers are added:

thinner and tighter layers local interconnections

thicker and sparser layers global

interconnections and power

Interconnects are scaling as expected

EEE C443 Analog and Digital VLSI Design

Multilevel Interconnect

EEE C443 Analog and Digital VLSI Design

Scaling Models Long Channel

SHORT CHANNEL EFFECTS

The Sub-Micron MOS Transistor

Threshold Variations

Parasitic Resistances

Velocity Sauturation and Mobility Degradation

Subthreshold Conduction

Latchup

Threshold Variations

V

T

L

Long-channel threshold

Low V

DS

threshold

Threshold as a function of

the length (for low V

DS

)

Drain-induced barrier lowering

(for low L)

Parasitic Resistances

W

L

D

Drain

Drain

contact

Polysilicon gate

D

S

G

R

S

R

D

V

GS,eff

Velocity Saturation (1)

E

(

V/

m)

E

sat

= 1.5

n

(

c

m

/

s

e

c

)

sat

= 10

7

Constant mobility (slope = )

constant velocity

E

t

(

V/

m)

n

(

c

m

2

/

V

s

)

n0

(b) Mobility degradation

(a) Velocity saturation

0

700

250

100

Velocity Saturation (2)

V

DS

(V)

I

D

(

m

A

)

L

i

n

e

a

r

D

e

p

e

n

d

e

n

c

e

V

GS

= 5

V

GS

= 4

V

GS

= 3

V

GS

= 2

V

GS

= 1

0.0 1.0 2.0 3.0 4.0 5.0

0.5

1.0

1.5

(a) I

D

as a function of V

DS

(b) I

D

as a function of V

GS

(for V

DS

= 5 V)

.

0.0 1.0 2.0 3.0

V

GS

(V)

0

0.5

I

D

(

m

A

)

Linear Dependence on V

GS

Sub-Threshold Conduction

0.0 1.0 2.0 3.0

V

GS

(V)

10

12

10

10

10

8

10

6

10

4

10

2

l

n

(

I

D

)

(

A

)

Subthreshold exponential region

Linear region

V

T

Latchup

(a) Origin of latchup

(b) Equivalent circuit

V

DD

R

psubs

R

nwell

p-source

n-source

n

+

n

+

p

+

p

+

p

+

n

+

p-substrate

R

psubs

R

nwell

V

DD

n-well

SPICE MODELS

Level 1: Long Channel Equations - Very Simple

Level 2: Physical Model - Includes Velocity

Saturation and Threshold Variations

Level 3: Semi-Emperical - Based on curve fitting

to measured devices

Level 4 (BSIM): Emperical - Simple and Popular

Fitting level-1 model for manual

analysis

V

GS

= 5 V

V

DS

= 5 V

V

DS

I

D

Long-channel

approximation

Short-channel

I-V curve

Region of

matching

Select k

and

such that best matching is obtained @ V

gs

= V

ds

= V

DD

Technology Evolution

Process Variations

Devices parameters vary between runs and even on

the same die!

Variations in the process parameters, such as impurity concentration den-

sities, oxide thicknesses, and diffusion depths. These are caused by non-

uniform conditions during the deposition and/or the diffusion of the

impurities. This introduces variations in the sheet resistances and transis-

tor parameters such as the threshold voltage.

Variations in the dimensions of the devices, mainly resulting from the

limited resolution of the photolithographic process. This causes (W/L)

variations in MOS transistors and mismatches in the emitter areas of

bipolar devices.

Impact of Device Variations

1.10 1.20 1.30 1.40 1.50 1.60

L

eff

(in mm)

1.50

1.70

1.90

2.10

D

e

l

a

y

(

n

s

e

c

)

0.90 0.80 0.70 0.60 0.50

V

Tp

(V)

1.50

1.70

1.90

2.10

D

e

l

a

y

(

n

s

e

c

)

Delay of Adder circuit as a function of variations in L and V

T

Latchup

(a) Origin of latchup

(b) Equivalent circuit

V

DD

R

psubs

R

nwell

p-source

n-source

n

+

n

+

p

+

p

+

p

+

n

+

p-substrate

R

psubs

R

nwell

V

DD

n-well

You might also like

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Lec 5 CMOS Technology ScalingDocument11 pagesLec 5 CMOS Technology ScalingMainak TarafdarNo ratings yet

- Scaling Factors and Scaling ParametersDocument22 pagesScaling Factors and Scaling Parametersvirajitha159467% (3)

- 3.5 MOSFET Scaling and Small-Geometry EffectsDocument19 pages3.5 MOSFET Scaling and Small-Geometry Effectspraritlamba25No ratings yet

- Vlsi Design & TechnolgyDocument60 pagesVlsi Design & TechnolgyDimple GalaNo ratings yet

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 3From EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 3Rating: 3 out of 5 stars3/5 (2)

- Class Presentation On CH 6 Interconnect: ECE 525 Digital Integrated Circuit Design-1 Presenter Zahed Reza KhurasaniDocument27 pagesClass Presentation On CH 6 Interconnect: ECE 525 Digital Integrated Circuit Design-1 Presenter Zahed Reza KhurasaniGuru VelmathiNo ratings yet

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1From EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1No ratings yet

- Scaling Mos CircuitsDocument6 pagesScaling Mos Circuitsmdhuq1No ratings yet

- IEEE Presentation On Properties of Digital Switching Currents (C'MOS)Document21 pagesIEEE Presentation On Properties of Digital Switching Currents (C'MOS)Trivendra JoshiNo ratings yet

- Stick DiagramDocument72 pagesStick DiagramBhanu Bond0% (1)

- Digital Integrated Circuits: A Design PerspectiveDocument66 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- EE42 100 Wb-Lecture19 080713-FDocument37 pagesEE42 100 Wb-Lecture19 080713-FozanistzNo ratings yet

- MOS Rabaey PDFDocument32 pagesMOS Rabaey PDFalamgirNo ratings yet

- Bwire Ans AssgDocument5 pagesBwire Ans AssgEria NalwasaNo ratings yet

- No 2 Power DissipationDocument28 pagesNo 2 Power DissipationHasanAlBannaBhuiyanNo ratings yet

- Variations Gobal LoacalDocument11 pagesVariations Gobal LoacalPullareddy AvulaNo ratings yet

- Flash ADC Design Challenges and MethodologyDocument15 pagesFlash ADC Design Challenges and MethodologyJagadeep KumarNo ratings yet

- MOSFET Scaling and Leakage CurrentsDocument43 pagesMOSFET Scaling and Leakage CurrentseleenaamohapatraNo ratings yet

- Mos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorDocument14 pagesMos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorKumar Amit VermaNo ratings yet

- MOS Transistor Theory: OutlineDocument24 pagesMOS Transistor Theory: OutlineCarlos AzevedoNo ratings yet

- CHP 2 - Mos Design and LayoutDocument104 pagesCHP 2 - Mos Design and Layoutkkece41No ratings yet

- MOSFET Scaling and Its Effects in 40 CharactersDocument109 pagesMOSFET Scaling and Its Effects in 40 CharactersLiferNo ratings yet

- Comp ArchitectureDocument21 pagesComp ArchitectureHariPrasanth GovindarajuNo ratings yet

- Scaling PDFDocument72 pagesScaling PDFMayank SinghNo ratings yet

- Spice Parameter CalculatorDocument14 pagesSpice Parameter Calculatorhamid_kh_56No ratings yet

- Earthing CalculationDocument14 pagesEarthing CalculationNatarajan Ramakrishnan100% (18)

- Gate Tunneling Current and Quantum Effects in Deep Scaled MosfetsDocument5 pagesGate Tunneling Current and Quantum Effects in Deep Scaled Mosfetsashishj1083No ratings yet

- Earthing Design Calculation ParametersDocument10 pagesEarthing Design Calculation ParametersRahul SrivastavaNo ratings yet

- A Low Noise Power 45 NM Technology Based Simultaneous Switching Noise (SSN) Reduction Model For Mixed Signal VLSI CircuitsDocument7 pagesA Low Noise Power 45 NM Technology Based Simultaneous Switching Noise (SSN) Reduction Model For Mixed Signal VLSI Circuitsdwie2254No ratings yet

- Mathcad - Ampacity CalculationDocument76 pagesMathcad - Ampacity CalculationAlex Ribeiro100% (4)

- The Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Document40 pagesThe Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004SrasVelNo ratings yet

- Microwave Networks: DR L.Anjaneyulu NIT, WarangalDocument79 pagesMicrowave Networks: DR L.Anjaneyulu NIT, Warangalnaveenchennuri_iasNo ratings yet

- NMOS FundamentalsDocument71 pagesNMOS FundamentalsManjit KaurNo ratings yet

- Low Power Delay Optimized CMOS Buffer DesignDocument6 pagesLow Power Delay Optimized CMOS Buffer DesignSwati JainNo ratings yet

- Chap4 Lect13 WireDocument18 pagesChap4 Lect13 Wirejubincb2No ratings yet

- Mos ModelsDocument39 pagesMos Modelsch0071No ratings yet

- VLSI Interconnect OptimizationDocument46 pagesVLSI Interconnect Optimizationparty0703No ratings yet

- Lecture - MOS & MOSFET-1Document21 pagesLecture - MOS & MOSFET-1Kartika MunirNo ratings yet

- Pn-Junction: Excess Minority Carrier Charge Space ChargeDocument28 pagesPn-Junction: Excess Minority Carrier Charge Space ChargePrashant Kumar SinghNo ratings yet

- Digital Integrated CircuitsDocument66 pagesDigital Integrated CircuitsRegina MerlinNo ratings yet

- PSEUDO CMOS: A DESIGN STYLE FOR LOW COST AND ROBUST FLEXIBLE ELECTRONICSDocument22 pagesPSEUDO CMOS: A DESIGN STYLE FOR LOW COST AND ROBUST FLEXIBLE ELECTRONICSjyothsnavkNo ratings yet

- The Cmos Inverter: OutlineDocument20 pagesThe Cmos Inverter: OutlinehappyharrNo ratings yet

- Chapter 7 Mosfets in Ics - Scaling, Leakage, and Other TopicsDocument43 pagesChapter 7 Mosfets in Ics - Scaling, Leakage, and Other Topicsmorcov19No ratings yet

- Filter Design PDFDocument11 pagesFilter Design PDFarunkr1No ratings yet

- Ee612 Taur4Document52 pagesEe612 Taur4sasi kiran sNo ratings yet

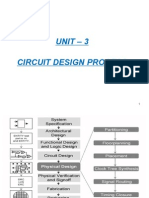

- Unit - 3 Circuit Design ProcessDocument30 pagesUnit - 3 Circuit Design ProcessNagarjun RajputNo ratings yet

- Spice Computation of MOSDocument10 pagesSpice Computation of MOSJaymee LalbhaiNo ratings yet

- MOSFET Scaling and Future DirectionsDocument22 pagesMOSFET Scaling and Future DirectionsSHAIK MUSTHAFANo ratings yet

- Interconnections and Signal Integrity: DAC TutorialDocument49 pagesInterconnections and Signal Integrity: DAC TutorialCesar Santiago Bolaño SalazarNo ratings yet

- Dančak2018 Chapter TheFinFETATutorialDocument33 pagesDančak2018 Chapter TheFinFETATutorialAhmed KamalNo ratings yet

- Long Channel MOSFET 4Document27 pagesLong Channel MOSFET 4Cruise_IceNo ratings yet

- EE603 Topic 1Document36 pagesEE603 Topic 1Shoby Kesavan PillaiNo ratings yet

- Ch. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocument43 pagesCh. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (1)

- MMIC Processing Techniques and Design ConsiderationsDocument23 pagesMMIC Processing Techniques and Design ConsiderationsVishal IyerNo ratings yet

- Microdevices: Mosfets - Metal Oxide Field Effect Transistors N MosfetDocument11 pagesMicrodevices: Mosfets - Metal Oxide Field Effect Transistors N Mosfetblue7nicoNo ratings yet

- Electrical properties and characteristics of MOSFET transistorsDocument36 pagesElectrical properties and characteristics of MOSFET transistorsDebanjan DattaNo ratings yet

- Principles of Data VisualizationDocument38 pagesPrinciples of Data VisualizationAnurag LaddhaNo ratings yet

- Allen: Neet-2017 Test Paper With Answer & Solutions (Held On Sunday 07 MAY, 2017)Document7 pagesAllen: Neet-2017 Test Paper With Answer & Solutions (Held On Sunday 07 MAY, 2017)Anurag LaddhaNo ratings yet

- Principles of Data VisualizationDocument30 pagesPrinciples of Data VisualizationAnurag LaddhaNo ratings yet

- Lecture 8 - Small MultiplesDocument43 pagesLecture 8 - Small MultiplesAnurag LaddhaNo ratings yet

- PhySICS Paper With AnswerDocument5 pagesPhySICS Paper With Answersudhir_narang_3No ratings yet

- Lecture 3 - Data ManipulationDocument51 pagesLecture 3 - Data ManipulationAnurag LaddhaNo ratings yet

- Lecture 4 - Animated Data VisualizationDocument35 pagesLecture 4 - Animated Data VisualizationAnurag LaddhaNo ratings yet

- Lecture 10 - Network VisualizationDocument57 pagesLecture 10 - Network VisualizationAnurag LaddhaNo ratings yet

- Principles of Data VisualizationDocument35 pagesPrinciples of Data VisualizationAnurag LaddhaNo ratings yet

- Lecture 2 - Data AcquisitionDocument28 pagesLecture 2 - Data AcquisitionAnurag LaddhaNo ratings yet

- Visualizing Data NarrativesDocument58 pagesVisualizing Data NarrativesAnurag LaddhaNo ratings yet

- Lecture 3 BDocument45 pagesLecture 3 BAnurag LaddhaNo ratings yet

- Lecture 7 - Integrated Analysis With RDocument79 pagesLecture 7 - Integrated Analysis With RAnurag LaddhaNo ratings yet

- How to display or delete an image file in WindowsDocument32 pagesHow to display or delete an image file in WindowsAnurag LaddhaNo ratings yet

- Fall 2017 MIS6326 SyllabusDocument13 pagesFall 2017 MIS6326 SyllabusAnurag LaddhaNo ratings yet

- Chemistry Paper With Answer PDFDocument5 pagesChemistry Paper With Answer PDFAnurag LaddhaNo ratings yet

- Lecture 2Document70 pagesLecture 2Anurag LaddhaNo ratings yet

- CMOS Technology: Only 15,432,758 More Mosfets To Do..Document30 pagesCMOS Technology: Only 15,432,758 More Mosfets To Do..manjulavkNo ratings yet

- Lecture 2Document70 pagesLecture 2Anurag LaddhaNo ratings yet

- Lecture 3cDocument34 pagesLecture 3cAnurag LaddhaNo ratings yet

- Antim Prayas PDFDocument11 pagesAntim Prayas PDFAnurag LaddhaNo ratings yet

- MOS Capacitances Scaling TechniquesDocument61 pagesMOS Capacitances Scaling TechniquesAnurag LaddhaNo ratings yet

- Lecture 1aDocument70 pagesLecture 1aAnurag LaddhaNo ratings yet

- I C ProcessingDocument9 pagesI C ProcessingAnurag LaddhaNo ratings yet

- Analog & Digital VLSI Design: A Perspective EE C443 Instructor-In-ChargeDocument21 pagesAnalog & Digital VLSI Design: A Perspective EE C443 Instructor-In-ChargeAnurag LaddhaNo ratings yet

- Designing Combinational Logic CircuitsDocument127 pagesDesigning Combinational Logic CircuitsAnurag LaddhaNo ratings yet

- Project Format and Weightage: Analog Subsystem Design, EEE C443 February 6, 2012Document3 pagesProject Format and Weightage: Analog Subsystem Design, EEE C443 February 6, 2012Anurag LaddhaNo ratings yet

- Analog Design Assignment: Analog and Digital VLSI Design - EEE C443 February 1, 2012Document9 pagesAnalog Design Assignment: Analog and Digital VLSI Design - EEE C443 February 1, 2012srishaharidasNo ratings yet

- Analog and Digital VLSI Design EEE C443: An Overview of VLSIDocument15 pagesAnalog and Digital VLSI Design EEE C443: An Overview of VLSIAnurag LaddhaNo ratings yet

- Differences between GTO and IGBT devicesDocument3 pagesDifferences between GTO and IGBT devicesDevarshi GaurNo ratings yet

- Bilayer CVD Graphene FetsDocument4 pagesBilayer CVD Graphene FetsHOD EEENo ratings yet

- 9T16GH MOSFET CANAL N SMDDocument4 pages9T16GH MOSFET CANAL N SMDVictorManuelBernalBlancoNo ratings yet

- Datasheet UMT3904 PDFDocument4 pagesDatasheet UMT3904 PDFPablo Andres Montenegro VargasNo ratings yet

- Efficient Photolithography Technique: Multi-Patterning LithographyDocument29 pagesEfficient Photolithography Technique: Multi-Patterning LithographyKrishna Saroja SankaNo ratings yet

- Irfz 24 NSPBFDocument11 pagesIrfz 24 NSPBFGalvan Javier LeonardoNo ratings yet

- DLD Assignment PDFDocument3 pagesDLD Assignment PDFMuhammad AliNo ratings yet

- Electronic Devices and Circuit Theory: Bipolar Junction TransistorsDocument26 pagesElectronic Devices and Circuit Theory: Bipolar Junction TransistorsKavinesh AnanthanNo ratings yet

- Poster Electronic Components1Document2 pagesPoster Electronic Components1RJ BevyNo ratings yet

- MMP60R360PDocument10 pagesMMP60R360PLalo NajeraNo ratings yet

- R1632043 III B. Tech II Semester Regular Examinations VLSI DesignDocument4 pagesR1632043 III B. Tech II Semester Regular Examinations VLSI Designpawan100% (1)

- Power Electronics Ned Mohan Slides Ch21Document27 pagesPower Electronics Ned Mohan Slides Ch21Anoop MathewNo ratings yet

- Analog VLSI Design: Technology TrendsDocument31 pagesAnalog VLSI Design: Technology TrendsSathyaNarasimmanTiagarajNo ratings yet

- IC Packaging 2008Document26 pagesIC Packaging 2008Angelo CorderoNo ratings yet

- Item # Manufacturer Ref Des Qty MFG Part #: XXXX XXXX XXXXX Xxpcs Bom (Sample Bill of Materials)Document3 pagesItem # Manufacturer Ref Des Qty MFG Part #: XXXX XXXX XXXXX Xxpcs Bom (Sample Bill of Materials)KenrickNo ratings yet

- Optimos - 5 Power-Transistor: Product SummaryDocument9 pagesOptimos - 5 Power-Transistor: Product SummarycqlNo ratings yet

- Introduction To Cmos Vlsi Design: Nonideal TransistorsDocument30 pagesIntroduction To Cmos Vlsi Design: Nonideal TransistorsSumanth VarmaNo ratings yet

- PhototransnsitorDocument8 pagesPhototransnsitorVipan SharmaNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationLeandro MarconNo ratings yet

- Integrated Circuits Training NotesDocument12 pagesIntegrated Circuits Training NotesDasNo ratings yet

- MTP3N120EDocument8 pagesMTP3N120EAdilson LucaNo ratings yet

- A New CMOS Charge Pump For Low Voltage ApplicationsDocument4 pagesA New CMOS Charge Pump For Low Voltage Applicationskhausar1785No ratings yet

- Photodiode Investigatory ProjectDocument25 pagesPhotodiode Investigatory ProjectSajjad AliNo ratings yet

- Effect of light intensity on LDRDocument3 pagesEffect of light intensity on LDRAlura100% (1)

- TransistorsDocument4 pagesTransistorsapi-3713690No ratings yet

- Troubleshoot and repair RB450Gr2v3 router boardDocument8 pagesTroubleshoot and repair RB450Gr2v3 router boardCipri CroitorNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument11 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataViviana AlbornozNo ratings yet

- Anexa A1 SMD - 435A - Slabu - AndreiDocument9 pagesAnexa A1 SMD - 435A - Slabu - AndreiAndrei SlabuNo ratings yet

- MOSFET Digital Electronics Analysis and DesignDocument45 pagesMOSFET Digital Electronics Analysis and DesignsitiNo ratings yet

- Ultrasonic and Megasonic CleaningDocument10 pagesUltrasonic and Megasonic CleaninglukeaspergerNo ratings yet