Professional Documents

Culture Documents

An 610

Uploaded by

aceratm1Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

An 610

Uploaded by

aceratm1Copyright:

Available Formats

AN-610

Application Note

One Technology Way P.O. Box 9106 Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 www.analog.com

The PGA on - ADCs

by Adrian Sherry

Rev. A | Page 1 of 4

INTRODUCTION

The AD7708/AD7718, AD7709, AD7719, and AD7782/

AD7783 high resolution - ADCs feature a programmable

gain amplifier (PGA) at the input to the - modulator as

shown in Figure 1.

MUX BUF PGA

-

MODULATOR

0

3

1

8

3

-

0

0

1

Figure 1. - ADC with PGA

This application note discusses the use and benefits of

this PGA.

INPUT RANGES

The programmable gain amplifier (PGA) on the AD7708/

AD7709/AD7718/AD7719 offers a choice of eight input ranges

to the ADC. With a 2.5 V reference, the eight differential ranges

are nominally 2.56 V, 1.28 V, 640 mV, 320 mV, 160 mV,

80 mV, 40 mV, and 20 mV. In unipolar mode, the range is

from 0 V to 2.56 V, and so on. If the reference is doubled to 5 V,

then the maximum full-scale input for each range is doubled.

Similarly, if the reference is halved, the full-scale range is also

halved. Thus, the actual signal range for any PGA setting is

RN

REF

V

7

2

024 . 1

where RN is the value of the 3-bit signal RN[2:0]. For now, a

2.5 V reference will be assumed, so the range with RN[2:0] =

111 is equal to 2.56 V. This is also referred to as the gain-of-1

range. On the AD7782/AD7783, there are two ranges available,

2.56 V and 160 mV.

OVERRANGE CAPABILITY

The input range with a 2.5 V reference when RN[2:0] = 111 is

2.56 V, that is, the maximum full-scale input is 1.024 times the

reference input. This effectively means that the ADC has a 2.4%

overrange capability, so it can convert signals slightly more

positive than the reference. This needs to be considered if

performing system full-scale calibrations because applying a

full-scale input of +VREF and initiating a system full-scale

calibration will change the input range to VREF, that is, 2.5 V

with a + 2.5 V reference. An internal full-scale calibration

internally connects VREF to the ADC inputs for the calibration,

but the calibration routine compensates for the 2.4% overrange

to result in a 2.56 V range after calibration.

NOISE/RESOLUTION

The primary benefit of having a PGA is that the noise, in terms

of F, decreases when the gain is increased. In effect, the input

signal is gained up before being applied to the ADC, but the

noise contribution is not gained up to the same extent, so there

is an improvement in the signal-to-noise ratio. The noise does

not quite halve when moving to the next highest gain, so the

resolution (in bits) decreases as the higher gains are selected,

(an LSB on a high gain setting is smaller than an LSB on a low

gain setting.) However, the resolution of a given input span does

improve on the high gain settings.

For example, a 20 mV full-scale input signal can be converted

with 0.52 V of rms noise on the 20 mV range, whereas if this

same signal were converted on the 2.56 V range, the noise

would be 2 V. Therefore, a p-p noise resolution of 150 ppm of

20 mV can be achieved on the high gain range, but only

600 ppm p-p resolution of a 20 mV signal can be achieved on

the 2.56 V range.

The typical noise of an AD7719 on all ranges at one update rate

is shown in Table 1.

Table 1. AD7719 Unbuffered Mode RMS Noise at 19.79 Hz Update Rate

2.56 V 1.28 V 640 mV 320 mV 160 mV 80 mV 40 mV 20 mV

RMS Noise 2.0 V 1.21 V 0.82 V 0.56 V 0.56 V 0.56 V 0.56 V 0.52 V

P-P Res. 18.5 bits 18 bits 17.5 bits 17 bits 16 bits 15 bits 14 bits 13 bits

AN-610 Application Note

Rev. A | Page 2 of 4

TABLE OF CONTENTS

Introduction ...................................................................................... 1

Input Ranges...................................................................................... 1

Overrange Capability ....................................................................... 1

Noise/Resolution .............................................................................. 1

Revision History ............................................................................... 2

Offset Errors...................................................................................... 3

Range Matching.................................................................................3

Calibrations ........................................................................................3

Offset Register....................................................................................3

Input Currents ...................................................................................4

Summary ............................................................................................4

REVISION HISTORY

1/11Rev. 0 to Rev. A

Updated Format..................................................................Universal

Changes to Input Currents Section................................................ 4

2/03Revision 0: Initial Version

Application Note AN-610

Rev. A | Page 3 of 4

OFFSET ERRORS

A problem with changing ranges on many other ADCs with

PGAs is that the ADC offset may change with range, so offset

calibrations are generally necessary after changing gain. However,

with this family of chopped ADCs, the ADC offset error is

insignificant, so there is no appreciable change in ADC offset

when changing to another range. If the AD7708 or AD7718

is used with chopping disabled, offset calibrations should be

performed when the range is changed.

RANGE MATCHING

Previous implementations of PGAs have partially relied on

techniques such as binarily weighted circuit elements that are

selectively switched in or out as the gain is changed. Because

of manufacturing mismatches between these components, the

gain does not exactly scale by two when the range is changed,

meaning that an analog input will convert to different values

depending on which gain is selected.

This family of ADCs from Analog Devices, Inc., uses a

proprietary switching scheme to implement the PGA by using

scaled sampling rates. This yields excellent matching between

the different ranges, that is, a given analog input converts to

a very similar value on different ranges. The specification on

range matching is 2 V typical, which means there will

typically be only a 2 V difference between conversion results

of a fixed input on any of the eight ranges. (Note that this refers

to the average dc result of a number on conversions rather than

just a single reading, since the peak-to-peak noise on the 2.56 V

range is greater than 2 V.)

The combination of very small offset error and accurate gain

matching greatly simplifies the process of auto ranging using

the ADC. If the input signal is low level, it can be converted

with maximum resolution on a high gain setting, but if the

signal overranges the ADC, then the next lower gain setting

can be selected and used immediately, without recalibrating

the ADC.

Figure 2 illustrates a 19.92 mV signal being converted across all

eight ranges. No offset or gain calibrations are performed when

the range changes. As can be seen, the mean code only varies by

2 V to 3 V across the eight ranges.

0

3

1

8

3

-

0

0

2

19.928

19.926

19.924

19.922

19.920

19.918

RN

0 1 2 3 4 5 6 7

m

V

Figure 2. Range Matching Across All Ranges

CALIBRATIONS

A major advantage of accurate gain tracking is that an ADC

calibration performed at one gain setting is also valid on the

other gain settings. Previously, most ADCs with a PGA had to

be recalibrated whenever the gain was changed, which reduced

the ADC throughput; now a single ADC gain calibration is suffi

cient. This allows the ADC to be calibrated in the factory on the

2.56 V range and used on any other range without recalibrating.

The AD7708/AD7718/AD7719 do have an internal ADC

calibration mode available, but this should only be necessary if

the ADC is operating at conditions significantly different from

the factory calibration conditions given in the data sheet. The

expected change in gain can be determined from the PSR and

gain drift vs. temperature specifications in the data sheet. If the

maximum expected change in gain is higher than the error

budget for the application, then recalibration can be performed

periodically.

OFFSET REGISTER

One situation on the AD7708/AD7718/AD7719 in which the

ADC can produce apparently different conversion results on

different ranges is if the offset register contains a value other

than the default 8000(00)H, as a result of a system offset

calibration or by writing into the offset register. The weight of

an offset register LSB depends on the selected range, so a value

8001(00)H removes twice as much offset on the 2.56 V range

than on the 1.28 V range. If a system offset calibration were

performed on one range with a nonzero analog input to the

ADC, there would be nonzero ADC results if the same input

were to be converted on another range. Therefore, care must be

taken when changing range if the offset register contains

something other than the default 8000(00)H.

AN-610 Application Note

Rev. A | Page 4 of 4

INPUT CURRENTS

The PGA varies the input and reference sampling rates in

implementing the various gains, altering the dynamic load

presented by the switched capacitor circuit. This could lead to

gain and/or linearity errors due to external source impedances.

However, with a buffer present at the ADC input prior to the

PGA, minimal current is drawn by the analog inputs, and this

current does not vary with input range. The AD7719 can

operate with the buffer bypassed, so it is important to take care

with external resistor and capacitor combinations in this case.

The reference sampling rate seen at the pin is fixed at 524 kHz

for the 2.56 V to 320 mV ranges, and the reference sampling

capacitor is also fixed, so there is no variation in reference

current across these ranges. Therefore, any gain error due

to resistance on the reference input remains fixed across

these ranges.

If the reference current varied with range, any gain error caused

by external resistance/capacitance on the reference would vary

with range, so the benefit of having an ADC with excellent

range matching could be lost. The reference current on these

ADCs does vary at higher gain ranges, so care needs to be taken

if the PGA gain is changed and there are external impedances

on the reference input.

0

3

1

8

3

-

0

0

3

C

IN

C

REF

f

IN

= 64kHz 524kHz

f

REF

= 524kHz

A

IN

(+)

A

IN

()

REF

IN

(+)

REF

IN

()

1nA MAX BUF

Figure 3. Input and Reference Model

SUMMARY

The PGA on this family of ADCs offers the benefit of higher

resolution/lower noise at high gains, but without the disadvantage

of requiring regular calibration every time the range is changed.

A buffered input and a new reference sampling scheme avoid

many of the problems associated with previous multirange ADCs.

20032011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

AN03183-0-1/11(0)

You might also like

- IAG - FAQ - All Common Motion - How To Set INP (In Position) Logic With Common Motion UtilityDocument1 pageIAG - FAQ - All Common Motion - How To Set INP (In Position) Logic With Common Motion Utilityaceratm1No ratings yet

- ADAM-3600 RESTful SpecificationDocument41 pagesADAM-3600 RESTful Specificationaceratm1No ratings yet

- APAX-5000 Series Manual Ver1.15Document68 pagesAPAX-5000 Series Manual Ver1.15aceratm1No ratings yet

- Aimb-210 DSDocument2 pagesAimb-210 DSaceratm1No ratings yet

- AIMB-240 User's Manaul 2nd EditionDocument99 pagesAIMB-240 User's Manaul 2nd Editionaceratm1No ratings yet

- User Manual: 8/16-Port RS-232/422/485 Serial Device ServerDocument92 pagesUser Manual: 8/16-Port RS-232/422/485 Serial Device Serveraceratm1No ratings yet

- ADAM-4572 - EKI-1221 - 1222 - 1224 - 1221D - 1222D Manual - Ed3Document62 pagesADAM-4572 - EKI-1221 - 1222 - 1224 - 1221D - 1222D Manual - Ed3kaicyemNo ratings yet

- Aimb-210 User Manual Ed-2 Final2Document96 pagesAimb-210 User Manual Ed-2 Final2aceratm1No ratings yet

- Aimb-280 User Manual Ed-1 FinalDocument96 pagesAimb-280 User Manual Ed-1 Finalaceratm1No ratings yet

- EDG-4100 Manual Ed1Document44 pagesEDG-4100 Manual Ed1aceratm1No ratings yet

- Aimb-210 DSDocument2 pagesAimb-210 DSaceratm1No ratings yet

- Aimb-210 User Manual Ed-2 Final2Document96 pagesAimb-210 User Manual Ed-2 Final2aceratm1No ratings yet

- ActiveSync User GuideDocument10 pagesActiveSync User Guideaceratm1No ratings yet

- 2 To 1 Transparent ServerDocument1 page2 To 1 Transparent Serveraceratm1No ratings yet

- 2 To 1 Transparent ServerDocument1 page2 To 1 Transparent Serveraceratm1No ratings yet

- Service Statistician WebDocument12 pagesService Statistician Webaceratm1No ratings yet

- DataStream and EventTrigger package detailsDocument1 pageDataStream and EventTrigger package detailsaceratm1No ratings yet

- ADAM-6000 Series Manual Ed2Document266 pagesADAM-6000 Series Manual Ed2aceratm1No ratings yet

- Service Statistician WebDocument12 pagesService Statistician Webaceratm1No ratings yet

- Data Acquisition in CSharpDocument40 pagesData Acquisition in CSharpLê Duy MinhNo ratings yet

- Service Statistician WebDocument12 pagesService Statistician Webaceratm1No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Aor Ar5001d Operating ManualDocument95 pagesAor Ar5001d Operating ManualRustemNo ratings yet

- ISGEC Heavy Engineering Limited: Checklist For Equipment InspectionDocument43 pagesISGEC Heavy Engineering Limited: Checklist For Equipment Inspectionallu arunNo ratings yet

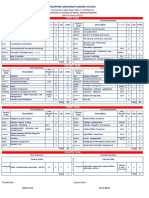

- Philippine Merchant Marine School: First YearDocument5 pagesPhilippine Merchant Marine School: First YearCris Mhar Alejandro100% (1)

- Class 11 Computer Science (Society Law and Ethics)Document19 pagesClass 11 Computer Science (Society Law and Ethics)prateekurmaliya5No ratings yet

- Apple Watch Series 3 - Apple (AU)Document1 pageApple Watch Series 3 - Apple (AU)garethNo ratings yet

- Source of Business IdeasDocument30 pagesSource of Business IdeasHannie Salve Bodomo100% (2)

- Quiz Questions on Internet ConceptsDocument3 pagesQuiz Questions on Internet Conceptsjohn100% (1)

- YUTAKI S Technical Bulletin Doc6286 v1 en-EUDocument18 pagesYUTAKI S Technical Bulletin Doc6286 v1 en-EUstomakosNo ratings yet

- Rpa SheetDocument5 pagesRpa SheetGaurav PoddarNo ratings yet

- GC-1M Operators ManualDocument12 pagesGC-1M Operators Manualnhocti007No ratings yet

- Design and Construction Standards For Kiosk Type SubstationsDocument37 pagesDesign and Construction Standards For Kiosk Type SubstationsFlo MircaNo ratings yet

- Hoosier Tire Midwest-PlymouthDocument2 pagesHoosier Tire Midwest-PlymouthAkbar SatrioNo ratings yet

- Practical Guide: Uses at Home: Task Suggested Activities TipsDocument1 pagePractical Guide: Uses at Home: Task Suggested Activities TipsAdelina SilvaNo ratings yet

- Social Media Marketing in IndiaDocument23 pagesSocial Media Marketing in IndiaYash MandaliaNo ratings yet

- Quick PDF Library Developer Guide September 01, 2009: DesktopDocument35 pagesQuick PDF Library Developer Guide September 01, 2009: DesktopDEBNo ratings yet

- UntitledDocument7 pagesUntitledVar UnNo ratings yet

- Application of The Rain-Flow Counting Method in Fatigue: Guojun Liu Dahuan Wang and Zeyou HuDocument5 pagesApplication of The Rain-Flow Counting Method in Fatigue: Guojun Liu Dahuan Wang and Zeyou HuMuhammad FaizNo ratings yet

- Useful verbs and workstation componentsDocument3 pagesUseful verbs and workstation componentsAlvaro Cesar Pereira de SouzaNo ratings yet

- Collaboration Explained - Faciliation Skills For Software Project LeadersDocument432 pagesCollaboration Explained - Faciliation Skills For Software Project LeaderscultimNo ratings yet

- Commodore 64 Programmer's Reference GuideDocument395 pagesCommodore 64 Programmer's Reference GuidemjmtNo ratings yet

- Ingun Ada Catalogue enDocument80 pagesIngun Ada Catalogue enMichael DoyleNo ratings yet

- Dffa b10100 02 7600.pdDocument8 pagesDffa b10100 02 7600.pdTraian SerbanNo ratings yet

- Newlester PhilipsDocument49 pagesNewlester PhilipsCarlos D MauroNo ratings yet

- CH 5 - Engine ElectricalDocument62 pagesCH 5 - Engine ElectricalEnrrique LaraNo ratings yet

- Ella Mae C. Acla Resume 2023 PDFDocument2 pagesElla Mae C. Acla Resume 2023 PDFMark Wilber Diano GuzonNo ratings yet

- Chemgineering OGLASDocument2 pagesChemgineering OGLASSrdjanNo ratings yet

- Electrical Sys - FGPSDocument52 pagesElectrical Sys - FGPSsatender_kumar86100% (1)

- Low Pressure CO2 SystemsDocument4 pagesLow Pressure CO2 SystemsNarineNo ratings yet

- Bizgram Export FileDocument58 pagesBizgram Export FileBizgram Asia0% (1)

- Group 20 M191en 05 2015 PDFDocument46 pagesGroup 20 M191en 05 2015 PDFDavid Solis0% (1)