Professional Documents

Culture Documents

Arquitectura IA 32

Uploaded by

Ivonne DíazCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Arquitectura IA 32

Uploaded by

Ivonne DíazCopyright:

Available Formats

Aprendiendo Sistemas Operativos:

Programacin de Procesadores de

Arquitectura IA-32

Este documento forma parte de la serie Aprendiendo Sistemas Operativos y sirve como una

introduccin a los aspectos bsicos de la programacin de procesadores de arquitectura IA-32. La

serie Aprendiendo Sistemas Operativos puede ser usada en un entorno acadmico previa

autorizacin del autor.

La serie Aprendiendo Sistemas Operativos tiene derechos reservados del autor. Queda prohibida

su reproduccin total o parcial sin autorizacin expresa del autor. La serie Aprendiendo Sistemas

Operativos no podr ser usada para fines comerciales sin autorizacin expresa del autor y luego

de pagar al mismo los costos de licenciamiento en las condiciones estipuladas para tal fin.

El Autor no ser bajo ninguna circunstancia responsable por perjuicios causados por el uso este

material o por trabajos derivados y/o adaptaciones del mismo. Asimismo, EL Autor no se hace

responsable por omisiones, errores o imprecisiones que puedan existir en el material. Los

comentarios, correcciones y observaciones se pueden enviar a la informacin de contacto del

autor que se encuentra al final de esta pgina.

Las marcas y los nombres de procesadores, herramientas, y sistemas operativos mencionados en

el documento tienen derechos reservados de sus titulares.

Autor:

Erwin Meza Vega

emezav@gmail.com

1 Generalidades de la arquitectura IA-32

Intel, el fabricante de estos procesadores de arquitectura IA-32, ha decidido mantener

compatibilidad hacia atrs para permitir que el cdigo desarrollado para procesadores desde 386

o 486 pueda ser ejecutado en procesadores actuales. Lo anterior implica una serie de decisiones

de diseo en la estructura interna y en el funcionamiento de los procesadores, que en ciertas

ocasiones limita a los programas pero que tambin ofrece una ventaja competitiva relacionada

con la adopcin masiva este tipo de procesadores y la posibilidad de ejecutar programas creados

para procesadores anteriores en las versiones actuales sin ninguna modificacin.

En los siguientes apartados se presentarn los aspectos generales de la arquitectura IA-32

requeridos para contar con una base slida, que permita iniciar con el desarrollo de programas en

ensamblador y en lenguaje C.

1.1 RESEA HISTRICA DE IA-32

Los procesadores Intel tienen sus orgenes en el 8086 y el 8088 (finales de los aos 70).

Implementaban la segmentacin de memoria como una estrategia para referenciar direcciones de

memoria mayores a las que se podan almacenar en un registro de propsito general. Usando la

combinacin de registros de segmento y registros de propsito general de 16 bits, estos

procesadores podan referenciar hasta 1 MB de memoria.

Intel introdujo los procesadores 286 a principios de los aos 80. Estos procesadores fueron los

primeros en implementar el modo protegido y el manejo de memoria virtual. En este modo

protegido, los procesadores podan referenciar hasta 16 MB de memoria.

La arquitectura IA-32 tiene su inicio oficial con el procesador 386, que fue introducido a mediados

de los aos 80. Este contaba con registros de propsito general de 32 bits, con lo cual desde el

punto de vista terico era posible referenciar hasta 4 GB (2

32

bytes) de memoria RAM. Tambin

inclua un modo especial, llamado Modo Virtual 8086, que ofreca compatibilidad para los

programas desarrollados para procesadores anteriores. Adicionalmente el 386 implementaba un

esquema ms general de segmentacin e implementaba la paginacin, que consiste en dividir la

memoria en regiones lgicas de igual tamao denominadas pginas.

A finales de los aos 80 se introdujo el procesador 486, que marc un hito en la historia del

computador personal (PC). Unido a los primeros sistemas operativos para PC, este procesador fue

uno de los principales promotores de la computacin personal una escala no vista hasta entonces.

El procesador 486 mejoraba el desempeo de su predecesor, incluyendo la capacidad de tener

varias instrucciones en diferentes niveles de ejecucin al mismo tiempo. Tambin implementaba

una memoria cach de primer nivel dentro del procesador, con lo cual se aumentaba la posibilidad

de ejecutar una instruccin en un ciclo de reloj. Adicionalmente, el 486 inclua una unidad de

punto flotante y capacidades para el manejo de la energa.

A principios de los aos 90 apareci el procesador Pentium, que por su diseo mejor

notablemente las capacidades del 486. Los aspectos ms notables de los procesadores Pentium y

posteriores (Pentium II, III, etc.) fueron su capacidad para ejecutar varias instrucciones por ciclo de

reloj, la introduccin de un segundo nivel de cach y la adicin de las extensiones MMX (diseadas

para acelerar el desempeo de la multimedia y las comunicaciones).

Los procesadores posteriores hasta los que estn disponibles hoy en da se dividen en familias que

incluyen caractersticas entre las que sobresalen: mltiples ncleos de procesamiento (por

ejemplo Dual Core, Core 2 duo o Xeon), arquitectura de 64 bits, mejoras en el cach, mejoras en la

gestin de energa, caractersticas para movilidad y tecnologas de virtualizacin (VT). Las familias

ms importantes de procesadores Intel en la actualidad son: Pentium, Core, Core 2, Itanuim y

Xeon.

Cada procesador actual cuenta con algunas o todas las caractersticas de la arquitectura IA-32. Por

ejemplo, algunos procesadores actuales poseen mltiples ncleos con registros de 32 bits o

mltiples ncleos con registros de 64 bits. Por ejemplo, un procesador Intel Core 2 Duo cuenta

con dos ncleos con registros de 32 bits, y un procesador Xeon generalmente incluye varios

ncleos con registros de 64 bits. La generacin actual de procesadores Intel Core (Core I3, Core I5

y Core I7) implementan arquitecturas de 2, 4 y hasta 6 ncleos con registros de 64 bits.

No obstante, para mantener la compatibilidad hacia atrs, todos los procesadores inician en un

modo en el cual se comportan como un procesador 8086 muy rpido, con algunas extensiones que

le permiten habilitar el modo de operacin en el cual aprovechan todas sus caractersticas. Esto

ofrece una posibilidad sin igual para el aprendizaje de la programacin bsica de procesadores de

la arquitectura IA-32.

1.2 CARACTERSTICAS DE LA ARQUITECTURA IA-32

A continuacin se enumeran las caractersticas ms importantes que ofrece la arquitectura IA-32

para la ejecucin de programas.

1.2.1 Modos de operacin

Los procesadores IA-32 pueden operar en varios modos, entre los que sobresalen:

Modo protegido: Este es el modo nativo del procesador. Aprovecha todas las

caractersticas de su arquitectura, tales como registros de 32 bits, y el acceso a todo su

conjunto de instrucciones y extensiones.

Modo real (Modo de direcciones reales): En este modo el procesador se encuentra en un

entorno de ejecucin en el cual se comporta como un 8086 muy rpido, y slo tiene

acceso a un conjunto limitado de instrucciones que le permiten ejecutar tareas bsicas y

habilitar el modo protegido. La limitacin ms notable en este modo consiste en que slo

se puede acceder a los 16 bits menos significativos de los registros de propsito general, y

slo se pueden utilizar los 20 bits menos significativos del bus de direcciones. Esto causa

que en modo real solo se pueda acceder a 1 Megabyte de memoria.

Modo de mantenimiento del sistema: En este modo se puede pasar a un entorno de

ejecucin limitado, para realizar tareas de mantenimiento o depuracin.

Modo Virtual 8086: Este es un sub-modo al cual se puede acceder cuando el procesador

opera en modo protegido. Permite ejecutar cdigo desarrollado para 8086 en un entorno

multi-tarea y protegido.

Modo IA32-e: Para procesadores de 64 bits, adems de los modos anteriores existen otros

dos sub-modos: modo de compatibilidad y modo de 64 bits. El modo de compatibilidad

permite la ejecucin de programas desarrollados para modo protegido sin ninguna

modificacin, y el modo de 64 bits proporciona soporte para acceder a los 64 bits de los

registros y un espacio de direcciones mayor que 64 Gigabytes.

1.2.2 Entorno de ejecucin

Cualquier programa o tarea a ser ejecutado en un procesador de arquitectura IA-32 cuenta con un

entorno de ejecucin compuesto por un espacio de direcciones de memoria y un conjunto de

registros. A continuacin se describen estos componentes.

1.2.2.1 Espacio de direcciones de memoria

En la arquitectura IA-32 la memoria puede ser vista como una secuencia lineal (o un arreglo) de

bytes, uno tras del otro. A cada byte le corresponde una direccin nica (Ver figura).

El cdigo dentro de una tarea o un programa puede referenciar un espacio direcciones de hasta 4

Gigabytes. Este espacio lineal puede estar mapeado directamente a la memoria fsica, con lo cual

se tendr acceso a 4 Gigabytes de RAM (2

32

direcciones lineales diferentes). Si el procesador

cuenta con las extensiones requeridas, es posible acceder a un espacio fsico de hasta 64

Gigabytes.

1 byte

Direccin lineal

0

size

Siguiente direccin lineal

1 byte

1.2.2.2 Espacio de direcciones de Entrada / Salida

Los procesadores IA-32 incluyen otro espacio de direcciones, diferente al espacio de direcciones

lineal, llamado espacio de direcciones de Entrada / Salida. A este espacio de 65536 (64K)

direcciones se mapean los registros de los controladores de dispositivos de entrada / salida como

el teclado, los discos o el mouse (Ver figura). Su acceso se realiza a travs de un par de

instrucciones especficas del procesador (in y out).

1.2.2.3 Registros

El procesador cuenta con una serie de registros en los cuales puede almacenar informacin. Estos

registros pueden ser clasificados en:

Registros de propsito general: Estos registros son utilizados para almacenar valores,

realizar operaciones aritmticas o lgicas o para referenciar el espacio de direcciones

lineal. En procesadores de 32 bits existen ocho (8) registros de propsito general, cada

uno de los cuales tiene un tamao de 32 bits. Estos registros son: EAX, EBX, ECX, EDX, ESI,

EDI, ESP y EBO. A pesar que se denominan registros de propsito general, y pueden ser

utilizados como tal, estos registros tienen usos especiales para algunas instrucciones del

procesador.

Registros de segmento: Estos registros permiten almacenar apuntadores al espacio de

direcciones lineal. Los procesadores IA-32 poseen seis (6) registros de segmento. Estos

son: CS (cdigo), DS (datos), ES, FS, GS (datos), y SS (pila). Su uso depende del modo de

operacin. En modo real, los registros de segmento almacenan un apuntador a la direccin

lineal del inicio del segmento dividida en 16. En modo protegido se denominan

1 byte

0

65535

1 byte

Disco

estado

control

Espacio de direcciones de E/S

Controlador del

disco

selectores, y contienen un apuntador a una estructura de datos en la cual se describe un

segmento de memoria.

Registro EFLAGS: Este registro de 32 bits contiene una serie de banderas (flags) que tienen

diversos usos. Algunas reflejan el estado del procesador y otras controlan su ejecucin.

Existen instrucciones especficas para modificar el valor de EFLAGS.

Registro EIP: Este registro almacena el apuntador a la direccin lineal de la siguiente

instruccin que el procesador debe ejecutar.

Registros de control: El procesador posee cinco (5) registros de control CR0 a CR5. Estos

registros junto con EFLAGS controlan la ejecucin del procesador.

Registros para el control de la memoria: Estos registros apuntan a las estructura de datos

requeridas para el funcionamiento del procesador en modo protegido. Ellos son: GDTR,

IDTR, TR y LDTR.

Registros de depuracin: Estos registros contienen informacin que puede ser usada para

depurar el cdigo que est ejecutando el procesador. Los procesadores IA-32 cuentan con

ocho (8) registros de depuracin, DR0 a DR7.

Registros especficos: Cada variante de procesador IA-32 incluye otros registros, tales

como los registros MMX, los registros de la unidad de punto flotante (FPU) entre otros.

Algunos registros de propsito general pueden ser sub-divididos en registros ms pequeos a los

cuales se puede tener acceso. Esto permite la compatibilidad con programas diseados para

procesadores anteriores. A continuacin se presentan las posibles sub-divisiones de los registros

de propsito general, considerando procesadores de hasta 64 bits:

64 bits 32 bits 16 bits 8 bits 8 bits

RAX EAX AX AH AL

RBX EBX BX BH BL

RCX ECX CX CH CL

RDX EDX DX DH DL

RSI ESI SI No disponible

RDI EDI DI No disponible

RSP ESP SP No disponible

RBP EBP BP No disponible

A nivel de programacin, es posible acceder a cada uno de estos sub-registros de acuerdo con el

modo de operacin. Por ejemplo, para modo de direcciones real, es posible usar los registros de 8

bits y los registros de 16 bits. En modo protegido se puede usar los registros de 8, 16 y 32 bits. Si el

procesador cuenta con registros de 64 bits y se encuentra en el modo de 64 bits, es posible

acceder a los registros de 8, 16, 32 y 64 bits.

La siguiente figura muestra como se encuentran dispuestos los bits de los registros de propsito

general. Los registros EBX, ECX y EDX se encuentran dispuestos de la misma forma que EAX. Los

registros EDI, ESP Y EBP se disponen de la misma forma que ESI.

El formato de almacenamiento de la arquitectura IA-32 es Little-Endian, lo cual significa que los

bits menos significativos de un nmero se almacenan en las posiciones menores de la memoria y

de los registros, y los bits ms significativos se almacenan en posiciones superiores (Ver figura).

Nmero hexadecimal: 7C00

0 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0

Binario

(menos significativo) ms significativo

7 C 0 0

Bit 0 Bit 15

Registro:

Memoria:

(menor posicin)

(mayor posicin)

7C

00

AL AH

0 7 15 31 63

AX

EAX

RAX

Modo real

32 bits

64 bits

Registros EAX, EBX, ECX, EDX

Registros ESI, EDI, ESP, EBP

0 7 15 31

SI

ESI

RSI

No se

pueden

sub-dividir

en 8 bits

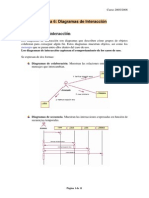

La siguiente figura muestra la disposicin de los bits (flags) dentro de registro EFLAGS. Este

registro almacena el estado y parte del control del procesador. El manual de arquitectura de

sistema de Intel ofrece una descripcin detallada de cada uno de los bits.

Los bits del registro EFLAGS se pueden clasificar en:

Bits de estado: Reflejan el estado actual del procesador. Son bits de estado: OF, SF, ZF, AF

y PF.

Bits de control: Controlan de alguna forma la ejecucin del procesador. Dentro de EFLAGS

se encuentra el bit DF, que permite controlar la direccin de avance en las operaciones

sobre cadenas de caracteres.

Bits del sistema: Los bits ID, VIP, VIF, AC, VM, RF, NT, IOPL, IF y TF son usados por el

procesador para determinar condiciones en su ejecucin, o para habilitar / deshabilitar

determinadas caractersticas. Por ejemplo, estableciendo el bit IF en 1 se habilitan las

interrupciones, mientras un valor de 0 en este bit deshabilita las interrupciones.

Bits reservados: Estos bits marcados con un color diferente se reservan por la arquitectura

IA-32 para futura expansin. Deben permanecer con los valores que se muestran en la

figura (cero o uno). No se deben usar, ya que es posible que en versiones posteriores de

los procesadores IA-32 tengan un significado especfico.

A continuacin se ilustra la disposicin de los bits dentro del registro CR0 (Control Register 0).

0

0 0 0 0 0 0 0 0 0

I

D

V

I

P

V

I

F

A

C

V

M

R

F

0

N

T

IO PL

O

F

D

F

I

F

T

F

S

F

Z

F

0

A

F

0

P

F

1

C

F

7

15

23

0

31

ID Flag

Virtual Interrupt Pending

Virtual Interrupt Flag

Alignment Check

Virtual 8086 Mode

Resume Flag

Nested Task

I/O Privilege Level

Overflow Flag

Direction Flag

Interrupt Flag

Trap Flag

Sign Flag

Zero Flag

Auxiliary Carry Flag

Parity Flag

Carry Flag

EFLAGS

Los bits ms importantes de CR0 desde el punto de vista de programacin son el bit 0 (Protection

Enable PE), y el bit 31 (Paging PG). Estos permiten habilitar el modo protegido y la paginacin,

respectivamente.

No obstante antes de pasar a modo protegido y de habilitar la paginacin se deben configurar

unas estructuras de datos que controlan la ejecucin del procesador. El paso a modo protegido y

las estructuras de datos asociadas se presentarn ms adelante en este documento.

1.2.3 Organizacin de la memoria

La memoria en los procesadores de arquitectura IA-32 se puede organizar y manejar en tres

formas bsicas: Modo segmentado, modo real de direcciones y modo plano. A continuacin se

muestran los detalles de cada modo de organizacin de memoria.

1.2.3.1 Modo segmentado

Este es el modo por defecto de organizacin de memoria. En este modo, la memoria se aprecia

como un grupo de espacios lineales denominados segmentos. Cada segmento puede ser de

diferente tipo, siendo los ms comunes segmentos de cdigo y datos.

Para referenciar un byte dentro de un segmento se debe usar una direccin lgica, que consiste

en un par selector: offset

1

. Con el selector se puede determinar la direccin lineal de inicio del

segmento, y el offset determina el nmero de bytes que se debe desplazar desde el inicio del

segmento. As se obtiene una direccin lineal en el espacio de direcciones de memoria. A

continuacin se presenta una figura que ilustra cmo realiza este proceso.

1

Se usarn la palabras offset y desplazamiento de forma indiscriminada.

0

C

D

N

W

A

M

W

P

N

E

E

T

T

S

E

M

M

P

P

E

7

15 23

P

G

31

Paging

Cache Disable

Non-write through

Alignment Mask

Write Protect

Numeric Error

Extension Type

Task Switched

Emulation

Control Register 0 CR0

16 18 29 30

Monitor Coprocessor

Protection Enable

1.2.3.2 Modo real de direcciones

El modo real de direcciones es el modo inicial de todo procesador IA-32 luego de ser encendido o

reiniciado. Se usa para ofrecer compatibilidad con procesadores de generaciones que abarcan

hasta el propio 8086. En modo real de direcciones el espacio lineal de direcciones se encuentra

dividido en segmentos con un tamao mximo de 64 Kilobytes. Adicionalmente slo es posible

usar los 16 bits menos significativos de los registros para referenciar una direccin lineal.

Las direcciones lgicas en modo real de direcciones tambin estn conformadas por un selector y

un offset. Tanto el selector como el desplazamiento tienen un tamao de 16 bits. Con el fin de

permitir el acceso a un espacio de direcciones lineal mayor, el selector almacena la direccin de

inicio del segmento dividida en 16. Para traducir una direccin lgica a lineal, el procesador toma

el valor del selector y lo multiplica por 16, para hallar la base del segmento. Luego a esta base le

suma el offset. La siguiente figura ilustra el proceso de transformar una direccin lgica a lineal en

el modo real de direcciones.

selector offset

Direccin lgica

Espacio lineal

Segmento en

memoria

:

base

offset

Con el selector se

halla la direccin

lineal de inicio del

segmento (base)

byte

Direccin lineal

2

32

- 1

0

Por las caractersticas especiales del modo real, solo es posible acceder a los primeros 2

20

bytes del

espacio lineal de direcciones. En la prctica esto significa que en modo real slo se puede tener

acceso al primer Megabyte de memoria.

1.2.3.3 Modo plano (Flat)

El modo plano es otro caso especial del modo segmentado. La memoria en este modo se presenta

como un espacio continuo de direcciones (espacio lineal de direcciones). Para procesadores de 32

bits, este espacio abarca desde el byte 0 hasta el byte 2

32

(4GB).

En la prctica, el modo plano se puede activar al definir segmentos que ocupan todo el espacio

lineal (con base = 0 y un tamao igual al mximo tamao disponible).

selector offset

Direccin lgica

Segmento en

memoria

(max. 64 KB)

:

base

offset

El selector almacena

la base del segmento

dividida en 16

byte

Direccin lineal

0

2

20

- 1

Selector (16 bits)

0 0 0 0

El valor del selector se multiplica por

16 (se desplaza 4 bits hacia la

izquierda) para hallar la base del

segmento

Desplazamiento dentro del segmento (16 bits)

0 0 0 0

+

Direccin lineal de 20 bits

base

offset

+

=

Dada una direccin lgica en modo real, el

procesador realiza automticamente la

siguiente operacin:

Dado que en este modo se puede ignorar la base del segmento (al considerar que siempre inicia

en 0), el desplazamiento en una direccin lgica es igual a la direccin lineal (Ver figura).

1.2.3.4 Modo de organizacin de memoria vs. Modo de operacin

El mapeo entre modo de organizacin de memoria y modo de operacin del procesador se da de

resume en la siguiente tabla:

Organizacin de

memoria/

Operacin

Modo real

Modo protegido

de 32 bits

Modo IA32-e

Modo de

compatibilidad

Modo de 64 bits

Modo segmentado NO SI SI NO

Modo real SI SI

2

SI (igual que en

modo protegido de

32 bits)

NO

Modo plano NO

3

SI SI SI

2

En modo protegido de 32 bits es posible acceder al modo real de organizacin de memoria slo en el sub-

modo Virtual 8086

3

Cuando el procesador opera en modo real, se puede activar un modo especial en el cual es posible acceder

a un pseudo-modo llamado modo unreal. En este pseudo-modo la memoria se organiza de forma similar al

modo plano.

selector offset

Direccin lgica

Segmento en

memoria

(Mismo tamao

del espacio

lineal)

:

base

offset

En el modo plano el

selector siempre

referencia un

segmento con base 0

byte

Direccin lineal

0

2

32

- 1

offset

Direccin lineal

=

You might also like

- Hablando Cloud IDG-Microsoft 2012 Capítulo 2Document12 pagesHablando Cloud IDG-Microsoft 2012 Capítulo 2Pepeillo2w013No ratings yet

- Kit de Herramientas Sobre IA y El Estado de Derecho para El Poder JudicialDocument206 pagesKit de Herramientas Sobre IA y El Estado de Derecho para El Poder JudicialGustavo FabianNo ratings yet

- Gestión de La Calidad Según Juran, Deming, Crosby e Ishikawa - GestioPolisDocument1 pageGestión de La Calidad Según Juran, Deming, Crosby e Ishikawa - GestioPolisAbel CabaNo ratings yet

- BioturbosinaDocument7 pagesBioturbosinaGloria Elena PerezNo ratings yet

- Analisis FodaDocument16 pagesAnalisis Fodara-ulNo ratings yet

- Inteligencia ArtificialDocument3 pagesInteligencia ArtificialInteligencia ArtificialNo ratings yet

- El Codigo QR en EducacionDocument5 pagesEl Codigo QR en EducacionReciclaNo ratings yet

- Ecosistema y Economía DigitalDocument425 pagesEcosistema y Economía Digitalronny_naranjo_nNo ratings yet

- Estándares Formales de UsabilidadDocument12 pagesEstándares Formales de UsabilidadCarlos ChasiluisaNo ratings yet

- Diagrama Aplicado A Los Bocetos en El Proceso de Diseño - Un Análisis Desde La Perspectiva de La Psicología de La RepresentaciónDocument19 pagesDiagrama Aplicado A Los Bocetos en El Proceso de Diseño - Un Análisis Desde La Perspectiva de La Psicología de La Representaciónliz ramos yangaliNo ratings yet

- Sensor InfrarrojoDocument6 pagesSensor Infrarrojoleboisdu6580No ratings yet

- Sistemas ComplejosDocument10 pagesSistemas ComplejosArlex Julian López MenesesNo ratings yet

- Auditoria Escuela Superior de Turismo IPNDocument44 pagesAuditoria Escuela Superior de Turismo IPNDripp UriBoyNo ratings yet

- Modelo de Hax y MajlufDocument12 pagesModelo de Hax y MajlufMatias OpazoNo ratings yet

- Gerencia Estrategica PresencialDocument85 pagesGerencia Estrategica PresencialJoan ChourioNo ratings yet

- Resumen XaaSDocument3 pagesResumen XaaSJessica SalgadoNo ratings yet

- Guía de Accesibilidad Universal 2014Document115 pagesGuía de Accesibilidad Universal 2014fergusmcroigNo ratings yet

- Marco Teorico Diseño de La InformaciónDocument6 pagesMarco Teorico Diseño de La InformaciónagustinadebiasiNo ratings yet

- Computo en La Nube-Detonador de CompetitividadDocument61 pagesComputo en La Nube-Detonador de CompetitividadFredd Zun LlnNo ratings yet

- Seguridad y ProteccionDocument9 pagesSeguridad y ProteccionLuis LiendoNo ratings yet

- Los Problemas y Errores Comunes Proyectos CosDocument7 pagesLos Problemas y Errores Comunes Proyectos Cosxxyeso100% (1)

- Ensayo-Inteligencia ArtificialDocument18 pagesEnsayo-Inteligencia ArtificialRafael DíazNo ratings yet

- Medios de Comunicación en La MultimediaDocument1 pageMedios de Comunicación en La Multimediaeldase0% (1)

- Que Es Una Base de Datos PDFDocument8 pagesQue Es Una Base de Datos PDFgeraldine ballesterosNo ratings yet

- Temario Mineria de DatosDocument10 pagesTemario Mineria de DatosDarioNo ratings yet

- ¡Prescindible organizado!: Una agenda docente, afectiva y disidente para el proyecto arquitectónicoFrom Everand¡Prescindible organizado!: Una agenda docente, afectiva y disidente para el proyecto arquitectónicoNo ratings yet

- Manual Mesa de AyudaDocument29 pagesManual Mesa de AyudaPaulo PérezNo ratings yet

- Web Quest Formatos Audio-VideoDocument6 pagesWeb Quest Formatos Audio-VideoVictorBarrero3No ratings yet

- A2 U2 Sistemas OperativosDocument12 pagesA2 U2 Sistemas OperativosThe Dark AngelNo ratings yet

- 07 Prieto Castillo, La Cuestión Del ReferenteDocument7 pages07 Prieto Castillo, La Cuestión Del ReferenteNoel CastilloNo ratings yet

- Ismael Nafria de La Web 2.0 A La Web 3.0Document58 pagesIsmael Nafria de La Web 2.0 A La Web 3.0premine100% (2)

- Ingeniería de Software IIDocument7 pagesIngeniería de Software IIderlypsNo ratings yet

- Configuracion Firewall - Ejercicios AdicionalesDocument11 pagesConfiguracion Firewall - Ejercicios AdicionalespepeNo ratings yet

- Héctor García Molina PDFDocument1 pageHéctor García Molina PDFYuyis CM CMNo ratings yet

- 63723-Texto Del Artículo-4564456564042-2-10-20190507Document16 pages63723-Texto Del Artículo-4564456564042-2-10-20190507Angela BarretoNo ratings yet

- Qué Es Un ProtocoloDocument9 pagesQué Es Un Protocolosamejardila2795No ratings yet

- Ventajas y Desventajas de Las Netbooks y TabletsDocument18 pagesVentajas y Desventajas de Las Netbooks y Tabletsmariotopillo33% (3)

- Analisis Del Funcionamiento de Los Sistemas InformaticosDocument74 pagesAnalisis Del Funcionamiento de Los Sistemas Informaticosc_elenilson100% (1)

- Ingeniería Económica: Herramientas financieras para la toma de decisionesDocument6 pagesIngeniería Económica: Herramientas financieras para la toma de decisionesveymar sanchez oliveraNo ratings yet

- La Situación Actual de La Ingeniería de SoftwareDocument9 pagesLa Situación Actual de La Ingeniería de SoftwareCarlos CardenasNo ratings yet

- Revisión de lenguaje para la ejecución de algoritmos en pseudocódigo y construcción de su compiladorDocument309 pagesRevisión de lenguaje para la ejecución de algoritmos en pseudocódigo y construcción de su compiladorRikardo BenalcazarNo ratings yet

- Contrucción en BélgicaDocument47 pagesContrucción en BélgicaPromoMadridNo ratings yet

- Introducción A La Computación Grid PDFDocument57 pagesIntroducción A La Computación Grid PDFJuan Ignacio Álvarez HernándezNo ratings yet

- Principales Protocolos de AutenticaciónDocument29 pagesPrincipales Protocolos de AutenticacióngaryelingenieroNo ratings yet

- Metodolgias AgilesDocument8 pagesMetodolgias AgilesJert ZeeNo ratings yet

- Office 365 Migration Challenges and Solutions Flyer EsDocument4 pagesOffice 365 Migration Challenges and Solutions Flyer Esyorfan mauricio colmenares padillaNo ratings yet

- Ergonomia MetodologíaDocument18 pagesErgonomia MetodologíaMauricio Díaz CortésNo ratings yet

- Historia IADocument9 pagesHistoria IAJULIANNo ratings yet

- Innovacion Abierta Henry Chesbrough Descargar Libro - Buscar Con Google PDFDocument1 pageInnovacion Abierta Henry Chesbrough Descargar Libro - Buscar Con Google PDFjohn miguelNo ratings yet

- Historia de La Actuaria en Mexico - CONAC2021Document59 pagesHistoria de La Actuaria en Mexico - CONAC2021Fátima Flores OrtegaNo ratings yet

- Estrategia de Los Cuatro Circulos PDFDocument3 pagesEstrategia de Los Cuatro Circulos PDFAlfredo Antonio Yepez RuizNo ratings yet

- 5.-M - P - V-Sistema Contable PDFDocument68 pages5.-M - P - V-Sistema Contable PDFWillian Edar Evangelio AvilaNo ratings yet

- Multimedia, RepositoriosDocument6 pagesMultimedia, RepositoriosJimmy CabreraNo ratings yet

- Sistemas OperativosDocument9 pagesSistemas OperativosTerkiumss100% (1)

- Magic Quadrant For Mobile App Development PlatformsDocument47 pagesMagic Quadrant For Mobile App Development PlatformsjcmoridiazNo ratings yet

- CanvasDocument31 pagesCanvasNada Nada100% (1)

- Qué Es Un IPS e IDSDocument5 pagesQué Es Un IPS e IDSGabriel CaNo ratings yet

- Políticos, técnicos y comunidades: Una visión institucionalista del urbanismo social en MedellínFrom EverandPolíticos, técnicos y comunidades: Una visión institucionalista del urbanismo social en MedellínNo ratings yet

- Ciencia y tecnología para el Hábitat popular 2010: Hábitat. Fortalecimiento del espacio disciplinar en los sistemas de CyTFrom EverandCiencia y tecnología para el Hábitat popular 2010: Hábitat. Fortalecimiento del espacio disciplinar en los sistemas de CyTNo ratings yet

- Instalación de ORACLEDocument8 pagesInstalación de ORACLEIvonne DíazNo ratings yet

- Instalación de ORACLEDocument8 pagesInstalación de ORACLEIvonne DíazNo ratings yet

- Memoria TecnicaDocument13 pagesMemoria TecnicaIvonne DíazNo ratings yet

- Plan de TrabajoDocument11 pagesPlan de TrabajoIvonne DíazNo ratings yet

- Seguridad en La RedDocument38 pagesSeguridad en La RedHarol DíazNo ratings yet

- Admon. de Base de Datos. Unidad 2Document20 pagesAdmon. de Base de Datos. Unidad 2Gyna ValenciaNo ratings yet

- El Sistema de Archivos Ntfs 615 K8u3gjDocument2 pagesEl Sistema de Archivos Ntfs 615 K8u3gjIvonne DíazNo ratings yet

- CUADROCOMPARATIVO Costo LicenciasDocument4 pagesCUADROCOMPARATIVO Costo LicenciasIvonne DíazNo ratings yet

- Plan de TrabajoDocument11 pagesPlan de TrabajoIvonne DíazNo ratings yet

- Todos Los Examenes Ccna3Document59 pagesTodos Los Examenes Ccna3Hebert MolinaNo ratings yet

- Seguridad Pptx1057523461Document38 pagesSeguridad Pptx1057523461Sagermix Djalex GomezNo ratings yet

- DNS y DHCPDocument49 pagesDNS y DHCPIvonne DíazNo ratings yet

- 2 1 Organizacion Del Procesador PDFDocument4 pages2 1 Organizacion Del Procesador PDFIvonne DíazNo ratings yet

- 1.2 Conceptos WANDocument13 pages1.2 Conceptos WANIvonne DíazNo ratings yet

- Cabeceras UDP TCPDocument6 pagesCabeceras UDP TCPangelcaido860% (1)

- Investigacion Pura Y AplicadaDocument6 pagesInvestigacion Pura Y AplicadahipolitocelestiNo ratings yet

- Tabla Comparativa Sobre Los DBMSDocument2 pagesTabla Comparativa Sobre Los DBMSDiego HernandezNo ratings yet

- Leyes de Kirchoff, Analisis de Mallas y NodosDocument24 pagesLeyes de Kirchoff, Analisis de Mallas y NodosAlejandro Castro50% (2)

- C Agua y ReligionesDocument9 pagesC Agua y ReligionesIvonne DíazNo ratings yet

- 145 KilosDocument4 pages145 KilosIvonne DíazNo ratings yet

- Bit A Cora Dear Quite Ctur A PDFDocument29 pagesBit A Cora Dear Quite Ctur A PDFIvonne DíazNo ratings yet

- Características Del Lenguaje Java VENTAJAS Y DESVENTAJASDocument4 pagesCaracterísticas Del Lenguaje Java VENTAJAS Y DESVENTAJASBismarck Jaime100% (4)

- Diagram A de Inter Acci OnDocument11 pagesDiagram A de Inter Acci OnIvonne DíazNo ratings yet

- Leyes de Kirchoff, Analisis de Mallas y NodosDocument24 pagesLeyes de Kirchoff, Analisis de Mallas y NodosAlejandro Castro50% (2)

- Caracteristicas de PHP PDFDocument3 pagesCaracteristicas de PHP PDFDulce Ma Flores RosasNo ratings yet

- Temario Arquitectura de ComputadorasDocument2 pagesTemario Arquitectura de ComputadorasIvonne DíazNo ratings yet

- 2 1 Organizacion Del Procesador PDFDocument4 pages2 1 Organizacion Del Procesador PDFIvonne DíazNo ratings yet

- Cabeceras UDP TCPDocument6 pagesCabeceras UDP TCPangelcaido860% (1)

- NanotecnologiaDocument92 pagesNanotecnologiaMaría Claudia Rosales Contreras100% (1)

- Jtable de JavaDocument27 pagesJtable de JavaMarco Antonio Seclen MioNo ratings yet

- Windows 7Document64 pagesWindows 7DANTENo ratings yet

- Manual Storm User 2.2Document39 pagesManual Storm User 2.2perriliNo ratings yet

- Evolución de La RTPCDocument8 pagesEvolución de La RTPCCamilo SepulvedaNo ratings yet

- Marketing de ExcelenciaDocument2 pagesMarketing de ExcelenciaGismara Alonso Aguilar100% (3)

- Contrato de Locación de ServiciosDocument11 pagesContrato de Locación de ServiciosMáximo Calero100% (1)

- Big DataDocument3 pagesBig DataYouli Albert RondonNo ratings yet

- Photoshop Informaciones BásicasDocument4 pagesPhotoshop Informaciones BásicasDiego Ysmael Brand AriasNo ratings yet

- Tema II Sistemas Socio TecnicosDocument17 pagesTema II Sistemas Socio Tecnicosdowba renterNo ratings yet

- Autómatas de pila y analizadores LR SLRDocument5 pagesAutómatas de pila y analizadores LR SLRsamo123456No ratings yet

- Comercio electrónico: conceptos básicosDocument13 pagesComercio electrónico: conceptos básicosJose AmbrocioNo ratings yet

- Copia de TALLER DE LECTORES 4° 4P 2021Document4 pagesCopia de TALLER DE LECTORES 4° 4P 2021karen LealNo ratings yet

- Bbva Total 2Document14 pagesBbva Total 2Fernando Mori SoteloNo ratings yet

- Evaluación Unidad 3 - Revisión Del IntentoDocument9 pagesEvaluación Unidad 3 - Revisión Del Intentoingrid johanna GaitanNo ratings yet

- Anexo 2 - Guia Margarita NietoDocument12 pagesAnexo 2 - Guia Margarita NietoAzazo29No ratings yet

- Configuracion de Tl280 para Aplicacion Powerseries Neo GoDocument10 pagesConfiguracion de Tl280 para Aplicacion Powerseries Neo GoWilmer3530100% (1)

- Prueba Tecnica - DEVDocument8 pagesPrueba Tecnica - DEVLuis Alberto GpNo ratings yet

- Examen Software EducativoDocument3 pagesExamen Software EducativoISAAC ANTONIO REYES CONTRERASNo ratings yet

- Fastcam SpanishDocument290 pagesFastcam SpanishGerardo Hernández67% (3)

- Tarea 3 Analisis y DiseñoDocument9 pagesTarea 3 Analisis y Diseñoluis maury perez guzmanNo ratings yet

- GPIP 103 BDR - GisDocument33 pagesGPIP 103 BDR - GisJulian Andrés FajardoNo ratings yet

- Ancho de Banda en SquidDocument4 pagesAncho de Banda en SquidLeOnel ViLlacrésNo ratings yet

- Configura servidores AD, DNS, DHCP y webDocument2 pagesConfigura servidores AD, DNS, DHCP y webAnthony AparicioNo ratings yet

- Instalar METAMASK en GOOGLE CHROME o Mozilla FirefoxDocument10 pagesInstalar METAMASK en GOOGLE CHROME o Mozilla FirefoxMauricio ChicaizaNo ratings yet

- TASCOIDocument3 pagesTASCOIPaola Garcia AmaroNo ratings yet

- CONTENIDO 01 REVIT (Autoguardado) 1Document27 pagesCONTENIDO 01 REVIT (Autoguardado) 1Richard EspinoNo ratings yet

- Informe Topografico PaijanDocument32 pagesInforme Topografico PaijanGuevara Sandoval EliNo ratings yet

- 100000I52N BaseDeDatosDocument2 pages100000I52N BaseDeDatosLogan arredondoNo ratings yet

- Cuaderno 1 Ofimática BásicaDocument45 pagesCuaderno 1 Ofimática BásicaPablo J. ChavezNo ratings yet

- BCP - Metodologia Recomendada 1Document62 pagesBCP - Metodologia Recomendada 1Ricardo Marcelo GómezNo ratings yet