Professional Documents

Culture Documents

Electronica de Potencia Nuevo2 Juan Martin

Uploaded by

Juan Martin RomeroCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electronica de Potencia Nuevo2 Juan Martin

Uploaded by

Juan Martin RomeroCopyright:

Available Formats

- Trabajo Integral

I NVERSOR MULTI NI VEL DE TRES ETAPAS

EN CASCADA

Romero Peralta Juan Martin

Ahumada Bruno Ariel

-2014-

UNIVERSIDAD NACIONAL DE TUCUMAN

Facultad de Ciencias Exactas y Tecnologa

Departamento de Electricidad, Electrnica y Computacin

Av. Independencia 1800 (4000) Tucumn Argentina

Tel. +54 381 4364093 int. 7792

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

2

ndice

Resumen. ....................................................................................................................................... 3

I. Introduccin ............................................................................................................................... 4

1.1 Objetivo de la memoria ................................................................................................. 4

1.1.1 Necesidad de la memoria .......................................................................................... 4

1.1.2 Alcance de la memoria .............................................................................................. 4

1.1.3 Organizacin de la memoria ..................................................................................... 4

1.2 Inversores multinivel ..................................................................................................... 5

1.2.1 Topologa de inversores multinivel ........................................................................... 8

II. Inversor Multinivel de tres Etapas en Cascada con Fuente Comn ........................................ 14

2.1 Inversor Multietapa en Cascada Con Fuentes Independientes [2] ............................. 14

2.1.1 Modulacin de Amplitud ......................................................................................... 15

2.2 Inversor Multinivel de tres Etapas en Cascada con Fuente Comn ........................... 16

2.2.1 Modulacin de Amplitud ......................................................................................... 17

III. Diseo y Construccin ................................................................................................. 17

3.1 Especificaciones .......................................................................................................... 17

3.2 Consideraciones preliminares ..................................................................................... 17

3.2.1 Etapas del inversor .................................................................................................. 18

3.3 Bloque de Control ....................................................................................................... 19

3.3.1 Definicin ................................................................................................................ 19

3.3.2 Diseo ...................................................................................................................... 20

3.3.3 Simulaciones ............................................................................................................ 25

3.3.4 Construccin ............................................................................................................ 26

3.3.5 Especificaciones Tcnicas ........................................................................................ 28

3.4 Bloque de Potencia ..................................................................................................... 29

3.4.1 Diseo ...................................................................................................................... 29

3.4.2 Simulaciones ............................................................................................................ 31

3.4.3 Construccin ............................................................................................................ 34

3.4.4 Especificaciones Tcnicas ........................................................................................ 47

IV. Resultados Experimentales .................................................................................................... 47

V. Conclusiones .......................................................................................................................... 47

ANEXO I ................................................................................................................................... 48

ANEXO II .................................................................................................................................. 49

ANEXO III ................................................................................................................................. 50

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

3

Resumen.

A partir del creciente empleo de la energa fotovoltaica, creci el desarrollo en el campo de la

electrnica de potencia de los inversores de tensin.

Los convertidores de cd a ca se conocen como inversores. La funcin de un inversor es

cambiar un voltaje de entrada en cd a un voltaje de salida en ca, con la magnitud y frecuencia

deseada. Tanto el voltaje de salida como la frecuencia pueden ser fijos o variables *1+.

Recordando que, un panel solar produce una tensin continua, para poder aprovecharla es

necesario un inversor de tensin. De esta manera se puede proveer a hogares o industrias la

energa de los sistemas fotovoltaicos. Pero esta aplicacin de inversores no es la nica, por

nombrar otra como ejemplo, estn presentes en fuentes de poder de tensin alterna

conocidas por sus siglas en Ingles como UPS (UninterruptedPowerSystem).

Existen diversas topologas de inversores de tensin, difieren unos de otros segn el modo de

operar para producir una tensin alterna a partir de una continua.

En este trabajo se detallan los procesos realizados durante el diseo y posterior construccin

de un inversor de tensin monofsico de 300[VA] y 220[V].

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

4

I. Introduccin

1.1 Objetivo de la memoria

En el presente trabajo se detalla el proceso de diseo y construccin de un Inversor Multinivel

de Tres Etapas Monofsico, que utiliza transistores de potencia del tipo MOSFET para la

funcin de conmutacin.

1.1.1 Necesidad de la memoria

La memoria nace por una necesidad de documentar el proceso de diseo y construccin del

inversor de tensin. Esta memoria sirve como respaldo terico del trabajo tangible y adems

puede servir como Manual de usuario y referencia para la operacin, mantenimiento y

modificacin del inversor fabricado.

1.1.2 Alcance de la memoria

La documentacin terica que se presenta abarca el diseo y construccin del inversor de

tensin, incluye observaciones al proceso de diseo y de construccin, adems tiene en cuenta

aspectos futuros como ser mejoras propuestas que se pueden implementar al aparato

construido.

1.1.3 Organizacin de la memoria

Captulo I: En este captulo se presenta una introduccin al trabajo realizado, se describe

distintos tipos de inversores de tensin del tipo multinivel y sus ventajas y desventajas.

Captulo II: Se describe el inversor multinivel desarrollado, en la configuracin de tres etapas,

se muestra simulaciones de su operacin y se compara la presencia de armnicas segn la

cantidad de etapas que posea el inversor.

Captulo III: En este captulo se presenta el proceso de diseo y posterior construccin,

empezando por las especificaciones, luego continua lo referente a la etapa de control y por

ltimo la etapa de potencia.

Captulo IV: Se muestran los resultados experimentales obtenidos mediante ensayos al

inversor.

Captulo V: En el ltimo captulo se encuentran las conclusiones y observaciones al trabajo.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

5

1.2 Inversores multinivel

Un inversor multinivel genera una tensin alterna (ca) a partir de diferentes valores o

niveles de tensin continua (cd).

Estos inversores multiniveles, se pueden conectar entre si en serie (si se tienen varias fuentes

de tensin continua de diferentes niveles de tensin) o en paralelo mediante transformadores

(si lo que se tiene es una nica fuente de tensin continua).

Un nico inversor multinivel individual o una etapa se caracteriza por la cantidad de

niveles de tensin alterna que produce en sus bornes de salida (OUTPUT).

Por ejemplo, un inversor de dos niveles, genera dos niveles de tensin en su salida. Esto se

puede observar en la Figura 1.

Figura 1. Inversor de dos niveles de tensin.

La Figura 2, muestra la tensin en bornes de la carga (LOAD) en funcin del tiempo, para una

tensin

y una frecuencia de

Figura 2. Tensin en bornes de LOAD en funcin del tiempo.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

6

Si se analiza un inversor de tres niveles de tensin, como se muestra en la Figura 3, se puede

observar forma de onda de la tensin sobre LOAD durante el transcurso del tiempo, esto est

representado en la Figura 4.

Figura 3. Inversor de tres niveles de tensin.

Figura 4.Forma de onda de la tensin sobre LOAD en funcin del tiempo.

Luego de haber visto las formas bsicas de inversores de dos y tres niveles de tensin se puede

generalizar que: el nmero de niveles de tensin de OUTPUT est dado por la siguiente

expresin.

Dnde:

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

7

Segn lo antes expuesto se puede deducir que: mientras mayor es el nmero de niveles de

tensin que construyen la forma de onda de tensin OUTPUT de un inversor, mayor es el

nmero de fuentes de cd y mayor la cantidad de elementos empleados para la construccin.

Hasta el momento, lo que se obtuvo como tensin OUTPUT ms que una seal alterna en el

tiempo (semiciclo (+) y semiciclo (-)) es una forma de onda de tensin del tipo pulsante en el

tiempo. Si al circuito de la Figura 1 se lo modifica segn se observa a continuacin:

Figura 5. Circuito conmutador capaz de generar una seal alterna en el tiempo.

Se puede obtener sobre los bornes de LOAD una tensin alterna en el tiempo. (Este es el

principio de funcionamiento de un puente inversor o tambin conocido como puente H). En

la Figura 6 se observa la forma de onda de la tensin sobre LOAD en funcin del tiempo y

segn la conmutacin de las llaves

.

Figura 6. Tensin OUTPUT en funcin del tiempo y segn la conmutacin de los interruptores.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

8

La secuencia lgica que siguen las llaves

para producir una tensin como muestra la

Figura 6 se muestra a continuacin en la Tabla 1:

0 1

1 0

Tabla 1. Secuencia lgica para las llaves

.

Es un hecho que a medida que se aumenta el nmero de niveles de tensin para construir la

seal alterna, el contenido armnico en la tensin de OUTPUT disminuye, esto se debe a que la

seal fabricada se aproxima cada vez ms a una onda de tensin senoidal. Y es esto lo que se

desea en la prctica: aumentar el nmero de niveles y as disminuir la influencia de las

armnicas. Este aumento de niveles, trae como consecuencia mayor cantidad de componentes

empleados para la fabricacin del inversor, como as tambin mayor complejidad en la

programacin del bloque lgico que gobierna el cierre o apertura (ON/OFF) de los MOSFET

empleados como llaves.

A continuacin se hace una breve referencia de las topologas ms comunes en inversores

multinivel.

1.2.1 Topologa de inversores multinivel

Inversor Acoplado por Diodo (Diode-ClampedInverter)[2]

Este tipo de inversor se caracteriza por dividir la tensin

en una cierta cantidad de niveles

de tensin por medio de capacitores conectados en serie. La cantidad de diferentes niveles de

tensin caracteriza al inversor. En la Figura 7 se muestra un inversor de tres niveles, obtenidos

con los condensadores

conectados en serie.

Figura 7. Esquema de un inversor acoplado por diodos de tres niveles.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

9

El punto medio entre los condensadores se puede definir como punto neutro. La tensin

de OUTPUT

se caracteriza por tener tres niveles o estados de tensin:

con

respecto al punto neutro. En la Tabla 2se muestra la secuencia de encendido de los

semiconductores que se emplean para generar los diferentes voltajes se OUTPUT para el

inversor de la Figura 7.

Van

1 1 0 0

0 0 1 1 0

0 0 1 1

Tabla 2. Secuencia de encendido para el inversor de la Figura 7.

En este tipo de inversor, los diodos

son componentes clave que no se encuentran en

los inversores de dos niveles comunes. Estos diodos acoplan la tensin de conmutacin para

dividir el nivel de voltaje de

Cuando

estn simultneamente cerrados, el voltaje

entra es de

. En este caso,

balancea el voltaje entre

haciendo que

bloquee el voltaje en

y que

bloquee el voltaje en

.

Inversor Acoplado por Capacitor (Capacitor-ClampedInverter)[2]

En la Figura 8, se muestra el diagrama esquemtico de un inversor acoplado por condensador.

El inversor de la Figura 8 corresponde a uno de tres niveles, el cual genera entre los terminales

los siguientes valores de tensin:

.

Figura 8. Esquema de inversor acoplado por condensador de tres niveles.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

10

En la Tabla 3 se puede ver las combinaciones de los valores lgicos que controlan a los

semiconductores de potencia que deben conducir para generar lo diferentes niveles de

tensin.

Van

1 1 0 0

0 1 0 1 0

0 0 1 1

Tabla 3. Secuencia de encendido para el inversor de la Figura 8.

Inversor Multietapa con Puentes H e Inversores en Cascada [2]

Se puede casi duplicar el nmero de niveles de las topologas anteriores sin hacer crecer el

nmero de fuentes de tensin continua, utilizando la estrategia de los Puentes H. Estos

puentes se construyen utilizando dos inversores multinivel idnticos, de alguno de los tipos

mostrados en la Figura 1 o Figura 3. Una configuracin generalizada de un puente H como el

mencionado se ilustra en la Figura 9.

Figura 9. Puente H generalizado.

Ahora para este tipo de configuracin, los niveles de tensin continua que forman la onda de

tensin de OUTPUT estn dados por la expresin:

Donde son lo mismo que se definio para la ecuacin .

El puente H ms elemental es aquel formado por ramas de dos niveles de tensin cada una,

como el mostrado en la Figura 10. Puede observarse que este puente genera tres niveles con

solo una fuente de tensin continua.

Figura 10. Puente H en su configuracin ms elemental.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

11

El puente H de la Figura 10 genera tres niveles de tensin de OUTPUT

diferentes:

conectando la tensin de entrada al de salida con diferentes combinaciones de

los cuatro interruptores (semiconductores de potencia)

. Para obtener

, los

semiconductores

se ponen en conduccin esto es un valor lgico igual a 1 (ON),

mientras que

estn en un estado de no conduccin (OFF) lo que representa a un valor

lgico igual a 0. Encendiendo los semiconductores

y apagando

, se obtiene la

tensin

. Con las combinaciones

en estado ON se obtiene un potencial

de 0[V] a la salida del inversor. Cualquier otra combinacin no est permitida ya que provocara

un cortocircuito de la fuente de cd. La lgica que maneja los interruptores de este puente H

est dada en la Tabla 4.

Van

1 0 0 1

0 0 0 1 1

0 1 1 0

Tabla 4. Secuencia de encendido de los transistores de potencia del puente H de la Figura 10.

Estos puentes H pueden conectarse en cascada (serie o paralelo) y dependiendo el nmero de

puentes (Etapas) que se conecten, se podr obtener un nmero diferente de niveles de

tensin.

La relacin que existe entre el nmero de niveles de tensin y etapas se ver ms adelante.

En la Figura 11 se puede ver el diagrama de conexin para un Inversor en Cascada Simtrico de

dos etapas. Este inversor puede generar cinco niveles de tensin, dos en el semiciclo positivo,

dos en el negativo y el valor de 0[V].

Figura 11. Inversor en Cascada Simtrico de dos Etapas.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

12

En la siguiente figura: Figura 12 se muestra el diagrama de un Inversor en Cascada Asimtrico

de dos Etapas.

Al igual que el inversor de la Figura 11, este puede generar dos niveles de tensin para el

semiciclo positivo, dos para el negativo y el valor de 0[V], pero a diferencia del Inversor en

Cascada Simtrico los niveles de tensin que conforman la tensin de OUTPUT son desiguales.

Figura 12. Inversor en Cascada Asimtrico de dos Etapas.

La ventaja que ofrece el circuito de la Figura 12 respecto al Inversor Simtrico de dos Etapas es

que: si se varia la programacin de la lgica que gobierna a los transistores de potencia, se

puede obtener hasta siete niveles de tensin para formar la tensin de OUTPUT, siendo tres

niveles para el semiciclo positivo, tres para el negativo y el valor de 0[V].

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

13

Inversor Multietapa en Cascada con Fuente Comn [2]

En la Figura 13 se puede observar el circuito correspondiente a un Inversor en Cascada de dos

Etapas con Fuente Comn. Como puede observarse, a diferencia del inversor con fuentes

independientes, ambos puentes estn alimentados desde la misma fuente de tensin

continua, y en este caso la amplitud de la tensin de OUTPUT se la obtiene mediante

transformadores.

La forma de onda de la tensin alterna conseguida con esta topologa corresponde a la del

inversor en cascada con fuentes independientes, y simtrico (Ver Figura 12)y por lo tanto es

capaz de generar cinco niveles de tensin. La ventaja de esta configuracin frente a la que no

utiliza transformadores, es que a partir de una sola fuente de tensin continua se puede

alimentar todos los puentes del inversor.

Utilizando transformadores de distinta relacin de transformacin se puede construir un

Inversor Asimtrico de Fuente Comn como el que se ilustra en la Figura 14.

Figura 14. Inversor en Cascada Asimtrico de dos Etapas con Fuente Comn.

Figura 13. Inversor en Cascada Simtrico de dos Etapas con Fuente Comn.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

14

En el prximo captulo se desarrolla este tipo de inversor, o sea el Inversor en Cascada

Asimtrico de tres Etapas con Fuente Comn, que es el que se desarroll y construy.

II. Inversor Multinivel de tres Etapas en Cascada con Fuente Comn

El Inversor en Cascada con Fuente Comn corresponde a una particularizacin del Inversor en

Cascada con Fuentes Independientes, por ello que a continuacin se desarrolla de manera

resumida el Inversor con fuentes Independientes.

2.1 Inversor Multietapa en Cascada Con Fuentes Independientes [2]

En la Figura 11se mostr el mdulo bsico utilizando para la implementacin del Inversor

Multietapa, cada etapa del inversor est constituido por un mdulo de puente H que solo

puede entregar tres niveles de tensin:

combinando etapas se eleva el nmero

de niveles de tensin que forman la forma de onda de tensin de OUTPUT.

Utilizar diferentes niveles de tensin en las fuentes que alimentan cada etapa del inversor

mejora la calidad de la forma de onda de la tensin de OUTPUT. Adems, si los niveles de

tensin de las diferentes etapas del inversor son las que se calculan con la expresin siguiente:

Dnde:

Los puentes H utilizados pueden producir tres niveles de tensin se tiene que:

Reemplazando en se obtiene:

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

15

Segn las tensiones de fuentes independientes que alimentan las etapas estn escalonada

en potencias de como se puede observar en la Figura 15.

Figura 15. Inversor de tres Etapas en Cascada con Fuentes Independientes.

2.1.1 Modulacin de Amplitud

Se vio anteriormente que los niveles de tensin que forman la onda de tensin de OUTPUT

estn dados segn la expresin:

Donde se definieron en respectivamente. Esto se traduce en que: al aumentar

el nmero de etapas la tensin formada tiene ms escalones y se aproxima con menor error a

una sinusoide. En el presente proyecto se utilizaron 3 etapas por lo que se tiene segn :

27 niveles de tensin, se emplean 13 para formar el semiciclo positivo, 13 para el negativo y 1

para el nivel de 0[V].

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

16

En la Figura 16 se puede observar la forma de onda de la tensin de OUTPUT para el caso en

que se emplean 3 etapas de puentes H.

Figura 16. Tensin modulada en amplitud.

2.2 Inversor Multinivel de tres Etapas en Cascada con Fuente Comn

Empleando el mismo circuito de puente H que ilustra la Figura 10 conectndolos a una fuente

comn de tensin continua y acoplados entre s mediante transformadores se obtiene el

Inversor de tres Etapas en Cascada con Fuente Comn como se muestra en la Figura 17.

Figura 17. Inversor de tres Etapas en Cascada con Fuente Comn.

Se puede observar que las relaciones de transformacin en los transformadores, tambin

obedecen a potencias de por lo deducido en la expresin .

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

17

2.2.1 Modulacin de Amplitud

En este tipo de inversor, la modulacin de amplitud de tensin se logra ya no con distintos

valores de

(como en inversores con fuentes independientes) sino, con los transformadores

ubicados en las salidas de los puentes H, estos transformadores, como ya se explic tienen

distintas relaciones de transformacin.

III. Diseo y Construccin

3.1 Especificaciones

Se desea disear y construir un Inversor Multinivel de tres Etapas en Cascada con Fuente

Comn, de potencia nominal de y una tensin OUTPUT eficaz de . En la

siguiente figura, se puede observar mediante un diagrama de bloque la constitucin del

inversor, luego en el desarrollo de la memoria se estudiara puntualmente cada bloque que lo

constituye.

Figura 18. Diagrama de bloques de un inversor multinivel.

A continuacin se abordara el diseo y construccin del inversor especificado anteriormente.

3.2 Consideraciones preliminares

Estas consideraciones son necesarias tanto para el diseo de la etapa de control

como para el diseo de la etapa de potencia. Esto es un una profundizacin a la

especificacin del valor de tensin que debe entregar el inversor en sus bornes de

salida.

Una de las especificaciones que condiciona el diseo y construccin del inversor es la tensin

en bornes de salida, esta tensin es de valor eficaz. Se alimentara a cada puente H con

un valor de de cd, este hecho obedece a que con un arreglo de 4 bateras de cd de

en serie, se consigue el valor de . Se piensa en bateras del tipo GEL ya que se

desea que el inversor sea un aparato portable.

Circuito

De

Control

Circuito

De

Potencia

Proteccin

Consumo

Alimentacin de CC

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

18

Se acoplaran las tres etapas del inversor mediante los secundarios de transformadores, las

relacione de los transformadores son tales que al conectarlos (sus secundarios) de manera

aditiva se obtenga una tensin de aproximadamente de pico, valor correspondiente a

la tensin de pico de una tensin alterna de eficaces.

3.2.1 Etapas del inversor

A continuacin se definir con nombres a las etapas del inversor y se determinara la tensin

en bornes del secundario del transformador que acompaa a cada puente H.

Etapa Auxiliar 2

Esta etapa solo aporta un de potencia a la potencia total que puede entregar el inversor a

una determinada carga. Esto se debe al porcentaje de tensin que representa su secundario

con respecto a la tensin total obtenida por sumar el aporte de los secundarios de las tres

etapas. El valor de tensin del secundario del transformador de la etapa Auxiliar 2 est dado

segn la expresin siguiente:

Dnde:

Reemplazando en se tiene:

Etapa Auxiliar 1

Esta etapa aporta un de potencia respecto a la potencia total que puede entregar el

inversor. El valor de tensin (

) de esta etapa esta dado segn la expresin siguiente:

Reemplazando en se tiene:

Etapa Principal

Esta es la etapa ms exigida del inversor respecto a la potencia, esta entrega el de la

potencia total que tiene el inversor. El valor de la tensin en bornes del secundario del

transformador de esta etapa est determinado segn:

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

19

Reemplazando en se tiene:

El factor que aparece en obedece a lo visto anteriormente en 2.1.

Se deduce de lo anterior que si se suma las tensiones que aportan cada etapa, se obtiene la

tensin total en bornes del inversor: tensin de pico de una onda senoidal de

eficaces.

Luego de haber hecho estas consideraciones se puede avanzar en el diseo del inversor, se

empezara por el diseo del bloque lgico.

3.3 Bloque de Control

El estudio de la etapa de control est dividida en: la definicin y diseo de la misma, con sus

simulaciones correspondientes, y posterior a esto la construccin de la etapa de control.

3.3.1 Definicin

El circuito de control es el encargado de generar las seales lgicas para el encendido o

apagado de los transistores de potencia presentes en los puentes H. El block de control

adems de establecer el orden de encendido y apagado de los transistores debe fijar el

tiempo de duracin de cada estado (ON/OFF). Segn la expresin los niveles de tensin

que forman la onda de tensin de OUTPUT esta en relacin de potencias de 3 segn la

cantidad de etapas empleadas. En el presente proyecto el inversor consta de 3 etapas por lo

que se tiene un total de 27 niveles. El circuito de control es el encargado de manejar los

transistores y sus secuencias de encendido o apagado para obtener estos 27 niveles.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

20

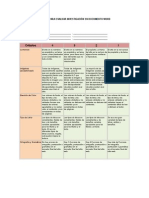

Los transistores de los puentes H funcionan segn las secuencias indicadas en la Tabla 5.

Nivel

Etapa 3 o Principal Etapa 2 o Auxiliar 1 Etapas 1 o Auxiliar 2

Q9 Q10 Q11 Q12 Q5 Q6 Q7 Q8 Q1 Q2 Q3 Q4

Niveles de tensin positivos (Semiciclo +)

0 0 0 1 1 0 0 1 1 0 0 1 1

1 0 0 1 1 0 0 1 1 1 0 0 1

2 0 0 1 1 1 0 0 1 0 1 1 0

3 0 0 1 1 1 0 0 1 0 0 1 1

4 0 0 1 1 1 0 0 1 1 0 0 1

5 1 0 0 1 0 1 1 0 0 1 1 0

6 1 0 0 1 0 1 1 0 0 0 1 1

7 1 0 0 1 0 1 1 0 1 0 0 1

8 1 0 0 1 1 1 0 0 0 1 1 0

9 1 0 0 1 1 1 0 0 0 0 1 1

10 1 0 0 1 1 1 0 0 1 0 0 1

11 1 0 0 1 1 0 0 1 0 1 1 0

12 1 0 0 1 1 0 0 1 0 0 1 1

13 1 0 0 1 1 0 0 1 1 0 0 1

Niveles de tensin negativos (Semiciclo -)

-1 0 0 1 1 0 0 1 1 0 1 1 0

-2 0 0 1 1 0 1 0 0 1 0 0 1

-3 0 0 1 1 0 1 0 0 0 0 1 1

-4 0 0 1 1 0 1 1 0 0 1 1 0

-5 0 1 1 0 1 0 0 1 1 0 0 1

-6 0 1 1 0 1 0 0 1 0 0 1 1

-7 0 1 1 0 1 0 0 1 0 1 1 0

-8 0 1 1 0 0 0 1 1 1 0 0 1

-9 0 1 1 0 0 0 1 1 0 0 1 1

-10 0 1 1 0 0 0 1 1 0 1 1 0

-11 0 1 1 0 0 1 1 0 1 0 0 1

-12 0 1 1 0 0 1 1 0 0 0 1 1

-13 0 1 1 0 0 1 1 0 0 1 1 0

Tabla 5. Tabla de verdad que describe la lgica de los transistores de los puentes H.

La Tabla 5muestra el nivel de tensin (de los 27 niveles posibles) generado y que transistores

deben estar encendidos o apagados para obtenerlo.

3.3.2 Diseo

El control se implementa mediante un PIC. Los PIC son una familia de microcontroladores tipo

RISC (del ingls ReducedInstructionSet Computer, en espaol Computador con Conjunto de

Instrucciones Reducidas) fabricados por Microchip Technology Inc. y derivados del PIC1650,

originalmente desarrollado por la divisin de microelectrnica de General Instrument. [3] Para

la referencia poner http://es.wikipedia.org/wiki/Microcontrolador_PIC

El PIC utilizado es el PIC16F873A, a este dispositivo se le graba la Tabla 5 para comandar a

los transistores de cada puente H. este PIC tiene 28 pines de conexin, de los cuales 16 son del

tipo INPUT/OTPUT para seales, puertos A, B y C, o sea este dispositivo puede manejar hasta

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

21

16 bits de informacin. Para este proyecto solo se necesitan 12 bits. (Ya que son 12 los

transistores a manejar). En la Figura 19 se ilustra el PIC empleado y la designacin de cada pin.

Figura 19. PIC 16F873A de Microchip Technology Inc. Apariencia fsica y designacin de sus pines.

En la Tabla 6 podemos observar la distribucin de pines del puerto B y C utilizados. Por donde

saldrn las seales de control que se estableci en la Tabla 5.

PUERTO C PUERT B

ETAPA PRINCIPAL ETAPA AUXILIAR 1 ETAPA AUXILIAR 2

C0 C1 C2 C3 C7 C6 C5 C4 B7 B6 B5 B4

Q9 Q10 Q11 Q12 Q5 Q6 Q7 Q8 Q1 Q2 Q3 Q4

Al realizar la programacin del PIC hay que tener en cuenta:

Durante el encendido y apagado de los transistores: el tiempo de encendido

y el tiempo de

apagado

de los semiconductores. Estos tiempos, de encendido y apagado generalmente

difieren siendo el tiempo de apagado algo mayor que el de encendido, se deben tener en

cuenta al momento de realizar la programacin. Debido a que si transistores de igual rama del

puente estn encendidos en un mismo instante se puede generar un cortocircuito de la fuente

de tensin

. Para solucionar esto, en la programacin se agreg un tiempo de retardo en la

transicin -de una rama del puente H con respecto a la otra- de aproximadamente unos .

Otro aspecto a tener en cuenta es el hecho de emplear 12 bits del PIC para comandar 12

transistores. Se emplearon dos puertos del PIC, puertos B y C, cada uno de 8 bits, para manejar

los 12 bits que necesitan en conjunto las tres etapas del inversor. Pero la conmutacin de un

puerto a otro (las instrucciones de mando del Pic) durante el funcionamiento tiene cierto

retardo. Para solucionar se coloca en el circuito el cristal de , reduciendo los tiempos

de 2 a para cada instruccin.

Tabla 6. Distribucin de pines del Puerto B y Puerto C

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

22

A continuacin, en la Figura 20 se observa el diagrama del PIC y su conexin con el cristal.

Figura 20. Conexin de los pines del PIC al cristal de 20[MHz].

Se recomienda siempre que exista una separacin galvnica entre circuitos de potencia y

circuitos de control, esto evita interferencias del tipo de radiofrecuencia a lo que son sensibles

los dispositivos como los PIC y adems eliminar cualquier posibilidad de que tensiones

peligrosas se presenten en componentes electrnicos no diseados para soportarlas.

Para lograr esta separacin galvnica en este proyecto se recurri al empleo de acopladores

pticos. Los acopladores pticos combinan un diodo emisor infrarrojo (ILED) y un

fototransistor de silicio. La seal de entrada se aplica al ILED y la salida se forma del

fototransistor. [1]

En la Figura 21, se ve el esquema interno y circuito de conexin del opto acoplador 6N137de

la firma Fairchild Semiconductor, empleado en este proyecto.

Figura 21. Opto acoplador 6N137.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

23

Funcionamiento:

El microcontrolador enva la seal a la entrada del optoacoplador (seal con valor lgico igual a

1), esta seal se traduce en un pulso infrarrojo mediante un ILED es recibido por un dispositivo

fotosensible, que entrega un valor de tensin. Este nivel de tensin excita una de las entradas

de una compuerta lgica (esta compuerta posee dos entradas), la segunda entrada de la

compuerta se conecta mediante un pin Enable a un valor lgico de tensin 0 o 1 segn

corresponda. Las operaciones del optoacoplador se puede observar en la tabla de verdad

siguiente:

Entrada Habilitador(Enable) Salida

H H L

L H H

H L H

L L H

H NC L

L NC H

A la salida de los opto acopladores es necesario el empleo de compuertas inversoras, ya que la

seal que entra al opto acoplador en su salida se la tiene negada. Se emple las compuertas

54LS14 de la firma National Semiconductor. En la Figura 22 se ilustra el integrado de la

compuerta inversora.

Figura 22. Compuerta inversora 54LS14.

Tabla 7.Tabla de Verdad del OPTO 6N137

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

24

A continuacin se puede observar en la Figura 23 el circuito completo del bloque de control.

Figura 23. Bloque de control: elementos y conexionado.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

25

3.3.3 Simulaciones

A continuacin se simulara el funcionamiento del inversor de tres etapas segn la tabla de

verdad mostrada en Tabla 5. Las simulaciones son necesarias en esta etapa de diseo, ya que

permiten verificar el correcto funcionamiento y detectar problemas y as evitar prdidas

econmicas posteriores.

La simulacin se realiz en el programa PROTEUS 8 - PROFESSIONAL, que permite simular el

PIC 16F873a. Adems de la conexin de los elementos externos para el funcionamiento del

PIC, se necesita el programa que ejecutara (La programacin se encuentra en el ANEXO I).

Figura 24. Simulacin del micro controlador en el software PROTEUS 8

En la Figura 25 se puede visualizar las seales correspondientes a cada uno de los puentes.

Figura 25. Seales de control del PIC.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

26

En la Figura26 se observa el retardo entre el encendido y apagado de transistores de una

misma rama explicados con anterioridad.

Figura 26. Retardo impuesto en la seal de control.

3.3.4 Construccin

A partir del diagrama elctrico del bloque de control, y mediante el software PCB WIZARD se

disea la plaqueta del circuito o PCB (del ingls PrintedCircuitBoard). El bloque de control

estar conformado por dos plaquetas. Una correspondiente al microcontrolador solamente y

la segunda a la conexin de los optoacopladores. En la Figura 27 se puede observar el aspecto

del bloque de control Plaqueta PIC, esta imagen es creada por el software.

Figura 27. Circuito impreso del PIC simulado mediante software.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

27

En la Figura 28 se observa una visualizacin del aspecto del bloque de control Plaqueta

OPTO.

Figura 28. PCB del bloque de control Plaqueta OPTO diseado mediante el software PCB WIZAR.

El circuito de control construido se ilustra en la siguiente figura:

Q1

Q2

Q1

Q2

Q3

Q4

Q3

Q4

Q5

Q6

Q5

Q6

Q7

Q8

Q7

Q8

Q9

Q10

Q10

Q11

Q10

Q11

Q9

Q10

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

28

El circuito de control construido se ilustra en las siguientes figuras. El tamao final de la

plaqueta del PIC es de 10 cm de ancho por 10 cm de alto y la plaqueta de los optoacopladores

es de 10 cm de ancho por 20 cm de alto.

En la Figura 29 se puede observar cuales son los conectores que entregan la seal para cada

puente como tambin los conectores para la alimentacin.

3.3.5 Especificaciones Tcnicas

Alimentacin:

PIC - 16F873A = 5 [V] - Continua

Optoacoplador - 6N137 = 5[V] - Continua

Integrado - 74LS14 = 5[V] - Continua

Figura 29. Plaqueta de Control (PIC y Optoacopladores)

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

29

Salida:

Placa del PIC:

RB7-RB6-RB5-RB4 = 5 [V] Cuadrada Frecuencia: 1 KHz

RC7-RC6-RC5-RC4 = 5 [V] Cuadrada Frecuencia: 333 Hz

RC3-RC2-RC1-RC0 = 5 [V] Cuadrada Frecuencia: 50 Hz

Placa del Opto:

Q1-Q2-Q3-Q4 = 5[V] Cuadrada Frecuencia: 1KHz

Q5-Q6-Q7-Q8 = 5[V] Cuadrada Frecuencia: 333 Hz

Q9-Q10-Q11-Q12 = 5[V] Cuadrada Frecuencia: 50 Hz

3.4 Bloque de Potencia

El bloque de potencia est formado por los puentes H y por transformadores. Cada puente H

estar conectado al primario de su transformador correspondiente, luego los secundarios de

los transformadores estarn conectados en serie aditiva, y entre los dos bornes libres que

queden se desarrollara la tensin OUTPUT que se especific anteriormente.

. Se realizara el anlisis de la presencia de armnicos y luego de esto se simulara la respuesta

del inversor a distintas condiciones de carga. Esto corresponde a la etapa de potencia.

3.4.1 Diseo

Para poder operar los transistores de potencia como interruptores, debe aplicarse un voltaje

apropiado de compuerta o una corriente apropiada de base, y excitar los transistores al modo

saturacin para un voltaje activo bajo. El voltaje de control deber aplicarse entre las

terminales de compuerta y fuente o entre las terminales de base y emisor. A continuacin, se

observa en la Figura 30 un arreglo en puente H de cuatro MOSFET y un circuito generador

lgico (El desarrollado en 3.3), que como se dijo, es el encargado de definir las secuencias y

tiempos de encendido y apagado de los semiconductores de potencia. El circuito de la figura

genera cuatro pulsos desplazados en el tiempo para llevar a cabo la secuencia lgica requerida

para la conversin de potencia de cd a ca. Los cuatro pulsos, tiene la misma referencia ,

esta referencia se puede conectar a su vez con la referencia de la alimentacin

en cd.

Figura 30. Puente inversor y circuito lgico.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

30

La terminal

, que tiene una tensin

con respecto a la terminal , no se puede conectar

directamente a la terminal de compuerta

. La seal

deber aplicarse entre la terminal de

compuerta

y la terminal de fuente

del MOSFET

, se necesitara aislar e interconectar los

circuitos entre la lgica y los transistores de potencia. Sin embargo, los transistores

pueden excitarse directamente sin circuitos de aislamiento o interfaz, si las seales lgicas son

compatibles con los requisitos de excitacin de compuerta de los transistores. (En transistores

de potencia, generalmente la seal de tensin necesaria para la excitacin es de entre y

). La importancia de excitar un transistor entre la compuerta y la fuente, en lugar de

aplicar una tensin de compuerta entre la compuerta y tierra comn, se muestra en la Figura

31.

Figura 31. Excitacin compuerta-fuente en un MOSFET

La tensin efectiva compuerta-fuente en

es:

En donde

. El valor de

se reduce conforme se activa el transistor y llegando al

valor de rgimen permanente, requerido para equilibrar la carga. El valor efectivo

no es

predecible siendo una disposicin como sta no adecuada.

En la prctica, para resolver el problema de la referencia de las seales lgica, se emplea un

dispositivo electrnico llamado Driver este Driver ser un elemento intermediario entre el

circuito lgico y el circuito de potencia. Es el encargado de transmitir la orden de conmutacin

proveniente del block de control y proporcionara la tierra o referencia necesaria para el

funcionamiento de los MOSFET superiores del puente H.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

31

3.4.2 Simulaciones

Antes de realizar la comprar de elementos y luego la construccin del Puente inversor, se lo

simulo en el software PSim para poder determinar los valores a los que se encuentra

trabajando los MOSFET, poder visualizar la seal de salida y verificar que la lgica de control

sea la correcta (se verifica observando que se generen la cantidad correcta de escalones en la

seal de salida).

En la Figura 32 se puede visualizar circuito de la simulacin:

EL sector de control est conformado por el bloque lookuptable, que tiene como funcin

tomar el valor de entrada proveniente de la fuente V1 y entregar un valor de salida (1 o 0), que

se utiliza para el control de los MOSFET de cada puente. Cada uno de esto est conformado

por dos bloques (lookuptable) y cada uno tiene una tabla.

Figura 32. Simulacin del Inversor de 4 etapas

inver

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

32

1A 2A 1B 2B 1C 2C

-13,0

-12,0

-11,1

-10,0

-9,0

-8,1

-7,0

-6,0

-5,1

-4,0

-3,0

-2,1

-1,0

0,0

1,1

2,0

3,0

4,1

5,0

6,0

7,1

8,0

9,0

10,1

11,0

12,0

13,1

-13,1

-12,0

-11,0

-10,1

-9,0

-8,0

-7,1

-6,0

-5,0

-4,1

-3,0

-2,0

-1,1

0,0

1,0

2,1

3,0

4,0

5,1

6,0

7,0

8,1

9,0

10,0

11,1

12,0

13,0

-13,0

-12,0

-11,0

-10,0

-9,0

-8,0

-7,1

-6,1

-5,1

-4,0

-3,0

-2,0

-1,0

0,0

1,0

2,1

3,1

4,1

5,0

6,0

7,0

8,0

9,0

10,0

11,1

12,1

13,1

-13,1

-12,1

-11,1

-10,0

-9,0

-8,0

-7,0

-6,0

-5,0

-4,1

-3,1

-2,1

-1,0

0,0

1,0

2,0

3,0

4,0

5,1

6,1

7,1

8,0

9,0

10,0

11,0

12,0

13,0

-13,0

-12,0

-11,0

-10,0

-9,0

-8,0

-7,0

-6,0

-5,0

-4,0

-3,0

-2,0

-1,0

0,0

1,0

2,0

3,0

4,0

5,1

6,1

7,1

8,1

9,1

10,1

11,1

12,1

13,1

-13,1

-12,1

-11,1

-10,1

-9,1

-8,1

-7,1

-6,1

-5,1

-4,0

-3,0

-2,0

-1,0

0,0

1,0

2,0

3,0

4,0

5,0

6,0

7,0

8,0

9,0

10,0

11,0

12,0

13,0

En las siguientes figuras se visualiza la seal a la salida de los puentes por el lado del

secundario del transformador es:

Figura 33.Voltajes Secundarios de cada uno de los transformadores de cada etapa

Tabla 8.Contenido de los archivos .tbl de cada bloque lookuptable

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

33

A los voltajes secundarios tambin se les suele llamar voltaje modulados, que al sumarse

generaran la seal sinusoidal a la salida del inversor. Como se ve en la siguiente figura:

La onda obtenida, es muy parecida a una seal ideal. Esta comparacin la podemos apreciar

mejor en la siguiente figura.

Figura 34.Suma de voltajes secundario

Figura 35.Comparacin de la seal OUTPUT vs Senoidal

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

34

3.4.3 Construccin

En este proyecto se emplea el Driver IR2113 de International Rectifier, en la Figura 36 se

observa el Driver y su esquema de conexin.

Figura 36. Conexin del driver IR2113 a los MOSFET y elementos necesarios para su funcionamiento.

En la Figura 37 se observa el conexionado interno del driver

Figura 37. Conexionado Interno IR2113

Este integrado es capaz de manejar dos compuertas de manera independiente. Por lo tanto

para cada etapa de potencia se emplearan dos de estos integrados.

Una caracterstica muy importante a tener en cuenta en los drivers, es la tensin que se aplica

en el pin

. Cuando el transistor

de la Figura 36 esta encendido (ON) y el transistor

esta

apagado (OFF), en el terminal

se tiene respecto a la masa la tensin que se aplica al

puente

. Por ejemplo si en el datasheet indica una

, hace referencia a la

tensin que soportan los terminales del circuito integrado que se conectan al punto

intermedio del puente, y por lo tanto la mxima tensin de alimentacin del puente si se hace

uso de este driver, en este proyecto

.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

35

Funcionamiento del driver

La tensin

alimenta al bloque del driver que enciende el MOSFET de la parte

superior del puente. Esta tensin

, es una tensin flotante, no est referenciada a la

masa y se expresa en relacin a la tensin

. Cuando se enciende el MOSFET de la parte

superior

(Ver Figura 36) y el MOSFET inferior est en estado OFF, la tensin en la terminal

con respecto a la masa tomar un valor algo superior a

, tericamente

, donde

es la tensin entre compuerta y emisor del MOSFET

en estado de conduccin.

Existen mtodos para lograr la tensin

, el mtodo empleado en este proyecto

es el mtodo Bootstrap el mismo se muestra en la Figura 36. La alimentacin bootstrap est

formada por un diodo bootstrap

y un capacitor bootstrap

.

Operacin bootstrap

1. Cuando

est en estado OFF y

ON (Figura 38), el capacitor

se carga a un valor

de tensin prximo a

, el tiempo de carga de

es:

)

Dnde:

Figura 38. Carga de capacitor bootstrap

.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

36

2. Cuando

pasa a estado OFF y

a ON el diodo

se polariza inverso. (Figura 39)

Figura 39. Polarizacin inversa del diodo bootstrap

Con la tensin a la que se cargo

en el estado anterior se polariza el bloque del driver que

maneja el IGBT superior

del puente, por lo que ahora

pasa a ON. En esta situacin la

tensin inversa que soporta

es:

Se desea que

sea pequea para que se cargue lo ms rpido posible (

), pero por otro lado interesa que sea grande para que tarde en

descargarse.

La eleccin de los elementos que forman el bootstrap y los elementos auxiliares que necesita

el driver se basa en el trabajo se basa segn [4].

Diodo bootstrap:

Diodo de recuperacin rpida FR107

Capacitor bootstrap:

Capacitor electroltico

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

37

Transistor de potencia

La eleccin del semiconductor de potencia responde a las solicitaciones elctricas que

soportaran los mismos y tambin pensando en el stock y economa del componente. Se debe

escoger un transistor que pueda soportar la tensin de alimentacin continua igual a

entre Drain y Source. Segn la especificacin de potencia del inversor, el transistor debe

ser capaz de manejar una corriente de aproximadamente .

Para la realizacin de este proyecto se escogi el MOSFETCSD18534KCSDe la firma Texas

Instruments. Que cumple satisfactoriamente los requisitos de tensin y corriente. En la Figura

40, se ve el diagrama de este MOSFET y su aspecto fsico.

Figura 40. MOSFET CSD18534KCS.Texas Instruments.

A continuacin en la Figura 41, se ilustra el conexionado de una de las ramas de un puente H,

con el Driver IR2113 y los MOSFET CSD18534KCS.

Figura 41. Driver y MOSFETs manejados por el mismo.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

38

Igual que para el bloque de control se realizo la plaqueta del bloque de potencia y mediante el

software PCB WIZARD. El bloque de Potencia estar conformado por dos plaquetas, una

correspondiente al Driver y la segunda al Puente H. En la Figura 42 se puede observar el

aspecto de la plaqueta del bloque de potencia generada por el software.

Figura 42. Circuito del Driver PCB Software

Figura 43. Circuito Puente H PCB Software

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

39

El circuito de Potencia construido se ilustra en la Figura 44. El tamao final de la plaqueta del

Driver es de 10 cm de ancho por 10 cm de alto y la plaqueta del Puente H es de 10 cm de

ancho por 20 cm de alto.

Figura 44. Plaquetas del Bloque de Potencia

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

40

Transformadores

Para poder generar la tensin senoidal, cada puente H debera aportar distintos niveles de

tensin, pero esto no es posible ya que todos comparten la misma fuente de alimentacin

.Para llevar a cabo la tarea de formar una seal de salida con la mejor

aproximacin a una seal senoidal es que se emplean transformadores con sus primarios

conectados a los distintos arreglos de puentes H y sus secundarios conectados entre ellos en

serie como se muestra en la Figura 45.

Figura 45. Arreglo de puentes H transformadores.

A partir de lo visto en3.2 se confecciona la Tabla 9 para los transformadores de cada etapa.

Tabla 9. Tensiones primarias y secundarias de los transformadores y sus relaciones de transformacin.

El diseo y clculo de los transformadores consiste en elegir el tipo de ncleo que se va a

utilizar, elegir el carrete correspondiente, definir los nmeros de espiras de primario y

secundario, as como los dimetros de los conductores esmaltados de los dos bobinados.

Etapa

Tensin del primario Tensin del secundario Relacin de

transformacin terica

Auxiliar 1

Auxiliar 2

Principal

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

41

Los datos de partida para cada grupo son las tensiones de primario y secundario del

transformador, su potencia nominal, su tensin de circuito abierto o de vaco y el

calentamiento permitido para el funcionamiento correcto del transformador.

Diseo

El circuito magntico de un transformador monofsico est caracterizado por dos reas o

superficies caractersticas: el rea de Ncleo,

, que es la superficie de la columna central del

transformador, y el rea de Ventana,

, , que es la superficie del hueco o ventana que queda

entre la columna central y las laterales; en realidad es la superficie que estar ocupado por los

bobinados de primario y secundario, as como por los aislamientos.

Las chapas magnticas que se utilizarn tienen forma de E y de I. En la Figura 43 puede verse el

tipo de chapas que se utilizarn para construir el ncleo del transformador.

Figura 46. Chapas magnticas empleadas en la fabricacin del ncleo.

Segn la notacin que se observa en la figura se puede expresar el rea ventana y el rea

ncleo de la siguiente forma:

rea ventana:

rea ncleo:

Donde es la profundidad del ncleo.

En lo posible, en la prctica siempre se trata de tomar , asi

ser una seccin

prcticamente cuadrada.

Al producto

se lo denomina rea producto

, y es un valor muy significativo en el

diseo del transformador, ya que est relacionado con la potencia nominal y con la densidad

de corriente de los bobinados de primario y secundario.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

42

Parmetro de los bobinados

Para definir completamente cada bobinado es necesario determinar sus dimensiones, el

tamao del conductor que la forma y el nmero de espiras. En este caso, la altura de ventana

est definida por el tipo de chapas:

, siendo el ancho de la columna central de la chapa

magntica. En la Figura 47 se puede observar las distintas dimensiones y parmetros de un

conjunto de dos bobinados concntricos.

Figura 47 Dimensiones de los bobinados.

Las dimensiones de las bobinas son, adems de y (altura y espesor de la bobina;

si hay dos bobinados), la profundidad () y la anchura () de las chapas magnticas

(son las dimensiones del ncleo: y ), el espesor del carrete y la longitud media de bobina

o de espira

(se le llama tambin

o ). El espesor del aislamiento entre bobinados

es . No toda la superficie (

para cada bobina) ser efectiva.

Normalmente esto se mide con el coeficiente de llenado, que ser un valor comprendido entre

0.4

0.6.

La relacin entre las dimensiones geomtricas y el nmero de capas y de espiras por capa para

cada bobina es la siguiente:

Nmero de espiras por capa:

)

Nmero de capas de la bobina:

)

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

43

Altura:

Espesor de bobina:

(

)

Nmero total de espiras:

De la figura(figura anterior) se puede deducir la longitud de conductor y la resistencia de

cada bobina:

Es la resistencia a la cd, para conocer la resistencia a la ca se multiplica esta valor por 1.2.

La inductancia de dispersin de flujo equivalente en el primario

para un bobinado en capas

como el analizado se lo calcula mediante la expresin:

Con las longitudes en .

Como se dijo anteriormente el rea producto,

, es un valor significativo en el diseo de los

transformadores, ya que est relacionada con la potencia nominal y con la densidad de

corriente de los bobinados de primario y de secundario. Su valor es el punto de partida del

diseo de un transformador y es funcin de distintas magnitudes y coeficientes, tal como

puede verse.

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

44

Dnde:

Observaciones:

rea transversal del hierro:

rea real del cobre:

Densidades de corriente:

Donde

]

Se puede tomar en una primera instancia y si es necesario al rehacer los clculos se

puede ver si interesa que

.

Adems se puede obtener la densidad de la corriente de cada bobinado de acuerdo con el

valor de

y el elegido. De esa manera la densidad de la corriente ser:

Se partir del valor obtenido del rea producto y en una primera aproximacin, se intentara

que la columna central del ncleo tenga seccin transversal cuadrada o, al menos

aproximadamente cuadrada. De esta forma se tomara el tamao de chapa que interese y se

obtendr el valor real de y el nmero de chapas necesarias. Con estos datos se elegir el

carrete adecuado.

Lo siguiente es calcular, con los valores anteriores, las secciones de los conductores de

primario y de secundario, y sus dimetros:

Para el primario se tiene la seccin:

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

45

Para el secundario se tiene la seccin:

Los nmeros de espiras de primario y secundario se obtienen segn:

Habr que comprobar que las bobinas as definidas, con su nmero de espiras y con el

dimetro de conductor, puedan colocarse en la ventana disponible. Se puede hacer la

comprobacin calculando el valor total de superficie de cobre que habr en la ventana y ver si

es menor que la superficie de sta; adems, se comprobara que su valor est comprendido

entre 0.4 y 0.6 si no, habr que rehacer los clculos.

Una vez que este clara la eleccin de los conductores y de las bobinas, hay que obtener el

nmero de espiras por capa y el nmero de capas de cada bobinado.

Etapa Principal

A continuacin se desarrolla el dimensionado y posterior construccin de la etapa principal. De

3.2.1 se saba que

, desde ahora en adelante

, y segn

especificaciones del inversor en 3.2

, adems para la etapa Principal se tiene

, pero para el clculo adopto

. En cuanto a las

corrientes se tiene:

y segn

, se tiene:

rea producto de la etapa Principal:

Con:

[

(

)

]

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

46

Se considerara que:

Con

] [

]

Seccin de los conductores

Primario:

Se adopta

Secundario:

Se adopta

Dimensin de la chapa :

En una primera instancia se considera por lo que el rea producto se puede expresar

como:

Recordando que

, de la expresin anterior se puede despejar

Se adopta y la profundidad de la columna central igual a

Nmero de espiras

Primario:

Secundario:

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

47

3.4.4 Especificaciones Tcnicas

IV. Resultados Experimentales

V. Conclusiones

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

48

ANEXO I

Se presenta las lneas de cdigo fuente del programa de inversor:

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

49

ANEXO II

Enlaces de los Datos Tcnicos de los elementos

A. Microcontrolador 16F873A

http://ww1.microchip.com/downloads/en/DeviceDoc/39582b.pdf

B. Optoacoplador 6N137

http://www.fairchildsemi.com/ds/6N/6N137.pdf

C. Compuerta Inversora

http://www.nxp.com/documents/data_sheet/74HC_HCT14.pdf

D. Driver IR2113

http://www.irf.com/product-info/datasheets/data/ir2110.pdf

E. Transistor CSD18533KCS

http://www.ti.com/lit/ds/symlink/csd18533kcs.pdf

F. Disipador

http://www.gmelectronica.com.ar/catalogo/pag82-83.html

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

50

ANEXO III

Disipador de Calor

Durante el funcionamiento del transistor se genera un aumento de temperatura debido al

calor que se genera en la unin. Este calor debe transferirse del dispositivo a un medio ms

frio, a fin de mantener la temperatura de operacin dentro del rango especificado. Esta

transferencia de calor se realiza por medio de conveccin, el cual el calor debe fluir desde el

dispositivo hacia su carcasa de ah al disipador de calor y este al medio enfriador.

El disipador de calor es un elemento complementario de aluminio que se usan para aumentar

la evacuacin de calor del componente al que se le coloque, hacia el aire que lo rodea. Hay una

amplia gama de disipadores de calor extruido disponible comercialmente, que utilizan aletas

de enfriamiento a fin de aumentar la capacidad de transferencia de calor, algunos de estos se

ven en la siguiente figura.

Para el clculo del disipador veremos primero la ley de ohm trmica. El cual al igual que en los

circuito elctricos, se puede definir un ley de ohm en los circuitos de flujo de calor. El papel de

la fuente de tensin elctrica lo cumple el componente que genera el calor que se desea

evacuar. El papel de masa de un circuito elctrico lo tiene el aire. La diferencia de tensin

elctrica encuentra su anlogo en la diferencia de temperatura. La potencia generada en

forma de calor en el componente tiene su equivalente en la corriente elctrica entregada por

la fuente de tensin. Por ltimo, la resistencia elctrica tiene su reflejo en la resistencia

trmica medida en C/W. Con esto podemos ya formular la ley de ohm trmica:

: Temperatura mxima de la unin del elemento semiconductor.

: Temperatura Ambiente

: Potencia consumida por el componente

: Resistencia trmica total entre la unin y el aire ambiente.

FiguraNN.Disipadores de aluminio

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

51

El diagrama de montaje de componente-disipador ser el siguiente:

A partir de este, tenemos el siguiente circuito trmico, o de flujo de calor asociado:

Por la analoga con los circuitos elctricos se puede ver que

Y partir de la ley de ohm trmica, podr expresarse as:

)

Lo que se necesita para la eleccin del disipador es determinar

. Como todos los

dems valores de la ley de ohm trmica son conocidos, se los despeja y se determina el valor.

: Temperatura de la unin semiconductora

: Temperatura del aire circundante

: Temperatura de la capsula del transistor

: Temperatura del disipador

: Resistencia trmica entre la unin y la capsula

: Resistencia trmica entre la capsula y el disipador

: Resistencia trmica entre el disipador y el

ambiente

: Potencia disipada en forma de calor por el transistor

FiguraNN.Conexin del disipador

FiguraNN.Circuito Trmico

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

52

Para el puente H, se utilizara el transistor CSD18533KCS MOSFET, cuyos datos para el clculo

son:

Despejando de la ley de ohm trmica el valor de

tendremos:

Por lo tanto, el disipador que le coloquemos al transistor deber tener una resistencia trmica

de cmo mucho

De acuerdo a los catlogos de disipadores se selecciono el disipador que se muestra en la

Figura NN, cuyas dimensiones se muestran en la Tabla NN.

= 125 *C+

= 40 *C+

= 0,5 *C/W+

= 1 *C/W+ (se adopto)

= 40 [W]

FiguraNN.Disipadores

Inversor Multinivel de Tres Etapas en Cascada

Electrnica de Potencia

53

Debido que no se encontr exactamente el mismo disipador, se utiliz perfiles de aluminio

comprado en el mercado local, el cual se muestra en la Figura NN

Para determinar si el perfil es el adecuado, se verifico midiendo y comparando la superficie de

ambos.

Tabla NN. Dimensiones de los Disipadores

Figura NN. Disipador del Proyecto

You might also like

- Interruptor-seccionador aislado en SF6 Hasta 36 kVDocument20 pagesInterruptor-seccionador aislado en SF6 Hasta 36 kVCesar Augusto Restrepo LopezNo ratings yet

- Compensacion en MTDocument9 pagesCompensacion en MTJuan Martin RomeroNo ratings yet

- Ensayo de Cortocircuito de Un TransformadorDocument4 pagesEnsayo de Cortocircuito de Un TransformadorJuan Martin RomeroNo ratings yet

- Cables aislados para distribución aérea: ventajas y evoluciónDocument22 pagesCables aislados para distribución aérea: ventajas y evolucióncolcha79No ratings yet

- Baterías selladas VRLA MC/MCE: especificaciones, aplicaciones y característicasDocument4 pagesBaterías selladas VRLA MC/MCE: especificaciones, aplicaciones y característicasPablo KuziwNo ratings yet

- Tira de Freno AvkoDocument1 pageTira de Freno AvkoJuan Martin RomeroNo ratings yet

- Catalogo Lineas AereasDocument50 pagesCatalogo Lineas Aereaslagm54No ratings yet

- ETN-97a 12-02Document10 pagesETN-97a 12-02Maman86No ratings yet

- Tira de Freno OkladzinyDocument4 pagesTira de Freno OkladzinyJuan Martin RomeroNo ratings yet

- Bancos PosteDocument6 pagesBancos PosteLuis CuripomaNo ratings yet

- Aplic Matlab Motor InduccionDocument10 pagesAplic Matlab Motor InduccionjglunaNo ratings yet

- Mezcladora de Audio Con Atenuadores Automatizados Por Una PCDocument9 pagesMezcladora de Audio Con Atenuadores Automatizados Por Una PCJuan Martin Romero100% (1)

- Capitulo 3Document0 pagesCapitulo 3Konejito BallinasNo ratings yet

- Eu Pss EspesDocument2 pagesEu Pss EspesJuan Martin RomeroNo ratings yet

- Monografía (Centrales) FinalDocument32 pagesMonografía (Centrales) FinalJuan Martin RomeroNo ratings yet

- F Ace Sensores Fotoelectricos PDFDocument1 pageF Ace Sensores Fotoelectricos PDFJuan Martin RomeroNo ratings yet

- Mezcladora de Audio Con Atenuadores Automatizados Por Una PCDocument9 pagesMezcladora de Audio Con Atenuadores Automatizados Por Una PCJuan Martin Romero100% (1)

- GeneralDocument0 pagesGeneralClaudio SotoNo ratings yet

- DialuxDocument5 pagesDialuxJuan Martin RomeroNo ratings yet

- Horario Yachay TechDocument30 pagesHorario Yachay TechAntonio Villagómez ChiluisaNo ratings yet

- Informe de ExtintoresDocument2 pagesInforme de Extintoresandres roman100% (1)

- Desconsuelo Al Amanecer - Alejandra AndradeDocument374 pagesDesconsuelo Al Amanecer - Alejandra AndradeLaura GutièrrezNo ratings yet

- TEMA 1.concepto y Función 1docDocument9 pagesTEMA 1.concepto y Función 1docmariapi_1984No ratings yet

- Bianco 2 ESPAÑOL 6 GRADODocument19 pagesBianco 2 ESPAÑOL 6 GRADOBolivar Concepcion PrescottNo ratings yet

- Rubrica para Evaluar Investigacin en WordDocument1 pageRubrica para Evaluar Investigacin en Wordapi-257093331No ratings yet

- Analisis de Intersecciones C 00 1PBDocument5 pagesAnalisis de Intersecciones C 00 1PBmarco antonio arroyo ortegaNo ratings yet

- Joven de 20 Años Muere Por Tomar Tapsin Caliente Día de NocheDocument7 pagesJoven de 20 Años Muere Por Tomar Tapsin Caliente Día de NocheVicente100% (1)

- SEMANA 1-2-3-4-5 Entorno Económico y Social de MéxicoDocument67 pagesSEMANA 1-2-3-4-5 Entorno Económico y Social de MéxicoAna Paulina DávalosNo ratings yet

- Pts Rodillo Compactador MilkoDocument12 pagesPts Rodillo Compactador MilkoKarina Moreno RiquelmeNo ratings yet

- Actividad 2. Conceptos Fundamentales.Document5 pagesActividad 2. Conceptos Fundamentales.Andrea SantacruzNo ratings yet

- Dispositivos InformaticosDocument18 pagesDispositivos InformaticosClaudio R. MartínezNo ratings yet

- Cotización Mundo InmobiliarioDocument1 pageCotización Mundo Inmobiliarioyobani canastujNo ratings yet

- Luz y Sombras en Los Elementos Naturales y ArtificialesDocument13 pagesLuz y Sombras en Los Elementos Naturales y ArtificialesVictor Hugo Alejandro67% (3)

- Indicadores en Música ProfesoresDocument45 pagesIndicadores en Música ProfesoresfelicreazNo ratings yet

- TemperaturaDocument12 pagesTemperaturaJustiniano de la CruzNo ratings yet

- Transmisión de PotenciaDocument13 pagesTransmisión de PotenciaAlvaro Diaz AvilaNo ratings yet

- Carga Variable y ConstanteDocument6 pagesCarga Variable y ConstantePliiNxekika PerexNo ratings yet

- 02 Programa Montaje 2013 PDFDocument11 pages02 Programa Montaje 2013 PDFGustavo Noel Chavarria CastellanoNo ratings yet

- Especialidades Scouts: Deportes y actividades al aire libreDocument55 pagesEspecialidades Scouts: Deportes y actividades al aire libreAnny SfmNo ratings yet

- Previo 3. Anatomía Comparada de La Rata y HumanoDocument10 pagesPrevio 3. Anatomía Comparada de La Rata y HumanoFelipe rodriguez islas100% (1)

- Pánico EscénicoDocument3 pagesPánico EscénicocarolinaNo ratings yet

- Guia Documento (Plan de Mejora Prácticas) Nivel Tecnologo 2Document5 pagesGuia Documento (Plan de Mejora Prácticas) Nivel Tecnologo 2JOHN EDINSON ACHAGUANo ratings yet

- Tesis - Completa Torre Autosoportada 40M UNAM PDFDocument142 pagesTesis - Completa Torre Autosoportada 40M UNAM PDFOtilio López OlmNo ratings yet

- Disposiciones Complementarias FinalesDocument2 pagesDisposiciones Complementarias FinalesAdriana NicollNo ratings yet

- Ensayo de Formacion SocioculturalDocument5 pagesEnsayo de Formacion SocioculturalJosé Montes de OcaNo ratings yet

- Planificacion Procedimientos Tecnicos para 2doDocument21 pagesPlanificacion Procedimientos Tecnicos para 2doMíriamNo ratings yet

- Actividad de Refuerzo: María Inmaculada School Investigando Caminamos Hacia La ExcelenciaDocument3 pagesActividad de Refuerzo: María Inmaculada School Investigando Caminamos Hacia La ExcelenciaMariana OrtegonNo ratings yet

- Hemorragia PostpartoDocument3 pagesHemorragia Postpartojuan pablo lopezNo ratings yet

- UnidadDocument5 pagesUnidadjos22miguel2moreno2cNo ratings yet