Professional Documents

Culture Documents

Matched Length PCB

Uploaded by

John LeungOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Matched Length PCB

Uploaded by

John LeungCopyright:

Available Formats

Advances in PCB Routing

Martin D.F. Wong

Dept of Electrical and Computer Engineering

University of Illinois at Urbana-Champaign

SLIP-2010

Printed Circuit Board (PCB)

2

Components plug

in or mounted on to

PCB

Each component

corresponds to a

pin array on the

board

Multiple routing

layers

PCB Routing

Planar routing

on each layer

Escape routing

Pin to boundary

Satisfying

constraints

Area routing

Between

boundaries

Length matching

3

Length-Matching Routing

T. Yan & M. Wong, ICCAD-2008

Length-matching routing in PCB

In high frequency boards, the timing requirements on

wires are very tight

Most wires are assigned min-max length bounds

Difficult due to the competition for resources

1

1

2

2

3

3

Previous Works

LR based monotonic routing

Min-max river routing

General topology

They are all gridded

Major drawback: problem size determined by

physical distance, not routing difficulty

Same topology, but different problem size for gridded router

Problem definition

Input:

Two components and a set of nets connecting them (net

ordering on the boundary guarantees planarity)

Design rules

Length bounds for the nets

Output

Rectilinear routing that satisfies design rule and length bounds

Length-matching = Area-matching

If we consider the wire as a fat wire

width () = wire_width + separation

Then the length of the wire is proportional to the

area it occupies

Instead of control the length, we control the area

each wire occupies.

Bounded-Sliceline Grid

Originally proposed for placement

Dissect the plane into cells by short

segments (walls)

By moving the segments, we can enlarge,

shrink and move cells

Workflow of our router

Workflow of our router (cont)

BSG embedding

Can be done by heuristics like maze router

Need to follow some guidelines:

Allow empty rooms between adjacent nets

Use proper number of BSG cells

Keep the topological relationships between

components and pins

BSG embedding

Key step: Cell sizing

Need to size the cells so that the following

constraints are satisfied:

Design rule

Component and pin location

Length(area) bounds for each net

We formulate this problem as a mathematical

programming problem

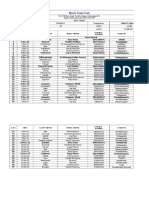

Experimental results

Compare with Ozdal & Wong TCAD06 LR-

based router

Tested on 7 data:

monotonic_1*, monotonic_2*, monotonic_3,

monotonic_4

general_1*, general_2, general_3

Expeirmental results

An example (general_3)

Escape Routing

T. Yan and M. Wong, DAC 2009

Escape Routing

Route (black) pins to the boundary of the pin grid array

The grid has Orthogonal and Diagonal wiring capacity (O-cap and D-cap)

Traditional network-flow model

O-cap can be guaranteed, but D-cap is not reflected

Some works assign node capacity to tile node, but it still

does not reflect D-cap correctly

When traditional model fails

Assume O-cap =2and D-cap =3

No constraints on tile node leads to illegal routing (a)

Let tile node capacity = 3 or less misses the legal routing

case (b)

Traditional network-flow model is not capable of

capturing diagonal capacity

O-cap

O-cap

O-cap

O-cap

(b) (a)

Our Network Flow Model

W

S

N

E C

: capacity =O-cap

: capacity =O-cap/2

: capacity =1

: capacity =

: node capacity =D-cap 2 O-cap/2

Node capacity

implementation

Capture O-cap and D-cap

W

S

N

E C

An orthogonal cut cuts only

one hallow edge, which has

capacity exactly O-cap

An diagonal cut cuts two solid

edges and center node. The sum

of their capacities is

2O-cap/2+(D-cap - 2O-cap/2)

=D-cap

The Entire Flow Network

Pin Grid

(O=2, D=3)

Network

Optimal single-layer

escape routing!

Missing pin

In real designs, some pins in the array maybe

removed. This leads to extra routing resource

A B

The wiring capacity

between A and B

increases from 4 to 6

due to the missing pin.

We call the difference,

2, extra capacity and

denote it as

Consider missing pins in our model

1

1

1

1

1

1

1

1

1

1

1

Consider the missing

pin as a resource

node

The capacity of the

resource node is

exactly the extra

capacity

Experimental results

Tested on industrial data

Results indicate that our model has zero D-cap violation

for all data while traditional model has violations

Though our model is more complicated, the runtime are

comparable

A sample result

Pin Assignment

H. Kong, T. Yan and M. Wong, ASP-DAC 2010

Pin Assignment for Buses

31

One routing layer

32

Pin Assignment Problem

Assign signals (nets) to Pins

Significant influence on later routing

Existing algorithms

Based on heuristic metrics to estimate routability

No routability guarantee

Simple routing solution

Complex routing solution

33

Single-Layer Pin Assignment and Routing

Solve two independent escape routing problems

Assign pins to nets by sweeping pin escape positions

Optimal pin assignment and routing

Multi-Layer Pin Assignment and Routing

35

Projection Style Escape

Projection Interval: Project the bounding box to the component

boundary.

Nets escape the component from its bus projection interval

Need multiple layers

Different pin/layer assignments affect routing resource utilization

36

Experimental Results

Equal-length routing

Back detours in the left component

Complex length extension between component boundaries

Single-layer solution

37

Experimental Results

Equal-length solution

No back detours

Simple length extension between component boundaries

37.15% shorter total length

21.36% shorter escape wire length

44.96% shorter detailed wire length

Cut-style solution: Layer 1

Experimental Results

Cut-style solution: Layer 2

Experimental Results

State-of-the-art industrial PCB

7000+ nets

80 buses

12 routing layers

Previously routed manually

manual routing typically takes 2 months per board

Pin assignment and escape routing results

All 80 buses takes less than 5 minutes

The largest bus

338 nets

Takes 6 routing layers

39

Simultaneous Escape

Lijuan Luo et al, ISPD-2010

Simultaneous Escape

Approach

Net-by-net routing with various routing styles

Determine next net to route

Route net along routing boundary

Routing boundary

Experimental Results

Performs significantly better than Cadence Allegro

Runtimes range from 0.2s to 289s

Experimental Results

Bus Escape Problem

Hui Kong et al DAC 2010

46

Bus Escape Routing

Route nets from pins to component boundaries

Keep bus structures

Routing region for the bus is a boundary rectangle

Formulate as a Maximum Disjoint Subset problem.

47

Maximum Disjoint Subset (MDS) Problem

General rectangles NP-complete

Boundary rectangle Open Problem

Rectangle attached to one or more boundaries

We designed a polynomial time optimal algorithm!

Problem Solution

You might also like

- HttpsDocument1 pageHttpsJohn LeungNo ratings yet

- Volatile KeywordRTOSDocument6 pagesVolatile KeywordRTOSJohn LeungNo ratings yet

- TestingPrecedure 1141B EDCUDocument1 pageTestingPrecedure 1141B EDCUJohn LeungNo ratings yet

- ZCR 19372 v0.4Document10 pagesZCR 19372 v0.4John LeungNo ratings yet

- 23 Cmsis-RtosDocument17 pages23 Cmsis-RtosJohn LeungNo ratings yet

- Viracon Architectural Glass: Tech TalkDocument4 pagesViracon Architectural Glass: Tech TalkJohn LeungNo ratings yet

- New LRV PS Mainbody - Appendix 12Document332 pagesNew LRV PS Mainbody - Appendix 12John Leung100% (1)

- Vibration Assessment Report For Sensor ID595 Test2Document54 pagesVibration Assessment Report For Sensor ID595 Test2John LeungNo ratings yet

- Vibration Assessment Report For Sensor ID595 Test3Document68 pagesVibration Assessment Report For Sensor ID595 Test3John LeungNo ratings yet

- Strainoptics: PSV-100 Portable Strain ViewerDocument2 pagesStrainoptics: PSV-100 Portable Strain ViewerJohn LeungNo ratings yet

- Jjg 233-1996 揤萇樓厒僅數潰隅寞最Document16 pagesJjg 233-1996 揤萇樓厒僅數潰隅寞最John LeungNo ratings yet

- First Time Right Multistage AmplifiersDocument11 pagesFirst Time Right Multistage AmplifiersJohn LeungNo ratings yet

- JJF 1059 - 1-2012Document61 pagesJJF 1059 - 1-2012John LeungNo ratings yet

- Jjg 233-2008 压电加速度计检定规程 The document is for vibration analysisDocument20 pagesJjg 233-2008 压电加速度计检定规程 The document is for vibration analysisJohn LeungNo ratings yet

- Rochester: Insulated GlassDocument6 pagesRochester: Insulated GlassJohn LeungNo ratings yet

- RTOS For Fault Tolerant ApplicationDocument8 pagesRTOS For Fault Tolerant ApplicationKarthick SubramaniamNo ratings yet

- Introduction To Arduino MicrocontrollersDocument32 pagesIntroduction To Arduino MicrocontrollersJohn LeungNo ratings yet

- STM32F30xx-31xx Standard Peripheral Library UM1581Document584 pagesSTM32F30xx-31xx Standard Peripheral Library UM1581John LeungNo ratings yet

- Introduction To Arduino MicrocontrollersDocument21 pagesIntroduction To Arduino MicrocontrollersJohn LeungNo ratings yet

- Intro To The ArduinoDocument18 pagesIntro To The ArduinoJohn LeungNo ratings yet

- RTOS Main Problem of Priority Inversion and RTOS-Versus-GposDocument5 pagesRTOS Main Problem of Priority Inversion and RTOS-Versus-GposJohn LeungNo ratings yet

- EDU Curriculum ENGDocument2 pagesEDU Curriculum ENGJohn LeungNo ratings yet

- Arduino Section ProgrammingDocument54 pagesArduino Section ProgrammingJohn LeungNo ratings yet

- Arduino 101 Intro by Ted Markson / Jim SweeneyDocument18 pagesArduino 101 Intro by Ted Markson / Jim SweeneyJesus Perez CarrenoNo ratings yet

- ArduinoDocument25 pagesArduinoJohn LeungNo ratings yet

- ArduinoDocument33 pagesArduinosurendersuriNo ratings yet

- Arduino Board: Arduino UNODocument104 pagesArduino Board: Arduino UNOJohn LeungNo ratings yet

- PIC2Document85 pagesPIC2John LeungNo ratings yet

- Trebuchet ProjectDocument256 pagesTrebuchet ProjectJohn LeungNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Temperature Transmitter RadixDocument4 pagesTemperature Transmitter RadixRohit MoreNo ratings yet

- BSBRSK501 Manage RiskDocument105 pagesBSBRSK501 Manage RiskStavros NathanailNo ratings yet

- Agency and Empowerment: A Proposal For Internationally Comparable IndicatorsDocument60 pagesAgency and Empowerment: A Proposal For Internationally Comparable IndicatorsClaudia LyNo ratings yet

- Panasonic KW1M HDocument11 pagesPanasonic KW1M Hbole90No ratings yet

- 10ME64 FEM Lesson Plan (Student)Document9 pages10ME64 FEM Lesson Plan (Student)PavanKumarNNo ratings yet

- Sri Final Job SheetDocument4 pagesSri Final Job SheetMohan LalNo ratings yet

- Communication Systems Projects PDFDocument2 pagesCommunication Systems Projects PDFAmandaNo ratings yet

- Parametric Cost Estimating Model For Conceptual Cost Estimating of Building Construction ProjectsDocument24 pagesParametric Cost Estimating Model For Conceptual Cost Estimating of Building Construction ProjectsmrvictormrrrNo ratings yet

- Splunk 4.2.3 AdminDocument426 pagesSplunk 4.2.3 AdminjazzymoonNo ratings yet

- Crash 2023 05 28 - 22.13.25 ClientDocument7 pagesCrash 2023 05 28 - 22.13.25 Clientdanker37xpNo ratings yet

- All mIRC CommandsDocument4 pagesAll mIRC CommandsAbhishek KunalNo ratings yet

- Kubernetes Troubleshooting DocsDocument15 pagesKubernetes Troubleshooting Docschandrashekar_ganesanNo ratings yet

- SAT Math Notes: by Steve Baba, PH.DDocument6 pagesSAT Math Notes: by Steve Baba, PH.DAnas EhabNo ratings yet

- Civil Engineering Report GuidelinesDocument14 pagesCivil Engineering Report GuidelinesjinshadNo ratings yet

- Quiz1 - Conditional Control If StatementsDocument5 pagesQuiz1 - Conditional Control If StatementsAncuta CorcodelNo ratings yet

- Notes Polar Complex Numbers PDFDocument3 pagesNotes Polar Complex Numbers PDFXavier RodríguezNo ratings yet

- Mobile MarketingDocument9 pagesMobile MarketingGianiCristeaNo ratings yet

- D72896GC40 - Oracle Solaris 11 System Administration - SG2Document430 pagesD72896GC40 - Oracle Solaris 11 System Administration - SG2Mounir Ben Mohamed100% (2)

- OracleCloudEstimate EDIDocument1 pageOracleCloudEstimate EDIArsenij KroptyaNo ratings yet

- Bank StatmentDocument41 pagesBank StatmentManager VikasNagar 22No ratings yet

- Experiment No.1: Design All Gates Using VHDLDocument38 pagesExperiment No.1: Design All Gates Using VHDLashutoshdabas17No ratings yet

- POAF (Employer)Document1 pagePOAF (Employer)Youka MainNo ratings yet

- All About Data Transfer Process (DTP) - SAP BW 7 - SCNDocument6 pagesAll About Data Transfer Process (DTP) - SAP BW 7 - SCNloknathtanikantiNo ratings yet

- HAMEG FA Oscilloscopes Why Analog EDocument2 pagesHAMEG FA Oscilloscopes Why Analog EGeorgeNo ratings yet

- In Christ Alone With Cornerstone by - Digital Sheet Music For Octavo - Download & Print H1.C6231DP Sheet Music PlusDocument1 pageIn Christ Alone With Cornerstone by - Digital Sheet Music For Octavo - Download & Print H1.C6231DP Sheet Music PlusAlexander Trujillo0% (1)

- SLHT Grade 7 CSS Week 2Document6 pagesSLHT Grade 7 CSS Week 2princeyahweNo ratings yet

- WDV Dep MethodDocument24 pagesWDV Dep Methodsudershan9No ratings yet

- Antivirus SoftwareDocument1 pageAntivirus SoftwareMary Ann SalvatierraNo ratings yet

- Jura J9.3 Wiring DiagramDocument4 pagesJura J9.3 Wiring DiagramGrom NeposedaNo ratings yet

- Requirements Specification and Analysis IIDocument35 pagesRequirements Specification and Analysis IIayushNo ratings yet