Professional Documents

Culture Documents

Verilog1995 2001

Uploaded by

Pardhasaradhi DamarlaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Verilog1995 2001

Uploaded by

Pardhasaradhi DamarlaCopyright:

Available Formats

Verilog 1995 Vs Verilog 2001

Introduction

The Verilog-2001 Standard was approved by the IEEE in June of 2000 and includes

enhancements to the previously existing Verilog standard in the following areas:

Enhance the Verilog language to help with todays deep-submicron and intellectual

property modelling issues

Ensure that all enhancements were both useful and practical, and that simulator and

synthesis vendors would implement Verilog-2001 in their products

Correct any ambiguities in the Verilog-1995 standard (IEEE 1364-1995) Verilog 2001

expands the construct set of Verilog 1995 but does not replace or change the behavior of

previously implemented constructs. Users may seamlessly mix new and previously existing

constructs.

Supported Verilog 2001 Constructs

Precision Synthesis V2002c offers support for the following Verilog-2001 constructs

Signed arithmetic extensions

Comma-separated sensitivity list

Combinational logic sensitivity token

Combined port / data type declarations

ANSI-style port lists

Power Operator

Automatic width extension past 32 bits

Register declaration with initialization

Multi dimension Arrays

Generate Loop

Detailed Description

Combinational logic sensitivity token

To properly model combinational logic using a Verilog always procedure, the sensitivity list

must include all input signals used by that block of logic. In large, complex blocks of

combinational logic, it is easy to inadvertently omit an input from the sensitivity list, which

can lead to simulation and synthesis mismatches.

Verilog-2000 adds a new wild card token, @*, which represents a combinational logic

sensitivity list. The @* token indicates that the simulator or synthesis tool should

automatically be sensitive to any values used by the procedure in decisions or in expressions

on the right-hand side of assignment statements.

In the following example, the @* token will cause the procedure to automatically be

sensitive to changes on sel, a or b.

always @* //combinational logic sensitivity

if (sel)

y = a;

else y = b;

Combined port / data type operator

Verilog requires that signals connected to the input or outputs of a module have two

declarations: the direction of the port, and the data type of the signal. In Verilog-1995, these

two declarations had to be done as two separate statements. Verilog-2000 adds a simpler

syntax, by combining the declarations into one statement.

module mux8 (y, a, b, en);

output reg [7:0] y;

input wire [7:0] a, b;

input wire en;

Power operator

Verilog-2001 adds a power operator, represented by an ** token. This operator preforms

similar functionality as the C pow() function. It will return a real number if either operand is

a real value, and an integer value if both operands are integer values. One practical

application of the power operator is to calculate values such as 2n.

For example:

always @(posedge clock)

result = base ** exponent;

Signed Arithmetic Extensions

For integer math operations, Verilog uses the data types of the operands to determine if

signed or unsigned arithmetic should be performed. If either operand is unsigned, unsigned

operations are performed. To perform signed arithmetic, both operands must be signed. In

Verilog-1995, the integer data type is signed, and the reg and net data types are unsigned. A

limitation in Verilog- 1995 is that the integer data type has a fixed vector size, which is

32-bits in most Verilog simulators.

Thus, signed integer math in Verilog-1995 is limited to 32-bit vectors. The Verilog- 2000

standard adds five enhancements to provide greater signed arithmetic capability:

Reg and net data types can be declared as signed

Function return values can be declared as signed

Integer numbers in any radix can be declared as signed

Operands can be converted from unsigned to signed

Arithmetic shift operators have been added

The Verilog-1995 standard has a reserved keyword, signed, but this keyword was not used

in Verilog-1995. Verilog-2000 uses this keyword to allow reg data types, net data types,

ports, and functions to be declared as signed types. Some example declarations are:

reg signed [63:0] data;

wire signed [7:0] vector;

input signed [31:0] a;

function signed [128:0] alu;

In Verilog-1995, a literal integer number with no radix specified is considered a signed value,

but a literal integer with a radix specified is considered an unsigned value. Verilog-2000 adds

an additional specifier, the letter s, which can be combined with the radix specifier, to

indicate that the literal number is a signed value.

16'hC501 //an unsigned 16-bit hex value

16'shC501 //a signed 16-bit hex value

In addition to being able to declare signed data types and values, Verilog-2000 adds two

new system functions, $signed and $unsigned. These system functions are used to convert

an unsigned value to signed, or vice-versa.

reg [63:0] a; //unsigned data type

always @(a) begin

result1 = a / 2; //unsigned arithmetic

result2 = $signed(a) / 2; //signed arithmetic

end

One more signed arithmetic enhancement in Verilog-2000 is arithmetic shift operators,

represented by >>> and <<< tokens. An arithmetic right-shift operation maintains the sign of

a value, by filling with the sign-bit value as it shifts.

For example, if the 8-bit variable D contained 8b10100011, a logical right shift and an

arithmetic right shift by 3 bits would yield the following:

D >> 3 //logical shift yields 8'b00010100

D >>> 3 //arithmetic shift yields 8'b11110100

Comma-separated sensitivity list

Verilog-2000 adds a second way to list signals in a sensitivity list, by separating the signal

names with commas instead of the or keyword. The following two sensitivity lists are

functionally identical:

always @(a or b or c or d or sel)

always @(a, b, c, d, sel)

The new, comma-separated sensitivity list does not add any new functionality. It does,

however, make Verilog syntax more intuitive, and more consistent with other signal lists in

Verilog.

ANSI-style port lists

Verilog-1995 uses the older Kernighan and Ritchie C language syntax to declare module

ports, where the order of the ports is defined within parentheses, and the declarations of

the ports are listed after the parentheses. Verilog- 1995 tasks and functions omit the

parentheses list, and use the order of the input and output declarations to define

the input/output order. Verilog-2000 updates the syntax for declaring inputs and outputs of

modules, tasks, and functions to be more like the ANSI C language. That is, the declarations

can be contained in the parentheses that show the order of inputs and outputs.

module mux8 ( output reg [7:0] y,

input wire [7:0] a,

input wire [7:0] b,

input wire en );

function [63:0] alu (

input [63:0] a,

input [63:0] b,

input [7:0] opcode );

Automatic Width Extension past 32 bits

With Verilog-1995, assigning an unsized high-impedance value (e.g.: bz) to a bus that is

greater than 32 bits would only set the lower 32 bits to high-impedance. The upper bits

would be set to 0. To set the entire bus to high-impedance requires explicitly specifying the

number of high impedance bits. For example:

Verilog-1995:

parameter WIDTH = 64;

reg [WIDTH-1:0] data;

data = 'bz; //fills with 'h00000000zzzzzzzz

data = 64'bz; //fills with 'hzzzzzzzzzzzzzzzz

The fill rules in Verilog-1995 make it difficult to write models that are easily scaled to new

vector sizes. Redefinable parameters can be used to scale vector widths, but the Verilog

source code must still be modified to alter the literal value widths used in assignment

statements.

Verilog-2000 changes the rule for assignment expansion so that an unsized value of Z or X

will automatically expand to fill the full width of the vector on the left-hand side of the

assignment.

Verilog-2000:

parameter WIDTH = 64;

reg [WIDTH-1:0] data;

data = 'bz; //fills with 'hzzzzzzzzzzzzzzzz

This Verilog-2001 enhancement is not backward compatible with Verilog-1995. However,

the IEEE standards group felt the Verilog-1995 behavior was a bug in the standard that

needed to be corrected. It is expected that all existing models with greater than 32-bit

busses have avoided this bug by explicitly specifying the vector sizes. Therefore,

there should not be any compatibility problems with existing models.

Register declaration with initialization

Verilog-2000 adds the ability to initialize variables at the time they are declared, instead of

requiring a separate initial procedure to initialize variables. The initial value assigned to the

variable will take place within simulation time zero, just as if the value had been assigned

within an initial procedure.

Verilog-1995:

reg clock;

initial

clk = 0;

Verilog-2000:

reg clock = 0;

Multi dimension Arrays

In Verilog 1995, you can declare one dimension arrays of integer, reg and time,

We use arrays of reg to model memories and arrays of integer and time in the testbench.

But in verilog 2001 we can declare arrays of any variables or net type, and also declare any

number of dimensions.

Reg [7:0] mem [0:255] [0:3]; // Four 258X8 memories

Reg array3D [7:0] [0:255] [0:3]; // 3-D arrays of bits

Generate Loop

Here's a simple 8-bit shift register created by generating eight "dflop" modules.The nine

"path" wires connect the chain of dflops, from first input through last output. "count"

simply generates a square-wave test signal, like a built-in test bench.

module top (clk, out);

input clk;

reg [3:0] count = 0;

wire [8:0] path;

output out;

always @ (posedge clk)

count <= count + 1;

assign path[0] = count[3];

assign out = path[8];

genvar n;

generate

for (n=0; n<=7; n=n+1) begin : flops

dflop u (.clk(clk), .in(path[n]), .out(path[n+1]));

end

endgenerate

endmodule

module dflop (clk, in, out);

input clk, in;

output reg out;

always @ (posedge clk)

out <= in;

endmodule

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Static Timing Analysis-Bridging The Gap Between Simulation and SiliconDocument6 pagesStatic Timing Analysis-Bridging The Gap Between Simulation and SiliconPardhasaradhi DamarlaNo ratings yet

- Novel and Efficient Power Grid Design For Lesser Metal Layer Process SOC'sDocument8 pagesNovel and Efficient Power Grid Design For Lesser Metal Layer Process SOC'sPardhasaradhi DamarlaNo ratings yet

- Desinging Analog ChipsDocument242 pagesDesinging Analog ChipsRyan Sullenberger100% (12)

- Techniques To Reduce Timing Violations Using Clock Tree Optimizations in Synopsys ICC2Document10 pagesTechniques To Reduce Timing Violations Using Clock Tree Optimizations in Synopsys ICC2Pardhasaradhi Damarla100% (1)

- Research Statement: Patrick ChiangDocument3 pagesResearch Statement: Patrick ChiangPardhasaradhi DamarlaNo ratings yet

- A Design Methodology Using Power-Grid Prototyping To Optimize Area Performance of SoCsDocument10 pagesA Design Methodology Using Power-Grid Prototyping To Optimize Area Performance of SoCsPardhasaradhi DamarlaNo ratings yet

- StarRC UserguideDocument966 pagesStarRC UserguidePardhasaradhi Damarla100% (1)

- OpenSPARCT1 Micro Arch PDFDocument268 pagesOpenSPARCT1 Micro Arch PDFPardhasaradhi DamarlaNo ratings yet

- Common Emitter Amplifier With Current Series Feedback.: R H 2K, R R 10K. Since The Gain Is Very High, RC Is SelectedDocument3 pagesCommon Emitter Amplifier With Current Series Feedback.: R H 2K, R R 10K. Since The Gain Is Very High, RC Is SelectedPardhasaradhi DamarlaNo ratings yet

- AMBA Transactors User and Reference Guide: Product Version 5.4 May 2005Document170 pagesAMBA Transactors User and Reference Guide: Product Version 5.4 May 2005Pardhasaradhi DamarlaNo ratings yet

- Physical Design CompleteDocument303 pagesPhysical Design CompleteReddicool89100% (47)

- Verilog Interview Questions and AnswersDocument16 pagesVerilog Interview Questions and AnswersAashish AggarwalNo ratings yet

- Modelsim TUTORIAL PDFDocument82 pagesModelsim TUTORIAL PDFhasbiiieNo ratings yet

- SV AssertionsDocument99 pagesSV AssertionsPardhasaradhi DamarlaNo ratings yet

- HHHDocument4 pagesHHHPardhasaradhi DamarlaNo ratings yet

- Verilog ADocument170 pagesVerilog Aaminkhan83No ratings yet

- Linaer Integrated CircuitsDocument440 pagesLinaer Integrated CircuitsPardhasaradhi DamarlaNo ratings yet

- LTE Implementation Uing Xilinx FPGADocument294 pagesLTE Implementation Uing Xilinx FPGAPardhasaradhi Damarla100% (1)

- VLSI Design of Low Power Booth MultiplierDocument3 pagesVLSI Design of Low Power Booth MultiplierPardhasaradhi DamarlaNo ratings yet

- C#Document338 pagesC#bebikash011100% (3)

- LTE Implementation Uing Xilinx FPGADocument294 pagesLTE Implementation Uing Xilinx FPGAPardhasaradhi Damarla100% (1)

- Implementation of FPGA Based Fault Injection Tool (FITO) For Testing Fault Tolerant DesignsDocument5 pagesImplementation of FPGA Based Fault Injection Tool (FITO) For Testing Fault Tolerant DesignsPardhasaradhi DamarlaNo ratings yet

- Power and Delay ComparisonDocument5 pagesPower and Delay ComparisonPardhasaradhi DamarlaNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Debbuging Bootloader and Application Using KDSDocument32 pagesDebbuging Bootloader and Application Using KDSSantiago González FabiánNo ratings yet

- InstruçõesDocument22 pagesInstruçõesJf FrmNo ratings yet

- Foxit PDF SDK Upgrade Warnings - AndroidDocument7 pagesFoxit PDF SDK Upgrade Warnings - AndroidLinh Đan TrầnNo ratings yet

- Object Interconnections C++ PDFDocument12 pagesObject Interconnections C++ PDFMSohaibAkramNo ratings yet

- DS Chapter 3Document39 pagesDS Chapter 3Maddula PrasadNo ratings yet

- Unit I PROBLEM SOLVING AND PYTHON PROGRAMMINGDocument51 pagesUnit I PROBLEM SOLVING AND PYTHON PROGRAMMINGRaj KumarNo ratings yet

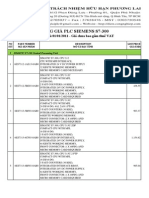

- Bang Gia PLC Siemens s7 300Document11 pagesBang Gia PLC Siemens s7 300916153No ratings yet

- Linux PermissionsDocument4 pagesLinux PermissionsPeddinti shivsai Mohanrao laxmiNo ratings yet

- Accepted Paper List in VlsiDocument4 pagesAccepted Paper List in VlsiGagana PrakashaNo ratings yet

- Voice Attack HelpDocument129 pagesVoice Attack HelparniingiNo ratings yet

- Command Line Assembly Language Programming For Arduino Tutorial 2Document10 pagesCommand Line Assembly Language Programming For Arduino Tutorial 2Kalaignan RajeshNo ratings yet

- Product CatalogueDocument26 pagesProduct CatalogueJason VelasquezNo ratings yet

- FINALDocument24 pagesFINALNaveenKrishNo ratings yet

- Software InstallationDocument51 pagesSoftware InstallationshehzadNo ratings yet

- Windows Server 2008 SetupDocument230 pagesWindows Server 2008 SetupPravinNo ratings yet

- Pin FunctionsDocument12 pagesPin FunctionsMarvin MayormenteNo ratings yet

- Vplex P Hardware Reference v4 PDFDocument78 pagesVplex P Hardware Reference v4 PDFrosennedkovNo ratings yet

- Tidrws6 PDFDocument9 pagesTidrws6 PDFM. T.No ratings yet

- User Manual Boot Manager Boot-US: November/16/2021Document160 pagesUser Manual Boot Manager Boot-US: November/16/2021winkywinnypapuchoNo ratings yet

- DBMS Lab FileDocument9 pagesDBMS Lab Filegaurav chauhanNo ratings yet

- Ilog Jrules TutorialDocument74 pagesIlog Jrules Tutorialvijaykumar015100% (3)

- DL TR 2022 002Document20 pagesDL TR 2022 002popmilo2009No ratings yet

- Hackr Excel Cheat Sheet PDFDocument8 pagesHackr Excel Cheat Sheet PDFNaveed AhmedNo ratings yet

- Aca QBDocument9 pagesAca QBSherril VincentNo ratings yet

- Lab Answer Key: Module 3: Implementing Ipv6 Lab: Configuring and Evaluating Ipv6 Transition TechnologiesDocument10 pagesLab Answer Key: Module 3: Implementing Ipv6 Lab: Configuring and Evaluating Ipv6 Transition TechnologiesLadislauNo ratings yet

- Alfresco 34Document10 pagesAlfresco 34Ayesha KhalidNo ratings yet

- Pcap PDFDocument55 pagesPcap PDFA NguyenNo ratings yet

- FortiGate HA ConfigDocument13 pagesFortiGate HA ConfigBe yoUrs BUNo ratings yet

- 01-How To Install Java On LinuxDocument3 pages01-How To Install Java On LinuxHeba RefaieNo ratings yet

- Avatar PDFDocument600 pagesAvatar PDFJuan JoseNo ratings yet