Professional Documents

Culture Documents

M.tech Vlsi Syllabus: D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley, 1997

Uploaded by

yupsup90 ratings0% found this document useful (0 votes)

91 views6 pagesM.tech Vlsi Syllabus Analog VLSI Advanced MOS modeling, BJT modeling, CS, CD and CG amplifiers. Current mirrors - active loads. High input impedance current mirrors. BJT gain stages. CMOS operational amplifierscompensation. Comparators. Sample and hold circuits MOS, CMOS and Bi CMOS S / H circuits. Switched capacitor filters, operation, analysis and applications. Nyquist rate.

Original Description:

Original Title

M.docx

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentM.tech Vlsi Syllabus Analog VLSI Advanced MOS modeling, BJT modeling, CS, CD and CG amplifiers. Current mirrors - active loads. High input impedance current mirrors. BJT gain stages. CMOS operational amplifierscompensation. Comparators. Sample and hold circuits MOS, CMOS and Bi CMOS S / H circuits. Switched capacitor filters, operation, analysis and applications. Nyquist rate.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

91 views6 pagesM.tech Vlsi Syllabus: D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley, 1997

Uploaded by

yupsup9M.tech Vlsi Syllabus Analog VLSI Advanced MOS modeling, BJT modeling, CS, CD and CG amplifiers. Current mirrors - active loads. High input impedance current mirrors. BJT gain stages. CMOS operational amplifierscompensation. Comparators. Sample and hold circuits MOS, CMOS and Bi CMOS S / H circuits. Switched capacitor filters, operation, analysis and applications. Nyquist rate.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 6

M.

tech Vlsi Syllabus

Analog VLSI

Advanced MOS modeling, BJT modeling , CS, CD and CG amplifiers. Current mirrors active loads. High

input impedance current mirrors. BJT gain stages.

CMOS operational amplifiers- compensation. Comparators. Sample and hold circuits

MOS, CMOS and Bi CMOS S/H circuits. Switched capacitor filters, operation, analysis and applications.

Nyquist rate. D/A converters. A/D converters.

Over sampling techniques, filter design.

D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley , 1997.

Basics of VLSI

Introduction to CMOS circuits: MOS transistors, CMOS combinational logic gates, multiplexers, latches and

flip-flops. CMOS fabrication and layout. VLSI design flow.

MOS transistor theory: Ideal I-V and C-V characteristics, non ideal I-V effects, DC transfer characteristics.

Switch level RC delay models.

CMOS technologies. Layout design rules. CMOS process enhancement. Technology related issues.

Circuit characterization and performance estimation: Delay estimation. Logical effort and transistor sizing.

Power dissipation. Interconnect design margin. Reliability. Scaling.

Circuit simulation : Device models, Device and circuit characterization. Interconnect simulation.

N.H.E.Weste etal, CMOS VLSI Design (3/e), Pearson, 2005

Modeling and Synthesis with the Verilog HDL

Hardware modeling with the verilog HDL. Encapsulation, modeling primitives, different types of description.

Logic system, data types and operators for modeling in verilog HDL. Verilog Models of propagation delay and

net delay path delays and simulation, inertial delay effects and pulse rejection.

Behavioral descriptions in verilog HDL. Synthesis of combinational logic.

HDL-based synthesis- technology-independent design, styles for synthesis of combinational and sequential

logic, synthesis of finite state machines, synthesis of gated clocks, design partitions and hierarchical structures.

Synthesis of language constructs, nets, register variables, expressions and operators, assignments and

compiler directives. Switch-level models in verilog. Design examples in verilog.

M.D.Ciletti , Modeling, Synthesis and Rapid Prototyping with the Verilog HDL, Prentice Hall, 1999.

M.G.Arnold, Verilog Digital Computer Design, Prentice Hall (PTR), 1999.

S. Palnitkar , Verilog HDL A Guide to Digital Design and Synthesis, Pearson , 2003.

Digital System Design

Programmable logic devices (PLDs). Programmable gate arrays. Xilinx series FPGAs. Altera complex PLDs.

Altera Flux 10K series CPLDs.

FPGA- based system design. FPGA fabrics. Combinational network delay. Power and energy optimization

sequential machine design styles. Rules for clocking. Performance analysis.

Combinational circuit design: circuit families, static CMOS, ratioed circuits. Cascade voltage switch logic,

Dynamic circuits. Pass transistor circuits, Differential circuits.

Sequencing static circuits. Circuit design of latches and flip-flops. Static sequencing element methodology.

Sequencing dynamic circuits. Synchronizers.

Datapath and array subsystems : Addition / Subtraction , Comparators, counters, coding, multiplication and

division. SRAM,DRAM,ROM, serial access memory, context-addressable memory.

N.H.E.Weste etal, CMOS VLSI Design (3/e), Pearson, 2005

Low Power VLSI Circuits

Evolution of CMOS technology. 0.25 m and 0.1 m technologies. Shallow trench

isolation. Lightly-doped drain. Buried channel. BiCMOS and SOI CMOS technologies. Second order effects

and capacitance of MOS devices.

CMOS inverters, static logic circuits of CMOS, pass transistor, BiCMOS, SOI CMOS and low power CMOS

techniques.

Basic concepts of dynamic logic circuits. Various problems associated with dynamic logic circuits. Differential,

BiCMOS and low voltage dynamic logic circuits.

Different types of memory circuits.

Adder circuits. Multipliers, advanced structures. PLA. PLL. Processing unit.

J.B.Kuo & J.H.Lou, Low-voltage CMOS VLSI Circuits, Wiley., 1999.

FPGA - based System Design

Multirate signal processing- Decimation and Interpolation. Spectrum of decimated and interpolated signals,

Polyphase decomposition of FIR filters and its applications to multirate DSP. Sampling rate converters, Sub-

band encoder.

Filter banks-uniform filter bank. direct and DFT approaches. Introduction to ADSL Modem. Discrete multitone

modulation and its realization using DFT. QMF. Computation of DWT using filter banks.

DDFS- ROM LUT approach. Spurious signals, jitter. Computation of special functions using CORDIC. Vector

and rotation mode of CORDIC. CORDIC architectures.

Block diagram of a software radio. Digital downconverters and demodulators Universal modulator and

demodulator using CORDIC. Incoherent demodulation - digital approach for I and Q generation, special

sampling schemes. CIC filters. Residue number system and high speed filters using RNS. Down conversion

using discrete Hilbert transform. Undersampling receivers, Coherent demodulation schemes.

Speech coding- speech apparatus. Models of vocal tract. Speech coding using linear prediction. CELP coder.

An overview of waveform coding. Vocoders. Vocoder attributes. Block diagrams of encoders and decoders of

G723.1, G726, G727, G728 and G729.

S. K. Mitra, Digital Signal processing, McGrawHill, 1998

J. H. Reed, Software Radio, Pearson, 2002.

U. Meyer Baese , Digital Signal Processing with FPGAs, Springer, 2001

VHDL Analysis and Design of Digital Systems

An overview of design procedures for system design using CAD tools. Design verification tools. Examples

using commercial PC based VLSI CAD tools. Design methodology based on VHDL. Basic concepts and

structural descriptions in VHDL.

Characterizing hardware languages, objects and classes, signal assignments, concurrent and sequential

assignments. Structural specification of hardware.

Design organization, parameterization and high level utilities, definition and usage of subprograms, packaging

parts and utilities, design parameterization, design configuration, design libraries. Utilities for high-level

descriptions.

Data flow and behavioral description in VHDL- multiplexing and data selection, state machine description, open

collector gates, three state bussing, general dataflow circuit, updating basic utilities. Behavioral description of

hardware.

CPU modelling for discrete design- Parwan CPU, behavioral description, bussing structure, data flow, test

bench, A more realistic Parwan. Interface design and modeling, VHDL as a modeling language.

Z.Navabi, VHDL Analysis and Modeling of Digital Systems, (2/e), McGraw Hill, 1998.

Perry, VHDL (3/e), McGraw Hill.

VLSI System Testing

Faults and their manifestations. Fault models. Combinational logic and fault simulation.

Test generation basics. Structural and non-structural test generation techniques. Combinational ATPG. Current

sensing based testing.

Classification of sequential ATPG methods. Fault collapsing and simulation Test generation for synchronous

and asynchronous circuits. Test compaction.

Universal test. Pseudo-exhaustive and iterative logic array testing. Clocking schemes for delay fault testing.

Testability classifications for path delay faults. Test generation and fault simulation for path and gate delay

faults.

Design for testability: Scan design, use of scan chains, boundary scan. Built-in self test. Synthesis for

testability.

N. Jha & S.D. Gupta, Testing of Digital Systems, Cambridge,2003.

M. Abramovici etal, Digital System Testing and Testable Design, Computer Science

Press,1990

Electronic Design Automation Tools

An overview of OS commands. System settings and configuration. Introduction to Unix commands. Writing

Shell scripts. VLSI design automation tools.An overview of the features of practical CAD tools. Modelsim,

Leonardo spectrum, ISE 8.1i, Quartus II, VLSI backend tools.

Synthesis and simulation using HDLs-Logic synthesis using verilog and VHDL. Memory and FSM synthesis.

Performance driven synthesis, Simulation- Types of simulation. Static timing analysis. Formal verification.

Switch level and transistor level simulation.

Circuit simulation using Spice - circuit description. AC, DC and transient analysis. Advanced spice commands

and analysis. Models for diodes, transistors and opamp. Digital building blocks. A/D, D/A and sample and hold

circuits. Design and analysis of mixed signal circuits.

Mixed signal circuit modeling and analysis using VHDL AMS,

System design using systemC- SystemC models of computation. Classical hardware modeling in system C.

Functional modeling. Parametrized modules and channels. Test benches. Tracing and debugging.

M.J.S.Smith, Application Specific Integrated Circuits,Pearson,2002

M.H.Rashid, Spice for Circuits and Electronics using Pspice. (2/e), PHI.

T. Grdtker et al , System Design with SystemC, Kluwer, 2004.

P.J. Ashenden et al , The System Designers Guide to VHDL-AMS, Elsevier, 2005

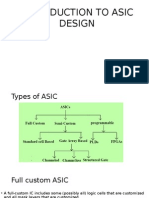

Designing with ASICs

Types of ASICs. ASIC design flow. Programmable ASICs. Antifuse, SRAM, EPROM, EEPROM based ASICs.

Programmable ASIC logic cells and I/O cells. Programmable interconnects.

An overview of advanced FPGAs and programmable SOCs : Architecture and configuration of Spartan II and

Virtex II FPGAs . Apex and Cyclone FPGAs. Virtex II PRO kits and Nios kits. OMAP. ASIC physical design

issues. system partitioning, interconnect delay models and measurement of delay.

ASIC floor planning, placement and routing.

Design issues in SOC. Design methodologies. Processes and flows. Embedded software development for

SOC. Techniques for SOC testing. Configurable SOC. Hardware/software codesign.

High performance algorithms for ASICS/ SOCS. SOC case studies- DAA and computation of FFT and DCT.

High performance filters using delta-sigma modulators. Case Studies: Digital camera, Bluetooth radio/modem,

SDRAM and USB controllers.

M.J.S. Smith : Application Specific Integrated Circuits,,Pearson,2003.

VLSI Digital Signal Processing Systems

Transformations for retiming. Folding and unfolding DSP programs.

Bit level arithmetic structures- parallel multipliers, interleaved floor plan and bit plan based digital filters. Bit

serial multipliers. Bit serial filter design and implementation . Canonic signed digit arithmetic, Distributed

arithmetic.

Redundant arithmetic, redundant number representations , carry free radix 2 addition and subtraction . Hybrid

radix 4 addition. Radix 2 hybrid redundant multiplication architectures , data format conversion. Redundant to

nonredundant converter. Numerical strength reduction.

Synchronous pipelining and clocking styles, clock skew and clock distribution in bit level pipelined VLSI

designs. Wave pipelining, constraint space diagram and degree of wave pipelining. Implementation of wave-

pipelined systems. Asynchronous pipelining.

Scaling versus power consumption. Power analysis, power reduction techniques, power estimation techniques.

Low power IIR filter design .Low power CMOS lattice IIR filter.

K.K. Parhi : VLSI Digital Signal Processing systems, John Wiley, 1999.

Digital Signal Processing Structures for VLSI

An overview of DSP concepts-Linear system theory, DFT, FFT, realization of digital filters. Typical DSP

algorithms, DSP applications. Data flow graph representation of DSP algorithm.

Loop bound and iteration bound Retiming and its applications.

Algorithms for fast convolution. Algorithmic strength reduction in filters and transforms. DCT and inverse DCT.

Parallel FIR filters. Pipelining of FIR filters. Parallel processing. Pipelining and parallel processing for low

power.

Pipeline interleaving in digital filters. Pipelining and parallel processing for IIR filters.Low power IIR filter design

using pipelining and parallel processing, Pipelined adaptive digital filters.

Round off noise and its computation. State variable description of digital filters, Round off noise computation

using state variable description. Scaling using slow-down, retiming and pipelining.

K.K.Parhi, VLSI Digital Signal Processing Systems, John-Wiley, 1999.

Optimization Techniques

Linear programming formulation Graphical and simplex methods Big-M method Two phase method

Dual simplex method Primal Dual problems.

Unconstrained one dimensional optimization techniques - Necessary and sufficient conditions Unrestricted

search method - Fibonacci and Golden section method Quadratic interpolation, cubic interpolation and direct

root methods.

Unconstrained n dimensional optimization techniques direct search methods Random search methods

Pattern search methods - Rosenbrocks method - Descent methods -Steepest descent, conjugate gradient,

Quasi - Newton methods.

Constrained optimization Techniques - Necessary and sufficient conditions Equality and inequality

constraints - Kuhn-Tucker conditions - Gradient projection method-cutting plane method- penalty function

method.

Dynamic programming Principle of optimality recursive equation approach application to shortest route,

cargo-loading, allocation and production schedule problems.

FOX, R. L., Optimization methods for Engineering Design, Addition Wesley.

RAO S. S., Optimization :Theory and Application, Wiley Eastern Press..

TAHA, H.A., Operations Research- An Introduction, Prentice Hall of India.

You might also like

- DO254 Project FlowDocument4 pagesDO254 Project Flowkundu.banhimitraNo ratings yet

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsFrom EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsRating: 4 out of 5 stars4/5 (3)

- 1450401864Document255 pages1450401864Henry Lois Davila AndradeNo ratings yet

- Analog IC Layout Services 1v2Document14 pagesAnalog IC Layout Services 1v2KumarNo ratings yet

- On-Chip Communication Architectures: System on Chip InterconnectFrom EverandOn-Chip Communication Architectures: System on Chip InterconnectNo ratings yet

- Resource Efficient LDPC Decoders: From Algorithms to Hardware ArchitecturesFrom EverandResource Efficient LDPC Decoders: From Algorithms to Hardware ArchitecturesNo ratings yet

- RF Analog Impairments Modeling for Communication Systems Simulation: Application to OFDM-based TransceiversFrom EverandRF Analog Impairments Modeling for Communication Systems Simulation: Application to OFDM-based TransceiversNo ratings yet

- ASIC-System On Chip-VLSI Design Backend (Physical Design) Interview Questions and AnswersDocument7 pagesASIC-System On Chip-VLSI Design Backend (Physical Design) Interview Questions and AnswersRohith RajNo ratings yet

- M.tech Vlsi Syllabus: D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley, 1997Document5 pagesM.tech Vlsi Syllabus: D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley, 1997Garth RodriguezNo ratings yet

- Rajasthan Technical University: Syllabus: M.Tech (Vlsi Design) 1Mvl1 Advanced MathematicsDocument6 pagesRajasthan Technical University: Syllabus: M.Tech (Vlsi Design) 1Mvl1 Advanced Mathematicskeerti06No ratings yet

- VLSI DesignDocument11 pagesVLSI DesignKennyNo ratings yet

- Vlsi Mtech 1st - Year - Jntu Kakinada SyllabusDocument8 pagesVlsi Mtech 1st - Year - Jntu Kakinada Syllabustele203No ratings yet

- Common Recruitment Examination June 2013: DeityDocument10 pagesCommon Recruitment Examination June 2013: DeitydannycbsNo ratings yet

- VLSI Design 4 Course InfoDocument4 pagesVLSI Design 4 Course InfoSwati HayaranNo ratings yet

- Mtech VlsiDocument15 pagesMtech VlsiMukesh MaheshwariNo ratings yet

- SyllDocument16 pagesSyllraj8bhondNo ratings yet

- EC657 Digital System Design and EC661 Digital Signal Processing StructuresDocument2 pagesEC657 Digital System Design and EC661 Digital Signal Processing StructuresAvinash KumarNo ratings yet

- W.E.F. 2009-10 Jawaharlal Nehru Technological University: Kakinada KAKINADA 533 003Document17 pagesW.E.F. 2009-10 Jawaharlal Nehru Technological University: Kakinada KAKINADA 533 003hvrkNo ratings yet

- TEC - Wireless Communication and NetworksDocument4 pagesTEC - Wireless Communication and NetworksAbhishek AntimNo ratings yet

- JNTU Kakinada ECE Course StructureDocument8 pagesJNTU Kakinada ECE Course StructureJagan Kumar0% (1)

- Applied Mathematics and Digital Signal ProcessingDocument5 pagesApplied Mathematics and Digital Signal ProcessingvigneshkumarcNo ratings yet

- (13ec604) Vlsi Design S: Ds Ds M DsDocument1 page(13ec604) Vlsi Design S: Ds Ds M DsSai Jaswanth SinghNo ratings yet

- Btech New SyllabusDocument8 pagesBtech New SyllabusDrBhoopal RaoNo ratings yet

- Revised Syllabus MicroelectronicsDocument19 pagesRevised Syllabus MicroelectronicsBaluvu JagadishNo ratings yet

- Vlsi Design PDFDocument22 pagesVlsi Design PDFKishore KumarNo ratings yet

- Btech-III Year Electronics Engineering 170715Document22 pagesBtech-III Year Electronics Engineering 170715Sandeep Kr AryaNo ratings yet

- Vlsi Mtech Jntu Kakinada SyllabusDocument11 pagesVlsi Mtech Jntu Kakinada Syllabusaditya414No ratings yet

- Vlsi DesignDocument12 pagesVlsi DesignTanveer AhmedNo ratings yet

- M.E. Microelectronics Course StructureDocument19 pagesM.E. Microelectronics Course StructureSneha NargundkarNo ratings yet

- CDAD Course Syllabus and Programming ConceptsDocument6 pagesCDAD Course Syllabus and Programming ConceptsTapas SatpathyNo ratings yet

- Vlsi System DesignDocument12 pagesVlsi System DesignMahender GoudNo ratings yet

- ISRO SCIENTISTS/ENGINEERS (SC) SYLLABUS OVERVIEWDocument5 pagesISRO SCIENTISTS/ENGINEERS (SC) SYLLABUS OVERVIEWVIVEK SINGHNo ratings yet

- MTech VLSI Design 1st Sem SyllabusDocument5 pagesMTech VLSI Design 1st Sem SyllabusPrakash Sinha100% (1)

- GTU PHD Core Syllabus CMOS Analog Circuit DesignDocument1 pageGTU PHD Core Syllabus CMOS Analog Circuit Designsubhash_tuhhNo ratings yet

- 8th Sem SallybusDocument4 pages8th Sem Sallybusgaurav_jindal87No ratings yet

- Department of Electrical EngineeringDocument14 pagesDepartment of Electrical EngineeringeserjeeNo ratings yet

- Es IiDocument16 pagesEs IiSivasankar YalavarthyNo ratings yet

- UEC2302 Digital System Design Course OverviewDocument10 pagesUEC2302 Digital System Design Course OverviewAmoga LekshmiNo ratings yet

- PHD Syllabus 09102023Document22 pagesPHD Syllabus 09102023Abhishek SasmalNo ratings yet

- Regulation - 2009: Affiliated Institutions Anna University, ChennaiDocument27 pagesRegulation - 2009: Affiliated Institutions Anna University, ChennaiYogeswaran SundarrajNo ratings yet

- Ae IIDocument27 pagesAe IIAnbu SelvanNo ratings yet

- Vlsi Vlsid Vlsisd Vlsi Me Ece PDFDocument18 pagesVlsi Vlsid Vlsisd Vlsi Me Ece PDFramanaidu1No ratings yet

- RGPV Syllabus Cbgs Ec 3 Sem All SubjectsDocument8 pagesRGPV Syllabus Cbgs Ec 3 Sem All SubjectsAyushNo ratings yet

- Proposed - BE E & TC 2019 - VLSI SyllabusDocument3 pagesProposed - BE E & TC 2019 - VLSI SyllabusRavindra DabhadeNo ratings yet

- Digital Communication (3 - 0 - 0) 3: ReferencesDocument4 pagesDigital Communication (3 - 0 - 0) 3: ReferencesPraveen IgnatiusNo ratings yet

- Wireless Communication Systems & NetworksDocument4 pagesWireless Communication Systems & Networkstornado2307No ratings yet

- M.tech2nd Sem SyllabusDocument8 pagesM.tech2nd Sem Syllabusirfan449No ratings yet

- M.E VLSI SyllabusDocument4 pagesM.E VLSI SyllabussayaryspielNo ratings yet

- Vlsi Logical DesignDocument4 pagesVlsi Logical DesignMahesh KanikeNo ratings yet

- Vlsi Mtech Jntu Kakinada II Sem SyllabusDocument16 pagesVlsi Mtech Jntu Kakinada II Sem Syllabusrv prasad50% (2)

- Syllabus For RTU-DAT Paper-IDocument28 pagesSyllabus For RTU-DAT Paper-Imanish_chaturvedi_60% (1)

- VLSI Syllabus M.tech BurlaDocument27 pagesVLSI Syllabus M.tech BurlaBiswajit BeheraNo ratings yet

- Vlsi Course Final - LOGIC DESIGNDocument3 pagesVlsi Course Final - LOGIC DESIGNMahesh KanikeNo ratings yet

- ME - Detailed Syllabus - 2016-17 OnwardsDocument24 pagesME - Detailed Syllabus - 2016-17 OnwardsfilmfilmfNo ratings yet

- EceDocument2 pagesEceDivya SeepanaNo ratings yet

- Millimeter-Wave Digitally Intensive Frequency Generation in CMOSFrom EverandMillimeter-Wave Digitally Intensive Frequency Generation in CMOSNo ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Embedded System Interfacing: Design for the Internet-of-Things (IoT) and Cyber-Physical Systems (CPS)From EverandEmbedded System Interfacing: Design for the Internet-of-Things (IoT) and Cyber-Physical Systems (CPS)No ratings yet

- Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLFrom EverandIntroduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLNo ratings yet

- Complete ASIC Design Flow 2021 - VLSI UNIVERSEDocument4 pagesComplete ASIC Design Flow 2021 - VLSI UNIVERSENaganithesh GhattamaneniNo ratings yet

- Water Pump Control PDFDocument81 pagesWater Pump Control PDFabubeker muhamedNo ratings yet

- Embedded DramDocument23 pagesEmbedded DramAbhi MaheshwariNo ratings yet

- Mipsology Aws f1Document10 pagesMipsology Aws f1hiperboreoatlantecNo ratings yet

- Quiz-2 Name: - Date: - Roll NumberDocument2 pagesQuiz-2 Name: - Date: - Roll NumberSyed Hasan RizviNo ratings yet

- Aruba 3810M Switch Series Technical Product GuideDocument21 pagesAruba 3810M Switch Series Technical Product GuideBatkhishig Tumen-OidovNo ratings yet

- Erts Chapter PPT by Vahid.Document39 pagesErts Chapter PPT by Vahid.Boppudi Sasi BinduNo ratings yet

- Fundamental of Embedded System Design: Unit IDocument12 pagesFundamental of Embedded System Design: Unit Ikaushalexp44No ratings yet

- Haps 80 BrochureDocument14 pagesHaps 80 BrochurevivekvlsiNo ratings yet

- Advanced ASIC Chip SynthesisDocument1 pageAdvanced ASIC Chip SynthesispaulpuscasuNo ratings yet

- Vlsi 2018 19 PDFDocument44 pagesVlsi 2018 19 PDFUmang yadavNo ratings yet

- Different Types of ASICDocument21 pagesDifferent Types of ASICParth Shah100% (1)

- Thesis ReportDocument60 pagesThesis ReportKarthiga MuruganNo ratings yet

- Gate Array Based DesignDocument6 pagesGate Array Based DesignSubir MaityNo ratings yet

- 02 Introduction To VLSI and ASIC DesignDocument23 pages02 Introduction To VLSI and ASIC DesignSiva Kumar T SNo ratings yet

- Lec 1Document45 pagesLec 1Abdullah MadniNo ratings yet

- Complex Simpler: Synopsys Professional Services, Smartech GroupDocument3 pagesComplex Simpler: Synopsys Professional Services, Smartech GroupSamNo ratings yet

- Graduate Report TejasDocument150 pagesGraduate Report TejasraghudatheshgpNo ratings yet

- Igloo Nano DsDocument148 pagesIgloo Nano Dssupertester12345No ratings yet

- Vlsi BrochureDocument12 pagesVlsi BrochureManas GhatasutraNo ratings yet

- Improving Embedded Deep Learning Object Detection by Integrating Infrared CameraDocument98 pagesImproving Embedded Deep Learning Object Detection by Integrating Infrared CameraArnaldo César dos SantosNo ratings yet

- Design and VLSI Implementation of High-Performance Face-Detection Engine For Mobile ApplicationsDocument2 pagesDesign and VLSI Implementation of High-Performance Face-Detection Engine For Mobile ApplicationsArjun0607No ratings yet

- FPGA Vs Micro ControlDocument11 pagesFPGA Vs Micro ControlsenthilvlNo ratings yet

- Design and Implementation of Traffic Lights Controller Using FpgaDocument29 pagesDesign and Implementation of Traffic Lights Controller Using FpgaNâséébûllāh BugtiNo ratings yet

- Verification of USB Using UVM MethodologyDocument14 pagesVerification of USB Using UVM MethodologySankeerth MamidalaNo ratings yet

- EdaDocument4 pagesEdaJyotirmoy GuhaNo ratings yet