Professional Documents

Culture Documents

HART Modem: General Description Features

Uploaded by

vigneshwaranj0 ratings0% found this document useful (0 votes)

51 views7 pagesHART protocol

Original Title

DS8500

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentHART protocol

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

51 views7 pagesHART Modem: General Description Features

Uploaded by

vigneshwaranjHART protocol

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 7

AVAILABLE

EVALUATION KIT AVAILABLE

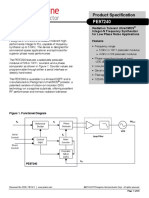

Functional Diagrams

Pin Configurations appear at end of data sheet.

Functional Diagrams continued at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

For pricing, delivery, and ordering information, please contact Maxim Direct

at 1-888-629-4642, or visit Maxims website at www.maximintegrated.com.

General Description

The DS8500 is a single-chip modem with Highway

Addressable Remote Transducer (HART) capabilities

and satisfies the HART physical layer requirements.

The device integrates the modulation and demodulation

of the 1200Hz/2200Hz FSK signal, has very low power

consumption, and needs only a few external compo-

nents due to the integrated digital signal processing.

The input signal is sampled by an analog-to-digital con-

verter (ADC), followed by a digital filter/demodulator.

This architecture ensures reliable signal detection in

noisy environments. The output digital-to-analog con-

verter (DAC) generates a sine wave and provides a

clean signal with phase-continuous switching between

1200Hz and 2200Hz. Low power is achieved by dis-

abling the receive circuits during transmit and vice

versa. The DS8500 is ideal for low-power process con-

trol transmitters.

Applications

420mA Loop-Powered Transmitters for

Temperature, Pressure, Flow, and Level

Measurement

HART Multiplexers

HART Modem Interface Connectivity

Features

Single-Chip, Half-Duplex, 1200bps FSK

Modulation and Demodulation

Digital Signal Processing Provides Reliable Input

Signal Detection in Noisy Conditions

Sinusoidal Output Signal with Lowest Harmonic

Distortion

Few External Components Enable a Space-Saving

Solution

Standard Component 3.6864MHz Crystal

Complies to HART Physical Layer Requirements

2.7V to 3.6V Operating Voltage

285A (max) Current Consumption

Space-Saving, 5mm x 5mm x 0.8mm, 20-Pin TQFN

Package

HART Modem

THIN QFN

(5mm 5mm)

TOP VIEW

19

20

18

17

7

6

8

D

V

D

D

R

S

T

O

C

D

9

D

V

D

D

F

S

K

_

I

N

F

S

K

_

O

U

T

A

V

D

D

A

G

N

D

1 2

DGND

4 5

15 14 12 11

D_OUT

D_IN

DGND

XTAL2

XTAL1

RTS

D

G

N

D

R

E

F

3

13

DGND

16 10 XCEN DGND

DS8500

+

*EP

*EXPOSED PAD.

Pin Configuration

Ordering Information

PART TEMP RANGE PIN-PACKAGE

DS8500-JND+ -40C to +85C 20 TQFN-EP*

+Denotes a lead(Pb)-free/RoHS-compliant package.

*EP = Exposed pad.

Rev 1; 2/09

DS8500

HART Modem

ABSOLUTE MAXIMUM RATINGS

RECOMMENDED DC OPERATING CONDITIONS

(V

DVDD

= V

AVDD

= 2.7V to 3.6V, T

A

= -40C to +85C.) (Note 1)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Note 1: Specifications to -40C are guaranteed by design and are not production tested.

Note 2: Active currents are measured when the device is driven by an external clock XCEN = 1 condition.

Note 3: Guaranteed by design and not production tested.

Note 4: Accuracy is guaranteed based on the external crystal or clock provided.

Voltage Range on All Pins (including AVDD,

DVDD) Relative to Ground .................................-0.5V to +3.6V

Voltage Range on Any Pin Relative to

Ground Except AVDD, DVDD.............-0.5V to (V

DVDD

+ 0.5V)

Operating Temperature Range ...........................-40C to +85C

Storage Temperature Range.............................-65C to +150C

Soldering Temperature...........................Refer to the IPC/JEDEC

J-STD-020 Specification.

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Digital Supply Voltage V

DVDD

2.7 3.6 V

Analog Supply Voltage V

AVDD

V

AVDD

= V

DVDD

2.7 3.6 V

Ground GND AGND = DGND 0 0 V

Digital Power-Fail Reset Voltage V

RST

Monitors V

DVDD

2.59 2.64 2.69 V

Active Current I

DD

V

AVDD

= V

DVDD

= 2.7V (Note 2) 285 A

Input Low Voltage V

IL

DGND

0.30 x

V

DVDD

V

Input High Voltage V

IL

0.75 x

V

DVDD

V

DVDD

V

Output Low Voltage V

OL

I

OL

= 4mA DGND 0.4 V

Output High Voltage V

OH

I

OH

= -4mA

0.8 x

V

DVDD

V

I/O Pin Capacitance C

IO

Guaranteed by design (Note 3) 15 pF

RST Pullup Resistance R

RST

19 45 k

Input Leakage Current XTAL,

RST

I

ILRX

-30 +30 A

Input Leakage Current All Other

Pins

I

IL

-2 +2 A

Input Low Current for RST I

IL1

V

IN

= 0.4V 170 A

CLOCK SOURCE

External Clock Frequency f

HFIN

-1% 3.6864 +1% MHz

VOLTAGE REFERENCE

Internal Reference Voltage V

REF

1.23 V

FSK INPUT

Input Voltage Range at FSK_IN 0 V

REF

V

FSK OUTPUT

Output Voltage at FSK_OUT V

OUT

AC-coupled max 30k load 400 500 600 mV

P-P

For a mark -1% 1200 +1%

Frequency of FSK_OUT (Note 4)

For a space -1% 2200 +1%

Hz

DS8500

2 Maxim Integrated

HART Modem

Pin Description

PIN NAME FUNCTION

1, 2 DVDD Digital Supply Voltage

3, 9, 16,

17, 18

DGND Digital Ground

4 RST

Active-Low Reset, Digital Input/Output. This pin includes an internal pullup resistor and is driven low

as an output when an internal reset condition occurs.

5 OCD

Carrier Detect, Digital Output. A logic-high indicates a valid carrier detection on FSK_IN.

OCD = 1 when FSK_IN amplitude is greater than 120mV

P-P

.

OCD = 0 when FSK_IN amplitude is less than 80mV

P-P

.

6 RTS

Request to Send, Digital Input. When set high, the device is put into the demodulator mode. A logic-low

puts the device into modulator mode.

7 XTAL1 Crystal Pin or Input for External Clock at 3.6864MHz

8 XTAL2 Crystal Pin or Output of the Crystal Amplifier

10 XCEN

External Clock Enable, Digital Input. When set high, this pin allows the user to drive an external clock

signal through XTAL1. When in this mode, XTAL2 should be left unconnected. An external crystal must

be connected between XTAL1 and XTAL2 when set low.

11 AVDD Analog Supply Voltage

12 FSK_OUT

FSK Out, Analog Output. Output of the modulator. Provides a phase-continuous, FSK-modulated output

signal (1200Hz and 2200Hz output frequencies) to the 420mA current loop interface circuit.

13 REF

Reference, Analog Output. The internal voltage reference is provided as output. This pin must be

connected to a 0.1F capacitor.

14 FSK_IN

FSK In, Analog Input. Input for the FSK-modulated HART receive signal from the 420mA current loop

interface circuit.

15 AGND Analog Ground

19 D_OUT Digital Data Out, Digital Output. Output from the demodulator.

20 D_IN Digital Data In, Digital Input. Input to the modulator.

EP Exposed Pad. Should be connected to ground (DGND, AGND).

Block Diagram

DS8500

CRYSTAL

OSCILLATOR

CLOCK

GENERATOR

XTAL1

RST AVDD AGND DGND DVDD

POWER

MONITOR

XTAL2

Rx

DEMODULATOR

DIGITAL

FILTER

SAMPLE/HOLD

ADC

OCD

D_OUT

Tx

MODULATOR

RTS

D_IN

XCEN

FSK_IN

REF

DAC FSK_OUT

V

REF

1.23V

DS8500

Maxim Integrated 3

Introduction to HART

HART is a backward-compatible enhancement to exist-

ing 420mA instrumentation networks that allows two-

way, hal f-dupl ex, di gi tal communi cati on wi th a

microcontroller-based field device. The digital signal is

encoded on top of the existing instrumentation signal.

Communication is accomplished through a series of

commands and responses dependent on the specific

protocol and network topology. The DS8500 does not

implement any portion of the communication protocol; it

only handles the modulation and demodulation of the

encoded information. Digital data is encoded using fre-

quency-shift keying (FSK), which is illustrated in Figure

1. A 1 is identified as a mark symbol and is represent-

ed with a center frequency of 1.2kHz. A 0 is identified

as a space symbol and is represented with a center fre-

quency of 2.2kHz. This allows a throughput of 1.2kbps,

with each symbol occupying an 833s slot.

Functional Description

The DS8500 modem chip consists of a demodulator, car-

rier detect, digital filter, ADC for input signal conversion, a

modulator and DAC for output signal generation, and

receive and transmit state machine blocks to perform the

HART communication. The Block Diagram illustrates

the interface between various blocks of circuitry.

The input HART signals noise interference is attenuat-

ed by a one-pole highpass filter that is external to the

chip; the attenuated signal is digitized by the ADC and

filtered by the receive state machine. The transmit state

machine modulates the input to the HART-compliant

signal with the help of the modulator and the DAC.

Modulator

The modulator performs the FSK modulation of the digi-

tal data at the D_IN input. The FSK-modulated sinu-

soidal signal is present at the FSK_OUT output as

illustrated in Figure 1. The modulator is enabled by RTS

being a logic-low. The modulation is done between

1200Hz (mark) or 2200Hz (space) depending on the

logic level of the input signal. The modulator preserves a

continuous phase when switching between frequencies

to minimize the bandwidth of the transmitted signal.

Figure 2 illustrates an example waveform of the DS8500

in modulate mode. The data to be modulated is pre-

sented in a UART format (start, 8 data bits, parity, stop

bit) at D_IN. FSK_OUT shows the modulated output.

Demodulator

The demodulator accepts an FSK signal at the FSK_IN

input and reproduces the original modulating signal at

the D_OUT output. The HART signal should be present-

ed as an 11-bit UART character with a start, data, pari-

ty, and stop bi ts for proper operati on of the

demodulator block. The nominal bit rate of the D_OUT

signal is 1200 bits per second. A simple RC filter is suf-

ficient for anti-aliasing. Figure 3 illustrates an example

waveform of the DS8500 in demodulate mode.

Applications Information

Figure 4 shows the typical application circuit. As the

DS8500 integrates a digital filter, only a simple passive

RC filter is required in front of the ADC. R3 and C3

implement a lowpass filter with a 10kHz cutoff frequen-

cy; C2 and R2/R1 implement a highpass filter with a

480Hz cutoff frequency. The resistor-divider formed by

R1 and R2 provides an input bias voltage of V

REF

/2 to

the ADC input (R1 = R2).

The output DAC provides a sine-wave signal, and C4

provi des the AC-coupl ed si gnal output from the

DS8500. The typical value of C4 can be anything

greater than 20nF based on the application.

Technical Support

For technical support, go to http://support.maxim-

ic.com/micro.

HART Modem

1.2kHz MARK

"1"

2.2kHz SPACE

"0"

V

T

Figure 1. HART FSK Signal

DS8500

4 Maxim Integrated

HART Modem

D_IN

FSK_OUT

START

PARITY

STOP

8-BIT DATA

1200bps/833s

Figure 2. Actual DS8500 Modulator Waveform

D_OUT

FSK_IN

START

STOP

8-BIT DATA

1200bps/833s

ONE UART CHARACTER (START, 8 DATA BITS, PARITY, STOP)

PARITY

Figure 3. Actual DS8500 Demodulator Waveform

DS8500

Maxim Integrated 5

HART Modem

DS8500

CRYSTAL

OSCILLATOR

CLOCK

GENERATOR

XTAL1

RST

AVDD

POWER SUPPLY

2.7V TO 3.6V

AGND DGND DVDD

POWER

MONITOR

XTAL2

Rx

DEMODULATOR

DIGITAL

FILTER

SAMPLE/HOLD

ADC

OCD

D_OUT

Tx

MODULATOR

RTS

D_IN

XCEN

MICROCONTROLLER

FSK_IN

REF

DAC

FSK_OUT

V

REF

1.23V

3.6864MHz

3.6864MHz

CRYSTAL

R1

R2

C1

C3

C2

C4

R3

HART IN

420mA

DAC OUTPUT

HART AND

420mA

OUT

Figure 4. Typical Application Circuit

PACKAGE TYPE PACKAGE CODE DOCUMENT NO.

20 TQFN T2055+3 21-0140

Package Information

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

DS8500

6 Maxim Integrated

HART Modem

Revision History

REVISION

NUMBER

REVISION

DATE

DESCRIPTION

PAGES

CHANGED

0 10/08 Initial release.

In the Electrical Characteristics table, changed the Frequency of FSK_OUT

parameter units from kHz to Hz.

2

1 2/09

Added the EP description to the Pin Description table. 3

DS8500

7 Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied.

Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical

Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

2009 Maxim Integrated The Maxim logo and Maxim Integrated are trademarks of Maxim Integrated Products, Inc.

You might also like

- DS8500Document7 pagesDS8500abdulmajeed_cetNo ratings yet

- WS2811 PDFDocument7 pagesWS2811 PDFManuel SierraNo ratings yet

- Max 2981Document13 pagesMax 2981Jamila RobinsonNo ratings yet

- XGSW XX12 40D FDocument9 pagesXGSW XX12 40D FnelusabieNo ratings yet

- Ads 7870Document43 pagesAds 7870Moorthy VenkatachalamNo ratings yet

- DRF4432F20Document6 pagesDRF4432F20Ilie CristianNo ratings yet

- 14-Bit, 160 Msps 2 Interpolating Dual Txdac+: Ⴛ/4Ⴛ/8Ⴛ D/A ConverterDocument52 pages14-Bit, 160 Msps 2 Interpolating Dual Txdac+: Ⴛ/4Ⴛ/8Ⴛ D/A Convertercbernal73No ratings yet

- MAX5556 Stereo Audio 16b DACDocument19 pagesMAX5556 Stereo Audio 16b DACJennifer NealNo ratings yet

- XGXP 1396 10dDocument7 pagesXGXP 1396 10dPeter AdelNo ratings yet

- DTMF Receiver HM 9270C/DDocument10 pagesDTMF Receiver HM 9270C/DCarlos Javier Solano GuzmánNo ratings yet

- Ad 9863Document40 pagesAd 9863AkashKosgiNo ratings yet

- Tda 10021 DatasheetDocument17 pagesTda 10021 DatasheetWilly DacoNo ratings yet

- 1.25Gbps SFP Optical Transceiver, 80km Reach: SfpgezDocument8 pages1.25Gbps SFP Optical Transceiver, 80km Reach: Sfpgeztv_romeoNo ratings yet

- 1.25Gbps SFP Bi-Directional Transceiver Provides 20km ReachDocument9 pages1.25Gbps SFP Bi-Directional Transceiver Provides 20km Reachtv_romeoNo ratings yet

- 1177 Sigma Delta DACDocument4 pages1177 Sigma Delta DACZoranNo ratings yet

- AD831-MIXER 200-500MHzDocument17 pagesAD831-MIXER 200-500MHzChelaru CosminNo ratings yet

- Sfpgel: 1.25Gbps SFP Optical Transceiver, 20km ReachDocument8 pagesSfpgel: 1.25Gbps SFP Optical Transceiver, 20km Reachtv_romeoNo ratings yet

- 2085 Hart MoDem DatasheetDocument8 pages2085 Hart MoDem DatasheetHPC HartNo ratings yet

- C) Descripción GSM SonyDocument4 pagesC) Descripción GSM SonyMiguel Angel Roman UrrietaNo ratings yet

- MC 145436 APDocument8 pagesMC 145436 APRobert SepulvedaNo ratings yet

- mp3 Decoder AT83SND2CMP3Document98 pagesmp3 Decoder AT83SND2CMP3Venkatesh KamathNo ratings yet

- 101-0016 InLink TC Data SheetDocument4 pages101-0016 InLink TC Data SheetSisEleN Neuquen ArgentinaNo ratings yet

- 1.25Gbps SFP Bi-Directional Transceiver, 20km Reach: GlcbxuDocument9 pages1.25Gbps SFP Bi-Directional Transceiver, 20km Reach: Glcbxutv_romeoNo ratings yet

- Adc11Dl066 Dual 11-Bit, 66 MSPS, 450 MHZ Input Bandwidth A/D Converter W/Internal ReferenceDocument24 pagesAdc11Dl066 Dual 11-Bit, 66 MSPS, 450 MHZ Input Bandwidth A/D Converter W/Internal ReferenceVănThịnhNo ratings yet

- Pe 97240 DsDocument21 pagesPe 97240 Dskhanafzaal2576No ratings yet

- IN44780U Dot Matrix Liquid Crystal Display Controller & DriverDocument10 pagesIN44780U Dot Matrix Liquid Crystal Display Controller & DriverSilviu AdgjNo ratings yet

- 2.488Gbps SFP Optical Transceiver, 2km Reach: DS-SFP-FC-2G-LWDocument8 pages2.488Gbps SFP Optical Transceiver, 2km Reach: DS-SFP-FC-2G-LWtv_romeoNo ratings yet

- WM8524 - Audio DacDocument25 pagesWM8524 - Audio DacJennifer NealNo ratings yet

- Circuit Schematic For Wireless Headphone With MicDocument48 pagesCircuit Schematic For Wireless Headphone With MicPooja TomarNo ratings yet

- TLV 320 Adc Stereo Evaluation Audio AmplifierDocument85 pagesTLV 320 Adc Stereo Evaluation Audio AmplifierJay VoraNo ratings yet

- Tda7317 EcualizadorDocument13 pagesTda7317 EcualizadorRafael AlcazarNo ratings yet

- Accurate, Fast Settling Analog Voltages From Digital PWM SignalsDocument2 pagesAccurate, Fast Settling Analog Voltages From Digital PWM SignalsAdhi Ne CutcakrowoNo ratings yet

- 16-Bit, Serial Input Multiplying Digital-to-Analog ConverterDocument16 pages16-Bit, Serial Input Multiplying Digital-to-Analog ConverternhbrNo ratings yet

- 4MSPS, 24-Bit Analog-to-Digital Converter: Features DescriptionDocument37 pages4MSPS, 24-Bit Analog-to-Digital Converter: Features DescriptionEric ChenNo ratings yet

- Stereo, Single-Supply 18-Bit Integrated DAC AD1859: SD Modulator With Triangular PDF DitherDocument16 pagesStereo, Single-Supply 18-Bit Integrated DAC AD1859: SD Modulator With Triangular PDF DitherSubir MaityNo ratings yet

- Technical Information: Stereo 20W (4 Digital Power Processing Technology TA2020-020Document13 pagesTechnical Information: Stereo 20W (4 Digital Power Processing Technology TA2020-020Tatang DevakaNo ratings yet

- Data Sheet: TDA1541ADocument13 pagesData Sheet: TDA1541Afarlocco23No ratings yet

- Pam8403 PDFDocument11 pagesPam8403 PDFShahzad RafiqNo ratings yet

- Esp LC SM 15km DatasheetDocument11 pagesEsp LC SM 15km DatasheetPowerstormNo ratings yet

- Precision Digital-to-Analog Converters: SEA DFAE Training Dec 2004Document38 pagesPrecision Digital-to-Analog Converters: SEA DFAE Training Dec 2004wildmonkey88No ratings yet

- Advanced Motion Controls Dr100re30a40ldcDocument7 pagesAdvanced Motion Controls Dr100re30a40ldcElectromateNo ratings yet

- Taos TCS3472 DatasheetDocument26 pagesTaos TCS3472 DatasheetKathryn WorkmanNo ratings yet

- 2.488Gbps SFP Optical Transceiver, 300m Reach: DS-SFP-FC-2G-SWDocument8 pages2.488Gbps SFP Optical Transceiver, 300m Reach: DS-SFP-FC-2G-SWtv_romeoNo ratings yet

- YS-C20K ManualDocument3 pagesYS-C20K ManualQasimNo ratings yet

- Realtek RTL2832U: The Mystery Chip at The Heart of RTL-SDRDocument2 pagesRealtek RTL2832U: The Mystery Chip at The Heart of RTL-SDRMoh MohNo ratings yet

- 10Gbps 20km LC BIDI SFP+ TransceiverDocument11 pages10Gbps 20km LC BIDI SFP+ TransceiverrauolNo ratings yet

- AEAT 9000 1GSH0 Full Option Ultra Precision 17 Bit Absolute Single Turn Encoder PDFDocument8 pagesAEAT 9000 1GSH0 Full Option Ultra Precision 17 Bit Absolute Single Turn Encoder PDFNguyen Quang VinhNo ratings yet

- Dynamic Testing of Highspeed Adcs Part 2Document17 pagesDynamic Testing of Highspeed Adcs Part 2ketkyhuNo ratings yet

- SGTL5000 QFN32Document73 pagesSGTL5000 QFN32yamaha640No ratings yet

- 9-0-9 Step Down TransformerDocument20 pages9-0-9 Step Down TransformerSarthak JoshiNo ratings yet

- DLA001Document36 pagesDLA001Rogerio GuimarãesNo ratings yet

- Lc8812 LedDocument14 pagesLc8812 LedWang Alan100% (1)

- Dac 8411Document38 pagesDac 8411jsmith012xNo ratings yet

- DDS RF Signal Generator Design GuideDocument9 pagesDDS RF Signal Generator Design GuideIan McNairNo ratings yet

- Advanced Motion Controls Dq111se25a20nacDocument7 pagesAdvanced Motion Controls Dq111se25a20nacElectromateNo ratings yet

- RXM XXX ES Data GuideDocument11 pagesRXM XXX ES Data GuideAstrid PorticaNo ratings yet

- Tda 7339Document12 pagesTda 7339Giovanni Carrillo VillegasNo ratings yet

- A4982 DatasheetDocument20 pagesA4982 DatasheetmedhyalNo ratings yet

- ARM-A Mandatory PrimerDocument4 pagesARM-A Mandatory PrimervigneshwaranjNo ratings yet

- D 3 NikelsphurDocument24 pagesD 3 NikelsphurvigneshwaranjNo ratings yet

- When Things Go Wrong in the ClassroomDocument12 pagesWhen Things Go Wrong in the ClassroomvigneshwaranjNo ratings yet

- HCPL4701Document16 pagesHCPL4701vigneshwaranjNo ratings yet

- ST Ms Project Integration GuideDocument42 pagesST Ms Project Integration Guideantothoppil001No ratings yet

- Energizer X 92Document2 pagesEnergizer X 92vigneshwaranjNo ratings yet

- The Object PrimerDocument84 pagesThe Object PrimerNeneFINo ratings yet

- DDE ServerDocument2 pagesDDE ServervigneshwaranjNo ratings yet

- Vsn700 Data Logger Bcd.00387 enDocument4 pagesVsn700 Data Logger Bcd.00387 envigneshwaranjNo ratings yet

- Ricardo Vargas Simplified Program Flow Color A3 enDocument1 pageRicardo Vargas Simplified Program Flow Color A3 envigneshwaranjNo ratings yet

- Project Management Professional (PMP) : Process Details of PMBOK Guide 5 Edition byDocument53 pagesProject Management Professional (PMP) : Process Details of PMBOK Guide 5 Edition byvigneshwaranjNo ratings yet

- CAN Error InjectionDocument6 pagesCAN Error InjectionvigneshwaranjNo ratings yet

- Python BasicsDocument20 pagesPython BasicsMuhammad Royyan ZahirNo ratings yet

- Ma To Serial ConversionDocument2 pagesMa To Serial ConversionvigneshwaranjNo ratings yet

- PMIW LocalCommunity WashingtonCircle PresentationSlides 2013-09Document21 pagesPMIW LocalCommunity WashingtonCircle PresentationSlides 2013-09vigneshwaranjNo ratings yet

- I-7567 Usermanual v1.0Document28 pagesI-7567 Usermanual v1.0vigneshwaranjNo ratings yet

- Module 3 Presentation MaterialsDocument26 pagesModule 3 Presentation MaterialsvigneshwaranjNo ratings yet

- Prime WebDocument1 pagePrime WebvigneshwaranjNo ratings yet

- Bluetooth in IndustryDocument6 pagesBluetooth in IndustryMohammed JunedNo ratings yet

- Daniel ModbusDocument82 pagesDaniel ModbusligdieliNo ratings yet

- Garlic KhasiatDocument32 pagesGarlic KhasiatRinawati BarusNo ratings yet

- Getting Started v10Document152 pagesGetting Started v10vigneshwaranjNo ratings yet

- Docklight Scripting ManualDocument135 pagesDocklight Scripting ManualvigneshwaranjNo ratings yet

- Docklight Scripting ManualDocument135 pagesDocklight Scripting ManualvigneshwaranjNo ratings yet

- Pi Mbus 300 PDFDocument121 pagesPi Mbus 300 PDFhipercortexNo ratings yet

- NETMF+for+STM32+-+Technical+Notes+Release+4 2Document5 pagesNETMF+for+STM32+-+Technical+Notes+Release+4 2vigneshwaranjNo ratings yet

- Hybrid Controller: Reluctance Motor 3-Phase SwitchedDocument122 pagesHybrid Controller: Reluctance Motor 3-Phase SwitchedvigneshwaranjNo ratings yet

- SIM900 ReviewDocument2 pagesSIM900 ReviewSlavko MitrovicNo ratings yet

- Microsoft Project 2010 Step by Step-Chapter2Document31 pagesMicrosoft Project 2010 Step by Step-Chapter2Arun HutabaratNo ratings yet

- KilatHosting Vulnerability ReportDocument14 pagesKilatHosting Vulnerability ReportDondy BappedyantoNo ratings yet

- B.Sc. CS Syllabus (CBCS) Thiruvalluvar UniversityDocument60 pagesB.Sc. CS Syllabus (CBCS) Thiruvalluvar UniversityAakash Santhanam100% (2)

- IPv6@ESTG-Leiria IPv6Wireless Relatorio FinalDocument94 pagesIPv6@ESTG-Leiria IPv6Wireless Relatorio FinalAndré MadeiraNo ratings yet

- F01 Bus SystemsDocument46 pagesF01 Bus SystemsPhan VănNo ratings yet

- Business Cloud SDN Solution: Omada EAP - Business Wi-Fi SeriesDocument27 pagesBusiness Cloud SDN Solution: Omada EAP - Business Wi-Fi Seriessaif rehmanNo ratings yet

- F5 BIG-IP APM - Implementation GuideDocument8 pagesF5 BIG-IP APM - Implementation GuideHenryNo ratings yet

- Bearer ServiceDocument4 pagesBearer ServiceManjula ChikkanargundNo ratings yet

- C. RouterDocument10 pagesC. RouterAim HighNo ratings yet

- Networking Cheatsheet CommandsDocument5 pagesNetworking Cheatsheet CommandsadminakNo ratings yet

- Medicion de RFC2544Document10 pagesMedicion de RFC2544Jairo Jesus Navarrete LomaNo ratings yet

- Comptia Cloud Cv0 003 Exam ObjectivesDocument18 pagesComptia Cloud Cv0 003 Exam ObjectivesSafari MatabishNo ratings yet

- WCDMA DesignHandbook PDFDocument593 pagesWCDMA DesignHandbook PDFRoxi Roxx100% (1)

- Task 1: Analyze Cisco Express ForwardingDocument3 pagesTask 1: Analyze Cisco Express ForwardingIonut StanciuNo ratings yet

- HITRUST Policies - Network Security Management ProcedureDocument8 pagesHITRUST Policies - Network Security Management ProcedureMebrat WorkuNo ratings yet

- Terraform Basic Commands, Fundamentals & VariablesDocument7 pagesTerraform Basic Commands, Fundamentals & VariablesshekhargptNo ratings yet

- Lab Security Policy Cyber Security PolicyDocument4 pagesLab Security Policy Cyber Security PolicyISCNo ratings yet

- Mimosa by Airspan C5x Datasheet - DS 0016 30 PDFDocument4 pagesMimosa by Airspan C5x Datasheet - DS 0016 30 PDFIsaacNo ratings yet

- Modbus Interface For SUNNY CENTRALDocument61 pagesModbus Interface For SUNNY CENTRALjosepablohg100% (1)

- PROFINET Design Guideline 8062 V153 Sept22Document242 pagesPROFINET Design Guideline 8062 V153 Sept22Gabriel NascimentoNo ratings yet

- MDS SD Series: Setup GuideDocument4 pagesMDS SD Series: Setup GuideCarlos David Ordaz JuárezNo ratings yet

- Ericsson ParametersDocument32 pagesEricsson Parametersinaki_rodriguez_reyesNo ratings yet

- Study RZ and NRZ Line CodingDocument5 pagesStudy RZ and NRZ Line CodingSRI HARSHA ACHINo ratings yet

- Iphone Issues On Call Set-UpDocument32 pagesIphone Issues On Call Set-UpEfosa Aigbe100% (1)

- Shark Fest 2015 Packet ChallengeDocument3 pagesShark Fest 2015 Packet Challengeשוקולד וסוכר ומלח שוקולד סוכרNo ratings yet

- ASR5x00 MME Attach Failure Because of S PDFDocument3 pagesASR5x00 MME Attach Failure Because of S PDFKhaleel Aboobackr.kNo ratings yet

- Expl WAN Chapter 1 Intro WANsDocument82 pagesExpl WAN Chapter 1 Intro WANsLeo LaguiNo ratings yet

- ChangeAuditor For Active Directory Event Reference GuideDocument62 pagesChangeAuditor For Active Directory Event Reference GuidevishwahNo ratings yet

- Datafill - RFPar - AREA1 (Sumatera)Document1,598 pagesDatafill - RFPar - AREA1 (Sumatera)Rixson SitorusNo ratings yet

- DT CNC BandwidthDocument9 pagesDT CNC BandwidthNgoc Tan NguyenNo ratings yet

- Cisco Certified Design Expert in DepthDocument562 pagesCisco Certified Design Expert in Depthdeltakio@gmail.com100% (1)