Professional Documents

Culture Documents

VLSI DEsign & Embedded Systems

Uploaded by

Kiran Kumar0 ratings0% found this document useful (0 votes)

208 views33 pagesVLSI

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentVLSI

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

208 views33 pagesVLSI DEsign & Embedded Systems

Uploaded by

Kiran KumarVLSI

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 33

NMAM INSTITUTE OF TECHNOLOGY

(An Autonomous Institution under VTU, Belgaum)

(Revised MAY 2013 )

Syllabus of Master of Technology

in

VLSI & EMBEDDED SYSTEMS DESIGN

Effective 2013-2014

Department of

Electronics and Communication Engineering

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 2

SCHEME OF TEACHING AND EXAMINATION FOR

VLSI AND EMBEDDED SYSTEM DESIGN - 2012 SCHEME

( effective MAY 2013 onwards)

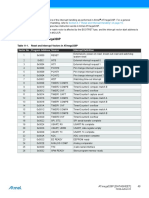

I SEMESTER

ELECTIVE I ELECTIVE - II

13VDE 111 Modeling of Digital Systems using VHDL 13VDE 121 Advanced Digital System Design

13VDE 112 High Speed VLSI Design 13VDE 122 DSP Algorithms & Architecture

13VDE 113 SoC Design 13 VDE 123 Soft Computing

Sub. code

Name of the Subject

L+T+P+S

Self

study/

Case

Study

Hrs/

week

Contact

Hrs/

Week

Duration

of Sem

End Exam

in hours

Marks for

Total

Credits

CIE

SEE

13VDE 101

Advanced Embedded

Systems

4+0+0+4

4 4 3 50 50 5

13VDE 102 CMOS VLSI Design 4+0+2+0 -- 6 3 50 50 5

13VDE 103 VLSI Design Verification

4+2+0+0

-- 6 3 50 50 5

13VDE 11X Elective I 4+0+0+0 -- 4 3 50 50 4

13VDE 12X Elective II 4+0+0+0 -- 4 3 50 50 4

13VDE 104

Application Lab-I

(Embedded Systems)

0+0+4+0

-- 4 - 100 -- 2

TOTAL 20+2+6+4 4 28 15 350 250 25

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 3

II SEMESTER

ELECTIVE III ELECTIVE - IV

13VDE 211 Advances in VLSI Design 13VDE221 System Design Using Embedded Processers

13VDE212 Algorithms for VLSI 13VDE 222 MEMS and IC Integration

13VDE213 Low Power VLSI 13VDE223 VLSI Signal Processing

Sub. code

Name of the Subject

L+T+P+S

Self

study

/Case

Study

Hrs/

week

Contact

Hrs/

Week

Duration

of Sem

End

Exam in

hours

Marks for

Total

Credits

CIE

SEE

13VDE 201 Advanced

Microcontroller

4+2+0+0

-- 6 3

50 50 5

13VDE 202

Design of Analog and

Mixed mode circuits

4+0+2+0

-- 6 3

50 50 5

13VDE 203 Real Time Operating

Systems

4+0+0+4

4 4 3

50 50 5

13VDE 21X Elective III 4+0+0+0 -- 4 3 50 50 4

13VDE 22X Elective IV 4+0+0+0 -- 4 3 50 50 4

13VDE 204 Application Lab-II

(VLSI & RTOS)

0+0+4+0

-- 4

-- 100 -- 2

TOTAL 20+2+6+4 4 28 15 350 250 25

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 4

III SEMESTER

IV SEMESTER

Sub. code

Name of the

Subject

Duration Marks for

Total Credits Practical/Field

work/Assignment

IA Exam

13VDE 301 Industrial Training/

Mini-Project

Full time 8 weeks 100

-- 6

13VDE 302 Seminar ---- 100 -- 4

13VDE 303 Project-part I Full time 8 weeks 200 -- 10

TOTAL 400 -- 20

Sub. code

Name of the

Subject

Duration Marks for

Total

Credits

Practical/Field

work

IA Exam

13VDE 401 Project part II

Report Submission,

Evaluation & Viva-

voce

14weeks

4 weeks

100

Report 100

Viva-voce 200

30

TOTAL 100 300 30

GRAND TOTAL from 1

st

to 4

th

semester : 100 credits

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 5

NOTE :

1. 13VDE301: Industrial Training /mini-project: Practical training report and oral presentation are

to be evaluated by the Department for 50 marks each. Alternatively, if mini-project is carried

out, it is evaluated for 100 marks by the Department

2. 13VDE302: The Seminar Marks are to be awarded by the Department committee constituted for

the purpose.

3. 13VDE303: Progress of work to be assessed by the Department Committee including the guide

for 100 marks.

4. 13VDE401: The project report valuation will be carried out separately by the guide for 50 marks,

Department Committee for 50 marks ( total IA marks 100 ) and the external examiner for 100

marks . Viva-Voce will carry 200 marks and will be conducted by a committee consisting of

the following:

a. Chairman, BOE (PG) or his nominee,

b. Project Guide and External examiner

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 6

I SEMESTER

Advanced Embedded System

Subject Code 13VDE 101 Credits 5

Hours/Week 4+0+0+4 CIE 50 Marks

Total Hours 52 SEE 50 Marks

Exam Hours 03

Typical Embedded System: Core of the Embedded System, Memory, Sensors and Actuators,

Communication Interface, Embedded Firmware, Other System Components.

Characteristics and Quality Attributes of Embedded Systems: Hardware Software Co-Design and

Program Modeling: Fundamental Issues in Hardware Software Co-Design, Computational Models in

Embedded Design, Introduction to Unified Modeling Language (Self Study/Case Study), Hardware

Software Trade-offs

Embedded Firmware Design and Development: Embedded Firmware Design Approaches, Embedded

Firmware Development Languages

Real-Time Operating System (RTOS) based Embedded System Design:

Operating System Basics, Types of OS, Tasks, Process and Threads, Multiprocessing and Multitasking,

Task Scheduling, Threads, Processes and Scheduling: Putting them altogether, Task Communication,

Task Synchronization, Device Drivers, How to Choose an RTOS (Self Study/Case Study).

The Embedded System Development Environment: The Integrated Development Environment (IDE)

(Self Study/Case Study), Types of Files Generated on Cross-compilation, Disassembler/Decompiler,

Simulators, Emulators and Debugging, Target Hardware Debugging, Boundary Scan.

Trends in the Embedded Industry: (Self Study/Case Study), Processor Trends in Embedded Systems,

Embedded OS Trends, Development Language Trends, Open Standards, Frameworks and Alliances,

Bottlenecks.

Reference Books:

R1. Shibu K V, Introduction to Embedded Systems, Tata McGraw Hill Education Private Limited, 2009

R2. James K Peckol , Embedded Systems A contemporary Design Tool, John Weily, 2008.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 7

CMOS VLSI DESIGN

Subject Code 13VDE 102 Credits 5

Hours/Week 4+0+2+0 CIE 50 Marks

Total Hours 52 SEE 50 Marks

Exam Hours 03

MOS Transistor Theory: n MOS / p MOS transistor, threshold voltage equation, body effect, MOS device

design equation, sub threshold region, Channel length modulation. mobility variation, Tunneling, punch

through, hot electron effect MOS models, small signal AC Characteristics, CMOS inverter, n / p ratio,

noise margin, static load MOS inverters, differential inverter, transmission gate, tristate inverter,

BiCMOS inverter.

CMOS Process Technology: Lambda Based Design rules, scaling factor, semiconductor Technology

overview, basic CMOS technology, p well / n well / twin well process. Current CMOS enhancement

(oxide isolation, LDD. refractory gate, multilayer inter connect) , Circuit elements, resistor , capacitor,

interconnects, sheet resistance & standard unit capacitance concepts delay unit time, inverter delays ,

driving capacitive loads, propagate delays, MOS mask layer, stick diagram, design rules and layout,

symbolic diagram, mask feints, scaling of MOS circuits.

Basics of Digital CMOS Design: Combinational MOS Logic circuits-Introduction, CMOS logic circuits with

a MOS load, CMOS logic circuits, complex logic circuits, Transmission Gate. Sequential MOS logic Circuits

- Introduction, Behavior of hi stable elements, SR latch Circuit, clocked latch and Flip Flop Circuits, CMOS

D latch and triggered Flip Flop. Dynamic Logic Circuits - Introduction, principles of pass transistor

circuits, Voltage boot strapping synchronous dynamic circuits techniques, Dynamic CMOS circuit

techniques

Dynamic CMOS and clocking: Introduction, advantages of CMOS over NMOS, CMOS\SOS technology,

CMOS\bulk technology, latch up in bulk CMOS., static CMOS design, Domino CMOS structure and

design, Charge sharing, Clocking- clock generation, clock distribution, clocked storage elements.

Reference Books:

R1. Neil Weste and K. Eshragian, Principles of CMOS VLSI Design: A System Perspective, 2nd

edition, Pearson Education (Asia) Pte. Ltd., 2000.

R2. Wayne, Wolf, Modern VLSI design: System on Silicon Pearson Education, Second Edition

R3. Douglas A Pucknell & Kamran Eshragian , Basic VLSI Design PHI 3rd Edition (original Edition

1994)

R4. Sung Mo Kang & Yosuf Leblebici, CMOS Digital Integrated Circuits: Analysis and Design, McGraw-

Hill (Third Edition)

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 8

CMOS VLSI DESIGN LAB

(Use any of the EDA Tools)

LAB EXPERIMENTS:

1. Develop Verilog code for the following. Perform simulations using test benches.

Universal Gates

A transmission gate

4 bit parallel adder

MOD-N synchronous counter

Asynchronous counter

2. Perform schematic simulation for a CMOS Inverter. Report the result of DC and AC analysis.

3. Perform schematic simulation for a static CMOS circuit to compute f =NOT[(A+B)(C+D) ]

4. Perform layout simulation for a CMOS inverter.

5. Using SPICE, perform simulation to measure the power for a digital circuit.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 9

VLSI DESIGN VERIFICATION

Subject Code 13VDE 103 Credits 5

Hours/Week 4+0+0+4 CIE 50 Marks

Total Hours 52 SEE 50 Marks

Exam Hours 03

Introduction: VLSI development process , role of testing and verification, VLSI Technology Trends

Affecting Testing, verification methodology, Types of Design Verification - Functional Verification,

Simulation Emulation

Testing and verification: how to test chips? test equipements, electrical parametric testing, types of

verification

Block-level Veriifcation. Functional Verification through simulation. Whitebox, blackbox and Graybox

testing. Verilog/VHDL test bench for functional verification

Static Timing Verification. Concept of static timing analysis. Timing constraints, timing models, critical

path analysis, false paths.

Physical Design Verification. Layout rule checks and electrical rule checks. Parasitic extraction. Antenna,

cross talk.

Fault modeling: defects, errors& fault, Functional Versus Structural Testing, fault models, single stuck at

faults

Logic and fault simulation: Modeling circuit for simulatuion, event driven simulation ,serial fault

simulation

Test generation & DFT: ATPG for combinational circuit, Design for testability and scan, scan cell

design, BIST

Reference Books:

R1. M. Bushnell, Vishwani Agrawal, Essentials of Electronic Testing for Digital, Memory, and Mixed-

Signal VLSI Circuits

R2. Prakash Rashinkar, Peter Paterson and Leena Singh System on a - Chip Verification

Methodology and Techniques , Kulwer Publishers, 2001.

R3. Laung-Terng wang, Cheng-Wen wu & Xiaoqing Wen, VLSI Test Principles and Architectures-

Design for Testability

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 10

R4. S. Minato Binary Decision Diagram and Applications for VLSI CAD, Kulwer Academic Pub.

November 1996.

R5. An excellent source for instructors for Formal Verification techniques (website developed by)

Prof. V. Narayanan, Penn State University, USA. http://www.cse.psu.edu/~vijay/verify/instuctors.html

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 11

APPLICATION LAB I

Subject Code 13VDE 104 Credits 2

Hours/Week 0+0+0+4 CIE 100 Marks

SEE ------

List of Experiments

ARM LAB

1. Digital I/O, MCU pin direction, and logical functions, written in assembly and simulated

2. LEDs and switching, written in assembly (simulated)

3. Use switches and LEDs, and control LED intensity using switches written in C (simulated)

4. Traffic Light Controller with bits, written in assembly (simulated)

5. Program simple loops and subroutines in C (simulated)

6. Reset system using watchdog timer in case of error.

7. Fixed point arithmetic in assembly

8. Simple FSM simulator in C

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 12

ELECTIVE-I

MODELING OF DIGITAL SYSTEMS USING VHDL

Subject Code 13VDE 111 Credits 4

Hours/Week 4+0+0+0 CIE 50 Marks

Total Hours 52 SEE 50 Marks

Exam Hours 03

Specification of combinational systems using VHDL, Introduction to VHDL, Basic language element of

VHDL, Behavioral Modeling, Data flow modeling, Structural modeling,Subprograms and overloading,

VHDL description of gates.

Description and design of sequential circuits using VHDL, Standard combinational modules,

Design of a Serial Adder with Accumulator, State Graph for Control Network, design of a Binary

Multiplier, Multiplication of a Signed Binary Number, Design of a Binary Divider.

Register- transfer level systems, Execution Graph, Organization of System, Implementation of

RTL Systems, Analysis of RTL Systems, and Design of RTL Systems.

Data Subsystems, Storage Modules, Functional Modules, Data paths, Control Subsystems,

Micro programmed Controller, Structure of a micro programmed controller, Micro instruction

Format, Micro instruction sequencing, Micro instruction Timing, Basic component of a microsystem,

memory subsystem. I/O subsystem, Processors, Operation of the computer and cycle time, Binary

Decoder, Binary Encoder, Multiplexers and Demultiplexers,Floating Point Arithmetic-Representation of

Floating Point Number, Floating Point Multiplication

Text Books:

1.. M. Ercegovac, T. Lang and L.J. Moreno, Introduction to Digital Systems, Wiley,2000

2. C. H. Roth, Digital System Design using VHDL, Thomson Learning,2001

3. J. Bhaskar, A VHDL Primer, Addison Wesley, 1999

Reference Books:

R1. John.F.Wakerly, Digital Design-Principles and Practices, PHI, 3rd Edition updated, 2005

R2. Douglas Perry, VHDL: Programming by Example, TMH, 2002

R3. Michae John Sebastian Smith, Application-Specific Integrated Circuits, Addison-Wesley, 1997

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 13

R4. Navabi, VHDL-Analysis and Modeling of Digital Systems, MGH, 1998

R5. Pedroni, Circuit Design with VHDL, PHI, 2005

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 14

HIGH SPEED VLSI DESIGN

Sub. Code 13VDE 112 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

Clocked Logic Styles, Single-Rail Domino Logic Styles, Dual-Rail Domino Structures, Latched Domino

Structures, Clocked Pass Gate Logic

Non-Clocked Logic Styles, Static CMOS, DCVS Logic, Non-Clocked Pass Gate Families.Circuit Design

Margining, Design Induced Variations, Process Induced Variations, ApplicationInduced Variations, Noise.

Latching Strategies, Basic Latch Design, and Latching single-ended logic, Latching Differential Logic

Race Free Latches for Pre-charged Logic Asynchronous Latch Techniques.

Signaling Standards, Chip-to-Chip Communication Networks, ESD Protection

Clocking Styles, Clock Jitter, Clock Skew, Clock Generation, Clock Distribution, Asynchronous

Clocking Techniques ,Skew Tolerant Design

Text Books:

T1. Kerry Bernstein & et. al., High Speed CMOS Design Styles, Kluwer, 1999.

T2. Evan Sutherland, Bob stroll, David Harris, Logical Efforts, Designing Fast CMOS Circuits,

Kluwer, 1999.

T3. David Harris, Skew Tolerant Domino Design.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 15

SoC DESIGN

Sub. Code 13VDE113 CIE Marks 50

Hrs./ week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs 3

Motivation for SoC Design - Review of Moores law and CMOS scaling, benefits of system-on-chip

integration in terms of cost, power, and performance. Comparison on System-on-Board, System-on-

Chip, and System-in-Package. Typical goals in SoC design cost reduction, power reduction, design

effort reduction, performance maximization. Productivity gap issues and the ways to improve the gap

IP based design and design reuse.

Embedded Processors microprocessors, microcontrollers, DSP and their selection criteria. Review of

RISC and CISC instruction sets, Von-Neumann and Harward architectures, and interrupt architectures.

Embedded Memories scratchpad memories, cache memories, flash memories, embedded DRAM.

Topics related to cache memories. Cache coherence. MESI protocol and Directory-based coherence.

Hardware Accelerators in an SoC comparison on hardware accelerators and general-purpose CPU.

Accelerators for graphics and image processing.

Typical peripherals in an SoC DMA controller, USB controller.

Interconnect architectures for SoC-. Bus architecture and its limitations. Network on Chip (NoC)

topologies. Mesh-based NoC. Routing in an NoC. Packet switching and wormhole routing.

Mixed Signal and RF components in an SoC- Sensors, Amplifiers, Data Converters, Power management

circuits, RF transmitter and receiver circuits.

SoC Design Flow -IP design, verification and integration, hardware-software codesign, power

management problems, and packaging related problems.

Reference Books:

R1. Sudeep Pasricha and Nikil Dutt, On-Chip Communication Architectures: System on Chip

Interconnect, Morgan Kaufmann Publishers 2008

R2. Henry Chang et al., Surviving the SOC revolution: a guide to platform-based design, Kluwer

(Springer), 1999

R3. Frank Ghenassia, Transaction Level Modeling with SystemC: TLM Concepts and Applications for

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 16

Embedded Systems, Springer 2005 (281 pages), ISBN:9780387262321

R4. Luca Benini and Giovanni De Micheli,Networks on Chips: Technology and Tools, Morgan

Kaufmann Publishers 2006 (408 pages), ISBN:9780123705211,

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 17

ELECTIVE-II

ADVANCED DIGITAL SYSTEM DESIGN

Sub. Code 13VDE 121 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

SEQUENTIAL CIRCUIT DESIGN :Analysis of clocked synchronous sequential circuits and modeling- State

diagram, state table, state table assignment and reduction-Design of synchronous sequential circuits-

design of iterative circuits-ASM chart and realization using ASM

ASYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN Analysis of asynchronous sequential circuit flow table

reduction-races-state assignment-transition table and problems in transition table- design of

asynchronous sequential circuit-Static, dynamic and essential hazards data synchronizers mixed

operating mode asynchronous circuits designing vending machine controller

FAULT DIAGNOSIS AND TESTABILITY ALGORITHMS :Fault table method-path sensitization method

Boolean difference method-D algorithm -Tolerance techniques The compact algorithm Fault in PLA

Test generation-DFT schemes Built in self test

SYNCHRONOUS DESIGN USING PROGRAMMABLE DEVICES :

Programming techniques, Reprogrammable device architecture- function blocks, I/O blocks,

Interconnects, realize combinational, arithmetic, sequential circuit with PLA, Architecture and

application of

NEW GENERATION PROGRAMMABLE LOGIC DEVICES:Foldback architecture with GAL, EPLD, EPLA,

PEEL; Realization of finite state machine using PLD FPGA Xilinx FPGA-Xilinx 4000

Reference Books:

R1 Charles H.Roth Jr, Fundamentals of Logic Design Thomson Learning 2004

R2 Nripendra N Biswas Logic Design Theory Prentice Hall of India, 2001

R3 Parag K.Lala Fault Tolerant and Fault Testable Hardware Design B SPublications, 2002

R4 Parag K.Lala Digital system Design using PLD B S Publications, 2003

R5 Charles H Roth Jr., Digital System Design using VHDL Thomson learning, 2004

R6 Douglas L.Perry, VHDL programming by Example Tata McGraw.Hill 2006

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 18

DSP Algorithms & Architecture

Sub. Code 13VDE 122 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

Introduction to Generic DSPs, Performance and Structural limitations. Measures and Structures for

enhancing performance.

Filter structures, Transform structures, Data Flow and Control flow issues. Array processing approaches

to DSP solutions.

Some modern DSP algorithms (audio, video and multimedia) and development of new computational

and arithmetic building blocks.

Architecture development for some Compression and Coding Algorithms. Reference to some standards

and development of Architecture based implementation of these.

Reference Books:

R1. Keshab K Parhi, VLSI Signal Processing Systems, John Wiley and Sons, New York, 1999.

R2. Peter Prissch, Architectures for Digital Signal Processing , Jhon Wiley and Sons, New York, 1998.

R3. Khalid Sayood, Introduction in Data Compression, 2E Harcourt India, New Delhi, 2000

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 19

SOFT COMPUTING

Sub. Code 13VDE 123 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

INTRODUCTION TO SOFT COMPUTING AND NEURAL NETWORKS:Evolution of Computing - Soft

Computing Constituents From Conventional AI to Computational Intelligence

GENETIC ALGORITHMS: Introduction to Genetic Algorithms (GA) Applications of GA in Machine

Learning - Machine Learning Approach to Knowledge Acquisition.

NEURAL NETWORKS: Introduction to Neural Network, Adaptive Networks Feed forward Networks.

FUZZY LOGIC: Fuzzy Sets Operations on Fuzzy Sets Fuzzy Relations Membership Functions- Fuzzy

Rules and Fuzzy Reasoning Fuzzy Inference Systems.

NEURO-FUZZY MODELING: Fuzzy Expert Systems Fuzzy Decision Making.

Text Books:

T1. Jyh-Shing Roger Jang, Chuen-Tsai Sun, Eiji Mizutani, Neuro-Fuzzy and Soft Computing, PHI, 2003.

T2. George J. Klir and Bo Yuan, Fuzzy Sets and Fuzzy Logic-Theory and Applications, PHI, 1995.

T3. James A. Freeman and David M. Skapura, Neural Networks Algorithms, Applications, and

Programming Techniques, Pearson Edn., 2003.

T4. Simon Haykin, Neural Networks, Prentice-Hall of India

Reference Books:

R1. Mitchell Melanie, An Introduction to Genetic Algorithm, Prentice Hall, 1998.

R2. David E. Goldberg, Genetic Algorithms in Search, Optimization and Machine Learning, Addison

Wesley, 1997.

R3. S. N. Sivanandam, S. Sumathi and S. N. Deepa, Introduction to Fuzzy Logic using MATLAB,

Springer, 2007.

R4. S.N.Sivanandam S.N.Deepa, Introduction to Genetic Algorithms, Springer, 2007.

R5. Jacek M. Zurada, Introduction to Artificial Neural Systems, PWS Publishers, 1992.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 20

II SEMESTER

ADVANCED MICROCONTROLLER

Sub. Code 13VDE 201 CIE Marks 50

Hrs./Week 4+2+0+0 SEE Marks 50

Total Hrs. 52 Credits 5

Exam Hrs. 3

Motivation for advanced microcontrollers Low Power embedded systems, On-chip peripherals, low-

power RF capabilities. Examples of applications.

MSP430 16-bit Microcontroller family. CPU architecture, Instruction set, Interrupt mechanism, Clock

system, Memory subsystem, bus architecture. The assembly language and C programming for MSP-

430 microcontrollers. On-chip peripherals. WDT, Comparator, Op-Amp, Timer, Basic Timer, Real Time

Clock (RTC), ADC, DAC, Digital I/O. Using the low-power features of MSP430. Clock system, low-power

modes, Clock request feature, Low-power programming and interrupts.

ARM -32 bit Microcontroller family. Architecture of ARM Cortex M3 General Purpose Registers, Stack

Pointer, Link Register, Program Counter, Special Register,. Nested Vector Interrupt Controller. Interrupt

behavior of ARM Cortex M3. Exceptions Programming. Advanced Programming Features. Memory

Protection. Debug Architecture.

Applications Wireless Sensor Networking with MSP430 and Low-Power RF circuits; Pulse Width

Modulation(PWM) in Power Supplies.

References Books:

R1. Joseph Yiu, The Definitive Guide to the ARM Cortex-M3, Newnes, (Elsevier), 2008.

R2. John Davies, MSP430 Microcontorller Basics, Newnes (Elsevier Science), 2008.

R3. MSP430 Teaching CD-ROM, Texas Instruments, 2008.

R4. Sample Programs for MSP430 downloadable from msp430.com

R5. David Patterson and John L. Henessay, Computer Organization and Design, (ARM Edition),

Morgan Kauffman.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 21

DESIGN OF ANALOG & MIXED MODE VLSI CIRCUITS

Sub. Code 13VDE 202 CIE Marks 50

Hrs./Week 4+0+2+0 SEE Marks 50

Total Hrs. 52 Credits 5

Exam Hrs. 3

Basic MOS Device Physics: General considerations, MOS I/V Characteristics, second order effects, MOS

device models. MOS Device as a Capacitor

Single stage Amplifier: CS stage with resistance load, diode connected load, current source load, triode

load, CS stage with source degeneration, source follower, common-gate stage, cascode stage, Folded

cascode, choice of device models.

Differential Amplifiers: Basic difference pair, common mode response, Differential pair with MOS loads,

Gilbert cell.

Passive and active Current mirrors: Basic current mirrors, Cascode current mirrors, active current

mirrors.

Frequency response of Amplifier: General considerations, Common source stage, source follower,

Common gate stage, Cascode stage and Difference pair. Noise in CS stage, CG stage, source follower,

cascode stage, differential pair.

Operational Amplifiers: One Stage OP-Amp, Two Stage OP-Amp, Gain boosting, Common Mode

Feedback, Slew rate, PSRR. Compenastion of two stage OP-Amp, Other compensation techniques.

Oscillators: Ring Oscillators, LC Oscillators, VCO, Mathematical Model of VCO.

PLL: Simple PLL, Charge pump PLL, Non-ideal effects in PLL, Delay locked loops and applications.

Reference Books:

R1. Behzad Razavi Design of Analog CMOS Integrated Circuits, TMH, 2007.

R2. R. Jacob Baker, Harry W. Li., David E. Boyce, CMOS : circuit Design , Layout and Simulation ,

PHI, 2003

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 22

ANALOG & MIXED MODE VLSI LAB

LAB EXPERIMENTS:

TOOLS TO BE USED: CADANCE/SYNOPSIS/MENTOR GRAPHICS.

1. Design a single stage amplifier using MOSFETs for the given specifications.

2. Design a differential amplifier using MOSFETs for the given specifications.

3. Design a two stage op-amp for the given specification. Determine the frequency response, slew

rate, offset effects and Noise.

4. Design a simple sample and hold circuit and measure the switching times.

NOTE: Design flow:

1. Draw the schematic and verify the following

2. DC Analysis

3. AC Analysis

4. Transient Analysis

5. Draw the Layout and verify the DRC, ERC

6. Check for LVS

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 23

REAL TIME OPERATING SYSTEMS

Sub. Code 13VDE 203 CIE Marks 50

Hrs./Week 4+0+0+4 SEE Marks 50

Total Hrs. 52 Credits 5

Exam Hrs. 3

Introduction to Real-Time Embedded Systems: Brief history of Real Time Systems, A brief history of

Embedded Systems.

System Resources: Resource Analysis, Real-Time Service Utility, Scheduling Classes, The Cyclic

Esecutive, Scheduler Concepts, Preemptive Fixed Priority Scheduling Policies, Real-Time OS, Thread Safe

Reentrant Functions.

Processing: Preemptive Fixed-Priority Policy, Feasibility, Rate Montonic least upper bound, Necessary

and Sufficient feasibility, Deadline Monotonic Policy, Dynamic priority policies. (Self Study/Case

Study) : EDF algorithm,IRIS tasks,Multiprocessor scheduling algorithms.

I/O Resources: ,Worst-case Execution time, Intermediate I/O, Execution efficiency, I/O Architecture.

Memory: Physical hierarchy, Capacity and allocation, Shared Memory, ECC Memory, Flash filesystems.

Multi-resource Services: Blocking, Deadlock and livestock, Critical sections to protect shared resources,

priority inversion.

Soft Real-Time Services:Missed Deadlines, QoS, Alternatives to rate monotonic policy, Mixed hard and

soft real-time services. (Self Study/Case Study): Hardware Synchronization using PLLs,Software

Synchronization algorithms(Interactive Convergence Averaging algorithms,Clock and its

representations.

Embedded System Components: Firmware components, RTOS system software mechanisms, Software

application components.

Debugging Components: Execptions assert, Checking return codes, Single-step debugging, kernel

scheduler traces, Test access ports, Trace ports, Power-On self test and diagnostics, External test

equipment, Application-level debugging.

Performance Tuning:

Basic concepts of drill-down tuning, hardware supported profiling and tracing, Building performance

monitoring into software, Path length, Efficiency, and Call frequency, Fundamental optimizations.

High availability and Reliability Design:

Reliability and Availability, Similarities and differences, Reliability, Reliable software, Available software,

Design trade offs, Hierarchical applications for Fail-safe design.

Design of RTOS PIC microcontroller. (Chap 13 of book Myke Predko) . (Self Study/Case Study): Case

studies based on MUCOS,VxWorks such as ACVM,Sending application layer byte streams on TCP/IP

stack,Smart card application.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 24

Reference Books:

R1. Sam Siewert, Real-Time Embedded Systems and Components , Cengage Learning India Edition,

2007.

R2. Myke Predko , Programming and Customizing the PIC microcontroller, 3rd Ed, TMH, 2008.

R3. Dreamtech Software Team, Programming for Embedded Systems, Jhon Wiley, India Pvt. Ltd.,

2008.

R4. C.M.Krishna,Kang.G.Shin, Real Time Systems

R5. Raj Kamal, Embedded System Design

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 25

APPLICATION LAB II

(VLSI & RTOS)

Sub Code 13VDE 204 CIE Marks 100

Hrs./Week 0+0+0+4 SEE Marks --

Crdits 2

VLSI LAB

TOOLS TO BE USED: CADANCE/SYNOPSIS/MENTOR GRAPHICS.

1. Design a VCO for the given specifications.

2. Design a PLL and measure all the parameters.

3. Design a simple 8-bit DAC and measure the data conversion time.

4. Design successive approximation ADC and determine its characteristics.

Real Time Operating Systems LAB

USE LINUX/SOLARIS/QNX OS ONLY.

1. Implement simple IPC protocol.

2. Implement Semaphore and Mutex for any given applications.

3. Communicate between 2 PCs using Socket programming or message passing techniques (ie., MPI).

4. Create a POSIX based message queue for communicating between several tasks as per the

requirements given below:-

i. Use a named message queue with name MyQueue.

ii. Create N tasks with stack size 4000 & priorities (n-1) & n respectively. N can be any number

but more than 4.

iii. Tasks creates the specified message queue as Read Write and reads the message present, if

any, from the message queue and prints it on the console.

iv. Tasks open the message queue and posts the message Hi from Task(n-1).

MINI PROJECTS: (optional)

1. Implement protocol converter (refer book 3 given in the RTOS theory)

2. Implement System Calls for the RTOS using RTLinux.

3. Implement an IP phone.

4. Implement Device Driver.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 26

ELECTIVE-III

Advances in VLSI Design

Sub. Code 13VDE 211 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

Review of MOS circuits: MOS and CMOS static plots, switches, comparison between CMOS and Bi -

CMOS.

MESFETS: MESFET and MODFET operations, quantitative description of MESFETS.

MIS structures and MOSFETS: MIS systems in equilibrium, under bias, small signal operation of

MESFETS.

Short channel effects and challenges to CMOS: Short channel effects: Two dimensional Potential

profile, High electric field in the short channel, Punch-through and channel length modulation.

Scaling theory: Constant field constant voltage and quasi-constant voltage models.

Beyond CMOS: Evolutionary advances beyond CMOS, carbon Nano tubes, conventional vs. tactile

computing, computing, molecular and biological computing, Molectronics-molecular Diode and diode-

diode logic.

Super buffers, Bi-CMOS and Steering Logic: Introduction, super buffers- An NMOS super buffer,

tristate super buffer and pad drivers, CMOS super buffers, Dynamic ratio less inverters, large capacitive

loads, pass logic, designing of transistor logic, General functional blocks - NMOS and CMOS functional

blocks.

Special circuit layouts and technology mapping: Introduction, Talley circuits, NAND-NAND, NOR- NOR,

and AOI Logic, NMOS, CMOS Multiplexers, Barrel shifter, Wire routing Algorithms: Need for algorithms,

study of Lee-Moore Maze running algorithm, Line search algorithm.

System design: CMOS design methods, structured design methods, Strategies encompassing hierarchy,

regularity, modularity & locality, CMOS Chip design Options, programmable logic, programmable

structure, Gate, standard cell approach, Full custom Design.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 27

Reference Books:

R1. Kevin F Brrnnan Introduction to Semi Conductor Device, Cambridge publications

R2. Eugene D Fabricius Introduction to VLSI Design, McGraw-Hill International publications

R3. D.A Pucknell Basic VLSI Design, PHI Publication

R4.Wayne Wolf, Modern VLSI Design Pearson Education, Second Edition, 2002.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 28

Algorithms for VLSI

Sub. Code 13 VDE 212 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Mark 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

Graph Algorithms: Graph search Algorithms, Spanning tree Algorithm, Shortest path Algorithm,

Matching Algorithm, Min cut and Max cut Algorithms and Steiner Tree Algorithm.

Computational geometry Algorithms: Line sweep method and extended line sweep method.

Basic data structures: Linked list of blocks, Bin based method, neighbor pointers and corner stitching.

Graph Algorithms for physical design: Classes of graphs in physical design, relationship between graph

classes, graph problems, Algorithms for interval graphs and Algorithms for permutations graphs.

Partitioning: Group migration Algorithms.

Floor planning and Pin assignment: floor planning, chip planning and pin assignment.

Placement: Simulated annealing, simulated evolutions, force directed placement, sequence pair

technique, Breuers Algorithm, Terminal propagation Algorithm, Cluster growth and quadratic

assignment.

Routing: Maze routing Algorithms: Lees Algorithm, Soukups Algorithm and Hadlocks Algorithm.

Shortest path algorithm, Steiner tree based Algorithm. Single layer routing Algorithms and two layer

routing Algorithms.

Over the cell routing, Via minimization, clock, power and ground routing.

Text books:

T1. Naveed Sherwani, Algorithms for VLSI physical design automation 3

rd

edition, Springer

international.

T2. Pinaki Mazumber, Elizabeth M Rudnick, Genetic Algorithms, Pearson education

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 29

LOW POWER VLSI DESIGN

Sub. Code 13VDE 213 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

Introduction : Need for low power VLSI chips, Sources of power dissipation on Digital Integrated

circuits. Emerging Low power approaches, Physics of power dissipation in CMOS devices.

Device & Technology Impact on Low Power: Dynamic dissipation in CMOS, Transistor sizing & gate

oxide thickness, Impact of technology Scaling, Technology & Device innovation

Power estimation, Simulation Power analysis: SPICE circuit simulators, gate level logic simulation,

capacitive power estimation, static state power, gate level capacitance estimation, architecture level

analysis, Monte Carlo simulation.

Probabilistic power analysis: Random logic signals, probability & frequency, probabilistic power analysis

techniques, signal entropy.

Low Power Design Circuit level: Power consumption in circuits. Flip Flops & Latches design, high

capacitance nodes, low power digital cells library

Logic level: Gate reorganization, signal gating, logic encoding, state machine encoding, pre-computation

logic

Low power Architecture & Systems: Power & performance management, switching activity reduction,

parallel architecture with voltage reduction, flow graph transformation, low power arithmetic

components, low power memory design.

Low power Clock Distribution: Power dissipation in clock distribution, single driver Vs distributed

buffers, Zero skew Vs tolerable skew, chip & package co design of clock network

Reference Books:

R1. Kaushik Roy, Sharat Prasad, Low-Power CMOS VLSI Circuit Design Wiley, 2000

R2. Gary K. Yeap, Practical Low Power Digital VLSI Design, KAP, 2002

R3. Rabaey, Pedram, Low Power Design Methodologies Kluwer Academic, 1997

R4. Anantha P. Chandrakasan & Robert W. Brodersen, Low Power Digital CMOS Design Kluwer

Academic Publications, 1994.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 30

ELECTIVE-IV

SYSTEM DESIGN USING EMBEDDED PROCESSORS

Sub. Code 13VDE 221 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

.

8-Bit Microcontrollers:

Architecture: CPU Block diagram, Memory Organization, Program memory, Data Memory, Interrupts

Peripherals: Timers, Serial Port, I/O Port

Programming: Addressing Modes, Instruction Set, Programming

Microcontroller based System Design:

Timing Analysis

Case study with reference to 8-bit 8051 Microcontroller.

A typical application design from requirement analysis through concept design, detailed hardware and

software design using 8-bit 8051 Microcontrollers.

32- Bit ARM920T Processor Core:

Introduction: RISC/ARM Design Philosophy, About the ARM920T Core, Processor Functional Block

Diagram

Programmers Model: Data Types, Processor modes, Registers, General Purpose Registers, Program

Status Register, CP15 Coprocessor,Memory and memory mapped I/O, Pipeline, Exceptions, Interrupts

and Vector table, Architecture revisions, ARM Processor Families.

Cache: Memory hierarchy and cache memory,

Cache Architecture Basic Architecture of a Cache, Basic operation of a cache controller,

Cache and main memory relationship, Set Associativity ,Cache Policy Write policy, Cache line

replacement policies, allocation policy on a cache miss Instruction Cache, Data Cache, Write Buffer and

Physical Address TAG RAM

Memory Management Units: How virtual memory works, Details of the ARM MMU, Page Tables,

Translation Look-aside Buffer Domains and Memory access permissions

ARM Instruction Set: Data Processing instructions, Branch instructions, Load - Store instructions,

Software Interrupt Instruction, Program Status Register Instruction, Loading Constants

Thumb Instruction Set: Thumb register usage, ARM-Thumb interworking, Branch instruction,

Data processing instructions,Load - store instructions, stack instructions, software interrupt

instructions.

Interrupt Handling: Interrupts, Assigning interrupts, Interrupt latency, IRQ & FIQ exceptions,

Basic interrupt stack design ,and implementation, Non-nested Interrupt handler

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 31

ARM9 Microcontroller Architecture:

AT91RM9200 Architecture: Block Diagram, Features, Memory Mapping

Memory Controller (MC), Memory Controller Block Diagram, Address Decoder, External Memory Areas,

Internal Memory Mapping

External Bus Interface (EBI), Organization of the External Bus Interface, EBI Connections to

Memory Devices

External Memory Interface, Write Access, Read Access, Wait State Management

AT91RM9200 PERIPHERALS

Interrupt Controller: Normal Interrupt, Fast Interrupt, AIC

System Timer (ST): Period Interval Timer (PIT), Watchdog Timer (WDT), Real-time Timer (RTT)

Real Time Clock (RTC)

Parallel Input/Output Controller (PIO)

Development & Debugging Tools for Microcontroller based Embedded Systems:

Software and Hardware tools like Cross Assembler, Compiler, Debugger, Simulator, In-Circuit Emulator

(ICE), Logic Analyzer etc.

Reference Books:

R1. Andrew N Sloss, Dominic Symes, Chris Wright, ARM System Developer's Guide - Designing and

Optimizing System Software, Elsevier, 2006

R2. Ayala, Kenneth J, 8051 Microcontroller - Architecture, Programming & Applications, 1

st

Edition, Penram International Publishing.

R3. Raj Kamal, Microcontroller - Architecture Programming Interfacing and System Design, 1st

Edition, Pearson Publication

R4. Joseph Yiu, The Definitive Guide to the ARM Cortex-M3, Newnes, (Elsevier), 2008.

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 32

MEMS AND IC INTEGRATION

Sub. Code 13VDE 222 CIE Marks 50

Hrs./Week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs. 3

Overview of CMOS process in IC fabrication Crystal growth, doping, Growth and deposition of

dielectric layers, epitaxial growth, masking and photolithography, etching, metallization, surface and

bulk micromachining, LIGA process, wafer bonding.

MEMS system-level design methodology, Equivalent Circuit representation of MEMS, signal-

conditioning circuits, and sensor noise calculation.

Pressure sensors with embedded electronics (Analog/Mixed signal): Accelerometer with transducer,

Gyroscope

RF MEMS, Bolo meter

Optical MEMS, MEMS scaling issues

Reference Books:

1. Gandhi S.K., VLSI Fabrication principles, John Wiley and sons, 1983

2. Gregory T.A. Kovacs, Micromachined Transducers Sourecbook, The McGraw-Hill, Inc.

1998

3. Stephen D. Senturia, Microsystem Design, Kluar Publishers, 2001

4. Nadim Maluf, An Introduction to Microelectromechanical Systems Engineering, Artech

House, 2000.

5. M.H. Bao, Micro Mechanical Transducers, Volume 8, Handbook of Sensors and

Actuators, Elsevier, 2000.

6. Masood Tabib-Azar, Microactuators, Kluwer, 1998.

7. Ljubisa Ristic, Editor, Sensor Technology and Devices, Artech House, 1994

8. D. S. Ballantine, et. al.,Acoustic Wave Sensors, Academic Press, 1997

9. H. J. De Los Santos, Introduction to Micro electro- mechanical (MEM) Microwave

Systems, Artech, 1999.

10. James M.Gere and Stephen P. Timoshenko, Mechanics of Materials, 2nd Edition,

Brooks/Cole Engineering Division, 1984

SYLLABUS FOR M.TECH VLSI & EMBEDDED SYSTEMS (AUTONOMOUS) [2013 Scheme]

Department of E&C, NMAMIT, Nitte Page 33

VLSI SIGNAL PROCESSING

Sub. Code 13 VDE223 CIE Marks 50

Hrs./ week 4+0+0+0 SEE Marks 50

Total Hrs. 52 Credits 4

Exam Hrs 3

Introduction to DSP systems Data flow representations - Iteration Bound Pipelined and parallel

processing.

Retiming unfolding algorithmic strength reduction in filters and transforms.

Systolic architecture design fast convolution pipelined and parallel recursive and adaptive filters.

Scaling and round off noise digital lattice filter structures bit level arithmetic architecture

redundant arithmetic.

Numerical strength reduction synchronous, wave and asynchronous pipelines low power design

programmable digit signal processors & applications.

Reference Books:

R1. Keshab K. Parthi, VLSI Digital signal processing systems, Design and Implementaion, Wiley,

Inter Science, 1999.

R2. Mohammad Isamail, Terri Fiez, Analog VLSI signal and information processing, Mc Graw

Hill

R3. S.Y. Kung, H.J. White House, T. Kailath, VLSI and Modern Signal Processing, Prentice Hall,

1985.

You might also like

- Embedded System Design MethodologyDocument37 pagesEmbedded System Design Methodologykaushikei22No ratings yet

- RTOSDocument6 pagesRTOSRevathiMurugesan100% (1)

- How To Make A Contact-Less Digital Tachometer Using IR-light Reflection Technique - Embedded Lab PDFDocument13 pagesHow To Make A Contact-Less Digital Tachometer Using IR-light Reflection Technique - Embedded Lab PDFdevchandarNo ratings yet

- Crop Monitoring System With Atmega 64 AVR MicrocontrollerDocument87 pagesCrop Monitoring System With Atmega 64 AVR Microcontrollerchakradhar_jalla100% (1)

- Osa Multi TaskingDocument14 pagesOsa Multi TaskingTrebor PeñarockNo ratings yet

- Neural Network Full CourseDocument10 pagesNeural Network Full Coursekarthi kaiNo ratings yet

- Carry Save Adder VHDL CodeDocument16 pagesCarry Save Adder VHDL CodeAnónimo AnónimoNo ratings yet

- Rtos & Embedded Lab RecordDocument94 pagesRtos & Embedded Lab RecordYuvarajaNo ratings yet

- Embedded BookletDocument16 pagesEmbedded BookletpratikgoleNo ratings yet

- Embedded System Design IDocument2 pagesEmbedded System Design IMaha Lakshmi ShankarNo ratings yet

- BEE 049 - Design of Embedded System PDFDocument95 pagesBEE 049 - Design of Embedded System PDFSubhamNo ratings yet

- 1-Introduction To VHDLDocument23 pages1-Introduction To VHDLVedansh JainNo ratings yet

- Embedded System DesignDocument45 pagesEmbedded System Designsramuk100% (1)

- The Design of The Noise Detector Based On AT89C52 MicrocontrollerDocument5 pagesThe Design of The Noise Detector Based On AT89C52 MicrocontrollerUmar Rahamatullah ShareefNo ratings yet

- Digital Image ProcessingDocument143 pagesDigital Image ProcessingNaveenNo ratings yet

- Complete Embedded SystemDocument724 pagesComplete Embedded SystemKeval ShahNo ratings yet

- Embedded Systems and IotDocument5 pagesEmbedded Systems and IotAntonius BlockNo ratings yet

- EmbeddedC InterviewDocument7 pagesEmbeddedC InterviewaravindNo ratings yet

- FSM Design Using VHDLDocument19 pagesFSM Design Using VHDLrajivsharma1610No ratings yet

- E-Content Available in VTU Elearning Website (E-Notes and Lecture Videos) SL No Sub. Code Course NameDocument6 pagesE-Content Available in VTU Elearning Website (E-Notes and Lecture Videos) SL No Sub. Code Course Nameysuresh_bngNo ratings yet

- Image Processing VerilogDocument18 pagesImage Processing VeriloggoutamkgNo ratings yet

- Digital System Design Using VHDL PaperDocument2 pagesDigital System Design Using VHDL PaperlambajituNo ratings yet

- Iot Cisco NotesDocument45 pagesIot Cisco NotesKenny O'brien100% (1)

- EE8691 Embedded Systems NotesDocument76 pagesEE8691 Embedded Systems NotesMalik MubeenNo ratings yet

- Wireless Communication and RF System Design Using Matlab and SimulinkDocument40 pagesWireless Communication and RF System Design Using Matlab and SimulinkThương HDNo ratings yet

- 3D IC DFT Chen SNUGDocument9 pages3D IC DFT Chen SNUGUmesh ParasharNo ratings yet

- VLSI Mixed Signal DesignDocument346 pagesVLSI Mixed Signal DesignSiddharth TaunkNo ratings yet

- IBM ASIC-SoC MethodologyDocument12 pagesIBM ASIC-SoC Methodologyghatakp2069No ratings yet

- Image Processing Using Fpgas: ImagingDocument4 pagesImage Processing Using Fpgas: ImagingAnonymous s516rsNo ratings yet

- Digital To Analog Converter Some PapersDocument696 pagesDigital To Analog Converter Some Papersapi-19709566No ratings yet

- 1 hMATLAB - Simulink - TutorialDocument12 pages1 hMATLAB - Simulink - TutorialWasimNo ratings yet

- Rvfpga Getting Started Guide: The Imagination University ProgrammeDocument102 pagesRvfpga Getting Started Guide: The Imagination University ProgrammeSantosh LamaniNo ratings yet

- C Code Generation For A MATLAB Kalman Filtering Algorithm - MATLAB & Simulink Example - MathWorks IndiaDocument8 pagesC Code Generation For A MATLAB Kalman Filtering Algorithm - MATLAB & Simulink Example - MathWorks IndiasureshNo ratings yet

- PBG BCI RoboticsDocument5 pagesPBG BCI Roboticsbangalore2009No ratings yet

- Wiley - Digital Signal and Image Processing - 978-0-471-32727-1 PDFDocument2 pagesWiley - Digital Signal and Image Processing - 978-0-471-32727-1 PDFMayank AwasthiNo ratings yet

- Dsplabmanual-By 22Document64 pagesDsplabmanual-By 22debasnan singh100% (1)

- Install TensorFlow With Pip - TensorFlowDocument3 pagesInstall TensorFlow With Pip - TensorFlowMuhammadAqzaNo ratings yet

- Data Communication FaqDocument4 pagesData Communication Faqdolon10No ratings yet

- Cmos Image SensorsDocument10 pagesCmos Image Sensorsaleksandar.haNo ratings yet

- Simulation LaboratoryDocument102 pagesSimulation LaboratoryPUBG ASSASIN தமிழ் ASASSINNo ratings yet

- FDP BrochureDocument2 pagesFDP BrochureajbioinfoNo ratings yet

- Embedded RtosDocument111 pagesEmbedded RtoscespalaciosariasNo ratings yet

- Hardware Program Project Manager in San Francisco Bay CA Resume Evan ChangDocument2 pagesHardware Program Project Manager in San Francisco Bay CA Resume Evan ChangEvanChangNo ratings yet

- Final Comb Filter PPT - 2007Document19 pagesFinal Comb Filter PPT - 2007Subrat BarsainyaNo ratings yet

- Embedded Systems - Theory and Design MethodologyDocument440 pagesEmbedded Systems - Theory and Design Methodologyalex100% (1)

- Verilog ADocument75 pagesVerilog Amano6690No ratings yet

- CMOS Image Sensor Simulation: 2D and 3D SimulationDocument17 pagesCMOS Image Sensor Simulation: 2D and 3D Simulationnasamohd17No ratings yet

- Microcontroller ManualDocument91 pagesMicrocontroller ManualjayanthNo ratings yet

- B01Document49 pagesB01hrrameshhrNo ratings yet

- System Generator TutorialDocument33 pagesSystem Generator TutorialAthul KsNo ratings yet

- Shakti ReportDocument24 pagesShakti Reportsachin m cNo ratings yet

- 1-Introduction To NetworkingDocument18 pages1-Introduction To NetworkingmikeNo ratings yet

- VLSI Lab Manual - Digital Cirucit Design Using VHDLDocument82 pagesVLSI Lab Manual - Digital Cirucit Design Using VHDLSakthikumar Balasundaram100% (3)

- SkillDocument3 pagesSkillfixrouter4400No ratings yet

- Digital Video ProcessingDocument261 pagesDigital Video ProcessingmuthubeNo ratings yet

- Lecture 1 3Document62 pagesLecture 1 3Sivakumar PothirajNo ratings yet

- 1.3 Future Scaling: Where Systems and Technology Meet: 25 Digest of Technical PapersDocument5 pages1.3 Future Scaling: Where Systems and Technology Meet: 25 Digest of Technical Papersck maitiNo ratings yet

- FSM-based Specification Formalisms: Giovanni de MicheliDocument40 pagesFSM-based Specification Formalisms: Giovanni de MicheliKiran KumarNo ratings yet

- Tutorial 5Document31 pagesTutorial 5Sathish KumarNo ratings yet

- Computer Architecture: Instruction Set Principles (Part 3)Document32 pagesComputer Architecture: Instruction Set Principles (Part 3)Kiran KumarNo ratings yet

- DT04 Arcsyn ReneDocument36 pagesDT04 Arcsyn ReneKiran KumarNo ratings yet

- On Signal Tracing in Post-Silicon Validation: Qiang Xu Xiao LiuDocument6 pagesOn Signal Tracing in Post-Silicon Validation: Qiang Xu Xiao LiuKiran KumarNo ratings yet

- CachesDocument21 pagesCachesKiran KumarNo ratings yet

- Pres VeriLog PDFDocument64 pagesPres VeriLog PDFpraveen_banthiNo ratings yet

- DT2 (Model)Document61 pagesDT2 (Model)Kiran KumarNo ratings yet

- CH 1-Relations and FunctionsDocument32 pagesCH 1-Relations and FunctionsAnshuman SinghNo ratings yet

- Jeas 0415 1868 PDFDocument7 pagesJeas 0415 1868 PDFKiran KumarNo ratings yet

- Chap 8Document20 pagesChap 8mahawebNo ratings yet

- RISC Processor Design: Multi-Cycle Cycle Implementation: MipsDocument49 pagesRISC Processor Design: Multi-Cycle Cycle Implementation: MipsKiran KumarNo ratings yet

- Keil MicrovisionDocument157 pagesKeil MicrovisionM Praveen KumarNo ratings yet

- Vending Machine ControllerDocument10 pagesVending Machine ControllerRahul CharanNo ratings yet

- Performance Analysis of Positive Feedback Adiabatic Logic For Low PowerDocument7 pagesPerformance Analysis of Positive Feedback Adiabatic Logic For Low PowerKiran KumarNo ratings yet

- Ece5745 Tut1 VcsDocument7 pagesEce5745 Tut1 VcsKiran KumarNo ratings yet

- Arbitrary CounterDocument1 pageArbitrary CounterKiran KumarNo ratings yet

- Datapath 1Document58 pagesDatapath 1Rayasam RakhiNo ratings yet

- VerilogDocument62 pagesVerilogAkbar FacefactorNo ratings yet

- HW 1Document1 pageHW 1Kiran KumarNo ratings yet

- BCD Subtractor Ieee Format TermpaperDocument28 pagesBCD Subtractor Ieee Format TermpaperAmber AgrawalNo ratings yet

- EE5320: Analog Integrated Circuit Design Assignment 1Document2 pagesEE5320: Analog Integrated Circuit Design Assignment 1Kiran KumarNo ratings yet

- ARM AssyLang PDFDocument0 pagesARM AssyLang PDFtamilpannaiNo ratings yet

- Comparison of VHDL Verilog and SystemVerilogDocument7 pagesComparison of VHDL Verilog and SystemVerilogKiran KumarNo ratings yet

- Course Specifications: M. Tech. ProgrammeDocument12 pagesCourse Specifications: M. Tech. ProgrammeKiran KumarNo ratings yet

- 2014-05!04!21!32!47 SVAUdemy Lec18 AssertionsCoverageMiniProjMemControllerDocument3 pages2014-05!04!21!32!47 SVAUdemy Lec18 AssertionsCoverageMiniProjMemControllerKiran KumarNo ratings yet

- EcDocument10 pagesEcKiran KumarNo ratings yet

- Sifive Interrupt CookbookDocument34 pagesSifive Interrupt Cookbookrose jackNo ratings yet

- E1307 A140 OMMO1 Interpretation of Alarms B enDocument10 pagesE1307 A140 OMMO1 Interpretation of Alarms B enPunjabi Totay 2017No ratings yet

- Lec 1 OS UpdatedDocument50 pagesLec 1 OS UpdatedalapabainviNo ratings yet

- MCQ's of Operating System (OS)Document32 pagesMCQ's of Operating System (OS)Anik75% (8)

- Interrupts: 11.1 Interrupt Vectors in Atmega328PDocument1 pageInterrupts: 11.1 Interrupt Vectors in Atmega328PnamerNo ratings yet

- SoftICE Command ReferenceDocument274 pagesSoftICE Command ReferenceIput Abinya RoyzakNo ratings yet

- Os AssiDocument13 pagesOs Assiruvina khanNo ratings yet

- XEC-DN32H T9 Manual 1.9 202012 ENDocument236 pagesXEC-DN32H T9 Manual 1.9 202012 ENEloy Hernandez GonzalezNo ratings yet

- Precision Measurement An032 enDocument34 pagesPrecision Measurement An032 endbmNo ratings yet

- Health - Check - S5300-09.05.13 08-00-01Document79 pagesHealth - Check - S5300-09.05.13 08-00-01K.m.khizir AhmedNo ratings yet

- TLC 5924Document34 pagesTLC 5924Fábio LopesNo ratings yet

- STM32 Interrupt ModelDocument27 pagesSTM32 Interrupt Modelsuresh_bhudur100% (3)

- MPC 5500 Family - MicroprocessadorDocument24 pagesMPC 5500 Family - MicroprocessadorTiago LeonhardtNo ratings yet

- Microprocessor EXPERIMENT-12-Completed Bahria UniversityDocument6 pagesMicroprocessor EXPERIMENT-12-Completed Bahria Universitybusiness 1No ratings yet

- 3HAC18152-1 RevB enDocument70 pages3HAC18152-1 RevB enSusheel ShuklaNo ratings yet

- S7-200 ModbusDocument17 pagesS7-200 ModbusCiwa DoankNo ratings yet

- Qcpu Hardware Users ManualDocument214 pagesQcpu Hardware Users ManualcabatoNo ratings yet

- Signal Chain Benchmarking - A Demonstration of Optimized Performance of C2000™ Real-Time Control MCUDocument18 pagesSignal Chain Benchmarking - A Demonstration of Optimized Performance of C2000™ Real-Time Control MCUMauro Andre PagliosaNo ratings yet

- 1DS20LVS04 1DS20LVS010 Aat-3Document12 pages1DS20LVS04 1DS20LVS010 Aat-3Sanjay GowdaNo ratings yet

- AUTOSAR SWS FlexRayStateManagerDocument73 pagesAUTOSAR SWS FlexRayStateManagerStefan RuscanuNo ratings yet

- 6502 Technical ReferenceDocument127 pages6502 Technical ReferenceTrinummusNo ratings yet

- Generate Stepper-Motor Speed Profiles in Real Time: Login RegisterDocument17 pagesGenerate Stepper-Motor Speed Profiles in Real Time: Login RegisterAlex MercanNo ratings yet

- EC8691-MPMC SyllabusDocument2 pagesEC8691-MPMC SyllabusBalaji SriNo ratings yet

- TSN2101/TOS2111 - Tutorial 1 (Introduction To Operating Systems)Document5 pagesTSN2101/TOS2111 - Tutorial 1 (Introduction To Operating Systems)MoonNo ratings yet

- CS501 Solved MCQs Final TermDocument45 pagesCS501 Solved MCQs Final Termfakhira siddiqNo ratings yet

- Organization Blocks For Time Delay Interrupt (S7-1200/1500)Document2 pagesOrganization Blocks For Time Delay Interrupt (S7-1200/1500)Mehtab AhmedNo ratings yet

- 16z034 - Gpio - Gpio Controller Ip CoreDocument4 pages16z034 - Gpio - Gpio Controller Ip CoreVijayKumarVaijwadeNo ratings yet

- SF-104474-CD-20 Onload User GuideDocument265 pagesSF-104474-CD-20 Onload User GuideTerryNo ratings yet

- Embedded-and-Real-Time-Systems-2 Marks FinalDocument20 pagesEmbedded-and-Real-Time-Systems-2 Marks FinalranjaniNo ratings yet