Professional Documents

Culture Documents

8051 Microcontroller

Uploaded by

At TanwiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8051 Microcontroller

Uploaded by

At TanwiCopyright:

Available Formats

Chapters 0 and 1

1st hour: Chapter 0: review

2nd hour: Chapter 1: intro to MCU

Administrative:

textbook:

M. Mazidi, J. Mazidi, and R. McKinlay,

The 8051 Microcontroller and Embedded

Systems Using Assembly and C,

Pearson International Edition, 2006. ISBN:

0-13-197089-5

Number systems

Numbers vs. Numerals

Number = value

Numeral = text representation of number

Base of a numeral

Decimal: Base 10, Binary: Base 2

Octal: Base 8, Hexadecimal: Base 16

Mapping

decimal binary octal hex Roman

0 0000 0 0 ??

1 0001 1 1 I

2 0010 2 2 II

3 0011 3 3 III

4 0100 4 4 IV

5 0101 5 5 V

6 0110 6 6 VI

7 0111 7 7 VII

8 1000 10 8 VIII

9 1001 11 9 IX

10 1010 12 A X

11 1011 13 B XI

12 1100 14 C XII

13 1101 15 D XIII

14 1110 16 E XIV

15 1111 17 F XV

2's complement

to represent negative numbers

"ip all bits and add one"

example: (assume 8-bit words)

1 as binary: 00000001

-1 is binary: 11111110 + 1 => 11111111

Reason: use the same adder for + or -

test: 00000001 + 11111111 = 00000000

(ignore the carry, keep only lower 8 bits)

Character

representation

ASCII (American Standard Code for

Information Interchange)

Dec Char Dec Char Dec Char Dec Char Dec Char Dec Char

33 ! 49 1 65 A 81 Q 97 a 113 q

34 ~ 50 2 66 B 82 R 98 b 114 r

35 # 51 3 67 C 83 S 99 c 115 s

36 $ 52 4 68 D 84 T 100 d 116 t

37 % 53 5 69 E 85 U 101 e 117 u

38 & 54 6 70 F 86 V 102 f 118 v

39 ' 55 7 71 G 87 W 103 g 119 w

40 ( 56 8 72 H 88 X 104 h 120 x

41 ) 57 9 73 I 89 Y 105 i 121 y

42 * 58 : 74 J 90 Z 106 j 122 z

43 + 59 ; 75 K 91 [ 107 k 123 {

44 , 60 < 76 L 92 \ 108 l 124 |

45 - 61 = 77 M 93 ] 109 m 125 }

46 . 62 > 78 N 94 ^ 110 n 126 ~

47 / 63 ? 79 O 95 _ 111 o 127 _

48 0 64 @ 80 P 96 ` 112 p

AND NAND

OR NOR

INVERT buffer

XOR Tristate

Digital Logic

1

2

3

1

2

3

1 2

1

2

3

1

2

3

2

3

1

1 2

1

2

3

2

3

1

1 2

3

Combinational Logic vs.

Sequential Logic

Combinational

no memory ("stateless"); pure function

e.g., AND gate, OR gate, connected w/out

cycle

Sequential

has memory ("stateful")

built by combinational logic with feedback

mux

choose 1

from n

demux

from 1 to

one of n

decoder

binary to

unary

bit-adder

sum and

carry

Examples of

Combinational Logic

A

B

Cin

Sum

Cout

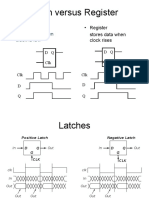

D-latch

remembers a new value every clock edge

D-ipop

remembers new value on clock edge AND

write-enable ("load")

Examples of Sequential

Logic

D

Clk

Q

D

Clk

Q

load

Synchronous vs.

Asynchronous logic

Both are sequential

Synchronous:

happens only with clock event

(rising edge or falling edge)

Asynchronous

not dependent on clock; happens any time

Most of the time, we use synchronous logic

More example of

sequential logic

Counter

each time, add 1

possible to reset

option to load

How to build it

D-register with +1 feedback

D

clk

load

count

Q adder

1

Memory

Conceptually: group of multiple D-ipops

Access to elements

Random access: give address

Sequential access: FIFO, LIFO (stack), ...

R/W

Read-only (can be viewed as combinational)

Read-Write

Register le

busA

<31:0>

Clk

busW

Write

Enable

32

32

busA

5 5

Rw Ra

32 32-bit

Registers

D<31:0>

load

clk

contains 32 registers, 3 shown

D<31:0>

load

clk

D<31:0>

load

clk

Clk

busW

1

:

3

2

d

e

m

u

x Write

Enable

Rw<4:0> Ra<4:0>

3

2

:

1

m

u

x

Q

Q

Q

Example with

32 registers

(5-bit addressable)

Bus

Shared electrical connection

Data, address, control

Internal or external

Serial or parallel

How to share?

Tri-state output

Arbitration policy

(master-slave, peer-to-peer, etc)

1 2

3

to bus

output

enable

ALU: Arithmetic and Logical

Unit

Data inputs (example: 32 bits)

AInput, BInput: operands

Control signal (3 bits for up to 8 operators)

ALUCtl: add, addu, sub, subu, and, or, xor, nor

Data output

Result: 32-bits

N, Z, C, V ags

32

32

ALUctl

ALU

N,Z,C,V

Result

AInput

BInput

32

3

What's inside an ALU?

Giant mux that inputs from Adder,

addu'er, ...

16

<31:0>

ALUctl

N,Z,C,V

Result

AInput

BInput

8

:

1

m

u

x

add

addu

sub

subu

and

or

xor

nor

AddOut

AdduOut

SubOut

SubuOut

AndOut

OrOut

XorOut

NorOut

MuxOut

<35:0>

<35:32>

Detailed connection of each unit

Giant mux that inputs from Adder,

addu'er, ...

17

<31:0>

ALUctl

N,Z,C,V

Result

AInput

BInput

8

:

1

m

u

x

add

addu

sub

subu

and

or

xor

nor

AddOut

AdduOut

SubOut

SubuOut

AndOut

OrOut

XorOut

NorOut

MuxOut

<35:0>

add

AInput

BInput

+

NZCV

AddOut

<35:0>

AddOut

<31:0>

AddOut

<35:32>

<31>

<35:32>

Structure of a CPU

Datapath

ALU

Register le

Control

Instruction decoder

Program counter

Program & Data memories, I/O

Reg

le

ALU

Data memory I/O

Microprocessors vs. MCU

Advantages of MCUs

Embedded systems

Choose a microcontroller

Speed, packaging, memory & cost per unit

Various members of 8051 family

Various manufacturers of 8051

Chapter 1: 8051

CPU vs. MCU vs.

embedded microproc.

Microprocessor, a.k.a. CPU

general purpose, usually w/out memory, I/O

Microcontroller (MCU)

CPU + integrated I/O for embedded apps

usually simpler (no MMU, no Floating Point)

Embedded Microprocessor

usually means higher-end CPU used in

embedded applications

8-bit MCU instruction-

set architectures

Older

6811 (formerly Motorola, now Freescale)

8051 (Intel), Z8 (Zilog), PIC 16 (Microchip)

Newer

ATMega (Atmel)

Hitachi H8

8-bit means registers (native data size) 8 bits

Block diagram of 8051

Intel allows others to make compatible MCUs

Atmel, Philips/Signetics, Siemens, Dallas

Semiconductor

New and improved

Silicon Labs (100MHz! low power, hi-perf)

Free designs available!

integrated RF (e.g., Nordic nRF24E1,

Chipcon CC2430, RadioPulse RG2400...)

Why 8051 is still popular

after 25 years

Feature 8051 8052 8031

ROM (on chip program

space in bytes)

4K 8k 0k

RAM (bytes) 128 256 128

Timers 2 3 2

I/O pins 32 32 32

Serial port 1 1 1

Interrupt sources 6 8 6

8051 Family

Question: how to

program?

Make ROM (cheap if large quantity)

Problem: you cannot change the program!

Make writable ROM

PROM: (P=programmable) write-once

EEPROM: electrically erasable PROM

UV-EPROM: erasable w/ultraviolet(UV) light

Flash: a type of EEPROM

NV-RAM: non-volatile RAM

EEPROM Programmer

and UV-Eraser

Flash memory

NAND-ash

cheaper, page access, erase whole page

before writing

good for data (e.g., digital camera)

NOR-ash

word addressable, more expensive

good for MCU program (rmware)

Limited number of rewrite cycles (10,000)

Package types

DIP (dual-inline package)

used in breadboards

PLCC (plastic leadless chip carrier)

removable from socket

BGA (ball-grid array)

connect on bottom

SMT (surface mount)

small or no leads

socket

Computing needs

Speed, packaging, power consumption,

RAM, ROM, I/O pins, timers, radio, cost

Voltage: TTL, CMOS, NMOS, ...

Software development tools

Assembler, debugger, C compiler, emulator,

technical support

Availability & source

Choosing a

Microcontroller

You might also like

- Transistor Switching and Sequential CircuitsFrom EverandTransistor Switching and Sequential CircuitsRating: 5 out of 5 stars5/5 (1)

- Practical Design of Digital Circuits: Basic Logic to MicroprocessorsFrom EverandPractical Design of Digital Circuits: Basic Logic to MicroprocessorsRating: 4.5 out of 5 stars4.5/5 (2)

- Latch Versus RegisterDocument23 pagesLatch Versus RegisterSGSNo ratings yet

- Clocking StrategiesDocument21 pagesClocking Strategiesswapnikasharma100% (1)

- L25 - Datapath Design - p1Document46 pagesL25 - Datapath Design - p1Shanawar AliNo ratings yet

- Chapter - 05 - Sequential CircuitsDocument43 pagesChapter - 05 - Sequential CircuitsThanh Diện NguyễnNo ratings yet

- Solution - Ass # 9 - CH 9 - s2016Document3 pagesSolution - Ass # 9 - CH 9 - s2016Abigail EngleNo ratings yet

- Sequential Circuits: Digital ElectronicsDocument10 pagesSequential Circuits: Digital ElectronicsAshu1803No ratings yet

- Sequential Circuits, Flip-Flops, Counters ExplainedDocument10 pagesSequential Circuits, Flip-Flops, Counters ExplainedAshu1803No ratings yet

- Registers Counters Finite State Machine (FSM) DesignDocument23 pagesRegisters Counters Finite State Machine (FSM) DesignRanveerNo ratings yet

- Sequential StaticDocument20 pagesSequential Staticvivek singhNo ratings yet

- ELE 4613 - ProjectDocument6 pagesELE 4613 - ProjectmukulNo ratings yet

- ELE-4613 Programmable Devices Baud Rate Generator ProjectDocument6 pagesELE-4613 Programmable Devices Baud Rate Generator ProjectMukul TanwarNo ratings yet

- 6004 Spring 1998: L10: Clocking and The Dynamic DisciplineDocument8 pages6004 Spring 1998: L10: Clocking and The Dynamic Disciplinemohammed zubairNo ratings yet

- VLSI Design I VLSI Design I VLSI Design I VLSI Design IDocument23 pagesVLSI Design I VLSI Design I VLSI Design I VLSI Design ISaksham sangwanNo ratings yet

- EO 301 NotesDocument31 pagesEO 301 Notessameer.anand.eee21No ratings yet

- Latches N FFsDocument24 pagesLatches N FFsAmoga LekshmiNo ratings yet

- Lecture 5Document51 pagesLecture 5abd rocksNo ratings yet

- ECE 545-Digital System Design With VHDL: Digital Logic Refresher Part B - Sequential Logic Building BlocksDocument20 pagesECE 545-Digital System Design With VHDL: Digital Logic Refresher Part B - Sequential Logic Building BlocksAli Mohamed EltemsahNo ratings yet

- Lec.1 .Document15 pagesLec.1 .kabeelm102No ratings yet

- Build Sequential Logic CircuitsDocument31 pagesBuild Sequential Logic CircuitsNavinaash Chanthra SegaranNo ratings yet

- A Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationDocument28 pagesA Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationVinitKharkarNo ratings yet

- ELE2120 Digital Circuits and Systems: Tutorial Note 8Document28 pagesELE2120 Digital Circuits and Systems: Tutorial Note 8SidhanNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogGaurav UpadhyayNo ratings yet

- VHDL Models of Sequential CircuitsDocument8 pagesVHDL Models of Sequential CircuitsbilgefNo ratings yet

- Static Sequential CircuitsDocument29 pagesStatic Sequential CircuitsfneojwgfjeNo ratings yet

- Chapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State UniversityDocument6 pagesChapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State Universitydemos2011No ratings yet

- Registers and Counters: PIPO, Shift RegistersDocument7 pagesRegisters and Counters: PIPO, Shift RegistersZoolJcNo ratings yet

- Latch Versus RegisterDocument23 pagesLatch Versus Registerfly2beyondgmail.comNo ratings yet

- Latches and Flip Flops CharacteristicsDocument13 pagesLatches and Flip Flops CharacteristicsWeaam RaedNo ratings yet

- Lab 1Document8 pagesLab 1Mulugeta AbebawNo ratings yet

- Latch Versus Register: Latch Stores Data When Clock Is LowDocument23 pagesLatch Versus Register: Latch Stores Data When Clock Is LowSrikrishna JanaNo ratings yet

- EncryptionDocument38 pagesEncryptionMohamed Kiwan100% (2)

- Experiment No - 04 Date: AimDocument7 pagesExperiment No - 04 Date: AimRaghav BansalNo ratings yet

- Digital Ic Design TutorialDocument4 pagesDigital Ic Design Tutorialkrishna kanthNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogKaleb FikreNo ratings yet

- Lecture 1Document35 pagesLecture 1زياد عبدالله عبدالحميدNo ratings yet

- Digital Logic Design No.6 (Counters and Registers)Document31 pagesDigital Logic Design No.6 (Counters and Registers)NaveedNo ratings yet

- Chapter 05 Sequential CircuitsDocument27 pagesChapter 05 Sequential CircuitsNguyen Yen NhiNo ratings yet

- Overview of Sequential Circuits Lecture and How They Enable Storing Bits in MemoryDocument9 pagesOverview of Sequential Circuits Lecture and How They Enable Storing Bits in MemoryKimberly Rose IlaganNo ratings yet

- PH36010 Numerical Methods: Solving Differential Equations Using MATHCADDocument32 pagesPH36010 Numerical Methods: Solving Differential Equations Using MATHCADbashasvuceNo ratings yet

- ArchL-Sequential Logic-03Document41 pagesArchL-Sequential Logic-03Ajax KrausNo ratings yet

- DelayDocument31 pagesDelayvarun186No ratings yet

- ITBP205 Digital Design and Computer Organization Memory ElementsDocument20 pagesITBP205 Digital Design and Computer Organization Memory ElementsJawad AadiNo ratings yet

- Filter Design and Implementation in 40 CharactersDocument66 pagesFilter Design and Implementation in 40 CharactersDilshan AnanthNo ratings yet

- ECE 545-Digital System Design With VHDL: Sequential Logic Review and Algorithmic State Machines 9/9/08Document29 pagesECE 545-Digital System Design With VHDL: Sequential Logic Review and Algorithmic State Machines 9/9/08Rahul TulsianiNo ratings yet

- Unit 6 Introduction To Sequential LogicDocument34 pagesUnit 6 Introduction To Sequential LogicTech Talk With MR. SNo ratings yet

- COMP 421 - Lec7 - RTL Register Transfer Languages 20142015 StudentsDocument28 pagesCOMP 421 - Lec7 - RTL Register Transfer Languages 20142015 StudentsmarklumbresNo ratings yet

- EE447 Lecture2Document48 pagesEE447 Lecture2Niresh BalajiNo ratings yet

- Lacthes and FlipflopsDocument30 pagesLacthes and FlipflopsNaveen KumarNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogKadal ChaitraNo ratings yet

- Digital Sequential CircuitsDocument77 pagesDigital Sequential CircuitsAnindra NallapatiNo ratings yet

- EECS 150 - Components and Design Techniques for Digital SystemsDocument41 pagesEECS 150 - Components and Design Techniques for Digital Systemsrifqi sutrisnoNo ratings yet

- Static Sequential XIDocument30 pagesStatic Sequential XISHOBHIT SHARMANo ratings yet

- 3 SequentialDocument25 pages3 SequentialABHI LIFENo ratings yet

- Retiming: Sequential digital circuit optimization for minimum delay and areaDocument33 pagesRetiming: Sequential digital circuit optimization for minimum delay and areaJay_NithNo ratings yet

- Lec 40Document16 pagesLec 40Tulus PramujiNo ratings yet

- IIT Kharagpur Prof Lecture Electrical Machines TransformerDocument17 pagesIIT Kharagpur Prof Lecture Electrical Machines TransformerDebayan BhattacharyaNo ratings yet

- DS1307 PDFDocument14 pagesDS1307 PDFtestzopNo ratings yet

- DS3231 Extremely Accurate I C-Integrated RTC/TCXO/Crystal: General Description Benefits and FeaturesDocument20 pagesDS3231 Extremely Accurate I C-Integrated RTC/TCXO/Crystal: General Description Benefits and FeaturesnovitaanggraheniNo ratings yet

- DJJ1012 - Class 02Document54 pagesDJJ1012 - Class 02MieSaidNo ratings yet

- Digital FIR Low-Pass Filter Design by Yankee Bush Software LLC - 2015Document20 pagesDigital FIR Low-Pass Filter Design by Yankee Bush Software LLC - 2015OANo ratings yet

- Finweek - December 3, 2015 PDFDocument48 pagesFinweek - December 3, 2015 PDFTulus PramujiNo ratings yet

- 105619r00ZB ZHC PTG-ZigBee Health Care Profile 1.0 Public PDFDocument56 pages105619r00ZB ZHC PTG-ZigBee Health Care Profile 1.0 Public PDFTulus PramujiNo ratings yet

- 4 Chip Board Assembly ManualDocument11 pages4 Chip Board Assembly ManualTulus Pramuji100% (1)