Professional Documents

Culture Documents

Diferencias Entre Procesadores CISC y RISC (Para Clases)

Uploaded by

Leo Montenegro0 ratings0% found this document useful (0 votes)

56 views3 pagesOriginal Title

Diferencias entre procesadores CISC y RISC (para clases).docx

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

56 views3 pagesDiferencias Entre Procesadores CISC y RISC (Para Clases)

Uploaded by

Leo MontenegroCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 3

Diferencias entre Procesadores CISC y RISC

Recopilacin hecha por la Ing. Patricia Ruiz

1

Para agregar a la pgina 4, de la Lectura N 9

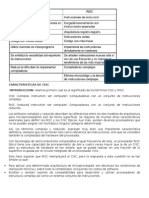

DIFERENCIAS ENTRE PROCESADORES CISC Y RISC:

CISC (Complex Instruction Set Computer, traducido: Computador con Conjunto de

Instrucciones Complejas): es un modelo de arquitectura de computadores.

CARACTERSTICAS:

1. Tienen un amplio repertorio de instrucciones.

2. Permite operaciones complejas entre operandos situados en la memoria o en

los registros internos (por ejemplo: los movimientos de cadenas de caracteres de

gran longitud y variable, en procesamiento de textos).

3. Las operaciones complejas requieren un nmero de pulsos que depende de la

secuencia de pasos necesarios para su ejecucin.

4. Debe contener una ROM de Control, que forma parte de la UC, para almacenar las

sucesivas combinaciones (microcdigos) que requiere la ejecucin de una

instruccin compleja.

5. Posee muchos Modos de Direccionamiento, para realizar la operacin que ordena

una instruccin.

6. Requiere un Compilador sencillo.

7. Hardware complejo.

8. Las instrucciones ocupan diferentes cantidades de bytes.

9. Menor velocidad que los RISC.

10. Menor nmero de registros de uso general de la CPU, que los RISC. Esto obliga a

utilizar ms instrucciones de LOAD-STORE, lo cual trae aparejado, en ms

accesos a MP respecto a los RISC.

11. Pierden mucho tiempo en las instrucciones de llamado a subrutinas y en las

interrupciones.

12. No incorporan un cach interno para instrucciones y otro para datos, salvo el

Pentium.

13. No puede aprovechar eficazmente su pipe line en la produccin de instrucciones,

debido a tener instrucciones ejecutables en diferentes pulsos de reloj.

Diferencias entre Procesadores CISC y RISC

Recopilacin hecha por la Ing. Patricia Ruiz

2

RISC (Reduced Instruction Set Computer, traducido: Computador con Conjunto de

Instrucciones Reducidas) es un tipo de diseo de CPU generalmente utilizado

en microprocesadores o microcontroladores.

CARACTERSTICAS:

1. Tiene un reducido repertorio de instrucciones.

2. Permite instrucciones muy simples (como las que ordenan sumar o restar dos

nmeros que estn en registros de la CPU y el resultado asignarlo a uno de esos

registros).

3. Las instrucciones simples, luego de su decodificacin, pueden ejecutarse en un

pulso de reloj (muy pocas requieren de dos pulsos de reloj).

4. No requiere una ROM de Control (de microcdigos).

5. Presentan muy pocos Modos de Direccionamiento.

6. Es necesario un Compilador complejo.

7. Requiere un hardware simple.

8. Las instrucciones son de formato fijo.

9. Mayor velocidad que los CISC.

10. La superficie que ocupara la ROM de Control, la aprovecha para aumentar el

nmero de registros de uso general de la CPU. Esto, permite utilizar menos

instrucciones de LOAD-STORE, lo cual trae aparejado, en menos accesos a MP

respecto a los CISC.

11. Como poseen un nmero elevado de registros, stos pueden utilizarse para el

manejo de llamados, en lugar de perder tiempo para escribir y leer la pila ubicada

en memoria.

12. Incorporan un cach interno para instrucciones y otro para datos, por necesidad

de velocidad.

13. Puesto que la mayora de las instrucciones se ejecutan en un pulso de reloj,

resulta un pipe line eficaz, terminndose de ejecutar, en promedio, una instruccin

por pulso reloj.

NOTA: pipeline: Los circuitos del hardware le permiten ejecutar varias instrucciones

paralelamente (simultneamente), de una forma solapada: se comienza con la prxima

instruccin cuando an no se termin de procesar la primera. Es un mtodo por el cual se

aumenta el rendimiento del funcionamiento en computadoras y dispositivos similares,

aplicndolo al microprocesador.

Diferencias entre Procesadores CISC y RISC

Recopilacin hecha por la Ing. Patricia Ruiz

3

You might also like

- Arquitectura CISC y RISCDocument10 pagesArquitectura CISC y RISCWilliams Alexander Trias AscanioNo ratings yet

- Informe RISC Vs CISCDocument7 pagesInforme RISC Vs CISCOlenka NahomyNo ratings yet

- Arquitectura Cisc y RiscDocument27 pagesArquitectura Cisc y RiscEucaris GarciaNo ratings yet

- Trabajo de Investigacion#1 Suñagua Aguilar Jhonattan JosueDocument7 pagesTrabajo de Investigacion#1 Suñagua Aguilar Jhonattan JosueFabian ParraNo ratings yet

- Introducción A Los Microprocesadores y MicrocontroladoresDocument4 pagesIntroducción A Los Microprocesadores y MicrocontroladoresOmar AguilarNo ratings yet

- Tecnologia Risc y CiscDocument5 pagesTecnologia Risc y CiscSonia CordovaNo ratings yet

- Arq. Comp - G7 - S2 - Arquitectura CISC RISCDocument14 pagesArq. Comp - G7 - S2 - Arquitectura CISC RISCJhonny Rojas MarcaNo ratings yet

- Arquitectura RISC Vs CISCDocument20 pagesArquitectura RISC Vs CISCEduardo SalazarNo ratings yet

- 05 - Arquitectura - CISC Vs RISCDocument36 pages05 - Arquitectura - CISC Vs RISCDamian ManzabaNo ratings yet

- Control de Microprocesadores Semana 2Document6 pagesControl de Microprocesadores Semana 2valdemar barrientosNo ratings yet

- Diferencia Entre Risc y CiscDocument9 pagesDiferencia Entre Risc y CiscMaria Isabel Fajardo DelgadoNo ratings yet

- Taller - Historia de La ComputaciónDocument7 pagesTaller - Historia de La ComputaciónSebastian GomezNo ratings yet

- 2 Características de La Arquitectura de RISC y CISCDocument6 pages2 Características de La Arquitectura de RISC y CISCLuisVillafuerteNo ratings yet

- Informe de Arquitecturas RISC Y CISCDocument13 pagesInforme de Arquitecturas RISC Y CISCJuan Carlos Romero Chalco0% (1)

- Tarea de Investigación 1 - Componentes de Hardware de Una Computadora PersonalDocument16 pagesTarea de Investigación 1 - Componentes de Hardware de Una Computadora PersonalOmar Cervantes GarcíaNo ratings yet

- Arquitecturas RISC y CISCDocument5 pagesArquitecturas RISC y CISCNadia JuarezNo ratings yet

- CPU o Procesador (Central Processing Unit)Document27 pagesCPU o Procesador (Central Processing Unit)Alejandro Torres PérezNo ratings yet

- Arquitectura RISCDocument9 pagesArquitectura RISCPili MiliNo ratings yet

- Risc CiscDocument13 pagesRisc CiscMary G RamirezNo ratings yet

- Resumen de Arquitectura de Computadoras Unidad IDocument5 pagesResumen de Arquitectura de Computadoras Unidad IAbelardo Martinez GonzalezNo ratings yet

- Arquitectura RISC y Arquitectura CISCDocument5 pagesArquitectura RISC y Arquitectura CISCSebas TNo ratings yet

- Tecnologia RISC Y CISC TrabajoDocument5 pagesTecnologia RISC Y CISC TrabajoEsteban Irusta ClaureNo ratings yet

- Analisis de Componentes CpuDocument16 pagesAnalisis de Componentes CpuJesús Melchor Hau NohNo ratings yet

- Arquitectura Cisc y RiscDocument18 pagesArquitectura Cisc y RiscsoldierelbalaNo ratings yet

- MicroI TeoriaDocument48 pagesMicroI Teoriaottoniel RosarioNo ratings yet

- Significado de Los Términos CISC y RISCDocument8 pagesSignificado de Los Términos CISC y RISCRandy EstradaNo ratings yet

- Diferencia CISC Vs RISCDocument3 pagesDiferencia CISC Vs RISCrodri2507No ratings yet

- Arquitectura RISC Vs CISCDocument25 pagesArquitectura RISC Vs CISCGiacinto DimambroNo ratings yet

- Risc y CiscDocument6 pagesRisc y CiscCamila CuevaNo ratings yet

- Microprocesadores Risc y CiscDocument15 pagesMicroprocesadores Risc y CiscErick GallupeNo ratings yet

- Características de Las Maquinas Con Tecnología Cisc y RiscDocument4 pagesCaracterísticas de Las Maquinas Con Tecnología Cisc y RiscEdwin SalinasNo ratings yet

- Desventajas Cisc y RiscDocument15 pagesDesventajas Cisc y RiscMilenka León ChavezNo ratings yet

- 1 Arquitectura RISC Vs CISCDocument6 pages1 Arquitectura RISC Vs CISCGerald AburtoNo ratings yet

- Grupo 5 - Resumen Unidad 5Document10 pagesGrupo 5 - Resumen Unidad 5Julio BonillaNo ratings yet

- Introduccion Risc y CiscDocument7 pagesIntroduccion Risc y CiscAldo ReignNo ratings yet

- Arquitectura RISC Vs CISCDocument10 pagesArquitectura RISC Vs CISCMario SaicoNo ratings yet

- Caracteristicas de Los PICDocument8 pagesCaracteristicas de Los PICt_toyoNo ratings yet

- Equipo - 4 DISEÑO DE CONJUNTO DE INSTRUCCIONESDocument88 pagesEquipo - 4 DISEÑO DE CONJUNTO DE INSTRUCCIONESAlanNo ratings yet

- Caracteristicas de CiscDocument3 pagesCaracteristicas de CiscWilliam Fernando Garcia100% (1)

- Risc y SiscDocument4 pagesRisc y SiscJuan Carlos Chaufon Cruz100% (1)

- Arquitectura RISC Vs CISCDocument9 pagesArquitectura RISC Vs CISCRaul CrookersNo ratings yet

- Tema 2. PIC-Arquitectura Lógica PDFDocument25 pagesTema 2. PIC-Arquitectura Lógica PDFRaquel UmañaNo ratings yet

- Taller #1 - Grupo ADocument6 pagesTaller #1 - Grupo ABryan PxNo ratings yet

- Arquitectura RISC Vs CISCDocument10 pagesArquitectura RISC Vs CISCVictor TomatsuNo ratings yet

- Arquitectura RISC y CISCDocument10 pagesArquitectura RISC y CISCUsiel RTNo ratings yet

- Miguel Jofre S2 Tarea MicrocontroldoresDocument6 pagesMiguel Jofre S2 Tarea MicrocontroldoresMiguel JofreNo ratings yet

- Rodrigo Soto Tarea2Document6 pagesRodrigo Soto Tarea2rodrigoNo ratings yet

- Cisc y RiscDocument5 pagesCisc y RiscIta GSNo ratings yet

- Unidad V - Estructura y Arquitectura Del ComputadorDocument8 pagesUnidad V - Estructura y Arquitectura Del ComputadorGregory VerasNo ratings yet

- Arquitectura Cisc Vs RiscDocument6 pagesArquitectura Cisc Vs RiscFernando ZapataNo ratings yet

- Cisk Vs RiskDocument9 pagesCisk Vs RiskWilberth Antonio Tuz SegoviaNo ratings yet

- Ciclo FetchDocument8 pagesCiclo FetchalejandraNo ratings yet

- Arquitectura CISCDocument6 pagesArquitectura CISCNayeli MayoNo ratings yet

- Procesadores RISCDocument15 pagesProcesadores RISCRonny AláNo ratings yet

- Ensayo Arquitectura Risc y CiscDocument6 pagesEnsayo Arquitectura Risc y CiscJCARLOS_CUEVAS_No ratings yet

- Arquitectura Interna de Un MicrocontroladorDocument8 pagesArquitectura Interna de Un MicrocontroladorOscar OrtizNo ratings yet

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeFrom EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeNo ratings yet

- UF0852 - Instalación y actualización de sistemas operativosFrom EverandUF0852 - Instalación y actualización de sistemas operativosRating: 5 out of 5 stars5/5 (1)

- Arquitectura de MicrocontroladoresDocument16 pagesArquitectura de MicrocontroladoresOdalis Berenice Montejo VictoriaNo ratings yet

- Procesos y Diagramas SIPOCDocument59 pagesProcesos y Diagramas SIPOCRo Saul Cohen75% (4)

- Practica 2Document3 pagesPractica 2davidNo ratings yet

- 1 Estructura de Los Autómatas PDFDocument95 pages1 Estructura de Los Autómatas PDFAlfredo GuzNo ratings yet

- Optimizando El Rendimiento Gráfico en UnityDocument6 pagesOptimizando El Rendimiento Gráfico en UnityatolonioNo ratings yet

- Sewer CadDocument83 pagesSewer CadGuillermo Del Valle100% (1)

- Práctica U3Document15 pagesPráctica U3Aldo ArgudinNo ratings yet

- Distribución Lógica de Una ComputadoraDocument12 pagesDistribución Lógica de Una ComputadoraJosé GonzálezNo ratings yet

- Estacion de Toma de DatosDocument9 pagesEstacion de Toma de DatosbetobagreNo ratings yet

- Señalización Por Canal Común o CCSDocument2 pagesSeñalización Por Canal Común o CCSMathias RSNo ratings yet

- ODROID Magazine 201411 EspanolDocument33 pagesODROID Magazine 201411 EspanolJhoony ZeladaNo ratings yet

- Curso Control Secuencial PLCDocument139 pagesCurso Control Secuencial PLCLogtown EasthNo ratings yet

- Unidad 1Document57 pagesUnidad 1Jamileth ArmijosNo ratings yet

- TP 1 - Introducción A Los Sistemas ConcurrentesDocument3 pagesTP 1 - Introducción A Los Sistemas ConcurrentesRosario RaffoNo ratings yet

- Guía Del Pic 16f84Document17 pagesGuía Del Pic 16f84b6dicNo ratings yet

- Adc 1.4 Introducción Arquitectura de ComputadorasDocument4 pagesAdc 1.4 Introducción Arquitectura de ComputadorasJuan RodriguezNo ratings yet

- Tema1 - Fundamentos Del Diseño y Evolución de Los ComputadoresDocument24 pagesTema1 - Fundamentos Del Diseño y Evolución de Los ComputadoresRosa Isabel Diaz de MuentesNo ratings yet

- Sistemas Operativos Por LotesDocument9 pagesSistemas Operativos Por LotesMaicol RaizorNo ratings yet

- Planificacion de Tecnologia 5 Basico JunioDocument4 pagesPlanificacion de Tecnologia 5 Basico JunioPatricia Alejandra Perez SeguraNo ratings yet

- 02 Grafos ComputacionDocument33 pages02 Grafos ComputacionManuel PalominoNo ratings yet

- Administracion de Recursos SolarisDocument46 pagesAdministracion de Recursos Solarisjoem20100% (1)

- Tipos ComputadorDocument7 pagesTipos ComputadorHENRY LEONIDAS ALZATE GUERRERONo ratings yet

- 16 FCFSDocument5 pages16 FCFSAlejo PighinNo ratings yet

- Reparacion de Tarjeta MadreDocument27 pagesReparacion de Tarjeta MadreHUMORNICA 02No ratings yet

- Cuestionario Electrónica Digital AplicadaDocument6 pagesCuestionario Electrónica Digital AplicadaCarlos MartinezNo ratings yet

- Kone Monospace Español Norma RamosDocument82 pagesKone Monospace Español Norma RamosBeltran Héctor100% (1)

- Controlador Logico Programable PLCDocument25 pagesControlador Logico Programable PLCJosep LopezNo ratings yet

- Registrador Grafico Circular Abb C1900 Guia de Operacion PDF SpanishDocument20 pagesRegistrador Grafico Circular Abb C1900 Guia de Operacion PDF SpanishJosue Isaias Lopez RomeroNo ratings yet

- Optimizar DebianDocument6 pagesOptimizar DebianIvan BorjasNo ratings yet

- Instalación Sistema GeovisionDocument34 pagesInstalación Sistema GeovisioncruzpiaNo ratings yet