Professional Documents

Culture Documents

Código Hamming Completo

Uploaded by

juliedmr060 ratings0% found this document useful (0 votes)

160 views20 pagesOriginal Title

Código Hamming Completo.docx

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

160 views20 pagesCódigo Hamming Completo

Uploaded by

juliedmr06Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 20

Repblica Bolivariana De Venezuela

Ministerio Del Poder Popular Para La Defensa

Universidad Experimental Politcnica De Las Fuerzas Armadas

UNEFA- Ncleo Sucre

CDIGO HAMMING.

Profesor: Luis Rodrguez

Integrantes:

Julied Mrquez

Rosa Rodrguez

Alfremar Ramrez

Marielys Villalba

Maringeles Sanes

Seccin: 03

Ing. De Telecomunicaciones

Cuman, septiembre de 2014.

INTRODUCCIN

Hamming trabaj en los Laboratorios Bell en la dcada de 1940 en el

Modelo V ordenador Bell, una mquina basada en rels electromecnicos

con tiempos de ciclo en segundos. En las telecomunicaciones los cdigos de

Hamming son una familia de lineal cdigos de correccin de errores que

generalizan el cdigo de Hamming inventado por Richard Hamming en 1950.

Los cdigos Hamming pueden detectar hasta dos y corregir hasta un error de

bit. Por el contrario, el cdigo de paridad simple no puede corregir los

errores, y puede detectar slo un nmero impar de errores. Los cdigos de

Hamming son especiales ya que son cdigos perfectos, es decir, que

alcanzan la tasa ms alta posible para los cdigos con su longitud de bloque

y la distancia mnima la cual es de tres.

Por otro lado, en trminos matemticos, los cdigos de Hamming son

una clase de cdigos lineales binarios. Para cada nmero entero hay un

cdigo con longitud de bloque y la longitud del mensaje. Por lo tanto la tasa

de cdigos de Hamming plantea que es ms alta posible para los cdigos

con la distancia y la longitud de bloque. La matriz de comprobacin de

paridad de un cdigo de Hamming se construye haciendo una lista de todas

las columnas de longitud que no son cero, lo que significa que el cdigo de

doble del cdigo de Hamming es el cdigo Hadamard pinchado. La matriz de

comprobacin de paridad tiene la propiedad de que cualquiera de las dos

columnas se pairwise linealmente independientes.

Adems, los cdigos de Hamming slo pueden aadir muy poca

redundancia a los datos, y por lo tanto, slo se pueden detectar y corregir

errores si hay casi nada de ruido. Este es el caso en la memoria del

ordenador, donde los errores de bits son extremadamente raros y los cdigos

de Hamming se usan ampliamente. En este contexto, a menudo se utiliza un

cdigo de Hamming extendido con un bit de paridad adicional. Los cdigos

de Hamming permiten alcanzar ciertas distancias las cuales permiten al

decodificador distinguir entre la situacin en la que se produjo un error de

bit y la situacin en la que se produjeron dos errores de bit.

CDIGO HAMMING.

Es un cdigo detector y corrector de errores que lleva el nombre de su

inventor, Richard Hamming. En los datos codificados en Hamming se pueden

detectar errores en un bit y corregirlos, sin embargo no se distingue entre

errores de dos bits y de un bit; para ello se usa Hamming extendido. Esto

representa una mejora respecto a los cdigos con bit de paridad, que pueden

detectar errores en slo un bit, pero no pueden corregirlo.

Explicacin del Cdigo Hamming.

Si se aaden junto al mensaje ms bits detectores-correctores de error

y si esos bits se pueden ordenar de modo que diferentes bits de error

producen diferentes resultados, entonces los bits errneos podran ser

identificados. En un conjunto de siete bits, hay slo siete posibles errores de

bit, por lo que con tres bits de control de error se podra especificar.

Hamming estudi los esquemas de codificacin existentes, incluido el

de dos entre cinco, y generaliz sus conclusiones. Para empezar, desarroll

una nomenclatura para describir el sistema, incluyendo el nmero de los bits

de datos y el de los bits detectores-correctores de error en un bloque. Por

ejemplo, la paridad incluye un solo bit para cualquier palabra de datos, as

que las palabras del Cdigo ASCII que son de siete bits, Hamming las

describa como un cdigo (8.7), esto es, un total de 8 bits de los cuales 7 son

datos. Con base a la anterior repeticin, sera un cdigo (3.1), siguiendo la

misma lgica. La relacin de la informacin es el segundo nmero dividido

por el primero, por nuestro ejemplo de la repeticin, 1/3.

Tambin estudi los problemas que surgan al cambiar dos o ms bits

a la vez y describi esto como distancia; la cual es ahora llamada distancia

de Hamming en su honor. La paridad tiene una distancia de 2, dado que

cualquier error en dos bits no ser detectado. La repeticin (3.1) tiene una

distancia de 3, pues es necesario el cambio simultneo de tres bits para

obtener otra palabra de cdigo. La repeticin (4.1), es decir; cada bit se

repite cuatro veces, tiene una distancia de 4; as que el cambio de dos bits

en el mismo grupo quedar sin definir.

Hamming estaba interesado en solucionar simultneamente dos

problemas: aumentar la distancia tanto como sea posible, a la vez que se

aumentan al mximo los bits de informacin. Durante los aos 40 desarroll

varios esquemas de codificacin que mejoraban notablemente los cdigos

existentes. La clave de todos sus sistemas era intercalar entre los bits de

datos los de paridad.

Hoy, el cdigo de Hamming se refiere al (7.4) que Hamming introdujo

en 1950. El cdigo agrega tres bits adicionales de comprobacin por cada

cuatro bits de datos del mensaje. El algoritmo de Hamming (7.4) puede

corregir cualquier error de un solo bit, pero cuando hay errores en ms de un

bit la palabra transmitida se confunde con otra, con error en un slo bit

siendo corregida, pero de forma incorrecta; es decir que la palabra que se

corrige es otra distinta a la original, y el mensaje final ser incorrecto sin

saberlo. Para poder detectar; aunque sin corregirlos, errores de dos bits se

debe aadir un bit ms, y el cdigo se llama Hamming extendido. El

algoritmo es el siguiente:

1. Todos los bits cuya posicin es potencia de dos se utilizan como

bits de paridad (posiciones 1, 2, 4, 8, 16, 32, 64, etc.).

2. Los bits del resto de posiciones son utilizados como bits de datos

(posiciones 3, 5, 6, 7, 9, 10, 11, 12, 13, 14, 15, 17, etc.).

3. Cada bit de paridad se obtiene calculando la paridad de alguno de

los bits de datos. La posicin del bit de paridad determina la secuencia de los

bits que alternativamente comprueba y salta, a partir de ste, tal y como se

explica a continuacin. Posicin 1: salta 0, comprueba 1, salta 1, comprueba

1, entre otros. Posicin 2: salta 1, comprueba 2, salta 2, comprueba 2, etc.

Posicin 4: salta 3, comprueba 4, salta 4, comprueba 4, etc. Posicin 8: salta

7, comprueba 8, salta 8, comprueba 8, etc. Posicin 16: salta 15, comprueba

16, salta 16, comprueba 16, etc. Regla general para la posicin n es: salta n-

1 bits, comprueba n bits, salta n bits, comprueba n bits. Y as sucesivamente.

En otras palabras, el bit de paridad de la posicin comprueba los bits en las

posiciones que tengan al bit k en su representacin binaria. Dicho a la

inversa, el bit 4, chequea los bits 4, 5, 6, 7, al ser estos los de su

representacin binaria: 4=100(2), 5=101(2), 6=110(2) y 7=111(2). Por el

contrario, el mismo bit de paridad no comprueba el bit 8, debido a que en su

representacin binaria el bit nmero 3 (=4) es igual a 0 (8=1000B). As, por

ejemplo, para los primeros trminos se tiene: En la Posicin 1 (2^0 = 1),

comprobaramos los bits: 1, 3, 5, 7, 9, 11, 13... En la Posicin 2 (2^1 = 2), los

bits: 2, 3, 6, 7, 10, 11, 14, 15... En la Posicin 4 (2^2 = 4), los bits: 4, 5, 6, 7,

12, 13, 14, 15, 20, 21, 22, 23... En la Posicin 8 (2^3 = 8) tendramos: 8, 9,

10, 11, 12, 13, 14, 15, 24-31... Siguiendo el algoritmo hasta completar la

nueva cadena.

Ejemplo.

Considere la palabra de datos de 7 bits "0110101". Para ver cmo se

generan y utilizan los cdigos Hamming para detectar un error, observe las

tablas siguientes. Se utiliza la d para indicar los bits de datos y la p para los

de paridad.

En primer lugar los bits de datos se insertan en las posiciones

apropiadas y los bits de paridad calculados en cada caso usando la paridad

par.

P1 = D1 exor D2 exor D4 exor D5 exor D7

P2 = D1 exor D3 exor D4 exor D6 exor D7

P3 = D2 exor D3 exor D4

P4 = D5 exor D6 exor D7

La nueva palabra de datos (con los bits de paridad) es ahora

"10001100101". Consideremos ahora que el bit de la derecha, por error,

cambia de 1 a 0. La nueva palabra de datos ser ahora "10001100100".

Sin errores.

Comprobacin de los bits de paridad (con primer bit de la derecha sin cambiar).

Clculo de los bits de paridad en el cdigo Hamming

Con errores.

Si se analiza en la tabla anterior la paridad que se debe obtener a la

derecha tras la llegada del mensaje sin errores debe ser siempre 0 (por cada

fila), pero en el momento en que ocurre un error esta paridad cambia a 1, de

all el nombre de la columna "prueba de paridad 1". Se observa que en la fila

en que el cambio no afect la paridad es cero y llega sin errores.

El paso final es evaluar los bits de paridad (el fallo se encuentra en

d

7

). El valor entero que representan los bits de paridad es 11 (si no hubieran

ocurrido errores este valor seria 0), lo que significa que el bit dcimo primero

de la palabra de datos (bits de paridad incluidos) es el errneo y necesita ser

cambiado.

Cambiando el bit dcimo primero 10001100100 se obtiene de nuevo

10001100101. Eliminando los bits de patrn de la paridad no se tienen en

cuenta los bits de paridad. Si el error se produjera en uno de ellos, en la

comprobacin slo se detectara un error, justo el correspondiente al bit de

paridad causante del mismo.

Comprobacin de los bits de paridad (con primer bit de la derecha cambiado)

Hamming Extendido.

Para detectar errores en 2 bits se utiliza un bit adicional de paridad

(Hamming Extendido) donde puede darse el caso de 3 posibilidades:

Cdigos pre-Hamming

Antes de los cdigos Hamming se utilizaron ciertos cdigos detectores

de error, como lo fueron el cdigo linteing, pero ninguno lleg a ser tan eficaz

como los de Hamming. A continuacin se describen algunos de estos

cdigos.

Paridad.

La paridad consiste en aadir un bit, denominado bit de paridad, que

indique si el nmero de los bits de valor 1 en los datos precedentes es par o

impar. Si un solo bit cambiara por error en la transmisin, el mensaje

cambiar de paridad y el error se puede detectar (ntese que el bit donde se

produzca el error puede ser el mismo bit de paridad). La convencin ms

comn es que un valor de paridad 1 indica que hay un nmero impar de unos

en los datos, y un valor de paridad de 0 indica que hay un nmero par de

unos en los datos.

La comprobacin de paridad no es muy robusta, dado que si cambia

de forma uniforme un nmero par de bits, el bit de paridad ser vlido y el

error no ser detectado. Se utiliza cuando se cumplen simultneamente dos

condiciones: que la probabilidad de que falle un bit es baja y que las fallas de

bits son sucesos independientes. De esta forma la probabilidad de que fallen

dos (o ms) bits es muy baja, por lo que cuando no detecta error es

altamente probable que el cdigo sea efectivamente correcto. Cabe destacar

que dichas condiciones se ajustan al caso de las memorias de las

computadoras modernas pero no ocurre lo mismo con los dispositivos de

almacenamiento que guardan la informacin en forma serial (un bit a

continuacin de otro) ni con los sistemas de transmisin de datos seriales ya

que en estos casos el hecho que falle un bit est vinculado, en forma no

despreciable, a la falla de otro adyacente.

Por otro lado, la paridad, aunque puede detectar que hay error, no

indica en qu bit se cometi. Los datos se deben desechar por entero y

volverse a transmitir. En un medio ruidoso, una transmisin correcta podra

tardar mucho tiempo o incluso, en el peor de los casos, no darse nunca. El

chequeo de paridad, aunque no es muy bueno, usa un nico bit, por lo que

produce muy poca sobrecarga, y adems permite la correccin de ese bit si

es conocida su posicin.

Dos entre cinco.

En los aos 40, Bell utiliz un cdigo algo ms sofisticado conocido

como dos-entre-cinco. Este cdigo se basa en que cada bloque de cinco bits

(conocido como penta-bit) tuviera exactamente dos unos, asegurando as

que tenga una Distancia de Hamming igual a dos. De este modo, la

computadora podra detectar posibles errores cuando en su entrada no haba

exactamente dos unos en cada penta-bit.

Este cdigo segua nicamente detectando errores por cambio en un

solo bit; si en un mismo penta-bit un 0 cambiaba a 1 y un 1 cambiaba a 0, la

regla de dos-entre-cinco se segua cumpliendo y el error quedaba sin

descubrir.

Repeticin.

Este cdigo consista en repetir cada bit de datos varias veces para

asegurarse de que la transmisin era correcta. Por ejemplo, si el bit de datos

que se enva fuera un 1, un cdigo de repeticin con n=3, enviara "111". Si

los tres bits recibidos no eran idnticos, haba un error. En un ambiente sin

demasiado ruido, la mayora de las veces solamente cambiara un bit en

cada paquete de tres bits. Por lo tanto, datos del tipo 001, 010, y 100 se

corresponden al bit 0, mientras que 110, 101, y 011 se corresponden con el

bit 1. Es como si el bit original se obtuviera por mayora en una "votacin". Un

cdigo con esta capacidad de reconstruir el mensaje original en la presencia

de errores se conoce como cdigo corrector de errores.

Sin embargo, este cdigo no puede reparar correctamente todos los

errores. En nuestro ejemplo, si el error en la transmisin provocara el cambio

simultneo de dos bits y el receptor recibiera "001", el sistema detectara el

error, pero considerando que el bit original era 0, lo cual es incorrecto. Si se

aumenta el nmero de veces que se repite cada bit a cuatro (n=4), es posible

detectar los errores en dos bits pero obviamente no se podrn corregir; con

cinco, es posible corregir errores de dos bits, pero no lo podr hacer en

errores de tres bits.

Por otra parte, el cdigo de la repeticin es extremadamente ineficaz,

pues reduce la velocidad de transmisin por tres en nuestro ejemplo original

y su eficacia cae drsticamente al aumentar el nmero de veces que cada bit

se repite para detectar y corregir ms errores. El uso del cdigo de bloques

no lineales para deteccin de errores no es muy implementado por lo tanto

emplearemos el cdigo de errores lineales para la correccin de errores.

Chequeo por Paridad.

Paridad Horizontal y Vertical.

La paridad horizontal y vertical es utilizada en algunos cdigos de bloque

para una combinacin de chequeo de (LRC / VRC) para detectar errores. El

LRC: Longitudinal Redundancy Checking ("Chequeo de Redundancia

Horizontal") y el VRC: Vertical Redundancy Checking ("Chequeo de

Redundancia Vertical").

Proceso.

El proceso para calcular la paridad de bloque es el siguiente:

Los caracteres a transmitir se agrupan en bloques de n filas y m

columnas.

Se calcula el bit de paridad de cada fila y se aade al principio (o al

final, segn convenio) de la fila.

Se calcula el bit de paridad de cada columna y se aade al principio (o

al final, segn convenio) de la columna.

El bloque final a transmitir tendr por tanto una fila y una columna ms

que el original.

La nueva columna estar formada por los bits de paridad horizontal de

todas las filas.

La nueva fila estar formada por los bits de paridad vertical de todas

las columnas.

Adicionalmente se emplea un bit de paridad cruzada que se calcula a

partir de los bits de paridad de filas y columnas.

Los chequeos de paridad horizontal y vertical se usan para detectar y

corregir los posibles errores que se puedan producir durante la transmisin

de datos.

En el siguiente ejemplo se chequea la paridad de un bloque de 48 bits,

distribuido en 6 filas de 8 bits cada una. Se usa paridad par.

Paridad Par o Impar

Un recurso sencillo para determinar si se han producido

reagrupamientos de bits durante la transmisin o el procesamiento consiste

en agregar un bit de paridad a los que ya representan a cada carcter. Si

agregamos un bit 1 de paridad solo a aquellos caracteres con l nmero

impar de bits 1 que les corresponde, obtendremos un cdigo en el cual todos

los caracteres estn integrados por un nmero par de bits 1. As, con

invertirse el valor de un bit se produce una combinacin no valida (impar).

Este mtodo de paridad impar o par es un caso particular del caso M de N.

Chequeo de Paridad Vertical (VRC).

Es un mtodo simple, aplicable a nivel byte. Su uso esta directamente

relacionado con el cdigo ASCII. El mtodo de codificacin de smbolos

ASCII, utiliza los valores binarios obtenidos con 7 bits para representar los

datos. El mximo valor binario representable es 7F(hex)=127(dec), por lo

tanto se tienen 128 posibilidades distintas (de 0 a la 127).

Se definen la "paridad" de un carcter en dos maneras:

Paridad "par", cuando l nmero total de bits en "1" en el byte es par.

Paridad "impar", cuando l nmero total de bits en "1" es impar.

En el momento de la transmisin, el extremo emisor calcula el bit de

paridad y lo adosa a los datos. El receptor recalca la paridad y la compara

con el criterio utilizado.

Este mtodo no asegura que no hayan ocurrido errores. Basta que

cambie su valor dos bits de datos simultneamente para que la paridad sea

correcta pero el dato no. VRC disminuye la paridad de que el dato final sea

errneo.

Chequeo de Paridad Longitudinal (LRC).

Si en lugar de considerar 7 bits como el dato a trasmitir en el momento de

calcular la paridad, consideramos un conjunto de caracteres con sus bits de

VRC y sobre esto calculamos la paridad, estaremos usando LRC.

Tomando el i-simo bit de cada byte y calculando a partir de ellos el bit de

paridad resultante obtendremos el i-simo bit del "BCC", para y variando

entre 1 y 8. Cuando se usa LRC, se agrega a un carcter al final del mensaje

que contiene todos los bits de paridad calculados como se dijo

anteriormente. Este byte adicional, se llama BCC (Block Check Character).

Chequeo Bidimensional.

El uso combinado de los mtodos vertical y longitudinal se conoce como

chequeo bidimensional.

Con el vertical obtendremos la abscisa y con la longitudinal la ordenada

del punto (bit) errneo, con una gran probabilidad de acierto. Parte de los

errores no filtrados por el vertical, pueden detectarse con esta tcnica

combinada.

Paridad Horizontal y Vertical.

Cuando se agrega un bit a cada grupo de bits que representan un

carcter en la forma que hemos descrito, la paridad se denomina vertical. El

nombre viene de la posicin relativa de los bits, si los observamos sobre la

cinta de papel en sentido longitudinal. La paridad horizontal, como se podra

suponer, resulta de agregar un bit al final del bloque de bits a lo largo de la

cinta. Si damos paridad horizontal a cada uno de los caracteres de la cinta,

se formara un carcter de paridad a continuacin por los caracteres de

informacin.

El uso de una paridad horizontal y vertical combinadas permite

superar una de las mayores desventajas que estos esquemas ofrecen por

separado: la incapacidad para localizar con exactitud el o los bits errneos.

En la matriz que se ilustra en la siguiente figura, el medio de recepcin ha

verificado la paridad horizontal y vertical de los caracteres entrantes e

identificado aquellos errneos debido a que su paridad no es la correcta.

Invirtiendo de los bits equivocados, el dispositivo receptor puede corregir el

carcter.

Aun cuando el esquema de paridad horizontal y vertical combinadas

ofrece mucha ms proteccin que cualquiera de ellas individualmente,

presenta un problema, y es que una codificacin rectangular de errores

pasara inadvertida. En la siguiente figura se mostrara una situacin posible

(pero muy improbable) en la cual los errores no seran detectados mediante

el empleo de paridad combinada horizontal y vertical. Si una fuente

perturbadora y generadora de errores invirtiese el valor de los bits marcados

con un crculo, los bits de paridad seguiran siendo vlidos y el error no sera

notado.

Errores no detectados por Paridad combinada Horizontal y Vertical.

Paridad Entrelazada

Para salvar en cierta medida este inconveniente de la paridad horizontal y

vertical se puede emplear otro mtodo de deteccin de errores, denominado

paridad entrelazada. Esta tcnica requiere dos bits de paridad por carcter:

uno de paridad par o impar para los bits primero, tercero y quinto de un

cdigo de seis bits, y el otro, tambin de paridad, para los bits que estn en

segundo, cuarto y sexto lugar, como lo muestra la figura, se formara la

paridad entrelazada de un carcter de seis bits. La paridad entrelazada

puede reducir enormemente la posibilidad de que un error pase sin ser

detectado, comparndola con la de un sistema sin verificacin. Este mtodo

se denomina tambin verificacin de redundancia cclica.

Generacin de Paridad Entrelazada Par.

Todo sistema de control de errores por paridad tiene un inconveniente

ms: la posibilidad de que la misma paridad sea recibida con error. A menos

que el error de informacin coincida exactamente con el otro; ser detectado

y podr corregirse por retransmisin.

CONCLUSIONES

Las principales contribuciones a la ciencia de Hamming fueron

el cdigo Hamming, la ventana Hamming y la distancia

Hamming.

El cdigo de Hamming es un cdigo que detecta errores y los

corrige; en los datos codificados.

La distancia de Hamming es la efectividad de los cdigos de

bloque y depende de la diferencia entre una palabra de cdigo

vlida y otra.

La paridad est fundamentada en aadir un bit, llamado bit de

paridad, que diga si el nmero de los bits de valor 1 en los

datos anteriores es par o impar.

La paridad detecta que hay error, pero no indica en qu bit se

efectu.

Para detectar errores de dos bits, se debe aadir un bit ms, y

el cdigo se llama Hamming extendido.

BIBLIOGRAFA

Codigo Hamming. Revisado (25-09-14).

<http://es.wikipedia.org/wiki/C%C3%B3digo_HammingS>.

Paridad Horizontal y Vertical. Revisado (25-09-14).

<http://es.wikipedia.org/wiki/Paridad_horizontal_y_vertical>.

Cdigo Hamming. Revisado (26-09-14).

<http://www.google.com/url?sa=t&rct=j&q=&esrc=s&source=web&cd=8&ved=

0CE4QFjAH&url=http%3A%2F%2Fwww.cimat.mx%2F~alram%2FSO%2FCo

digoHamming.ppt&ei=PiAqVJ998OewBLyZgbAJ&usg=AFQjCNF3XmFHeP5

mQPv0AtWXA6wGd67_2w>.

You might also like

- Fundamentos de TelecomunicacionesDocument42 pagesFundamentos de TelecomunicacionesWendy Santana EncarnacionNo ratings yet

- Actividad1 Montiel CerónDocument4 pagesActividad1 Montiel CerónAngélica Mont Cer100% (1)

- Generación Del Código de Hamming para 3 Bits de InformaciónDocument16 pagesGeneración Del Código de Hamming para 3 Bits de InformaciónJoel Lema Chulli100% (1)

- Código Hamming: Detección y corrección de errores en 7 bitsDocument9 pagesCódigo Hamming: Detección y corrección de errores en 7 bitsjoserecalde100% (1)

- 10 Codificación de Canal Código Hamming y Código Convolucional 1 PDFDocument24 pages10 Codificación de Canal Código Hamming y Código Convolucional 1 PDFTrianguloEquilatero100% (1)

- Qué Es ProteusDocument25 pagesQué Es ProteusNeyser Chavez100% (1)

- Tipos de encapsulados SMD: guía completaDocument8 pagesTipos de encapsulados SMD: guía completaJob Linux100% (1)

- 03 Codigo de HuffmanDocument78 pages03 Codigo de HuffmanErick Martínez100% (1)

- Mini-Transmisor y Receptor UHFDocument5 pagesMini-Transmisor y Receptor UHFNorberto Britos100% (1)

- HP 49G Manual de Usuario (Español)Document185 pagesHP 49G Manual de Usuario (Español)Josué Alvarado50% (2)

- Aprendamos A MedirDocument3 pagesAprendamos A Medirlgth100% (1)

- Administración - Del - ProcesadorDocument20 pagesAdministración - Del - Procesadorjuliomc19695137No ratings yet

- Comunicación Serial - Conceptos Generales - National Instruments PDFDocument4 pagesComunicación Serial - Conceptos Generales - National Instruments PDFStefy AlanizNo ratings yet

- Catálogo de Productos ElectrónicosDocument34 pagesCatálogo de Productos ElectrónicosAlan Castillo100% (1)

- Codigo HammingDocument4 pagesCodigo HammingMadi Made100% (1)

- Transmisor UHF-VHF de DatosDocument8 pagesTransmisor UHF-VHF de DatosHéctor Miculax100% (1)

- DigitArt Sintetizador TutotialDocument24 pagesDigitArt Sintetizador Tutotialpuesyo100% (1)

- Ensayo I de ANTENASDocument20 pagesEnsayo I de ANTENASDaniela LeonNo ratings yet

- Antenas Con Reflectores ParabolicosDocument15 pagesAntenas Con Reflectores ParabolicosPaul Tumbaco100% (1)

- P - F - Sensor de Temperatura Basado en Una Resistencia NTCDocument10 pagesP - F - Sensor de Temperatura Basado en Una Resistencia NTCGabriel Borrero ANo ratings yet

- 03 Codigo de HuffmanDocument78 pages03 Codigo de Huffmanrodrigo1214100% (2)

- Multiplexacion - Fundamentos de TelecomunicacionesDocument13 pagesMultiplexacion - Fundamentos de TelecomunicacionesMaury RazgadoNo ratings yet

- Sistemas de control automáticoDocument60 pagesSistemas de control automáticoDANIELNo ratings yet

- Teorema de NyQuistDocument3 pagesTeorema de NyQuistJar Dev Samuel0% (1)

- EjerciciosdeCodificacion CristianBermeoDocument4 pagesEjerciciosdeCodificacion CristianBermeoenchozx100% (1)

- Tesis Prototipo de Robot Móvil TeleoperadoDocument107 pagesTesis Prototipo de Robot Móvil TeleoperadoGerson DepablosNo ratings yet

- Núcleo de Red de TelecomunicacionesDocument81 pagesNúcleo de Red de TelecomunicacionesGastón Nicolás PereiraNo ratings yet

- Sistemas Digitales I ManualDocument53 pagesSistemas Digitales I ManualÄnii GonnzälezNo ratings yet

- Mosfets y ArduinoDocument5 pagesMosfets y Arduinopeto ricNo ratings yet

- Lab 1Document12 pagesLab 1Marcelo HA100% (1)

- Formula FriisDocument50 pagesFormula FriisPablo SepulvedaNo ratings yet

- Control de ErroresDocument4 pagesControl de ErroresCarlos Cahuana Castillo100% (1)

- Catapulta proyecto energíaDocument5 pagesCatapulta proyecto energíaJhorman Gustavo Maldonado Villamizar0% (1)

- ScilabDocument59 pagesScilabCaami RossNo ratings yet

- Fuente Conmutada SenaDocument8 pagesFuente Conmutada SenaJader Funez OliveraNo ratings yet

- Fundamentos de TelecomunicacionesDocument7 pagesFundamentos de TelecomunicacionesArturo Garcia100% (1)

- Comunicación USB de Alta Velocidad Entre LABVIEW y Un Microcontrolador para La Adquisición de Datos en Tiempo RealDocument5 pagesComunicación USB de Alta Velocidad Entre LABVIEW y Un Microcontrolador para La Adquisición de Datos en Tiempo RealpatrohellNo ratings yet

- Consulta IEEE Tipos de BombasDocument4 pagesConsulta IEEE Tipos de BombasSebastian CuencaNo ratings yet

- Amplificador Colector ComunDocument13 pagesAmplificador Colector ComunJorge Leonardo CamachoNo ratings yet

- Uso de WincuplDocument4 pagesUso de WincuplSergio agNo ratings yet

- Sistemas de Control: Partes y EstrategiasDocument25 pagesSistemas de Control: Partes y EstrategiasAdrian MorenoNo ratings yet

- Drivers para Motores DC y Motores Paso A PasoDocument10 pagesDrivers para Motores DC y Motores Paso A PasoLino Eduardo GarciaNo ratings yet

- Electronicafuentesconmutadason 151005063905 Lva1 App6891.en - EsDocument64 pagesElectronicafuentesconmutadason 151005063905 Lva1 App6891.en - EsJuan RiosNo ratings yet

- Montaje 2 Circuitos de Muestreo de SeñalDocument4 pagesMontaje 2 Circuitos de Muestreo de SeñalAlonsoMendozaNo ratings yet

- P2 - Circuitos Con J Fet y Amplificador-1 PDFDocument3 pagesP2 - Circuitos Con J Fet y Amplificador-1 PDFVíctor Fidel Rodriguez PerezNo ratings yet

- Cerradura Terminado PopoDocument19 pagesCerradura Terminado PopoGiovanni MayenNo ratings yet

- Informe Filtro ArduinoDocument3 pagesInforme Filtro ArduinoAndres ValdiviesoNo ratings yet

- MicroprocesadoresDocument8 pagesMicroprocesadoresDaniela Beltran50% (2)

- Introducción A Las Telecomunicaciones - UNEFADocument89 pagesIntroducción A Las Telecomunicaciones - UNEFARobinson ParraNo ratings yet

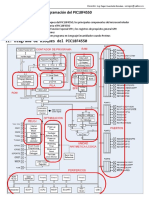

- P01 Modelo de Programación Del PIC18F4550Document14 pagesP01 Modelo de Programación Del PIC18F4550Fide Alvarado100% (1)

- Servicio de Mensajes Cortos (SMS) el Mercado Telefónico de EspañaFrom EverandServicio de Mensajes Cortos (SMS) el Mercado Telefónico de EspañaNo ratings yet

- Automatización Industrial Con PLC SDocument65 pagesAutomatización Industrial Con PLC SJorgeJonathanNo ratings yet

- Sistemas memristivos: representación físico-matemática desde la teoría de sistemas dinámicosFrom EverandSistemas memristivos: representación físico-matemática desde la teoría de sistemas dinámicosNo ratings yet

- Practica 10 ControlDocument11 pagesPractica 10 ControlMaury AzzNo ratings yet

- Analizador de EspectroDocument4 pagesAnalizador de EspectroKaren Milena RomeroNo ratings yet

- Acelerograma AGYE Ecuador 2016Document29 pagesAcelerograma AGYE Ecuador 2016Gian SanchezNo ratings yet

- Manual router Huawuei ONT configuraciónDocument9 pagesManual router Huawuei ONT configuraciónJose Antonio Aravena SilvaNo ratings yet

- 4.2. Introducción A Las Lan EthernetDocument2 pages4.2. Introducción A Las Lan EthernetInstituto Franco CondadoNo ratings yet

- Filtro pasa alto 40cDocument13 pagesFiltro pasa alto 40cAndrés VillanuevaNo ratings yet

- Arit (6) Sistemas de Numeracion - Iii 255-258Document4 pagesArit (6) Sistemas de Numeracion - Iii 255-258Juan Carlos Martinez OcasNo ratings yet

- Ejercicios Cap1Document3 pagesEjercicios Cap1jhonatanjarolNo ratings yet

- Lab 2Document4 pagesLab 2carmenNo ratings yet

- Comandos Basicos Backoffice en GSMDocument14 pagesComandos Basicos Backoffice en GSMJorge Romeo Gaitan RiveraNo ratings yet

- Montaje y Mantenimiento de Infraestructura de TelecomunicacionesDocument6 pagesMontaje y Mantenimiento de Infraestructura de TelecomunicacionesRommel Freddy Astudillo AguilarNo ratings yet

- Casos Prácticos de RedesIDocument4 pagesCasos Prácticos de RedesIAstin R. MartinezNo ratings yet

- 1ro Sec AritmDocument4 pages1ro Sec AritmAna Marita Quispe AstoNo ratings yet

- Estudio de Nuevas Tecnologías WIMAX, FSO, HAPS y UWBDocument174 pagesEstudio de Nuevas Tecnologías WIMAX, FSO, HAPS y UWBWilmer Huaman PasaperaNo ratings yet

- Capitulo 4 Acceso A La RedDocument123 pagesCapitulo 4 Acceso A La RedDjviik G R TiburonNo ratings yet

- Cable de Red Cat 6e + Punta RJ 45 - 56694335 Cuba - RevolicoDocument2 pagesCable de Red Cat 6e + Punta RJ 45 - 56694335 Cuba - RevolicoFrankmmt MTNo ratings yet

- El Sistema Mundial de Socorro y Seguridad Marítima (SMSSMDocument10 pagesEl Sistema Mundial de Socorro y Seguridad Marítima (SMSSMGenesis RojasNo ratings yet

- Actividad 1.2. Línea de Vista de Onda EspacialDocument2 pagesActividad 1.2. Línea de Vista de Onda EspacialDaniel Alexander Vasquez CazonNo ratings yet

- Antena Log PeriodicaDocument27 pagesAntena Log PeriodicaBryan Fernando Diaz MartinezNo ratings yet

- Propagación OssDocument116 pagesPropagación OssGiovany CardenasNo ratings yet

- Ejercicios Resueltos Efecto Doppler Ii PDFDocument8 pagesEjercicios Resueltos Efecto Doppler Ii PDFJordy Toro Rojas60% (5)

- Presentacion Osciloscopio DigitalDocument39 pagesPresentacion Osciloscopio DigitalGaston AmayaNo ratings yet

- Importante DFT FFTDocument27 pagesImportante DFT FFTJaime Zapata AmoresNo ratings yet

- GSM AmplificadorDocument2 pagesGSM Amplificadorshapla salehaNo ratings yet

- Nodo 1Document8 pagesNodo 1Luis Fernando Zuluaga DuqueNo ratings yet

- Tarea 2 Jose Montalvo Grupo 20Document4 pagesTarea 2 Jose Montalvo Grupo 20sebastianNo ratings yet

- 6-Comportamiento de Una Señal Eléctrica y ÓpticaDocument7 pages6-Comportamiento de Una Señal Eléctrica y ÓpticaAngel Kauil KumulNo ratings yet

- Simbologia Cartas Aeronauticas PDFDocument3 pagesSimbologia Cartas Aeronauticas PDFFernando Sebastian HussNo ratings yet

- DecodificadorDocument6 pagesDecodificadorjoefelix93261No ratings yet