Professional Documents

Culture Documents

Edn Design Ideas II

Uploaded by

agmnm1962Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Edn Design Ideas II

Uploaded by

agmnm1962Copyright:

Available Formats

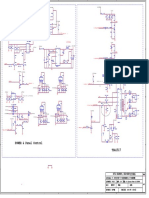

T

he popular USB interface can

charge a portable device while trans-

ferring data. But for high-capacity

batteries, the 500-mA output current of

USB hosts and powered hubs greatly ex-

tends the charging time. (Unpowered

USB hubs supply no more than

100 mA.) Thus, a system that ac-

cepts charging power from an ac adapter

as well as the USB port is more conven-

ient. Such a system can charge from a

notebook USB port when youre travel-

ing, yet can charge faster via the adapter

when youre at home or in the office. An

external transistor current source adds

dual-input capability to a single-chip

lithium-cell charger (Figure 1). The chip,

IC

1

, operates alone when you connect to

USB power and allows you to pin-pro-

gram it for a maximum charging current

of either 500 or 100 mA. When you plug

in an ac adapter, which the 600-mA com-

ponents set, the external-transistor cur-

rent source, Q

2

and Q

3

, turns on and sets

IC

1

s charging current to 500 mA. Be-

cause IC

1

and Q

2

both charge the battery

under that condition, the total charging

current is 1100 mA.

Q

2

and Q

3

form a current limiter for

the ac adapter. The limiter allows Q

2

and

R

1

to pass the additional 600 mA. When

the voltage drop across R

1

exceeds that

across R

2

, which R

2

and R

5

set, Q

2

begins

to turn off. Q

2

cancels V

BE

, enabling R

1

to

more accurately set the maximum cur-

rent. Voltage across R

3

sets the reference

voltage, and the output current limits

when the voltage drop on R

1

matches the

voltage on R

3

. Q

3

should have a beta high-

er than 200 at 1A, so that IC

1

s CHG pin

can sink enough current to turn on Q

3

.

High beta also minimizes error in the

transistor current source. When IC

1

changes from current mode to voltage

mode at approximately 4.15V, IC

1

s CHG

output turns off the transistor current

source. IC

1

remains on and finishes off

the taper to full charge. It also remains on

and continues to function when USB

power is gone and only ac power remains.

IC

1

also controls the prequalification

current, which is the current level neces-

sary to safely recover deeply discharged

cells at low battery voltage. The CHGout-

put assumes a high-impedance state dur-

ing cell prequalification to ensure that the

external current source remains off, and

that the prequalification current of ap-

proximately 50 mA comes only from IC

1

.

When you plug in the ac power, Q

1

turns

off to prevent back-feeding the USB in-

put. You install Q

1

backward with the

drain connected to USB input side, so

that USB power remains connected to the

IN pin (IC

1

pin 4) via Q

1

s body diode,

even when Q

1

is off.

www.edn.com September 19, 2002 | edn 103

ideas

design

Add current boost to a

USB charger ..................................................103

Transistor linearly digitizes airflow ..........104

Make a truly linear RF-power detector ..106

Simple circuit provides 5V gate

bias from 48V..........................................108

Circuit provides laser-diode control ........110

One amplifier has two gain figures ........110

Single switch controls digital

potentiometer................................................112

Instrumentation amp makes noninverting

integrator........................................................114

Publish your Design Idea in EDN. See the

Whats Up section at www.edn.com.

Edited by Bill Travis

MAX1811

SELV

SELI

GND

CHG

EN

GND

BATT

IN

4.7 F

4.7 F

1 F

Q

1

FND304P

Q

2

2N3904

Q

3

FTZ789A

OR 2SB1427

(>200 AT 1A)

R

2

200

R

3

10

R

1

0.25

1N5817

1N4148

1N5817

4.5 TO 6.5V AC

ADAPTER

(DOES NOT REQUIRE CURRENT LIMIT)

20k

USB

POWER

ON

OFF

500 mA

100 mA

(USB ONLY)

470k

100k

+

LI+

BATTERY

IC

1

Fi gure 1

Add current boost to a USB charger

Len Sherman, Maxim Integrated Products, Sunnyvale, CA

This battery charger delivers 100 or 500 mA (selectable) to a single lithium cell when USB power is

connected and charges at 1100 mA (settable via R

1

or R

2

) when ac power is present.

Is this the best Design Idea in this

issue? Select at www.edn.com.

104 edn | September 19, 2002 www.edn.com

ideas

design

A

sensitive and reliable way to

measure airflow is to take advantage

of the predictable relationship be-

tween heat dissipation and air speed. The

principle of thermal anemometry relies

on Kings Law, which dictates that the

power required to maintain a fixed dif-

ferential between the surface of a heated

sensor and the ambient air temperature

increases as the square root of air speed.

The popular hot-wire anemometer ex-

ploits this principle, but it suffers from

the disadvantage of using a specialized

and fragile metallic filament, the hot

wire, as the airflow sensor. The circuit in

Figure 1 avoids this disadvantage by us-

ing a pair of robust and inexpensive tran-

sistors instead of a flimsy wire for air-

speed sensing. The Q

1

/Q

2

front end of the

circuit borrows from an earlier Design

Idea (Reference 1). Just as in the 1996 cir-

cuit, the circuit in Figure 1 works by con-

tinuously maintaining the condition

V

Q1

V

Q2

. To perform this task, the circuit

must keep Q

1

approximately 50C hotter

than Q

2

.

V

BE

balance requires this temperature

difference, because Q

1

s collector current,

I

Q1

, is 100 times greater than that of Q

2

,

I

Q2

. If Q

1

and Q

2

were at the same tem-

perature, this ratio would result in V

Q1

s

being greater than V

Q2

by approximately

100 mV. Proper control of I

Q1

establishes

differential heating that makes Q

1

hotter

than Q

2

. The method thus exploits the

approximate 2-mV/C temperature co-

efficient of V

BE

to force V

Q

balance. The

resulting average, I

Q1

, proportional to the

average power dissipated in Q

1

, is the

heat-input measurement that forms the

basis for the thermal air-speed measure-

ment. Calibration of the sensor begins

with adjustment of the R

1

zero-adjust

trim. You adjust R

1

such that, at zero air-

flow, V

Q1

V

Q2

with no help from Q

3

.

Then, when moving air hits the transis-

tors and increases the heat-loss rate, V

Q1

increases and causes comparator IC

1

to

release the reset on C

1

. C

1

then charges

until IC

2

turns on, generating a drive

pulse to Q

1

through Q

3

.

The resulting squirt of collector cur-

rent generates a pulse of heating in Q

1

,

driving the transistors temperature and

V

BE

back toward balance. Proper adjust-

ment of R

2

calibrates the magnitude of

the I

Q1

-induced heating pulses to estab-

lish an accurate correspondence between

pulse rate and air speed. Now, consider

measurement linearization. The square-

root relationship of Kings Law makes the

relationship between heat loss and air

speed nonlinear. You must iron the kinks

out of the air-speed-calibration curve.

You might achieve linearization in soft-

ware, of course. However, depending on

W

F

+

Q

3

Q

1

I

D

V

C2

Q

2

V

Q1

I

Q1

V

Q2

R

1

V

3

V

C1

R

2

100 F

1 F

0.1 F

2N3906

Q

6

IC

2

C

1

IC

1

2N3904

ZERO

10k

240k

300k

240k

240k

5.1k

2.2k

2.2k

2k 5.1k

5.1k

12k

2k 5

6

8

7

CALIBRATE 1k

5k

1

2

2N4401

Q

5

2N5089

Q

4

2N5087

Q

7

2N3906

2N4401 3

4

82

AIRFLOW

10k

240k

1M

5.1k

F

1

5V

LM393

LM393

Fi gure 1

Transistor linearly digitizes airflow

Steve Woodward, University of North Carolina, Chapel Hill, NC

Using a simple transistor as sensor, this circuit yields a digitized, linear measurement of air speed.

106 edn | September 19, 2002 www.edn.com

ideas

design

the flexibility of the data system the

anemometer works with, a software cor-

rection is sometimes inconvenient. An-

other earlier Design Idea (Reference 2)

presented an analog solution to lin-

earization. But if you want the advan-

tages of a digital, pulse-mode output

that is, noise-free transmission over long

cable runsyou need a different fix.

The circuit in Figure 1 provides both

linearity and a digital output. The aver-

age heat the pulses deposit in Q

1

is

H5VIFW, where I is the ampli-

tude of the Q

1

current pulses (adjusted

with R

2

), F is the output frequency, and

W is the pulse width. W is inversely pro-

portional to I

D

, the discharge current that

ramps down V

C1

and controls the on-

time of IC

2

. Q

4

and Q

7

average the output

duty cycle to generate a control voltage

for Q

5

and thus make W a function of F.

In fact, the feedback loop this arrange-

ment establishes implicitly makes W

K/(WF), where K is a calibration con-

stant determined by the component val-

ues. Therefore, W

2

K/F, and H5

IF/K/F. This expression yields

F(H/5I)

2

/K, making F the desired func-

tion of H

2

and thus linearizing the rela-

tionship between frequency and air

speed.

References

1. Woodward, Steve, Self-heated tran-

sistor digitizes airflow, EDN, March 14,

1996, pg 86.

2. Woodward, Steve, Transistor and

FVCs make linear anemometer, EDN,

Sept 26, 1996, pg 72.

Is this the best Design Idea in this

issue? Select at www.edn.com.

M

odern high-performance trans-

mitters require accurate monitor-

ing of RF power, because most cel-

lular standards depend on strict power-

transmission levels to maintain an effec-

tive network. Regulation of transmitted-

signal strength also lets you build lower

cost systems. Figure 1 shows a waveform-

independent circuit that provides a lin-

ear measurement of RF power. Sophisti-

cated modulation schemes, such as

CDMA (code-division multiple access)

and TDMA (time-division multiple ac-

cess) have obsoleted traditional ap-

proaches to RF power. Diode-

based detectors have poor

temperature stability,

and thermal detectors

have slow response times.

Logarithmic amplifiers are

temperature-stable and have

a high dynamic range, but

they exhibit a waveform-de-

pendent response. This re-

sponse causes the output to

change with modulation type

and, in the case of spread-

spectrum technology, chan-

nel loading.

Power detection must be

waveform-independent in

systems that use multiple

modulation schemes. These

include point-to-point sys-

tems that are configurable to

transmit QPSK (quadrature-

phase-shift keying),

16QAM (quadrature

amplitude modulation), and

64QAM, for example, and

spread-spectrum systems such

as CDMA and W-CDMA

(wide CDMA). A logarithmic

amplifier in an automatic-

gain-control loop can regulate

the gain of a variable-gain

power amplifier, but the out-

put voltage is waveform-de-

pendent, because the logarith-

mic amplifier does not re-

spond to the rms level of

the signal. For example,

sine- and square-wave in-

puts that have the same

rms voltage levels have dif-

ferent logarithmic inter-

cepts (Figure 2). You could

use calibration factors to

correct this intercept dif-

ference in a multistandard

system.

An alternative solution

(Figure 1) uses the

AD8361, a high-frequency

true-power detector. Un-

like the logarithmic ampli-

fier, the AD8361 is an rms-

to-dc converter and,

therefore, responds to the

3

2.5

2

1.5

1

0.5

0

80 70 60 50 40 30 20 10 0 10 20

OUTPUT

VOLTAGE

(V)

INPUT POWER (dBm)

3.01 dB (75.25 mV)

SQUARE WAVE

SINE WAVE

Fi gure 1

This circuit provides an output voltage that is linearly pro-

portional to the input power in watts.

Make a truly linear RF-power detector

Victor Chang and Eamon Nash, Analog Devices, Wilmington, MA

_

+

AD707

3

2

15V

15V

4

7

6

V

OUT

R

7

4k

R

6

1k

R

5

1k

R

3

100

R

2

100 R

4

100k

X1

X2

Y1

Y2

AD633

VRMS

COMM

AD8361

FLTR

VPOS

RFIN

PWDN

1

2

3

4

+V

S

V

S

W

8

Z

7

6

5

15V

0.1 F

0.1 F

5V

5V

15V

1

2

3

4

5

C

5

1 nF

6

5V

C

3

100 pF

C

1

100 pF

R

1

75

C

2

0.01 F

V

RFIN

Fi gure 2

Log amps detect signals over a wide dynamic range, but are not rms-

responding.

input rms voltage. Hence, a sine

wave, a square wave, or any oth-

er input with the same rms level

produces the same dc output, al-

lowing you to incorporate wave-

form-independent measurement

into a multimodulation system.

With the addition of a

multiplier, the circuit

delivers an output voltage that is

proportional to the input power

level in watts. You can easily ad-

just gain and offset for this pow-

er meter with an op-amp circuit,

thus providing an output scaled

in volts per watt. A complex RF

waveform feeds the input of the

AD8361.

The multiplier squares the dc output

to produce a voltage proportional to the

power dissipated in the 50 input im-

pedance of the circuit. The AD633 mul-

tiplier squares the rms output of the

AD8361 and divides by 10. The AD707

provides a maximum gain of 6

[G(R

5

R

6

R

7

)/R

5

]. This

value is lower than the gain of

10 that you would need to ex-

actly cancel the effect of the

multiplier scaling and allows

the circuit to have a wider dy-

namic range, because the out-

put would saturate with a

smaller input with a gain of

10. You can easily adjust all cir-

cuit offsets with potentiome-

ter R

2

. Figure 3 shows meas-

urements made with this

power meter. The graphs plot

the output voltage and error

for input signals at frequencies

of 100 and 900 MHz. The de-

tector operates at frequencies as high as

2.7 GHz.

108 edn | September 19, 2002

www.edn.com

ideas

design

Is this the best Design Idea in this

issue? Select at www.edn.com.

V

OUT

(V)

100

10

1

0

4

2

0

2

4 0

0.01 0.1 1 10

ERROR (dB)

P

IN

(mW)

ERROR:900 MHz

ERROR:100 MHz V

OUT

:100 MHz

V

OUT

:900 MHz

Fi gure 3

The circuit in Figure 1 responds to rms signals, independent of wave-

form.

A

small and simple

circuit derives 5V

from the 48V rail

that telecomm applica-

tions typically

use (Figure 1).

Useful for gate

bias and other purposes,

the 5V supply delivers as

much as 5-mA output

current. A shunt refer-

ence, IC

1

, defines 5V as

ground reference for a charge pump, IC

2

.

The charge pump doubles this 5V differ-

ence between system ground and charge-

pump ground to produce 5V with respect

to the system ground. The shunt refer-

ence maintains 5V across its terminals by

regulating its own current, I

S

. I

S

is a func-

tion of the value of R. The current

through R, I

R

, is reasonably constant and

varies only with the input voltage. I

R

, the

sum of the charge-pump and shunt-ref-

erence currents (I

R

I

CP

I

S

), has maxi-

mum and minimum values set by the

shunt reference.

The shunt reference sinks as much as

15 mA and requires 60 A minimum to

maintain regulation. Maximum I

R

is a

function of the maximum input voltage.

To prevent excessive current in the shunt

reference with no load on the charge-

pump output, use the maximum input

voltage (48V10%52.8V) to cal-

culate the minimum value of R. The

maximum reference sink current, 15 mA,

plus the charge pumps no-load operat-

ing current, 230 A, equals the maxi-

mum I

R

value, 15.23 mA. Thus, R

MIN

(V

IN(MAX)

V

REF

)/I

R(MAX)

3.14 k.

Choose the next-highest standard 1%

value, which is 3.16 k. You calculate the

guaranteed output current for the charge

pump at the minimum line voltage:

48V10%43.2V. The charge

pumps maximum input current is

I

CP

(V

IN(MIN)

V

REF

)/RI

SH(MIN)

(43.2

5)/3.1690 A12 mA, where 90 A

is the minimum recommended operat-

ing current for the shunt reference. As-

suming 90% efficiency in the charge

pump, the output current is I

OUT

(I

CP

/2)0.9(12/2)0.95.4 mA. You

halve the charge-pump current, because

the output voltage is twice the input volt-

age. Be sure that R can handle the wattage

under no-load conditions. A 1W resistor

suffices in this example.

IN

OUT

GND

C+

C

MAX1683

IC

2

MAX6138

EXR50-T

IC

1

C

2

3.3 F

C

1

0.1 F

C

3

4.7 F

V

OUT

5V, 2 mA

MAXIMUM

1

+

2

R

8.2k

V

IN

48V

Fi gure 1

Simple circuit provides 5V gate bias from 48V

Will Hadden, Maxim Integrated Products, Sunnyvale, CA

This small, simple circuit produces 5V at 5 mA from a 48V input.

Is this the best Design Idea in this

issue? Select at www.edn.com.

110 edn | September 19, 2002 www.edn.com

ideas

design

L

aser diodes are sensitive to ESD,

rapid turn-on currents, and over-

voltage conditions. To address those

problems, the simple laser-diode con-

troller in Figure 1 has several functions.

The first part of the circuit comprises an

8.2V zener diode, D

1

that forms the heart

of a constant-voltage source for the laser

diode. Next, IC

1A

, half of a dual FET-in-

put op amp, forms an inverting integra-

tor to slow the turn-on time. To turn on

the laser diode, IC

1B

, the other half of the

op-amp IC, triggers the base of Q

2

. This

transistor forms a constant-current

source for the laser diode. You can mon-

itor the laser-diode supply voltage and

the sense-diode current and voltage. You

use these parameters as inputs to the dif-

ferential amplifier, IC

2A

, the first half of

another dual FET-input op amp. When

an overvoltage condition occurs, the dif-

ference amplifier detects the condition,

and its output drives IC

2B

, configured as

an open-loop comparator. You set the

threshold by using the potentiometer, R

1

.

Zener diode D

2

provides a constant-volt-

age source for that threshold setting.

When the voltage reaches the threshold,

the output triggers the base of Q

1

, which

instantly shuts down IC

1B

, which in turn

shuts down the laser diode.

IC

1A

LT1057

_

+

IC

1B

LT1057

_

+

IC

2A

LT1057

_

+

2

1

3

8

8

4

4

SPST

1M

0.001 F

1N914

330

499 Q

1

2N2222

Q

2

2N2222

5

6

12V

12V

7

1k

D

1

8.2V

12V

0.1 F

150

0.5W

CONSTANT-VOLTAGE SOURCE

SLOW TURN-ON

SHUTDOWN CIRCUIT

1k

10k

CONSTANT-CURRENT

SOURCE

LASER

DIODE

87.5

1W

SENSE

DIODE

LASER-DIODE

PACKAGE

1k

1k

10k

1k

1k

2

4

1

8 3

IC

2B

LT1057

_

+

6

4

8 5

10k

12V

12V

7

12V

330

D

2

8.2V

REFERENCE SETPOINT

56k

R

1

100k

CONSTANT-VOLTAGE

SOURCE

Fi gure 1

Circuit provides laser-diode control

Michael Fisch, Agere Systems, Longmont, CO

Constant voltage and current and slow turn-on time are the keys to laser diodes survival.

Is this the best Design Idea in this

issue? Select at www.edn.com.

T

he single-supply circuit in Figure

1 is an inverting amplifier with two

outputsone for positive output

voltages, V

OUT(POS)

, and the other for neg-

ative output voltages, V

OUT(NEG)

. Steering

diodes D

1

and D

2

split the amplifier, IC

1

,

output into the two output polarities rel-

ative to the 2.5V reference. The gain of

the inverting amplifier for each of the two

polarities features independent pro-

gramming, using Catalysts (www.cat

semi.com) 100-tap, digitally program-

mable potentiometers DPP

1

and DPP

2

.

You configure the potentiometers as vari-

able resistances and model them as

(1p)R

POT

, where p represents the pro-

portional position of the wiper as it

moves from one end (p0) of the DPP

to the other end (p1). R

POT

is the po-

tentiometers end-to-end resistance. In

terms of p, the gains of the circuit are

If R

1

R

POT

, the gain values can be less

One amplifier has two gain figures

Chuck Wojslaw, Catalyst Semiconductor, Sunnyvale, CA

, V 5 . 2 V 0 FOR

V

R

R ) p 1 (

V

IN

IN

1

1 POT 1

) POS ( OUT

< <

=

and

112 edn | September 19, 2002 www.edn.com

ideas

design

than one, one, or greater than one. For

the circuit values shown, you can

program the two gains from ap-

proximately

1

/10 to 10. If you characterize

the potentiometer, the measured accura-

cy of the circuit is approximately 1%.

This implementation of the circuit uses

only six components and is appropriate

for signal-processing applications.

Is this the best Design Idea in this

issue? Select at www.edn.com.

+

5V

5V 5V

1

4

2

3

3

5

6

3

5

6

11

p1R

POT1

V

OUT(NEG)

V

OUT(POS)

p2R

POT2

V

IN

IC

1

D

1

D

2

R

1

1k

1%

2.5V

NOTES:

IC

1

= LM6064.

R

POT1

=R

POT2

=10 k.

1

4

/

SERIAL

BUS

DPP

1

CAT5113

DPP

2

CAT5113

8 8

4 4

Fi gure 1

Using digitally programmable potentiometers, you can obtain two distinct gain figures from one

amplifier.

T

his Design Idea is an evolution and

simplification of another (Figure 1,

Reference 1). Replacing the three in-

verted-input NOR gates with their

logical equivalents, positive-input

NAND gates, makes these three gate

symbols consistent with the fourth,

which was drawn as a positive-input

NAND gate. The 74HC132s data sheet

describes the device as a quad, two-input

NAND gate with hysteresis.

As the earlier design also describes, you

can activate the DPDT rocker switch, S

1

,

to produce either a count-up or a

countdown effect at the digital poten-

tiometer, CAT5114. Moving the switch

up causes S

1A

to ground the input of IC

1A

,

thus causing the NAND-gate flip-flop,

IC

1A

and IC

1B

, to switch high, thereby

commanding the CAT5114 to count up.

At the same time, S

1B

causes the 1-F ca-

pacitor on IC

1C

s upper input to discharge

through a 10-k resistor. Eventually the

output of IC

1C

also switches high, thus

enabling the oscillator comprising IC

1D

.

Similarly, moving the switch down caus-

es S

1B

to ground the input of IC

1B

, thus

causing the NAND-gate flip-flop to

Single switch controls digital potentiometer

Jim Bach, Delphi Delco Electronics Systems, Kokomo, IN

1 F 1 F

DPDT

MOMENTARY

CONTACT

MOMENTARY

S

1A

S

1B

R

100k

C

4.7 F

5V

100k 10k

IC

1C

IC

1B

IC

1A

100k

100k 10k

100k

U/D

INC

CS

5V

CAT5114

74HC132

IC

1D

5V

5V

5V

OFF

Fi gure 1

This is the original circuit, as published in Reference 1.

TABLE 1SUMMARY OF SAVINGS

Component Figure 1 count Figure 4 count Savings

ICs Two Two Zero

Resistors Seven Four Three

Resistor values Two (10 k, 100 k) One (100 k) One

Capacitors Three Two One

Capacitor values Two (1 F, 4.7 F) Two (0.1 F, 4.7 F) One lower value and cheaper

Switches One DPDT One SPDT Single-pole and cheaper

. V 5 V V 5 . 2 FOR

V

R

R ) p 1 (

V

IN

IN

1

2 POT 2

) NEG ( OUT

< <

=

114 edn | September 19, 2002 www.edn.com

ideas

design

switch low, thereby commanding the

CAT5114 to count down. At the same

time, S

1A

causes the 1-F capacitor on

IC

1C

s lower input to discharge through

a 10-k resistor, thereby eventually en-

abling the oscillator comprising IC

1D

.

The first step in simplifying this design

is to rearrange the connections of S

1

so

that the A and B sections are not cross-

connected between operating the flip-

flop and the oscillator-enabling circuit.

You can rewire the interface structure as

shown in Figure 2. This circuit uses S

1A

to

control the flip-flop, whereas S

1B

controls

the oscillator-enable

circuit. This step

does nothing direct-

ly to reduce the parts

count of the circuit;

however, it does

make the subse-

quent step more ob-

vious. The next step

in the simplification

is to recognize that

the two RC net-

works on the inputs

of IC

1C

both do the

same thing but in

opposite switch po-

sitions. As far as IC

1C

is concerned, either

switch position performs the same func-

tion; that is, to debounce the switch con-

tacts and eventually enable the oscillator.

Thus, you need only one RC network,

and you can tie it to both of S

1B

s active

positions (Figure 3). Moving the switch

in either direction discharges the 1-F

capacitor through the 10-k resistor,

eventually causing the output of IC

1C

to

switch high, thus enabling the oscillator.

When you release the switch, S

1B

goes to

the open, or off, state, and the 1-F ca-

pacitor recharges through the 100-kre-

sistor, thus turning off the oscillator.

The last simplification step stems from

realizing that the sole purpose of IC

1C

and

the RC filter on its input is to generate a

high state whenever switch S

1

is in either

of its active positions. True, the RC filter

does debounce the switch contacts; how-

ever, the actual switch- closure informa-

tion available at S

1B

is also available at S

1A

.

Thus, you can simply use IC

1C

to direct-

ly monitor the S

1A

contacts. You can move

the RC filtering to the input of IC

1D

. This

step allows you to simplify S

1

, changing it

from a DPDT to a SPDT configuration,

which means you can use a cheaper

switch. Because the RC debounce filter

now connects to a low-impedance gate

output, IC

1C

, you can increase the R, thus

reducing the amount of C you need to

form the same time constant. Thus, you

can use smaller, cheaper capacitors. You

can also use the same resistor value, 100

k, in all four locations, eliminating the

need to inventory two resistor values. The

final circuit appears in Figure 4. Table 1

summarizes the savings in component

count and cost.

Reference

1. Wojslaw, Chuck, Single switch con-

trols digital potentiometer, EDN, Feb 7,

2002, pg 100.

Is this the best Design Idea in this

issue? Select at www.edn.com.

You can restructure the switch-interface circuit

of Figure 1 as shown.

S

1A

S

1B

DPDT

MOMENTARY

CONTACT

10k

10k

OFF

1 F

Fi gure 2

You can simplify the oscillator-enable structure,

as shown.

10k

1 F

100k

5V

IC

1C

S

1B

Fi gure 3

This circuit uses fewer and cheaper components than the circuit in

Figure 1.

0.1 F

SPDT

MOMENTARY

CONTACT

S

1

R

100k

C

4.7 F

100k

100k

100k

U/D

INC

CS

5V

CAT5114

74HC132

IC

1D

IC

1C

IC

1B

IC

1A

5V

5V

OFF

Fi gure 4

Instrumentation amp makes noninverting integrator

Glen Brisebois, Linear Technology Corp, Milpitas, CA

F

igure 1a shows the classic imple-

mentation of an integrator. The cir-

cuit has two properties that may be

undesirable in same applications: It nec-

essarily inverts, and it requires a split-

supply or midsupply reference. Figure 1b

shows an implementation of an integra-

tor that uses an LT1789 instrumentation

amplifier. This integrator does not invert,

and it works with a single supply. In ad-

dition, because it has a positive-only out-

put swing, the integrator capacitor can be

a high-value, polarized electrolytic unit,

as shown. Most of the circuit operates as

a voltage-controlled current source. The

116 edn | September 19, 2002 www.edn.com

ideas

design

LT1789 is a precision micropower

instrumentation amplifier

that can operate from 3 to

36V total-supply spans.

With a gain setting of 1, with

pins 1 and 8 open, the voltage be-

tween the inputs also appears be-

tween the Output and Reference

pins. The Output pin connects to

one side of R

1

, and the voltage on

the other side of R

1

drives the Ref-

erence. The input voltage, V

IN

, ap-

pears across R

1

, causing the cur-

rent-source action, with I

OUT

V

IN

/R

1

. Dumping this current into

a capacitor produces the integra-

tor action, with the time constant R

1

C

1

.

The LT1636 buffers the output voltage on

C

1

, thereby eliminating the loading ef-

fects of approximately 200 k of the

LT1789s Reference pin and any down-

stream circuitry. The wide, single-supply

range and micropower operation make

the circuit suitable for battery-powered

systems. As a positive-output-only inte-

grator, this circuit is not generally appli-

cable inside control loops. Suitable ap-

plications include accumulators,

adjustable ramp generators, and voltage-

to-frequency converters.

+

LT1789

LT1636

REF

3

3

8

6

1

2

4

2

4

+

+

+

7

7

6

V

S

V

S

V

S

R

1

10k

V

IN

V

IN

C

1

100 F

I

OUT

R

2

10

t=0

t=0

+

V

S

R

C

(a) (b)

Fi gure 1

The classic integrator in a inverts and requires split supplies. The circuit in b is noninverting and works

with a single supply.

Is this the best Design Idea in this

issue? Select at www.edn.com.

You might also like

- EDN Design Ideas 2000Document215 pagesEDN Design Ideas 2000chag1956100% (3)

- 16 Design IdeasDocument7 pages16 Design Ideasmailnehru8955100% (2)

- Edn Best of Design Ideas 2012Document25 pagesEdn Best of Design Ideas 2012srescia67% (3)

- EDN Design Ideas PDFDocument7 pagesEDN Design Ideas PDFAmine HalimiNo ratings yet

- Tty To Rs232Document8 pagesTty To Rs232sandeepverma8257100% (2)

- EDN Design Ideas 1998Document166 pagesEDN Design Ideas 1998chag1956100% (4)

- EDN Design Ideas 2008Document124 pagesEDN Design Ideas 2008chag1956100% (2)

- Best of DesignIdeasDocument48 pagesBest of DesignIdeastinears02100% (1)

- RS-485 Transceiver Tutorial: 1 IntersilDocument8 pagesRS-485 Transceiver Tutorial: 1 Intersilpiyushpandey100% (3)

- EDN's Best of Design Ideas - Volume 1Document24 pagesEDN's Best of Design Ideas - Volume 1ableseaman100% (4)

- Electronic Load and Other Circuit IdeasDocument6 pagesElectronic Load and Other Circuit Ideasanees_172000100% (1)

- Ee - 105 - ADSP-2100 Family C Programming Examples Guide (En)Document61 pagesEe - 105 - ADSP-2100 Family C Programming Examples Guide (En)tiretrakNo ratings yet

- LCD Display 16x02 - 20x04 Allinone ENDocument44 pagesLCD Display 16x02 - 20x04 Allinone ENcmdi100% (1)

- EDN Design Ideas 2004Document155 pagesEDN Design Ideas 2004chag1956100% (2)

- Edn Design Ideas IIIDocument5 pagesEdn Design Ideas IIIagmnm1962100% (2)

- Stereo Peak Indicator: Small CircuitscollectionDocument1 pageStereo Peak Indicator: Small CircuitscollectionTariq Zuhluf100% (1)

- EDN Design Ideas 2005Document134 pagesEDN Design Ideas 2005chag1956100% (2)

- FETs DatabookDocument189 pagesFETs DatabookTito Titon0% (1)

- A Further Study Into The Use of The PIC32MX250F128B, With Side Projects Using The AT91SAM3X8E (Arduino Due) and The Intel GalileoDocument15 pagesA Further Study Into The Use of The PIC32MX250F128B, With Side Projects Using The AT91SAM3X8E (Arduino Due) and The Intel Galileotahmidmc100% (2)

- Piu102 Piu201 Piu102 Piu201Document2 pagesPiu102 Piu201 Piu102 Piu201Costel Cojocaru100% (2)

- Ultrasonic TransducerDocument5 pagesUltrasonic TransducerRishabhKarn100% (3)

- NB2DSK01Document82 pagesNB2DSK01microbotica126100% (1)

- IntroductionDocument23 pagesIntroductionArryshah Dahmia100% (4)

- Component Ratings: Reflow & Lamp ControllerDocument1 pageComponent Ratings: Reflow & Lamp ControllerKeith Dobbelaere100% (4)

- Creating A PWM Signal Using A PIC 16F84Document5 pagesCreating A PWM Signal Using A PIC 16F84saadettin100% (2)

- The Seven Segment DisplayDocument5 pagesThe Seven Segment DisplayTewodros Kassahun100% (2)

- A Simple Usb Oscilloscope For The PCDocument15 pagesA Simple Usb Oscilloscope For The PCJuan Gil Roca100% (1)

- 1KM Power FM TransmitterDocument5 pages1KM Power FM TransmitterAntonio José Montaña Pérez de Cristo100% (1)

- SETUP of Mega2560+ESP8266-2Document6 pagesSETUP of Mega2560+ESP8266-2CyrusNo ratings yet

- PIC With LCD and ICSP Programmer Board - v3 - JRMDocument7 pagesPIC With LCD and ICSP Programmer Board - v3 - JRMm_menaka100% (2)

- Lab LCDDocument6 pagesLab LCDJesus Cotrina100% (1)

- Introdution To The DsPIC30FDocument17 pagesIntrodution To The DsPIC30Fboyluca100% (1)

- 7 Segment N LCDDocument38 pages7 Segment N LCDBaishakhi Bose100% (1)

- Understanding Modern ElectronicsDocument3 pagesUnderstanding Modern ElectronicsNarayana Mugalur100% (1)

- Easypic v7 Manual v104cDocument38 pagesEasypic v7 Manual v104cjuan0537100% (1)

- IcspDocument14 pagesIcspJOYCE100% (1)

- PIC of An IDer PDFDocument5 pagesPIC of An IDer PDFronaldbolorbaral8809100% (1)

- Schematic Ktc-Cbu 24 VCMDocument4 pagesSchematic Ktc-Cbu 24 VCMMarco Kersul100% (1)

- Practical PIC ProjectsDocument14 pagesPractical PIC ProjectsArdhika Dhennis Putra Ananda100% (1)

- What's The Difference Between The RS-232 and RS-485 Serial Interfaces?Document7 pagesWhat's The Difference Between The RS-232 and RS-485 Serial Interfaces?santanu_sinha87100% (2)

- Generating PWM With PIC Microcontroller - MikroC ProDocument3 pagesGenerating PWM With PIC Microcontroller - MikroC Proemilfrancu100% (1)

- Led DisplayDocument6 pagesLed DisplayIonut Octavian100% (2)

- Interface MSP430 With LCDDocument3 pagesInterface MSP430 With LCDLalith Krishnan100% (1)

- Uninterruptible Power Supply Reference Design With A PIC-Www - CircuitdiagramDocument60 pagesUninterruptible Power Supply Reference Design With A PIC-Www - Circuitdiagramirfan_ghani100% (1)

- Leakage and Continuity Tester: IdeasDocument1 pageLeakage and Continuity Tester: Ideassoumen1963100% (1)

- Ov7670 With Both Arduino Uno and Now MegaDocument96 pagesOv7670 With Both Arduino Uno and Now MegaThiago Cavalcante75% (4)

- ICD2 Poster 51265hDocument1 pageICD2 Poster 51265hngt881100% (1)

- Siemens Safety B10 Values - Extract From IC 10-2017Document2 pagesSiemens Safety B10 Values - Extract From IC 10-2017spuntoandreaNo ratings yet

- PDF Edne Nov 2013Document48 pagesPDF Edne Nov 2013torinomg100% (1)

- Pic-Web Development Board Users Manual: Rev.A, July 2008Document14 pagesPic-Web Development Board Users Manual: Rev.A, July 2008darazzi100% (1)

- WWW Mikroe Com Chapters View 69 Chapter 6 ExamplesDocument67 pagesWWW Mikroe Com Chapters View 69 Chapter 6 Examplesramnag4100% (1)

- Temperature Controlled Fan Using PIC 16F877A - GadgetronicxDocument8 pagesTemperature Controlled Fan Using PIC 16F877A - Gadgetronicxdevchandar100% (1)

- Broadband Lumped-Element Integrated - Way Power Dividers For Voltage StandardsDocument9 pagesBroadband Lumped-Element Integrated - Way Power Dividers For Voltage Standardsagmnm1962No ratings yet

- High Power CombinerDocument5 pagesHigh Power Combineragmnm1962No ratings yet

- A Novel Wideband Bandpass Power Divider With Harmonic Suppressed Ring Resonator 1.41-2.68 GHZDocument4 pagesA Novel Wideband Bandpass Power Divider With Harmonic Suppressed Ring Resonator 1.41-2.68 GHZagmnm1962No ratings yet

- 51W 10540 1Document16 pages51W 10540 1Mitrofan AnduNo ratings yet

- ACS712 Demo Board Guide PDFDocument11 pagesACS712 Demo Board Guide PDFagmnm1962No ratings yet

- Mirrored Coupling Structures For Microwave Signal Splitting and Combining PDFDocument6 pagesMirrored Coupling Structures For Microwave Signal Splitting and Combining PDFagmnm1962No ratings yet

- 12 G To 20 G Compact Rectangle Waveguide To Circular Waveguide Mode ConvertorDocument2 pages12 G To 20 G Compact Rectangle Waveguide To Circular Waveguide Mode Convertoragmnm1962No ratings yet

- A Compact Ultra-Wideband Power Divider With High Isolation 3.1-10.6 GHZDocument2 pagesA Compact Ultra-Wideband Power Divider With High Isolation 3.1-10.6 GHZagmnm1962No ratings yet

- Patch Antenna Design MAnualDocument36 pagesPatch Antenna Design MAnualkarthikvel_852246No ratings yet

- C106BOS Datasheetz PDFDocument6 pagesC106BOS Datasheetz PDFAnonymous na7OSZaNo ratings yet

- AN5142 Radio Link-Budget Calculations For ISM-RF ProductsDocument11 pagesAN5142 Radio Link-Budget Calculations For ISM-RF Productsagmnm1962No ratings yet

- DB3 DB4 SMDB3 - Diac PDFDocument6 pagesDB3 DB4 SMDB3 - Diac PDFmsicoie1851No ratings yet

- ADF4355 54-6800 MHZ Microwave Wideband Synthesizer With Integrated VCODocument35 pagesADF4355 54-6800 MHZ Microwave Wideband Synthesizer With Integrated VCOagmnm1962No ratings yet

- SP 500 SpecDocument2 pagesSP 500 Specagmnm1962No ratings yet

- Tipl762 - NPN Silicon Power TransistorsDocument7 pagesTipl762 - NPN Silicon Power Transistorsagmnm1962No ratings yet

- Scr's & Triacs Cross ReferenceDocument11 pagesScr's & Triacs Cross Referenceagmnm1962No ratings yet

- 200watt Active Load UnitDocument14 pages200watt Active Load Unitagmnm1962No ratings yet

- Data Sheet: UHF Push-Pull Power MOS TransistorDocument15 pagesData Sheet: UHF Push-Pull Power MOS Transistoragmnm1962No ratings yet

- Testing A Power Supply For Line and Load TransientsDocument7 pagesTesting A Power Supply For Line and Load Transientsagmnm1962No ratings yet

- MRF 175 GVDocument1 pageMRF 175 GVagmnm1962No ratings yet

- Sp431 High Voltage Adjustable Precision Shunt RegulatorsDocument11 pagesSp431 High Voltage Adjustable Precision Shunt Regulatorsagmnm1962No ratings yet

- Variable High Voltage BJT Regulator User ManualDocument7 pagesVariable High Voltage BJT Regulator User Manualagmnm1962No ratings yet

- tl783 PDFDocument26 pagestl783 PDFLuiz CaldeiraNo ratings yet

- Sprabw0b PDFDocument19 pagesSprabw0b PDFAshok KumarNo ratings yet

- Pads WhitepaperDocument23 pagesPads Whitepaperagmnm1962No ratings yet

- Christian AnderssonDocument55 pagesChristian Anderssonmarconi-agNo ratings yet

- Basic Calculation of A Boost Converter's Power StageDocument9 pagesBasic Calculation of A Boost Converter's Power Stagexuanvan1303No ratings yet

- Creating A Fast Load TransientDocument3 pagesCreating A Fast Load Transientagmnm1962No ratings yet

- LXA-7500 Series X-Band Low Noise AmplifiersDocument4 pagesLXA-7500 Series X-Band Low Noise Amplifiersagmnm1962No ratings yet

- A Review of Implantable Antennas For Wireless Biomedical DevicesDocument11 pagesA Review of Implantable Antennas For Wireless Biomedical Devicesagmnm1962No ratings yet

- HANA OverviewDocument69 pagesHANA OverviewSelva KumarNo ratings yet

- Genbio 1 NotesDocument1 pageGenbio 1 NoteselishaNo ratings yet

- AlgebraDocument66 pagesAlgebraOliseyenum Precious ChukuemekeNo ratings yet

- Various Image Enhancement Techniques-A Critical Review: S.S. Bedi, Rati KhandelwalDocument5 pagesVarious Image Enhancement Techniques-A Critical Review: S.S. Bedi, Rati KhandelwalArina AndriesNo ratings yet

- CHMT 2009 Week 5 Coal PropertiesDocument38 pagesCHMT 2009 Week 5 Coal PropertiesTiisetso MokwaneNo ratings yet

- Lab Assignment - 2: CodeDocument8 pagesLab Assignment - 2: CodeKhushal IsraniNo ratings yet

- PythagorasDocument109 pagesPythagorasaditya00012No ratings yet

- Chapter 7 Analysis of Stress and StrainDocument20 pagesChapter 7 Analysis of Stress and StrainLong Nguyễn HoàngNo ratings yet

- PHYSICSDocument24 pagesPHYSICS21SO204 AnvithaNo ratings yet

- Lab1: Access Control: Posix AclDocument7 pagesLab1: Access Control: Posix AclAla JebnounNo ratings yet

- Solution Manual For Introductory Statistics 9th Edition by Mann Chapters 1 13 PDFDocument10 pagesSolution Manual For Introductory Statistics 9th Edition by Mann Chapters 1 13 PDFa40095824643% (14)

- Engine Control System Circuit Diagram: Without This Message by Purchasing NovapdfDocument3 pagesEngine Control System Circuit Diagram: Without This Message by Purchasing NovapdfJose Luis Gutierrez TamayoNo ratings yet

- IK Gujral Punjab Technical University: 1. Electric ChargeDocument12 pagesIK Gujral Punjab Technical University: 1. Electric ChargeJashandeep KaurNo ratings yet

- Chapter 19. TemperatureDocument41 pagesChapter 19. TemperatureNguyên Nguyễn SơnNo ratings yet

- TE-419891-001 - 862-U-2301 - BIOCIDE DOSING PACKAGE - Rev.BDocument12 pagesTE-419891-001 - 862-U-2301 - BIOCIDE DOSING PACKAGE - Rev.Brizwan.zamanNo ratings yet

- Chapter 3Document23 pagesChapter 3pganoelNo ratings yet

- Murata Data Caps ESR ESLDocument6 pagesMurata Data Caps ESR ESLecl_manNo ratings yet

- Reverse Circulation Cementing: The Complete PictureDocument104 pagesReverse Circulation Cementing: The Complete PictureJoan Corso100% (1)

- Packages in JavaDocument4 pagesPackages in JavaKummeta KeerthiNo ratings yet

- EC 201 Network TheoryDocument2 pagesEC 201 Network TheoryJoseph JohnNo ratings yet

- Solved - Which $1,000 Bond Has The Higher Yield To Maturity, A T...Document4 pagesSolved - Which $1,000 Bond Has The Higher Yield To Maturity, A T...Sanjna ChimnaniNo ratings yet

- 3 DB RDMDocument49 pages3 DB RDMfaisal shahzadNo ratings yet

- From Assessment To Purchase - A Three-Stage ModelDocument15 pagesFrom Assessment To Purchase - A Three-Stage ModelRONAL EMERSON NOA ORTEGANo ratings yet

- Technical Data: Series Allclean AcnpDocument1 pageTechnical Data: Series Allclean AcnpBoško IvanovićNo ratings yet

- Coek - Info The Fabric of RealityDocument5 pagesCoek - Info The Fabric of RealityFredioGemparAnarqiNo ratings yet

- Chapter 6 AssignmentDocument6 pagesChapter 6 AssignmentRohit RajeevNo ratings yet

- Ampla's Technology ArchitectureDocument4 pagesAmpla's Technology ArchitecturesyeadtalhaaliNo ratings yet

- SPE-183743-MS Maintaining Injectivity of Disposal Wells: From Water Quality To Formation PermeabilityDocument19 pagesSPE-183743-MS Maintaining Injectivity of Disposal Wells: From Water Quality To Formation PermeabilityAminNo ratings yet

- Famous MathematicianDocument116 pagesFamous MathematicianAngelyn MontibolaNo ratings yet